The MC68302 is a versatile one-chip processor that incorporates the main building blocks needed for the

design of a wide variety of networking and communications products.

The MC68302 was the first device to offer the benefits of a closely coupled, industry-standard, MC68000/MC68008 microprocessor core and

a flexible communications architecture. This multi-channel communications device may be configured to

support a number of popular industry-standard interfaces, including those for the Integrated Services

Digital Network (ISDN) basic rate and terminal adapter applications. Through a combination of architectural

and programmable features, concurrent operation of different protocols is easily achieved using the

MC68302. Data concentrators, modems, line cards, bridges, and gateways are examples of other suitable

applications for this versatile device.

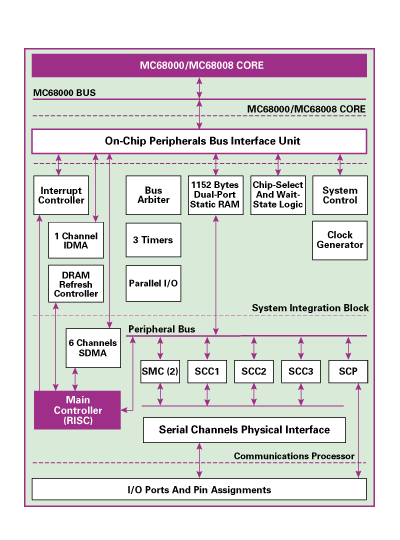

The MC68302 is an HCMOS device consisting of an

MC68000/MC68008 microprocessor core, a system integration block (SIB), and a communications processor (CP).

This device is still recommended for new designs.