#### **CHAPTER 1 - GENERAL INFORMATION**

#### 1•1 INTRODUCTION

This manual provides general information, preparation for use, installation and operating instructions, functional description, and support information for the M68302FADS Application Development System board.

#### 1•2 GENERAL FEATURES

- A complete system development board for 3 processors. The MC68302, MC68LC302 and MC68PM302.

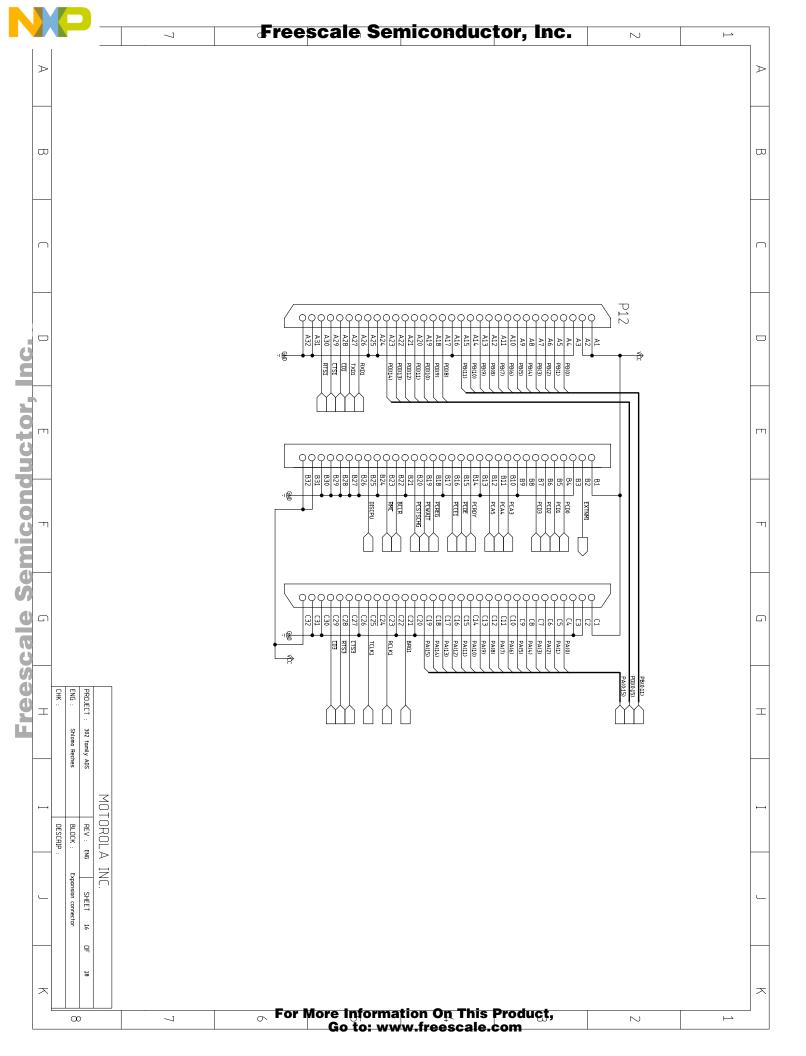

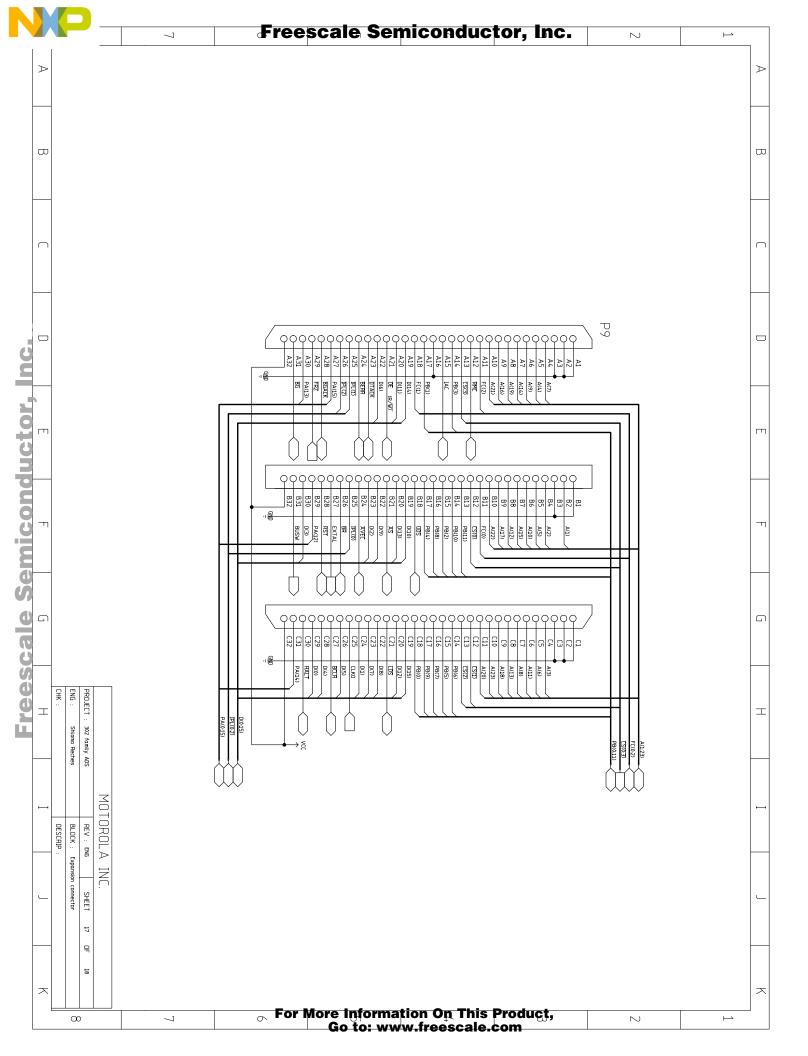

- Expansion connectors providing all 302 processor signals.

- Logic analyzer connectors similar to the expansion connectors.

- Single 5V supply.

- MC68302 core running at 25MHz.

- MC68LC302 core running at 20MHz.

- MC68302 core running at 20MHz.

- 512K byte, zero wait state static RAM, expandable up to 1M byte. (16 bit orientation)

- 1M byte FLASH. (16 bit orientation)

- 2K byte EEPROM. (8 bit orientation)

- Application Development Interface (ADI) port connector.

- MC68681 DUART, with wo RS232 serial ports.

- · RESET and ABORT controls.

- RUN and HALT status indicators. (LED's).

- Supports PCMCIA card standard 2.01. (For the MC68PM302)

- Board power can be controlled from the PCMCIA connector of an host PC. (Important when the ADS is used for developing a PCMCIA applications)

- An extender board for plugging into PCMCIA port is supplied with the M68302FADS ADS board.

- Bus expansion connector pin out, is compatible with the 302ADS.

#### 1•3 SPECIFICATIONS

The M68302FADS specifications and cooling requirements are given in Table 1-1.

Table 1-1 M68302FADS Specifications

| CHARACTERISTICS                                                        | SPECIFICATIONS                                                                                                                                 |

|------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| Power requirements (no other boards attached)                          | +5Vdc @ 0.8 A (typical), 3.15 A (maximum)                                                                                                      |

| Microprocessor                                                         | MC68302, MC68LC302, MC68PM302 - MC68302 @ 25 MHz - MC68LC302 @ 20 MHz - MC68PM302 @ 20 MHz                                                     |

| 302 processor addressing Total address range. SRAM FLASH memory EEPROM | 16M byte (4Mb external, for the LC302 and Pchip). 512K byte, 16 bit wide. (Expandable to 1M bytes) 1M byte, 16 bits wide. 2K byte, 8 bit wide. |

| Operating temperature                                                  | 0 degrees to 30 degrees C ambient air temperature                                                                                              |

| Storage temperature                                                    | -25 degrees to 85 degrees C                                                                                                                    |

| Relative humidity                                                      | 5% to 90% (non-condensing)                                                                                                                     |

| Dimensions Height Depth Thickness                                      | 9.196 inches (233.58 mm)<br>8.387 inches (213.03 mm)<br>0.063 inches (1.6 mm)                                                                  |

#### 1•4 COOLING REQUIREMENTS

The M68302FADS is specified designed, and tested to operate reliably with ambient air temperature range from 0 to 70 degrees C. Dynamic Burn-in is performed while the board is table mounted with no other boards attached to it. Test software is executed as the board is subjected to temperature variations. If the board is attached to other boards, the thermal conditions may worsen and it is recommended that operating temperature should not exceed 30 degrees C.

#### 1•5 GENERAL DESCRIPTION

The M68302FADS is a development tool for the MC68302, MC68LC302 and MC68PM302 devices. This board is used for hardware and software development of applications using any member of the 302 family. The M68302FADS has logic analyzer connectors as well as expansion connectors, providing physical connection to all processors' pins. The logic analyzer connectors, enable to monitor bus activity, by providing a direct connection to HP or other logic analyzers. The expansion connectors let the user, to attach hardware applications and to use board resources, to verify the design.

#### 1•6 RELATED DOCUMENTATION

The following publications are applicable to the M68302FADS and may provide additional helpful information.

- MC68302 IMP User's Manual.

- MC68LC302 IMP User's Manual.

- MC68PM302 IMP User's Manual.

- PCMCIA specifications paper

#### 1•7 ABBREVIATIONS USED IN THE DOCUMENT

- IMP The MC68302 integrated communication processor.

- LC302 or LCIMP A low cost version of the MC68302 integrated communication processor.

- PM302 or Pchip MC68302 integrated with a PCMCIA card interface.

- 302 processor Any of the IMP, LC302 and PM302.

- ADS Application Development System for the 302 family processor.

- ADI Application Development Interface.

- UART Universal Asynchronous Receiver/Transmitter.

- · spec Engineering specification document.

- nsec nano second.

- µsec micro second.

- NMI Non Maskable Interrupt.

#### 1•8 REQUIRED EQUIPMENT

The M68302FADS can be operated in two working environments:

- Host controlled

- Stand-alone

# AL INFORMATION

# Freescale Semiconductor, Inc.

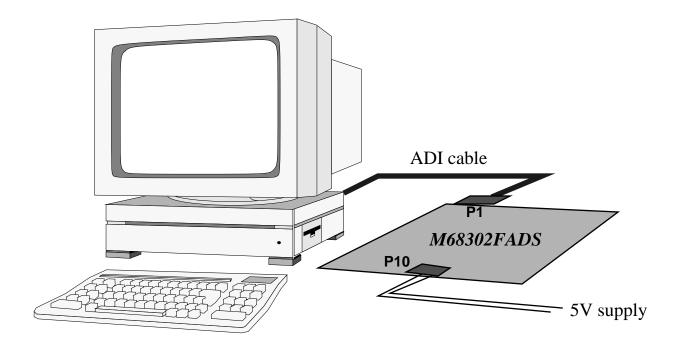

FIGURE 1-1 describes the setup of an host controlled mode.

The required equipment in this mode is as follows:

- +5V/3A power supply.

- Host Computer, one of the following:

- o Sun 4 (Sbus interface)

- o IBM-PC/XT/AT

- ADI board compatible with the host computer.

- 37 line flat cable with female 37 pin D-type connectors on each end.

## FIGURE 1-1 Host Controlled Configuration

## 1•8•1 Running the debugger

When the board is connected as shown in FIGURE 1-1, turn on the 5V power supply and run the host software, by typing:

host <ADI sbus slot No.> <ADS ADI address>

The manufacturer settings for ADS ADI address is 0. For more details on ADI addresses setting, please see section 2•3•2.

For example, to run the host on a sun machine with an ADI card installed in its Sbus slot number 1 and with ADS ADI address, set to 3, you should type, at command line prompt:

host 13

The prompt you get, depends on the processor installed, as listed in the following table

## **Table 1-2 Debugger prompt**

Freescale Semiconductor, Inc.

| Processor | Prompt                                                                                        |

|-----------|-----------------------------------------------------------------------------------------------|

| MC68302   | IMP Monitor/Debugger - Version 0.0 (C) Copyright 1995 by Motorola Inc. Cold Start IMPbug>     |

| MC68LC302 | LC302 Monitor/Debugger - Version 0.0 (C) Copyright 1995 by Motorola Inc. Cold Start LC302bug> |

| MC68PM302 | PCHIP Monitor/Debugger - Version 0.0 (C) Copyright 1995 by Motorola Inc. Cold Start PCHIPbug> |

## 1•8•2 Stand alone setup

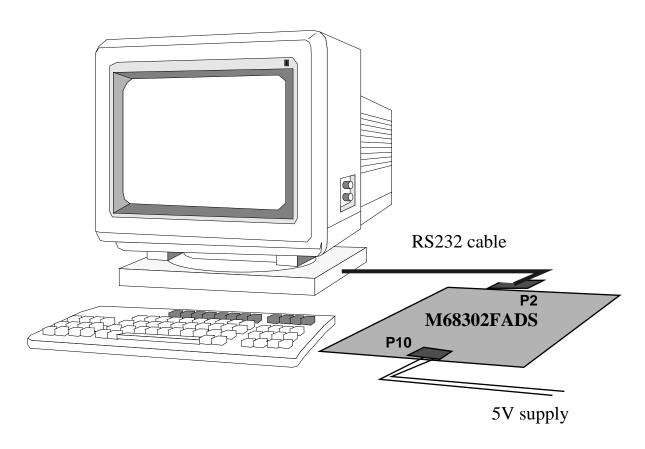

FIGURE 1-2 describes the setup of a stand-alone operating mode.

The required equipment in this mode is:

- +5V/3A power supply.

- VT100 compatible terminal.

- RS-232 cable with male 9 pin D-type connector on the ADS side.

FIGURE 1-2 Stand-alone Configuration

## 1•8•2•1 Terminal settings

The terminal connected to a M68302FASDS board, should be initialized to work with the following settings:

- Speed 9600 bps.

- · Character size 8 bits.

- Stop bit length 1 bit. (1.5 or 2 is fine but 1 is preferred for being a bit faster)

- No parity.

These settings are written shortly as - 9600, 8, 1 N.

After setting the terminal as specified and turning on the power, a debugger prompt as in Table 1-2, should appear on terminal screen.

## 1-8-2-2 Parallel ADI / Serial port, priority.

There is no control on board, to select between the parallel ADI or the serial port communication. The debugger decides automatically, with which it should communicate, by giving a priority to the serial port, in case, a terminal is detected. The serial port has some signals, by with the debugger can detect the presence of a terminal. If it is present, then the ADI connection is ignored and all board communication, goes to the serial port. When a terminal is not detected on the serial port, all communication, goes to the ADI port.

#### CHAPTER 2 - HARDWARE PREPERATION AND INSTALLATION

#### 2•1 INTRODUCTION

This chapter provides unpacking instructions, hardware preparation, and installation instructions for the M68302FADS.

#### 2•2 UNPACKING INSTRUCTIONS

#### **NOTE**

If the shipping carton is damaged upon receipt, request carrier's agent be present during unpacking and inspection of equipment.

Unpack equipment from shipping carton. Refer to packing list and verify that all items are present. Save packing material for storing and reshipping of equipment.

#### **CAUTION**

AVOID TOUCHING AREAS OF INTEGRATED CIRCUITRY; STATIC DISCHARGE CAN DAMAGE CIRCUITS.

#### 2•3 HARDWARE PREPARATION

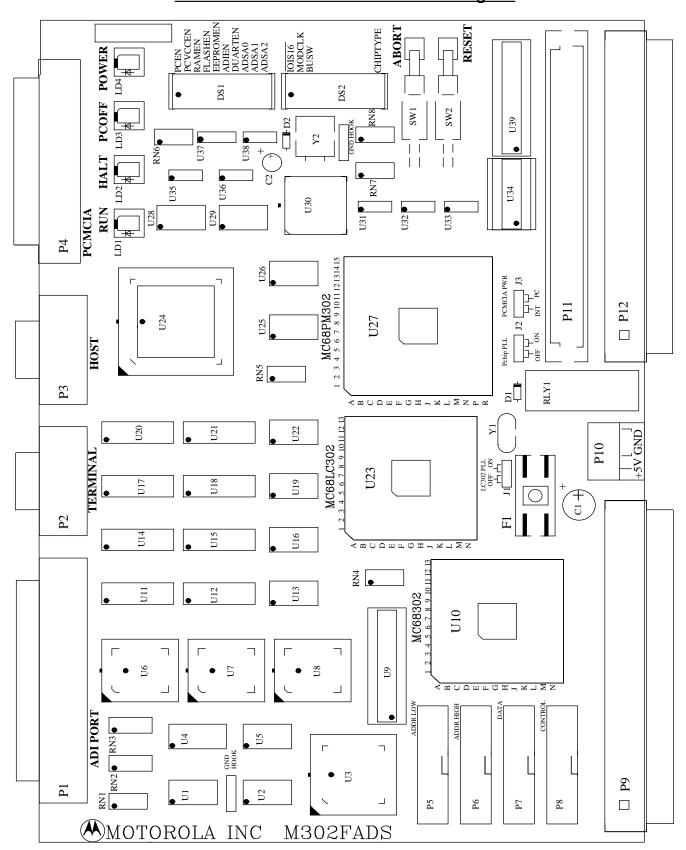

To select the desired configuration and ensure proper operation of the M68302FADS board, changes of the Dip-Switch/Jumpers settings may be required before installation. Switches, LEDs, Dip-Switches, and connectors are illustrated in FIGURE 1-3 M68302FADS Location diagram on page 11. The board has been factory tested and is shipped with Dip-Switch settings as described in the following paragraphs. Parameters can be changed for the following conditions:

- On board resources enable (SRAM, Flash, EEPROM, ADI port and DUART)

- Bus width.

- PLL ON/OFF.

- Processor type selection.

- ADI port address selection.

- Pchip PCMCIA enable.

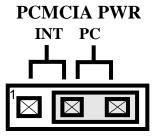

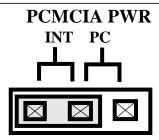

- Pchip PCMCIA block power source.

FIGURE 1-3 M68302FADS Location diagram

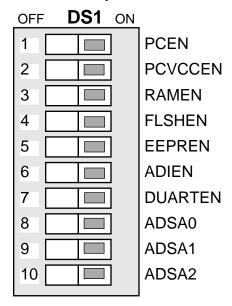

# 2•3•1 DS1 DIP switch configuration.

# FIGURE 1-4 Dip-Switch DS1

Table 1-3 describes the function of switches 1 - 7.

**Table 1-3 Dip-Switch DS1 Description**

| Switch | Name    | Function                                                                                                                                                                                                         | Default setting |  |  |  |

|--------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--|--|--|

| 1      | PCEN    | Direct control over the Pchip signal PCEN. When set to On, the internal Pchip PCMCIA interface is disabled.                                                                                                      |                 |  |  |  |

| 2      | PCVCCEN | When set to ON, the board is powered unconditionally, with respect to PCMCIA host power. When set to OFF, the board is powered, only when the host connected to the board through the PCMCIA port, is turned on. | ON              |  |  |  |

| 3      | RAMEN   | When set to ON, on board SRAM is enabled. (1Mbyte space)                                                                                                                                                         | ON              |  |  |  |

| 4      | FLSHEN  | When set to ON, on board FLASH memory is enabled.                                                                                                                                                                | ON              |  |  |  |

| 5      | EEPREN  | When set to ON, on board EEPROM is enabled.                                                                                                                                                                      | ON              |  |  |  |

| 6      | ADIEN   | When set to ON, ADI interface is enabled.                                                                                                                                                                        | ON              |  |  |  |

| 7      | DUARTEN | When set to ON, DUART MC68681 along with its RS232 port are enabled.                                                                                                                                             | ON              |  |  |  |

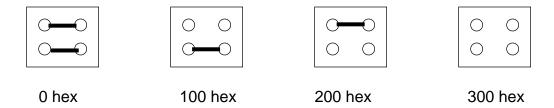

## 2•3•2 ADI Port Address Selection (Dip-Switch DS1 switches 8-10)

Each M68302FADS can have eight possible ADI port addresses, enabling up to eight M68302FADS boards to be connected to the same ADI card in a host computer. Address selection is done by setting switches 8, 9, 10 in DS1 Dip-Switch. Switch 10 is the most significant bit of the address while switch 8 is the least. A switch set to its 'ON' state, stands for logical '0'. The default setting is ADI address - 7.

Table 2-1 describes the switch settings for each slave address:

**Table 2-1 ADI Address Selection**

| ADDRESS | Switch 10 | Switch 9 | Switch 8 |

|---------|-----------|----------|----------|

| 0       | ON        | ON       | ON       |

| 1       | ON        | ON       | OFF      |

| 2       | ON        | OFF      | ON       |

| 3       | ON        | OFF      | OFF      |

| 4       | OFF       | ON       | ON       |

| 5       | OFF       | ON       | OFF      |

| 6       | OFF       | OFF      | ON       |

| 7       | OFF       | OFF      | OFF      |

# 2•3•3 DS2 DIP switch configuration (for LC302/PM302).

## FIGURE 1-5 Dip-Switch DS2

| OFF | D | <u>S2</u> | ON |          |

|-----|---|-----------|----|----------|

| 1   |   |           |    | IOIS16   |

| 2   |   |           |    | MODCLK   |

| 3   |   |           |    | BUSW     |

| 4   |   |           |    |          |

| 5   |   |           |    |          |

| 6   |   |           |    |          |

| 7   |   |           |    |          |

| 8   |   |           |    |          |

| 9   |   |           |    |          |

| 10  |   |           |    | CHIPTYPE |

Table 2-2 Dip-Switch DS2 description.

| Switch | Name     | Function                                                                                                                                                                                | Default                           |

|--------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

| 1      | IOIS16   | Set IOIS16 PCMCIA signal level. IOIS16, is not supported by the Pchip. When set to on, PCMCIA I/O transfers are 8 bits width. When set to off, PCMCIA I/O transfers, are 16 bits width. | ON                                |

| 2      | MODCLK   | Select PLL multiplication factor when PLL is enabled. (See J1, J2 jumpers) ON - selects x4 multiplication factor and OFF - selects x401 for 32KHz crystal.                              | ON                                |

| 3      | BUSW     | Controls BUSW input of the processor. Selects 16 bit bus when OFF and 8 bit bus width when set to ON.                                                                                   | OFF                               |

| 10     | CHIPTYPE | Selects between IMP and LC302/Pchip mode. ON - IMP, OFF - LC302 and Pchip.                                                                                                              | ON = IMP<br>OFF = LC302/PM302 (*) |

<sup>\*</sup> FIGURE 1-5, shows default settings for the LC302 and PM302. When the IMP is plugged in, switch 10 should be set to ON. All other switches are the same as for the LC302/PM302.

#### 2•4 INSTALLATION INSTRUCTIONS

When the M68302FADS has been configured as desired by the user, it can be installed according to the required working environment as follows:

## 2•4•1 +5V Power Supply Connection

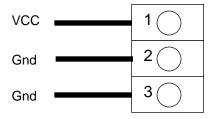

The M68302FADS requires +5Vdc @ 1A max, power supply for operation. The ADS has 3.15A fuses on the +5V line, and it is protected against reverse connection of the power supply. Connect the +5V power supply to connector P10 as shown below:

FIGURE 1-6 P18: +5V Power Connector

P10 is a 3 terminal block power connector with power plug. The plug is designed to accept 14 to 22 AWG wires. It is recommended to use 14 to 18 AWG wires. To insure solid ground, two Gnd terminals are supplied. It is recommended to connect both Gnd wires to the common of the power supply, while VCC is connected with a single wire.

#### **NOTE**

Since hardware applications can be connected to the M68302FADS using the expansion connectors P9 and P12, the additional power consumption should be taken into consideration when a power supply is connected to the ADS.

#### 2•4•2 ADI Installation

For ADI installation on various host computers, refer to APPENDIX A - ADI BOARD INSTALLATION on page 50.

### 2•4•3 Host computer to ADS connection

The M68302FADS ADI interface connector, P1, is a 37 pin, male, D type connector. The connection between the M68302FADS and the host computer is made by a 37 line flat cable, supplied with the ADI board. FIGURE 1-7 below shows the connector pin arrangement of the connector.

## FIGURE 1-7 ADI Port Connector P1

| Gnd Gnd Gnd Gnd Gnd Gnd Gnd (+ 12 v) N.C. HOST_VCC HOST_VCC HOST_VCC HOST_VCC HOST_PDC Gnd Gnd Gnd PD0 PD2 PD4 PD6 | 20<br>21<br>22<br>23<br>24<br>25<br>26<br>27<br>28<br>29<br>30<br>31<br>32<br>33<br>34<br>35<br>36<br>37 | 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16<br>17<br>18<br>19 | INT_ACK N.C. HST_ACK ADS_ALL ADS_RESET ADS_SEL2 ADS_SEL1 ADS_SEL0 HOST_REQ ADS_REQ ADS_ACK ADS_INT HOST_BRK~ ADS_BRK N.C. PD1 PD3 PD5 PD7 |

|--------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

|--------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

NOTE: Pin 26 on the ADI is connected to +12 v power supply, but it is not used in the ADS.

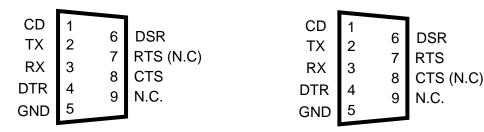

#### 2•4•4 Terminal to M68302FADS RS-232 Connection. (DCE port)

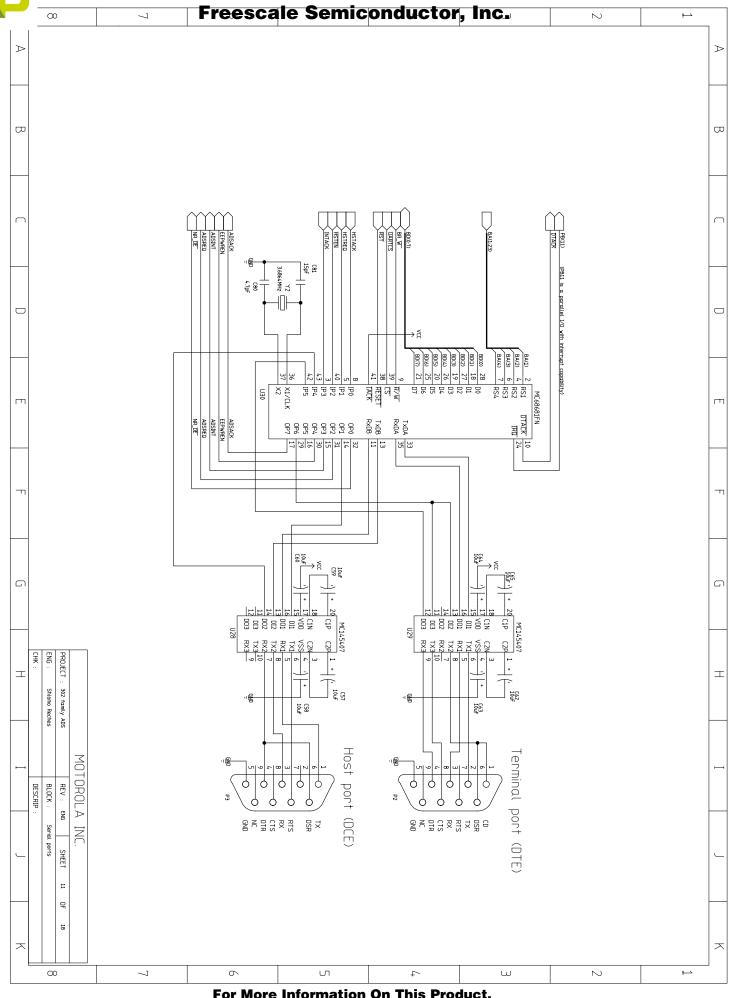

In a stand-alone operation mode, a VT100 compatible terminal should be connected to the RS-232 connector P2. The RS-232 connector is a 9 pin, female, D-type connector as shown in FIGURE 1-8.

FIGURE 1-8 RS-232 Serial Port Connector P2

NOTE: The RTS line (pin 7) is not connected in the M68302FADS.

## 2•4•5 Secondary RS-232 port. (DTE port)

The second RS232 port, is controlled, is not supported by the debugger. The user should write his own drivers to use this port. The connector pin out is shown in FIGURE 1-8.

## FIGURE 1-9 RS-232 Serial Port Connector P3

| TX   | 1 | 6 | DSR  |

|------|---|---|------|

| RX   | 2 | 7 | RTS  |

| DTR  | 3 | 8 | CTS  |

| GND  | 5 | 9 | N.C. |

| GIND |   |   |      |

NOTE: The CTS line (pin 8) is not connected in the M68302FADS.

### **CHAPTER 3 - OPERATING INSTRUCTIONS**

#### 3•1 INTRODUCTION

This chapter provides necessary information to use the M68302FADS in host-controlled and in a standalone configuration. This includes controls, indicators, memory map details, and software initialization of the board.

#### 3•2 CONTROLS AND INDICATORS

The M68302FADS has the following switches and indicators.

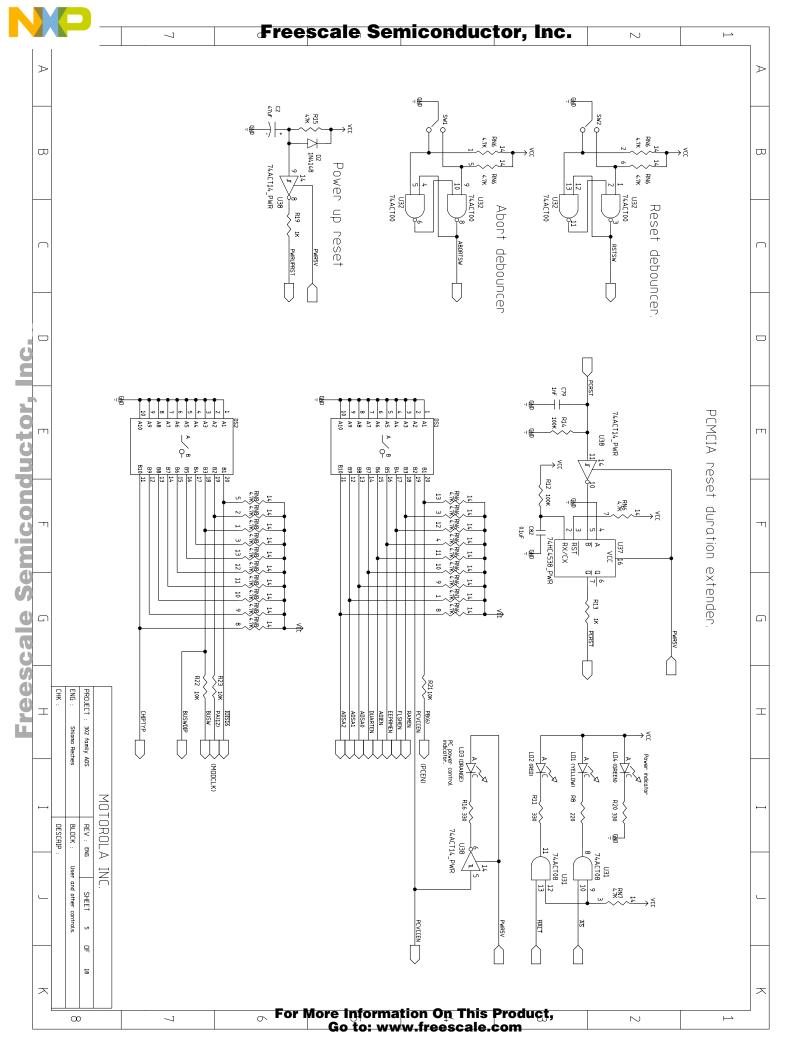

## 3•2•1 NMI (Abort) Switch SW1

The NMI switch SW2 asserts level 7 interrupt to the processor. The switch signal is debounced, and It is not possible to disable it by software. The NMI (Abort) switch is normally used to abort program execution and return the debugger control.

#### 3•2•2 RESET Switch SW2

The RESET switch SW2, resets all ADS devices and performs reset to the 302 processor. The switch signal is debounced, and it is not possible to disable it by software.

## 3•2•3 LC302 PLL enable jumper - J1.

The PLL of the LC302, is controlled by applying or preventing PLL block power, on the VCCSYN pin. The selection, is done with J1 jumper, as shown in FIGURE 1-10.

## FIGURE 1-10 LC302 PLL enable jumper (J1)

#### LC302 PLL - Disabled

When the jumper is installed on pins 2 - 3, LC302 PLL is disabled. This actually shorts the LC302 VCCSYN pin, to ground.

#### LC302 PLL enabled

When the jumper is installed on pins 1 - 2, the LC302 PLL is enabled. This actually connects VCCSYN pin of the LC302 to VCC.

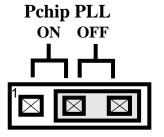

### 3•2•4 Pchip PLL enable jumper - J2.

The PLL of the Pchip, is controlled by applying or preventing PLL block power, on the VCCSYN pin. The selection, is done with J2 jumper, as shown in FIGURE 1-10.

## FIGURE 1-11 Pchip PLL enable jumper (J2)

#### **Pchip PLL - Disabled**

When the jumper is installed on pins 2 - 3, the Pchip PLL is disabled. This actually shorts the Pchip VCCSYN pin, to ground.

#### **Pchip PLL enabled**

When the jumper is installed between pins 1 - 2, the Pchip PLL is enabled. This actually connects VCCSYN pin of the Pchip to VCC.

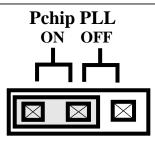

#### 3•2•5 PCMCIA power source selection - J3.

The PCMCIA block in the Pchip, can be powered by one of two sources. The first is the board common VCC supply and the second is an external power, supplied through a PC host, plugged into the PCMCIA connector. The selection, is done with J3 jumper, as shown in FIGURE 1-12.

## FIGURE 1-12 Pchip PLL enable jumper (J3)

# Pchip PCMCIA block is powered by a host PC

When the jumper is installed on pins 2 - 3, the Pchip PCMCIA block, get its power from a host PC, connected to PCMCIA connector - P4.

## Pchip PCMCIA block is powered by board supply board

When the jumper is installed on pins 1 - 2, the Pchip PCMCIA block, get its power from the board common supply.

#### 3•2•6 RUN indicator LD1

This yellow indicator is connected to the 302 processor address strobe (AS~) signal. It lit when AS~ is low (asserted) to indicate a bus activity.

#### 3•2•7 HALT indicator LD2

This red indicator, lit whenever the 302 processor HALT~ pin is low (asserted).

#### 3•2•8 PCOFF indicator LD3

This orange indicator, lit when PCMCIA power control is selected by the DIP-Switch DS1 switch 2 (PCVCCON set to the OFF position) and no external power is detected on the PCMCIA connector - P4. This is a reminder to the user, that the board is not powered, despite power existence, on P10 connector. The board would be powered, upon detection of a turned on PC, on the PCMCIA connector - P4.

#### 3•2•9 Power indicator LD4

This green indicator, lit when the board is powered. Please be aware that suppling 5V to P10 connector does not assure it is powered. When DIP switch DS2 switch number 2, is set to its off position, board power, is PCMCIA power dependent. The on board relay switches the power off, unless a 5V power is detected on the PCMCIA port. When DIP switch DS2 switch number 2, is set to its on position, the board is powered when 5V is supplied trough P10, unconditionally of PCMCIA port status.

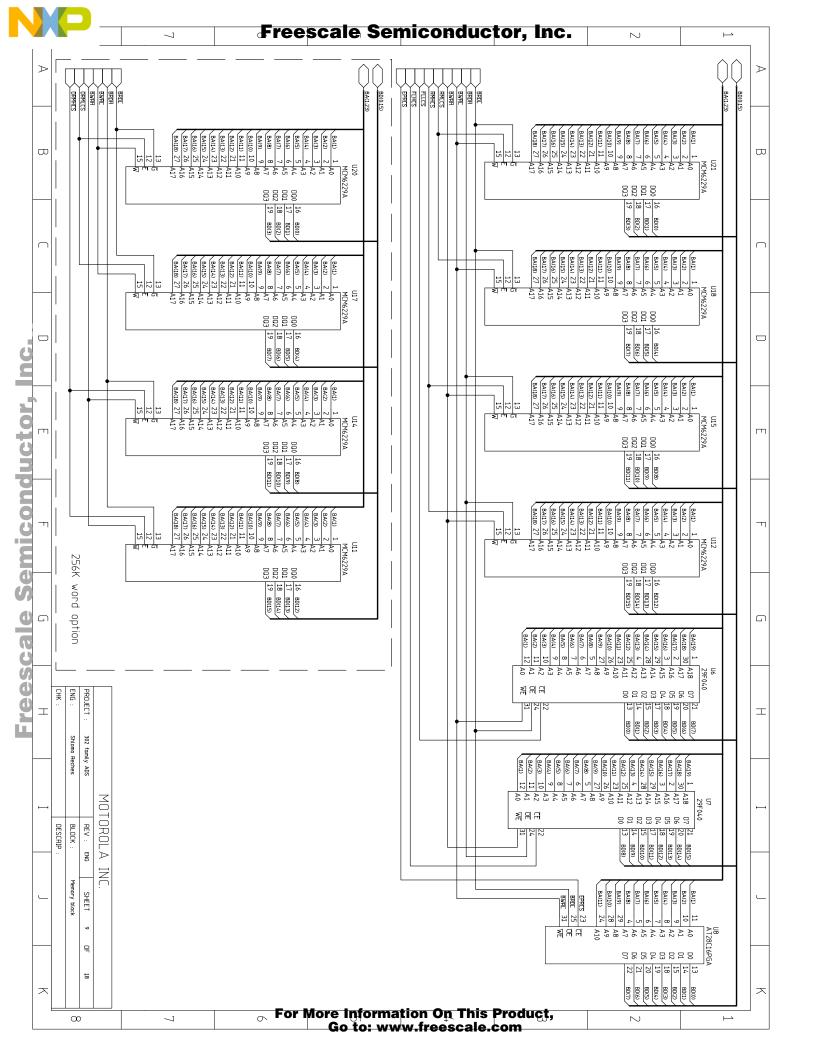

#### 3•3 IMP MEMORY MAP

FIGURE 1-13 IMP memory map on page 21, is one of two maps. After a cold or warm reset, the 302 processor's CS0, is automatically enabled for the first block of 8K bytes. In this page the 302 processor sees the first 8K bytes of the 1M bytes FLASH memory installed. No other space than those 8K, is available this time. At this point, the stack pointer and the program counter are fetched from Flash and the debugger starts. One of the debugger first tasks, is to enable the map shown in FIGURE 1-13. It is done by copying the code for the swap task, into the 302 processor's dual port Ram and jump to execute the code. The code redefines CS0, CS1 and CS2 to enable the map shown in FIGURE 1-13 and goes back to the debugger which has been moved due to the new map, to offset 20000H. The swap task is executed from the dual port RAM, so it would not be interrupted by the swap. The swap is done, in order to map a RAM at the 302 processor vector table (start at \$0), so the user would be able to change those vectors. (and not a FLASH at \$0 - a must after reset)

#### FIGURE 1-13 IMP memory map

|                  | D15 I              | D8  | D7                                   | D0  |                  |

|------------------|--------------------|-----|--------------------------------------|-----|------------------|

| FFFFFE           |                    |     |                                      |     | FFFFFF           |

| 700000           |                    |     | MC68302 internal<br>er applications. | í   | 700001           |

| 6FFFE            |                    |     |                                      |     | 6FFFF            |

|                  |                    |     | MC68681 DUA                          | ٩RT | 630001<br>620001 |

| 610000           |                    |     | 2K byte EEPR                         | OM  | 610001           |

| 600000           | ADI handshake      |     | ADI port da                          | ıta | 600001           |

| 5FFFFE           |                    |     |                                      |     | 5FFFFF           |

|                  |                    |     |                                      |     | 510001           |

| 500000           |                    |     |                                      |     | 500001           |

| 4FFFFE           |                    |     |                                      |     | 4FFFFF           |

|                  |                    |     |                                      |     | 410001           |

| 400000<br>3FFFFE |                    |     |                                      |     | 400001<br>3FFFFF |

| 311111           |                    |     |                                      |     | 511111           |

| 300000           |                    |     |                                      |     | 300001           |

| 2FFFFE           |                    |     |                                      |     | 2FFFFF           |

|                  | 1M byte FL         | _AS | H memory <sup>*</sup>                |     |                  |

| 200000           |                    |     |                                      |     | 200001           |

| 1FFFFE           |                    |     |                                      |     | 1FFFFF           |

|                  |                    |     |                                      |     |                  |

| 100000           |                    |     |                                      |     | 100001           |

| 0FFFFE<br>080000 | 512K byte static R | RAM | expansion mem                        | ory | 0FFFFF<br>080001 |

| 07FFFE           | 512K byte static   | RAN | A base memorv*                       |     | 07FFFF           |

| 000000           |                    |     |                                      |     | 000001           |

\*Note: The debugger uses 0-7FFF in the Static RAM and from 200000 to 21FFFF in the Dynamic RAM.

Each board comes with 1M byte of Flash memory (oriented as 512K words of 16 bits each) and a 512K bytes of static RAM (oriented as 256K words 16 bits each). The RAM can be expanded, on board to a total of 1M bytes. ADI logic, DUART MC68681 and 2K byte EEPROM, occupies each 64K byte which is the minimum division available, by on board chip select logic. Each empty space in the map, is considered available for the user. Any of the on board resources, can be disabled, to free its memory allocation for the user. Please see Table 1-3 Dip-Switch DS1 Description on page 12.

## 3•3•1 DUART MC68681 registers.

Table 2-3, shows the MC68681 internal registers. This is an eight bit device, connected to D0-D7 and thus located on odd addresses.

Table 2-3 MC68681 internal registers

| Register address | Read (R/W~ = 1)                            | Write (R/W~ = 0)                             |

|------------------|--------------------------------------------|----------------------------------------------|

| \$620001         | Mode register A (MR1A, MR2A)               | Mode register A (MR1A, MR2A)                 |

| \$620003         | Status register A (SRA)                    | Clock select register A (CSRA)               |

| \$620005         | Do not access *                            | Command register A (CRA)                     |

| \$620007         | Receiver buffer A (RBA)                    | Transmitter buffer A (TBA)                   |

| \$620009         | Input port change register (IPCR)          | Auxiliary control register (ACR)             |

| \$62000B         | Interrupt status register (ISR)            | Interrupt mask register (IMR)                |

| \$62000D         | Counter mode: Current MSB of counter (CUR) | Counter/Timer upper register (CTUR)          |

| \$62000F         | Counter mode: Current LSB of counter (CLR) | Counter/Timer lower register (CTLR)          |

| \$620011         | Mode register B (MR1B, MR2B)               | Mode register B (MR1B, MR2B)                 |

| \$620013         | Status register B (SRB)                    | Clock select register B (CSRB)               |

| \$620015         | Do not access *                            | Command register B (CRB)                     |

| \$620017         | Receiver buffer B (RBB)                    | Transmitter buffer B (TBB)                   |

| \$620019         | Interrupt vector register (IVR)            | Interrupt vector register (IVR)              |

| \$62001B         | Input port (unlatched)                     | Output port configuration register (OPCR)    |

| \$62001D         | Start counter command **                   | Output port register (OPR) bit set command   |

| \$62001F         | Stop counter command **                    | Output port register (OPR) bit reset command |

<sup>\*</sup> This address is used for factory testing and should not be accessed by the user.

For more details about the MC68681 DUART, please refer to M68000 family reference.

<sup>\*\*</sup> A trigger command.

# Freescale Semiconductor, Inc. OPERATING INSTRUCTIONS

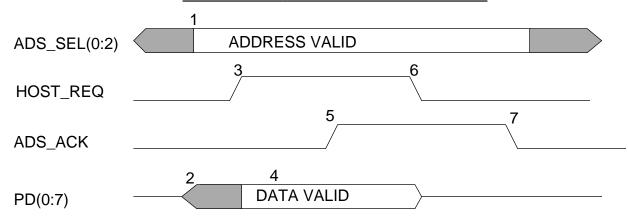

### 3•3•2 ADI handshake signals

ADI handshake signals consist of in and out, going signals. In going signals can be read from the MC68681 DUART input port found in address \$62001B or from the ADI input port located at address \$600000. The second is preferred due to the user ability to map the DUART off. The outgoing signals of the ADI interface are found in the DUART output port latch. In order to let the ADI port, be functional, when the DUART is disabled, all DUART register involved with the ADI outgoing handshake signals, were logically duplicated into the ADI space. So now, the outgoing signals, can be accessed trough two base addresses. The DUART as well as the ADI. Of course the second is preferred from the same reason explained above.

The following tables shows relevant ADI registers as well as the internal bit map of each register.

## Table 2-4 ADI registers.

| Address  | Read (R/W~ = 1)  | Write (R/W~ = 0)                                |

|----------|------------------|-------------------------------------------------|

| \$600000 | ADI input port   | Do not access                                   |

| \$60001B | DUART input port | DUART output port configuration register (OPCR) |

| \$60001D | Do not access    | DUART output port (OPR) bit set command         |

| \$60001F | Do not access    | DUART output port (OPR) bit reset command       |

To set a DUART output bit, a "1", should be written to the desired bit of the DUART OPR <u>reset</u> command register. To reset a DUART output bit, a "1", should be written into the DUART OPR <u>set</u> command register.

### Table 2-5 DUART output port bit set/reset map @\$60001D/@\$60001F

| 7       | 6                              | 5    | 4                   | 3       | 2       | 1        | 0        |

|---------|--------------------------------|------|---------------------|---------|---------|----------|----------|

| ADS ACK | CTS, DSR & CD to the terminal. | N.C. | EEPROM<br>wr enable | ADS INT | ADS REQ | Not used | Int mode |

## Table 2-6 DUART input port bit map @\$60001B

| 5                  | 4          | 3       | 2       | 1       | 0       |

|--------------------|------------|---------|---------|---------|---------|

| DTR from terminal. | Read as'0' | INT ACK | HST_EN~ | HST REQ | HST ACK |

#### Table 2-7 ADI input port bit map @600000

| 7          | 6          | 5          | 4       | 3       | 2       | 1       | 0        |

|------------|------------|------------|---------|---------|---------|---------|----------|

| Read as'0' | Read as'0' | Read as'0' | INT ACK | HST ACK | HST REQ | ADS BRK | ADS_SEL~ |

ADS\_SEL~ signal, is not a member in the ADI protocol, but is a signal, generated on board, to report, the ADS, is selected by the host. For more details on the ADI protocol, please refer to APPENDIX B - ADI PORT HANDSHAKE DESCRIPTION on page 55.

## 3•4 The IMP debugger.

Each M68302FADS board, is installed with a debugger, resides on the first two sectors of FLASH memories, U6, U7. Each sector of AM29F040 device, is 64K bytes, thus a total of 128K bytes (1 sectors per FLASH), are allocated for the debugger. Those two sectors are protected by software against, accidental programming.

#### 3•4•1 Debugger upgrade.

The debugger supports an on board upgrade capabilities. A new debugger release, is programmed on board, without the need to take the FLASHes out of their sockets and without the need of a special programmer. Further instruction will be supplied, with each upgrade.

#### 3•4•2 The debugger programming, of internal 302 processor registers.

The initialization done by the debugger to an internal 302 family processor registers, is writing to the base address register (BAR) and programming CS0, CS1 and CS2.

- The BAR is initialized, so the processor register block, resides starting from \$700000.

- CS0 is initilized for 1M bytes FLASH starting at 200000H.

- CS1 is initilized for 1M bytes RAM (512K bytes acttualy installed) starting at 000000H.

- CS2 is initilized for 30000H bytes starting at 600000H. CS3 is used for the ADI, EEPROM and DUART. The internal division of this space, is done by an additional logic, outside the 302 processor.

## 3•5 Functional description

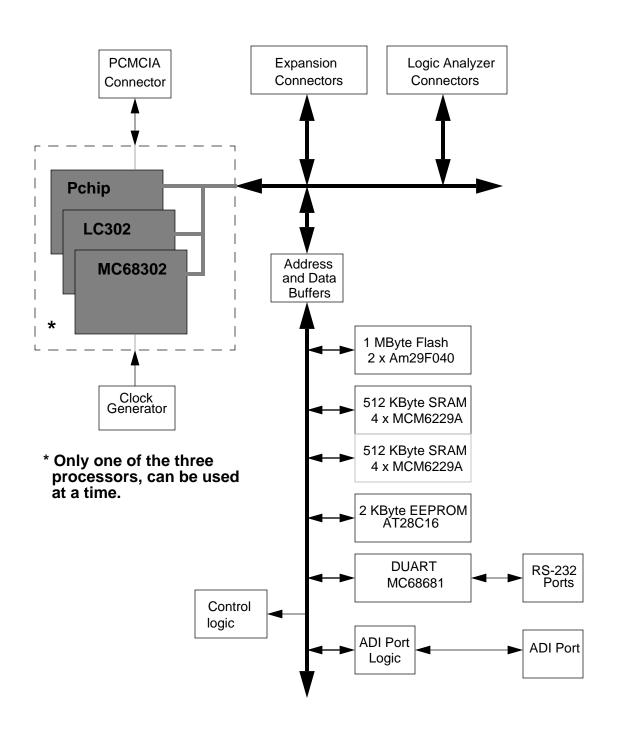

#### FIGURE 1-14 HARDWARE BLOCK DIAGRAM

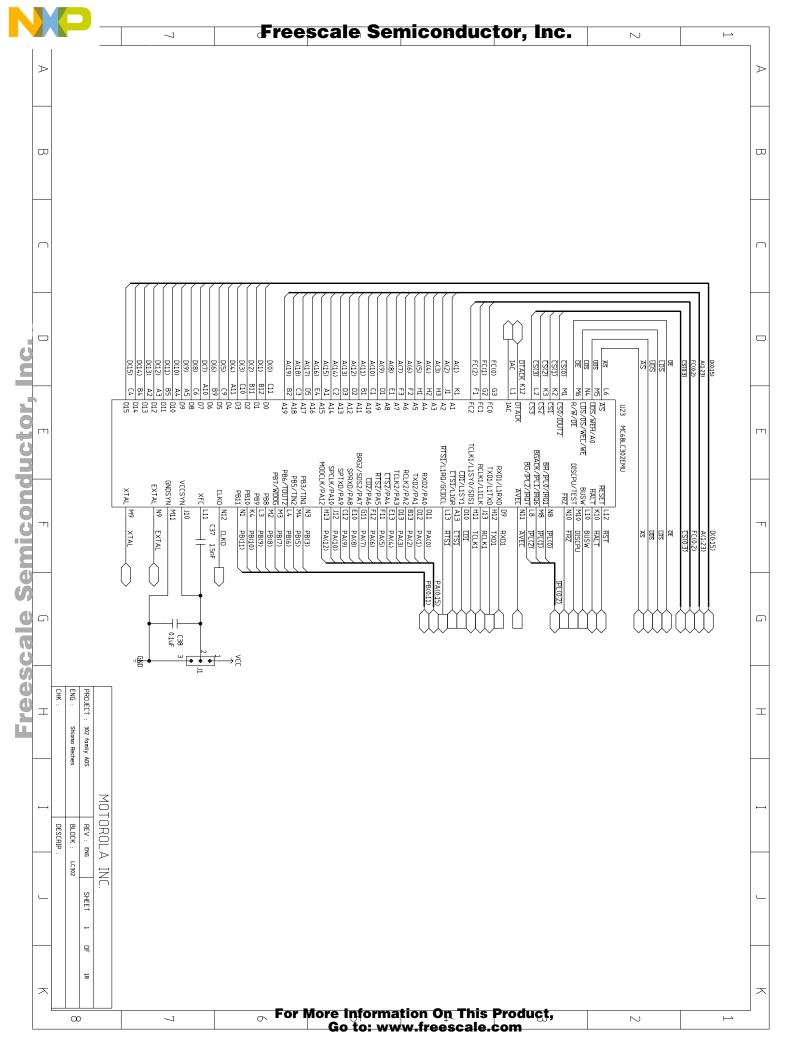

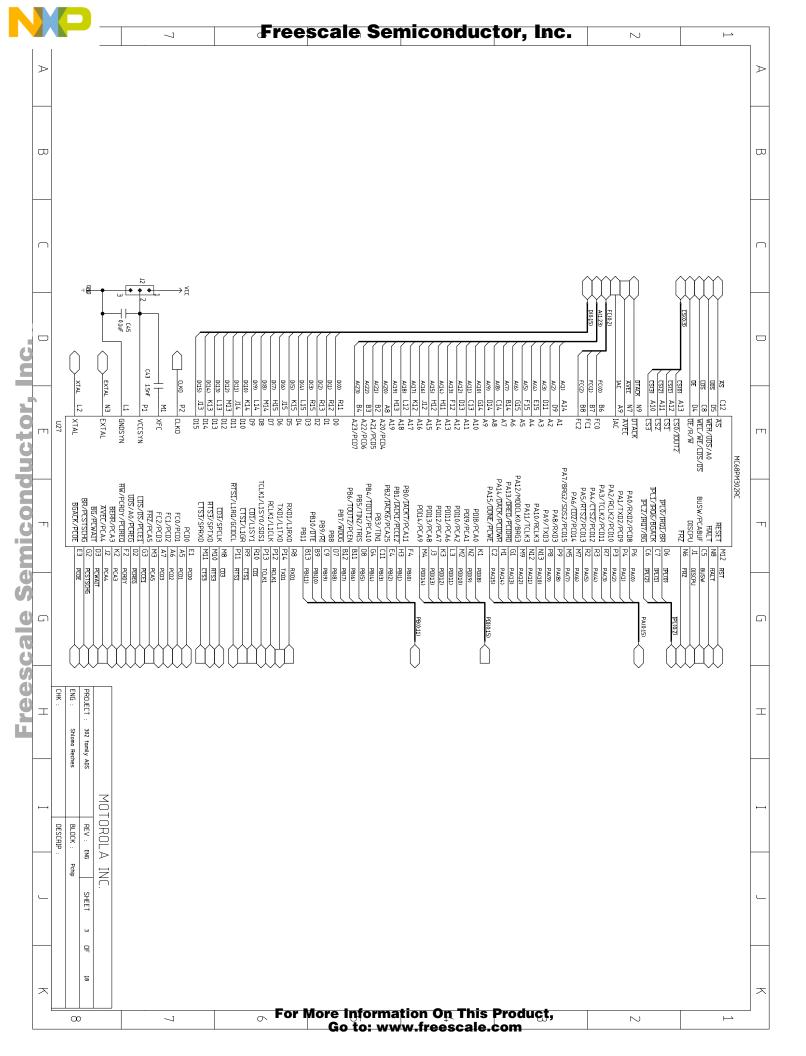

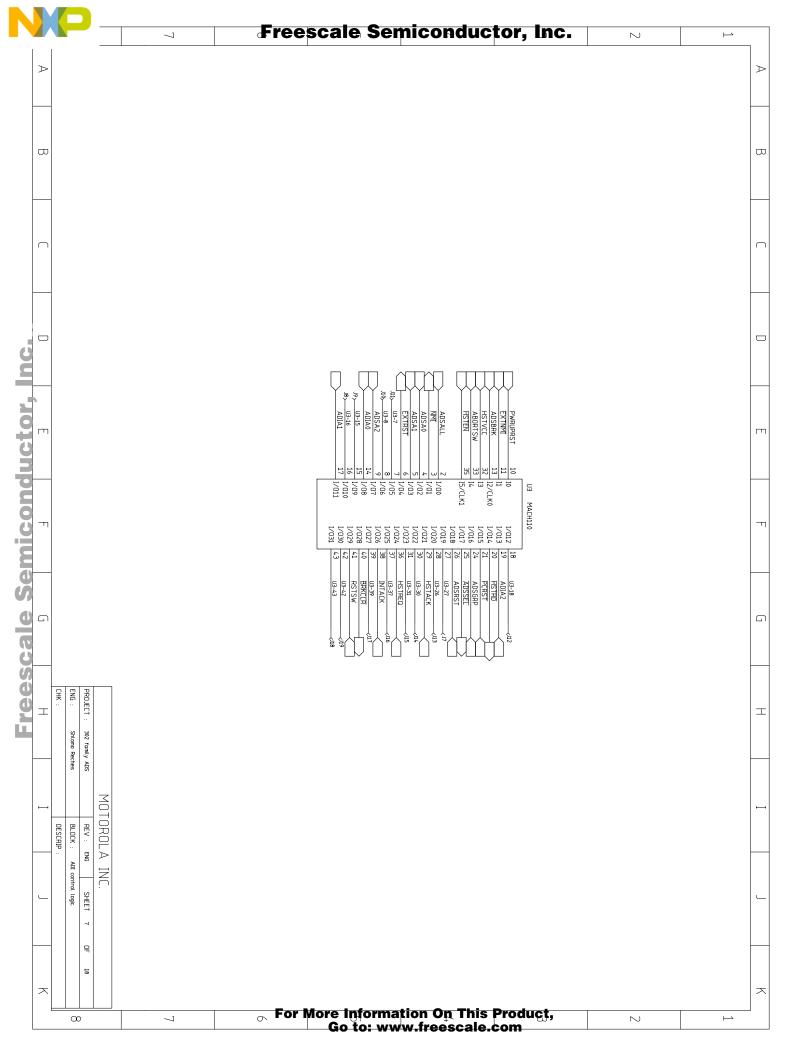

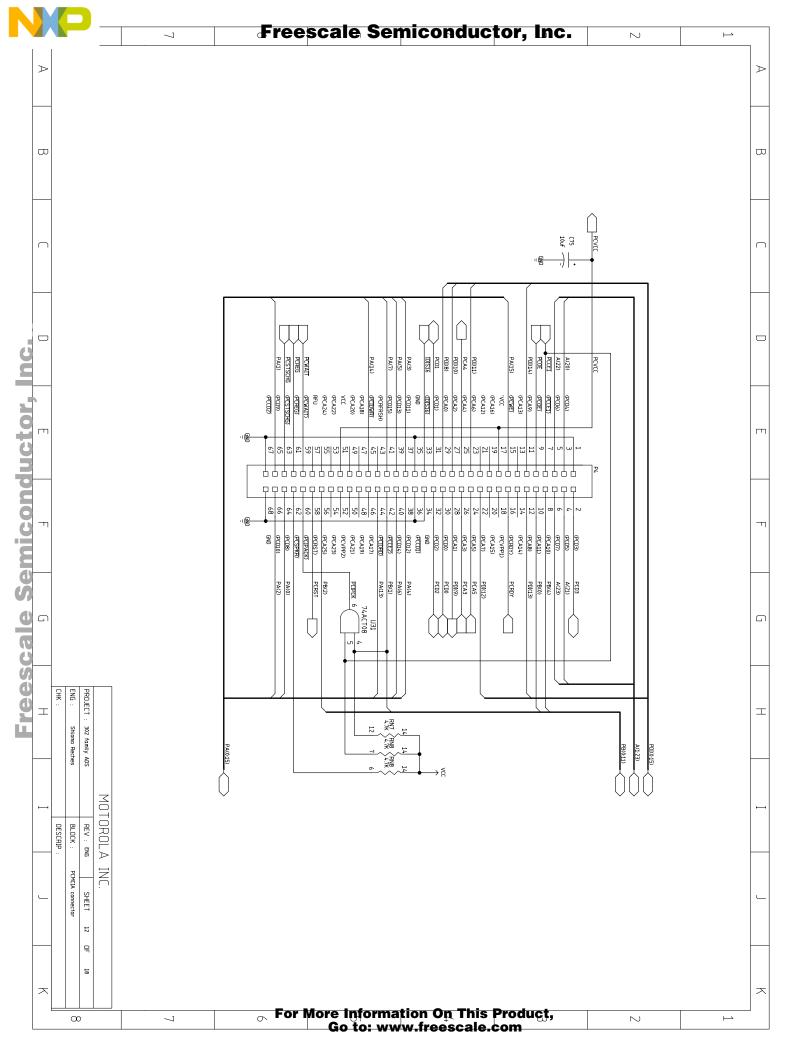

#### 3•5•1 MC68LC302 - LCIMP. (Sheet 1)

The LC302 is a low cost version of the original MC68302 - IMP, with an additional on chip PLL. The LC302, lacks a third SCC and has less pins in total. Pins that were taken off, includes the 4 upper address lines (A20-A23), function code (F0-F2), arbitration logic (BR~, BG~, BGACK) and more. For more details please refer to the MC68LC302 user manual. There are 2 packages available for the LC302. An 100 pin TQFP and 132 pin PGA package. The first has less functional pins and it is the low cost package you intended to put in your application. The PGA package is intended primary for development tools and is used in the M68302FADS. The pins added in the PGA package only are - FC0 - FC2, FRZ~, AVEC~ and IAC.

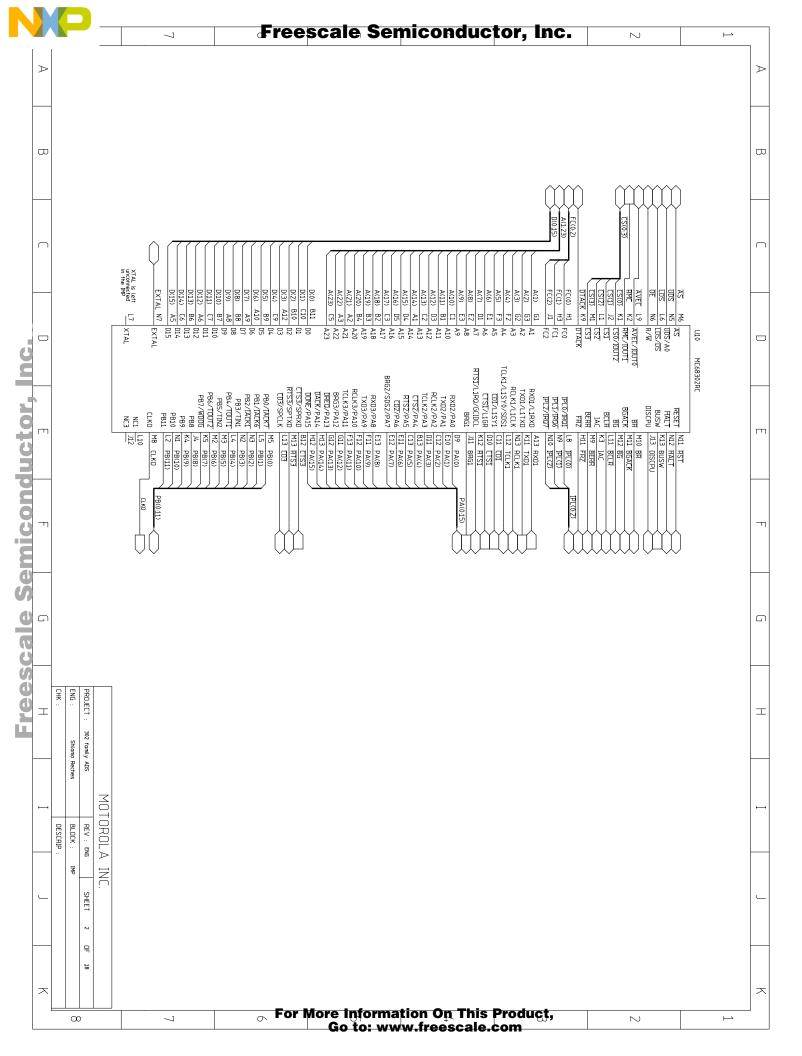

#### 3•5•2 MC68302 - IMP. (Sheet 2)

The IMP is the first chip of the 302 family. It is an integrated multi-protocol processor, using the well known 68000 core.

## 3•5•3 MC68PM302 - Pchip. (Sheet 3)

The Pchip is integration of the original MC68302 - IMP, with a PCMCIA card logic.As the LC302, it lacks a third SCC and has less pins in total. Pins that were taken off, includes the 4 upper address lines (A20-A23), function code (F0-F2), arbitration logic (BR~, BG~, BGACK) and more. For more details please refer to the MC68PM302 user manual. There are 2 packages available for the Pchip. An 130 pin TQFP and 181 pin PGA package. The first has less functional pins and it is the low cost package you intended to put in your application. The PGA package is intended primary for development tools. The pins added in the PGA package only are - FC0 - FC2, FRZ~, AVEC~ and IAC.

## 3•5•4 The on board processors, in general

The pins of all 3 processors, are available unbuffered to the user, through the expansion and the logic analyzer connectors. The user can monitor the processor activity and connects the ADS to his own hardware application during its development stage. All processors' pins, are buffered from all devices on the ADS to minimize their load and to enable easy connection to the user hardware application.

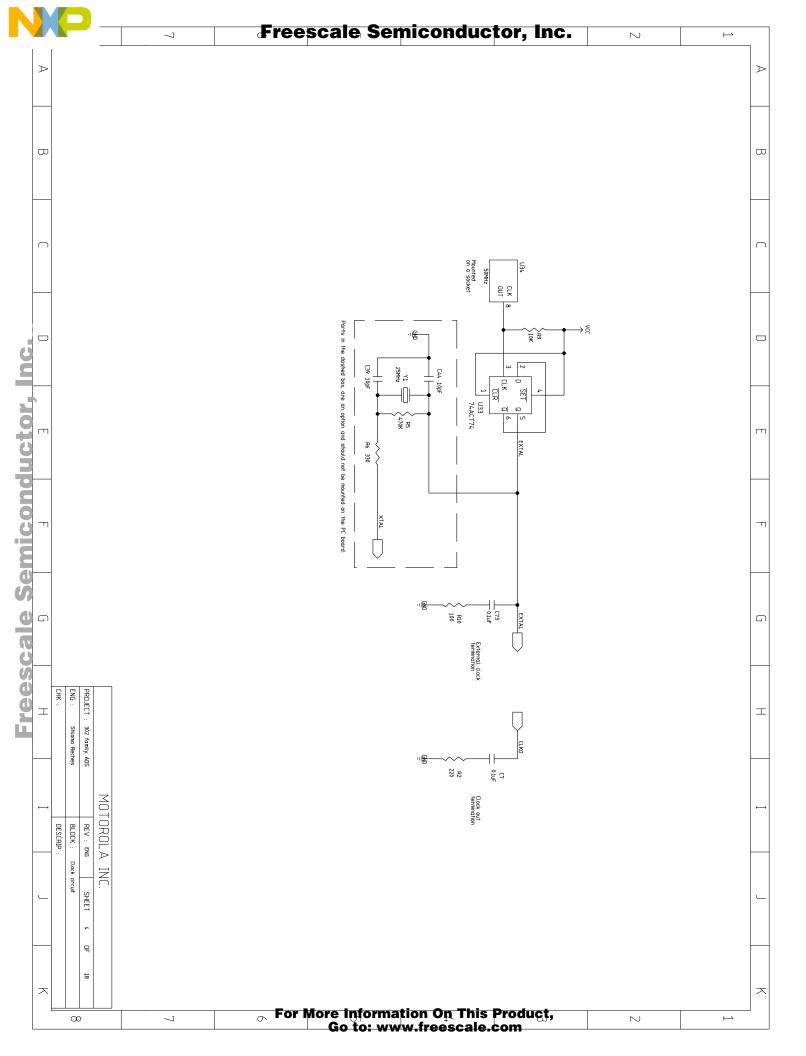

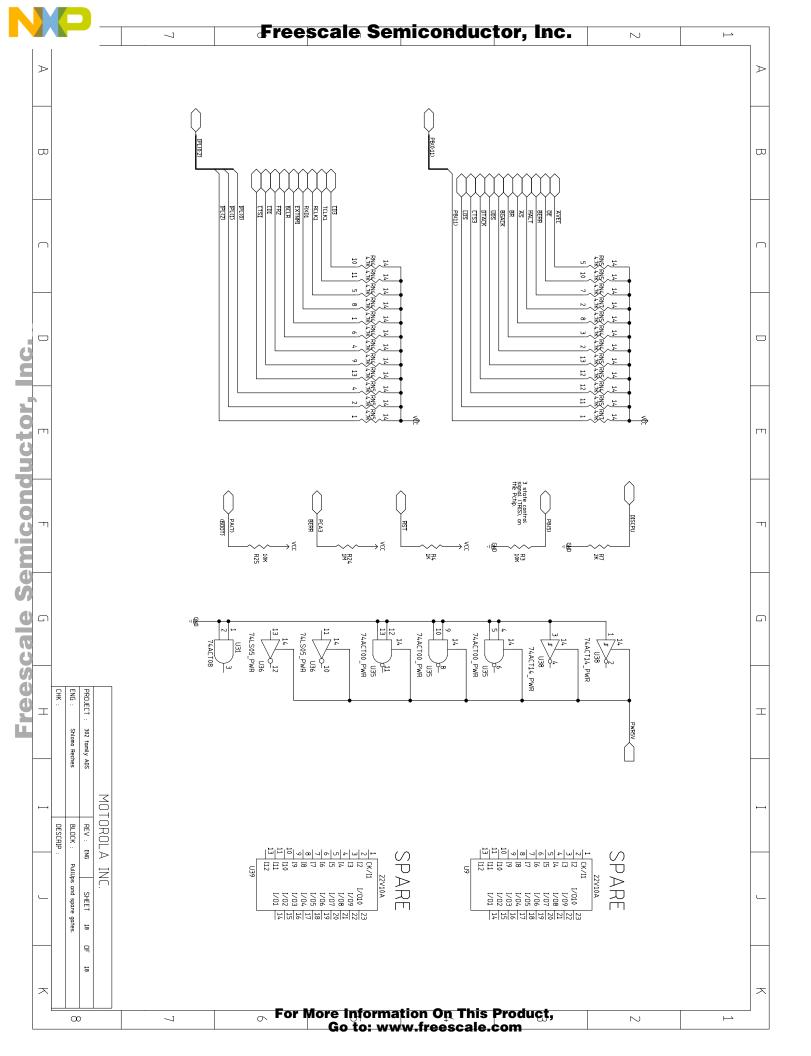

### 3•5•5 Processors' clock (sheet 4)

The system clock can be generated from one of 3 sources. On board clock oscillator, on board crystal circuit and an external clock source. The ADS is shipped with the first option. It consist of a clock oscillator running at twice the processor speed, followed by a divide by two flip flop. The divider assure a duty cycle of almost 50%. The clock oscillator device is mounted on a socket and can be easily replaced to get a different clock speed as requested. In case a crystal circuit or an external clock option is desired, please connect your Motorola dealer.

#### 3•5•6 Indicators and controls (sheet 5)

The ADS reset and abort, control buttons, each equipped with a debounce circuit to prevent oscillations. The board has run, halt power and pc power indicators.

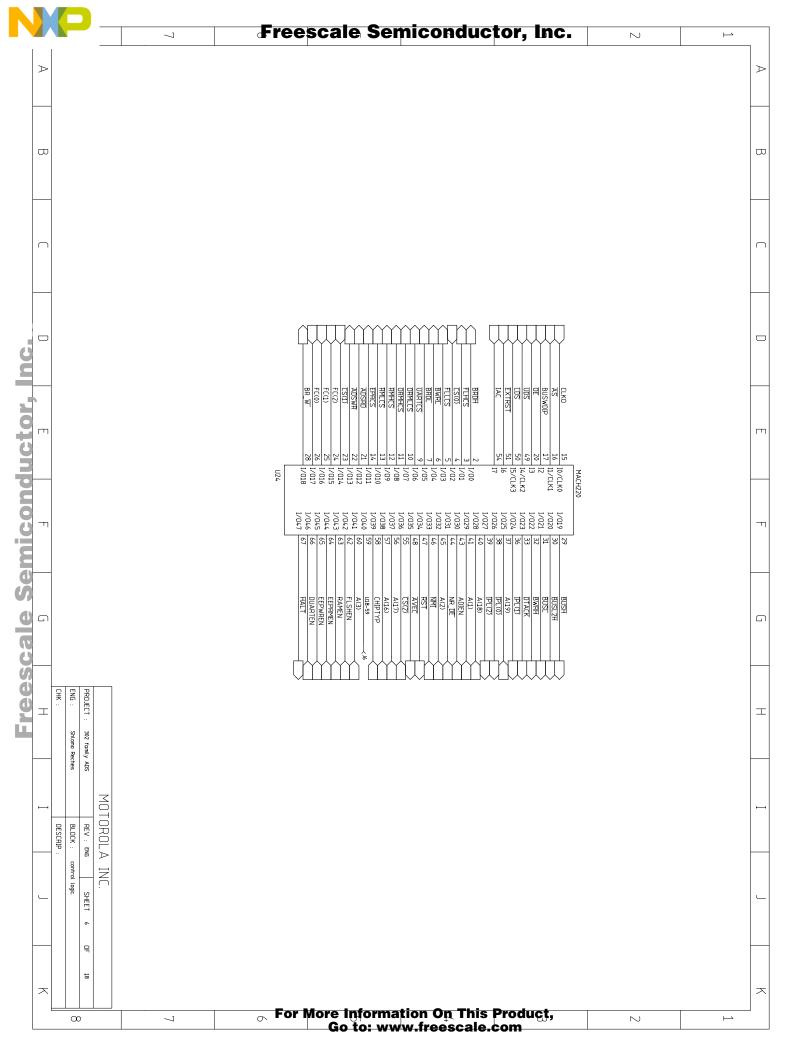

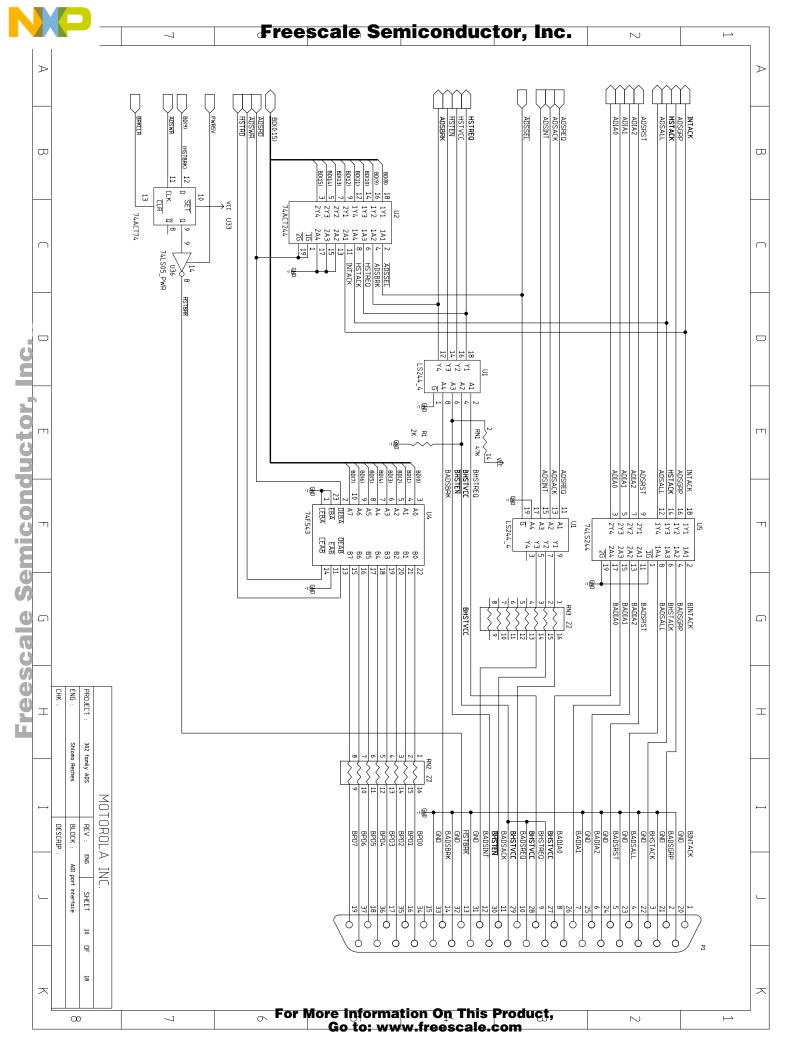

### 3•5•7 Control logic (sheet 6)

The IMP control logic is programmed into a MACH220 device. It consist of the following units:

- Chip select logic -

- Provides chip select for SRAM, FLASH, EEPROM, ADI, DUART. The chip selects are generated from the IMP CS0, CS1 and CS2. In the first two, the MACH reflect the signal as is. In the case of CS2, the MACH divide its range into three sections, 64K bytes each, for the ADI, EEPROM and the ADI.

- DTACK generator -

- DTACK is returned for all devices, accessed by the chip select logic, except the DUART, which has its own DTACK generator and the FLASH which has its CS0 default, for supplying an internal DTACK.

# Freescale Semiconductor, Inc. OPERATING INSTRUCTIONS

· Interrupt controller -

There are 3 level 7 (NMI) interrupt sources, on board. Abort switch, ADI abort and an external interrupt line. The interrupt controller, assert a level 7 interrupt with auto vector line and supports both IMP interrupt modes. Those modes are normal and dedicated. The interrupt controller, is reported with DUART output port bit 0, the interrupt operating mode. The debugger initializes the IMP with normal mode.

resources enable -

Resources like SRAM, FLASH, etc. can be taken out of the memory map (disabled) by this logic, by a user Dip switches selection.

wait state logic -

The wait state logic, delays a DTACK generation by several system clock out pulses, as programed into the MACH device for each resource.

Chip type selection -

The bus interface for the LC302 and the Pchip, is different from the original IMP. The first two has a glue less design concept and interface to external devices, through AS~, OE~, WEL~, WEH~ signal. The IMP, on contrary, uses AS~, DS~ and R/W~ signals. The MACH is used to interface those signals, according to the processor installed on board. (A selection between LC302/Pchip or IMP, is done by switch 10 of DIP switch set - DS2)

· buffers control -

This logic control data buffers in 16 and 8 bits bus width.

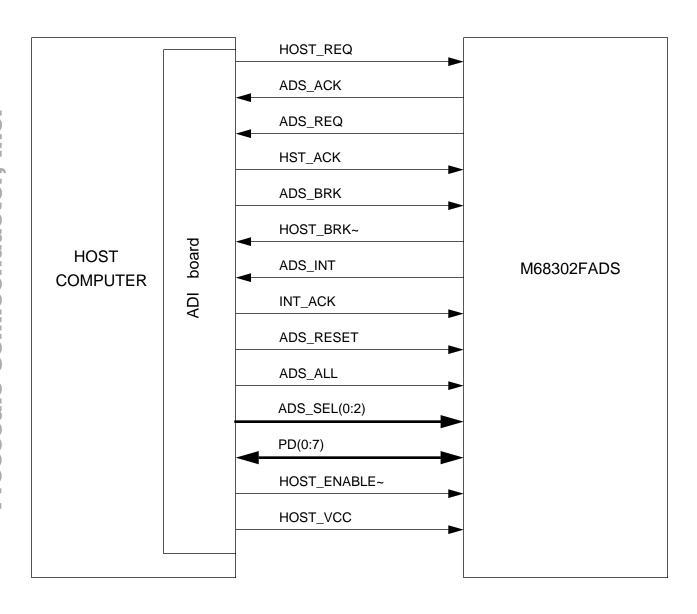

#### 3•5•8 ADI control logic (sheet 7)

A MACH100 device, controls the ADI interface. The ADI interface appears on sheet 10. (See APPENDIX B - ADI PORT HANDSHAKE DESCRIPTION, for more details on the ADI interface.

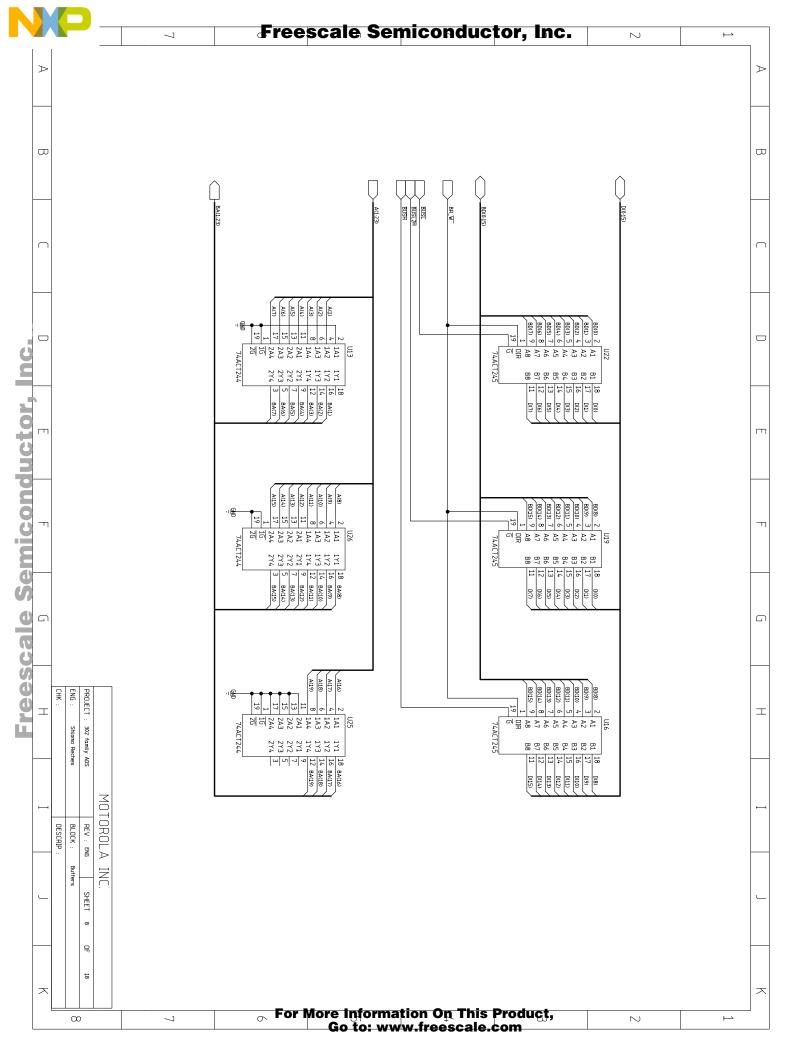

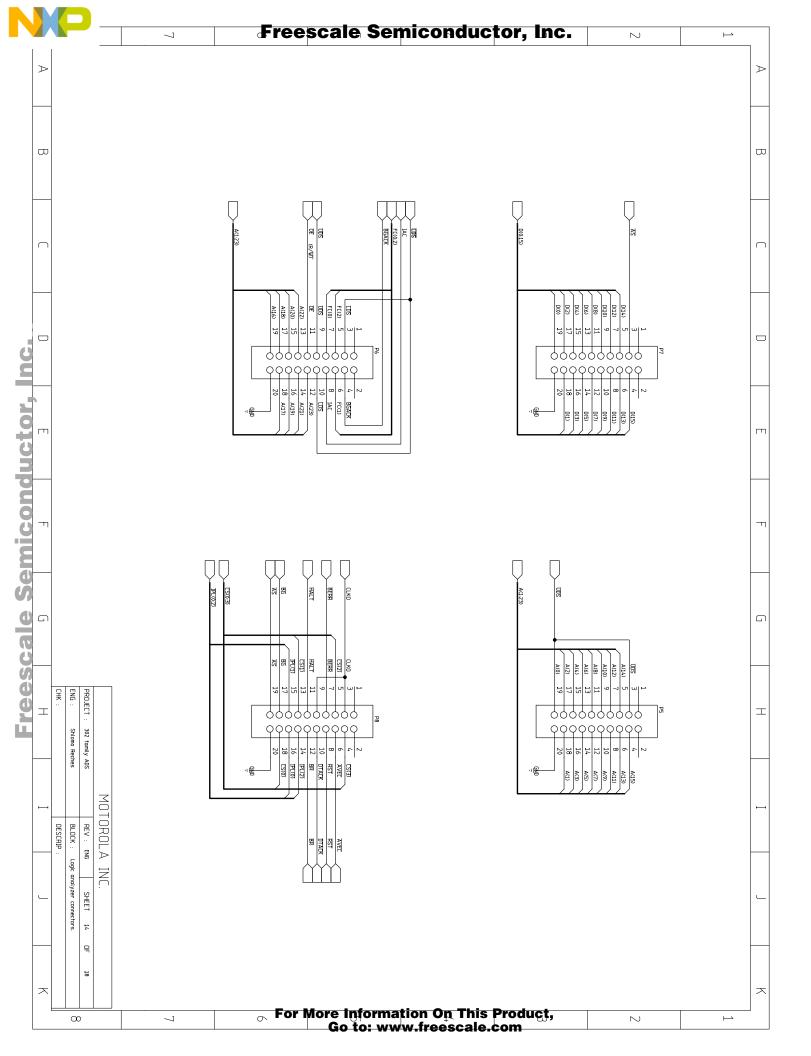

#### **3•5•9** Buffers (sheet 8)

To minimize signal load on the 302 processors pins, all address and data lines are buffered. The buffers support 8 bit bus width as well.

#### 3•5•10 SRAM (sheet 9)

The ADS is supplied with 512 Kilobyte of SRAM, which is implemented by four MCM6229A devices. The devices are organized as word (16 bits wide). The SRAM access time is 35 nsec.

Another bank of four MCM6229A devices can be soldered on the ADS to increase the SRAM memory space up to a 1 Mbyte.

#### 3•5•11 Flash Memory (sheet 9)

Two 512 Kilobyte Flash Memory devices, the 29F040, are used to form 1 Mbyte program storage memory. The devices are organized as word (16 bits wide). The Flash Memory access time is 90 nsec.

The Flash Memory devices are mounted on sockets, enable the user to load code, out of the board.

#### 3•5•12 EEPROM. (sheet 9)

The EEPROM used in the ADS is the AT28C16 device (250 nano-seconds access time, 2K x 8 bit). It appears as a static RAM for read or write cycle, with a write cycle extended up to 1 millisecond. During an internal write cycle, the 68302 must not access the EEPROM, but it may access any other device or performs a data polling on the EEPROM to detect end of a write cycle. The data polling feature of the EEPROM, enables the 68302 to detect the end of an internal write cycle. During an internal write cycle, the 302 processor, may read the last byte written to the EEPROM. If the internal write cycle is in process, then the result is the complement of the written data on bit 7, else the result is the true data. Only data pulling access, will return correct results from the EEPROM, during an internal write cycle. The AT28C16 has

internal hardware protection, against inadvertent writes to the EEPROM, that might happen during power up or power down time.

## 3•5•13 ADI port (sheet 10)

The ADI interface uses LS TTL drivers to communicate with the host. The ADI parallel port supplies parallel link from the ADS to various host computers. This port is connected via a 37 line cable to a special board called ADI (Application Development Interface) installed in the host computer. It is possible to connect the ADS board to an IBM-PC/XT/AT or to SUN-4 SPARC station, provided that they have an ADI board with the appropriate software drivers installed on them. Each ADS, has 8 possible slave addresses, for its ADI port, enabling up to 8 ADS boards to be connected to the same AD part. The ADS address is selected by the DS1 dip switch found on sheet 3. The ADI port connector P1 is a 37 pin, male, D type connector. (Same connector used for communicating with the on board command converter). The connection between the ADS and the host computer is by a 37 line flat cable, supplied with the ADI board. FIGURE 1-15 below shows the pin configuration of the connector.

## FIGURE 1-15 ADI Port Connector

| Gnd Gnd Gnd Gnd Gnd Gnd N.C. HOST_VCC HOST_VCC HOST_VCC HOST_DCC HOST_PD0 PD2 PD4 PD6 | 20<br>21<br>22<br>23<br>24<br>25<br>26<br>27<br>28<br>29<br>30<br>31<br>32<br>33<br>34<br>35<br>36<br>37 | 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16<br>17<br>18<br>19 | INT_ACK N.C. HST_ACK ADS_ALL ADS_RESET ADS_SEL2 ADS_SEL1 ADS_SEL0 HOST_REQ ADS_ACK ADS_INT HOST_BRK~ ADS_BRK N.C. PD1 PD3 PD5 PD7 |

|---------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

|---------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

#### 3.5.13.1 ADI Port Signal Description

In the list below, the directions 'I', 'O' and 'I/O' refer to the ADS board. (I.E. 'I' means input to the ADS)

•ADS SEL(0:2) -'I'

These three inputs determine the ADS board address. The address being set, would be the only one to which the board respond, when referenced by the host computer. Up to 8 boards can be addressed by one ADI port.

• ADS ALL -'I'

This input line is used to reset or abort program execution on all ADS development boards that are connected to the same ADI board. When this line is active, the IMP ADI and the on board command converter, are simultaneously referenced.

•HOST ENABLE~ -'I'

This line is always driven low by the ADI board. The ADS hardware uses this line to determine if a host is connected to the ADI port.

•ADS BRK -'I'

# Freescale Semiconductor, Inc. OPERATING INSTRUCTIONS

This line is used in conjunction with the addressing lines or with the ADS\_ALL line to generate a non-maskable interrupt (interrupt level 7) to the processor.

#### •ADS RESET -'I'

When a host is connected, this line is used in conjunction with the addressing lines or with the ADS ALL line to reset the ADS board.

#### •HOST REQ -'I'

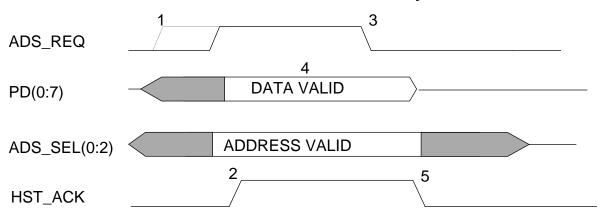

This signal initiates a host to ADS write cycle.

#### ADS ACK -'O'

This signal is the ADS response to the HOST\_REQ signal, indicating that the ADS board has detected the assertion of HOST\_REQ.

#### •ADS REQ -'O'

This signal initiates an ADS to host write cycle.

#### •HST ACK -'I'

This signal serves as the host's response to an ADS\_REQ signal.

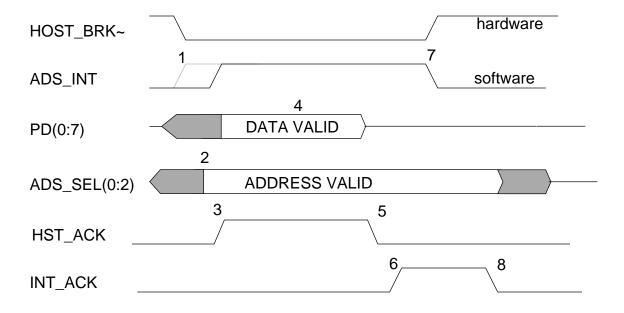

#### •HOST BRK~ -'O'

This open-collector signal, generates an interrupt to the host. This signal is common to all ADS boards that are connected to the same ADI.

#### •ADS INT -'O'

This line is polled by the host computer during its interrupt acknowledge cycle to determine which ADS board has generated an interrupt.

#### •INT ACK -'I'

This line is asserted by the host at the end of its interrupt acknowledge cycle. This signal is used by the ADS hardware to negate the HOST\_BRK~ signal. The ADS software, must negate the ADS\_INT signal upon detecting an assertion of INT\_ACK, to support the daisy-chain interrupt structure.

#### •HOST\_VCC -'I' (three lines)

These +5V power lines, are used by the ADI logic, to determine if a host computer is powered on. The ADS does not use these lines for power supply.

#### •PD(0:7) -'I/O'

These eight I/O lines are the parallel data bus. This bus is used to transmit and receive data from the host computer.

## 3•5•14 MC68681 DUART (sheet 11)

The MC68681 is DUART device connected to the 68302 part that provides the ADS with the following functions:

- 16 bit programmable counter/timer.

- ADI Port interface for the 68302 part.

- 2 RS-232 ports interface.

The debugger initializes port A of the DUART, to work with - 9600bps, 8 bit data, 1 stop bit and no parity.

#### 3•5•14•1 DUART Clock Source

The MC68681 uses a 3.6864Mhz crystal as its clock source, thus its communication rate, is independent of the system clock. The crystal is connected, between X1 and X2 pins, of the DUART.

#### 3•5•15 RS-232 serial ports. (sheet 11)

The RS-232 serial ports of the ADS are connected to channels A and B, of the MC68681 DUART. The ADS can be connected to a VT100 compatible terminal through the primary serial port (P2 connector), which is

the only one supported by the debugger. Both ports has a 9 pin, D-type, female connector as shown in FIGURE 1-8.

#### FIGURE 1-16 RS-232 Serial Ports Connector

P2 - Primery port (DCE port)

P2 - Secoundary port (DTE port)

## 3•5•15•1 Primary RS-232 port Signal Description

In the list below, the directions 'I', 'O' and 'I/O' refer to the ADS board. (I.E.'I' means input to the ADS)

- CD (O) Data Carrier Detect. This line is always asserted by the ADS.

- TX (O) Transmit Data.

- RX (I) Receive Data.

- DTR (I) Data Terminal Ready. This signal is used by the software in the ADS to detect if a terminal is connected to the ADS board.

- DSR (O) Data Set Ready. This line is always asserted by the ADS.

- RTS (I) Request To Send. This line is not connected in the ADS.

- CTS (O) Clear To Send. This line is always asserted by the ADS.

## 3•5•16 PCMCIA Connector (sheet 12)

The PCMCIA interface pins of the Pchip appears on an Sbus miniature connector, which is interfaced, into a PCMCIA port, trough an extender. The ADS does not use host PCMCIA power, but a relay on the ADS is used to power the ADS, upon power detection, on the PCMCIA connector pins. The user can choose to use this relay by a Dip switch selection.

<sup>\*</sup> The secondary port has the above signals with the opposite flow direction.

## **CHAPTER 4 - SUPPORT INFORMATION**

## 4•1 INTRODUCTION

This chapter provides the interconnection signals, parts list, and schematic diagrams of the M68302FADS board.

#### 4•2 INTERCONNECT SIGNALS

The M68302FADS board interconnects with external devices through the following connectors, listed in Table 2-8.

**Table 2-8 Board interconnection**

| Reference | Туре                                                                 | Function                  |  |

|-----------|----------------------------------------------------------------------|---------------------------|--|

| P1        | 37 pin, male D type connector                                        | ADI port                  |  |

| P2        | 9 pin, female D type connector                                       | RS232 terminal port (DCE) |  |

| P3        | 9 pin, female D type connector                                       | RS232 host port (DTE)     |  |

| P4        | 68 pin male, miniature Sbus connector                                | PCMCIA extender interface |  |

| P5 - P8   | 20 pin, male connectors, compatible with HP logic analyzer connector | logic analyzer connectors |  |

| P11       | 96 pin, male DIN connector                                           | logic analyzer connectors |  |

| P9, P12   | 96 pin, female DIN connector                                         | expansion port connectors |  |

| P10       | 3 pin power connector                                                | 5v power supply input     |  |

# 4•2•1 Connector P1 Interconnect Signals

P1 is a 37 pin, male D type connector. It is the ADI port of the M68302FADS. P1 signals, are listed in Table 2-9. (In the following table, input and output signals, refer to the ADS board)

**Table 2-9 Connector P1 Interconnect Signals**

| Pin No. | Signal Name  | Description                                                                                  |  |  |

|---------|--------------|----------------------------------------------------------------------------------------------|--|--|

| 1       | INT_ACK      | Interrupt Acknowledge input signal.                                                          |  |  |

| 2       | -            | Not connected                                                                                |  |  |

| 3       | HST_ACK      | Host Acknowledge input signal.                                                               |  |  |

| 4       | ADS_ALL      | ADS All, input signal.                                                                       |  |  |

| 5       | ADS_RESET    | ADS Reset input signal.                                                                      |  |  |

| 6       | ADS_SEL2     | ADS Select 2, input signal. (ADI address bit 2)                                              |  |  |

| 7       | ADS_SEL1     | ADS Select 1, input signal. (ADI address bit 1)                                              |  |  |

| 8       | ADS_SEL0     | ADS Select 0, input signal. (ADI address bit 0)                                              |  |  |

| 9       | HOST_REQ     | HOST Request, input signal.                                                                  |  |  |

| 10      | ADS_REQ      | ADS Request, output signal.                                                                  |  |  |

| 11      | ADS_ACK      | ADS Acknowledge, output signal.                                                              |  |  |

| 12      | ADS_INT      | ADS Interrupt, output signal.                                                                |  |  |

| 13      | HOST_BRK~    | HOST Break open collector, output signal.                                                    |  |  |

| 14      | ADS_BRK      | ADS Break, input signal.                                                                     |  |  |

| 15      | -            | Not connected                                                                                |  |  |

| 16      | PD1          | Bit 1 of the ADI port data bus                                                               |  |  |

| 17      | PD3          | Bit 3 of the ADI port data bus                                                               |  |  |

| 18      | PD5          | Bit 5 of the ADI port data bus                                                               |  |  |

| 19      | PD7          | Bit 7 of the ADI port data bus                                                               |  |  |

| 20 - 25 | GND          | board common ground                                                                          |  |  |

| 26      | -            | Not connected. The host supplies +12V on this pin, but it is not connected on the M68302FADS |  |  |

| 27 - 29 | HOST_VCC     | HOST VCC input (+5V). The M68302FADS does not use these inputs for power supply.             |  |  |

| 30      | HOST_ENABLE~ | HOST Enable, input signal.                                                                   |  |  |

| 31 - 33 | GND          | Ground signal of the M68302FADS                                                              |  |  |

| 34      | PD0          | Bit 0 of the ADI port data bus                                                               |  |  |

| 35      | PD2          | Bit 2 of the ADI port data bus                                                               |  |  |

| 36      | PD4          | Bit 4 of the ADI port data bus                                                               |  |  |

| 37      | PD6          | Bit 6 of the ADI port data bus                                                               |  |  |

## 4•2•2 Connector P2 Interconnect Signals

P2 is a 9 pin, female D type connector. It is the RS232 serial port of the M68302FADS. P2 signals are listed in Table 2-9. (In the following table, input and output signals, refer to the ADS board)

Table 2-10 Connector P2, Interconnect Signals

| Pin No. | Signal Name | Description                                             |

|---------|-------------|---------------------------------------------------------|

| 1       | CD          | Carrier Detect output.                                  |

| 2       | TX          | Transmit Data output.                                   |

| 3       | RX          | Receive Data input.                                     |

| 4       | DTR         | Data Terminal Ready input.                              |

| 5       | GND         | Ground signal of the ADS.                               |

| 6       | DSR         | Data Set Ready output.                                  |

| 7       | RTS (N.C.)  | Request To Send. This line is not connected in the ADS. |

| 8       | CTS         | Clear To Send output.                                   |

| 9       | -           | Not connected                                           |

## 4•2•3 Connector P3 Interconnect Signals

P3 is a 9 pin D type female connector. It is a host secondary RS232 port. Signals are listed in Table 2-13.

**Table 2-11 Connector P3, Interconnect Signals**

| Pin No. | Signal Name | Description                                                |  |

|---------|-------------|------------------------------------------------------------|--|

| 1       | TX          | Transmit Data input.                                       |  |

| 2       | -           | Not connected                                              |  |

| 3       | RX          | Receive Data output.                                       |  |

| 4       | DTR         | Data Terminal Ready output.                                |  |

| 5       | GND         | Ground signal of the ADS.                                  |  |

| 6       | DSR         | Data Set Ready input.                                      |  |

| 7       | RTS         | Request To Send output.                                    |  |

| 8       | CTS (N.C)   | Clear To Send input. This line is not connected in the ADS |  |

| 9       | -           | Not connected                                              |  |

## 4•2•4 Connector P4 interconnect signals

P4, is 68 pin, SBUS type connector. It is the PCMCIA extender port. P4 signals are listed in Table 2-12.

Table 2-12 Connector P4 interconnect signals

| Pin No. | Signal name | I/O | Description         |

|---------|-------------|-----|---------------------|

| 1       | GND         |     | Board common ground |

| 2       | D3          | I/O | PCMCIA data bit 3   |

| 3       | D4          | I/O | PCMCIA data bit 4   |

| 4       | D5          | I/O | PCMCIA data bit 5   |

| 5       | D6          | I/O | PCMCIA data bit 6   |

**Table 2-12 Connector P4 interconnect signals**

| Pin No. | Signal name | I/O | Description                           |

|---------|-------------|-----|---------------------------------------|

| 6       | D7          | I/O | PCMCIA data bit 7                     |

| 7       | CE1~        | ı   | Card enable 1                         |

| 8       | A10         | ı   | PCMCIA address bit 10                 |

| 9       | OE~         | l   | PCMCIA output enable                  |

| 10      | A11         | l   | PCMCIA address bit 11                 |

| 11      | A9          | l   | PCMCIA address bit 9                  |

| 12      | A8          | I   | PCMCIA address bit 8                  |

| 13      | A13         | I   | PCMCIA address bit 13 (Not supported) |

| 14      | A14         | I   | PCMCIA address bit 14 (Not supported) |

| 15      | WE~         | I   | PCMCIA write enable                   |

| 16      | RDY         | 0   | PCMCIA ready output.                  |

| 17      | VCC         | -   | Host power.                           |

| 18      | VPP1        | -   | Programming voltage (Not supported)   |

| 19      | A16         | l   | PCMCIA address bit 16 (Not supported) |

| 20      | A15         | l   | PCMCIA address bit 15 (Not supported) |

| 21      | A12         | l   | PCMCIA address bit 12 (Not supported) |

| 22      | A7          | l   | PCMCIA address bit 7                  |

| 23      | A6          | ı   | PCMCIA address bit 6                  |

| 24      | A5          | l   | PCMCIA address bit 5                  |

| 25      | A4          | l   | PCMCIA address bit 4                  |

| 26      | A3          | ı   | PCMCIA address bit 3                  |

| 27      | A2          | l   | PCMCIA address bit 2                  |

| 28      | A1          | l   | PCMCIA address bit 1                  |

| 29      | A0          | l   | PCMCIA address bit 0                  |

| 30      | D0          | I/O | PCMCIA data bit 0                     |

| 31      | D1          | I/O | PCMCIA data bit 1                     |

| 32      | D2          | I/O | PCMCIA data bit 2                     |

| 33      | IOIS16~     | 0   | I/O is 16. (Set by on board jumper)   |

| 34      | GND         | -   | Board common ground                   |

| 35      | GND         | -   | Board common ground                   |

| 36      | CD1~        | 0   | PCMCIA card detect 1 (Grounded)       |

| 37      | D11         | I/O | PCMCIA data bit 11                    |

| 38      | D12         | I/O | PCMCIA data bit 12                    |

| 39      | D13         | I/O | PCMCIA data bit 13                    |

| 40      | D14         | I/O | PCMCIA data bit 14                    |

| 41      | D15         | I/O | PCMCIA data bit 15                    |

| 42      | CE2~        | l   | PCMCIA card enable 2                  |

| 43      | RFRSH       |     | Not supported                         |

| 44      | IORD        | l   | PCMCIA I/O read                       |

| 45      | IOWR        |     | PCMCIA I/O write                      |

| Table 2-12 Connector | P4 | interconnect | signals |

|----------------------|----|--------------|---------|

|----------------------|----|--------------|---------|

| Pin No. | Signal name | I/O | Description                     |

|---------|-------------|-----|---------------------------------|

| 46      | A17         | 1   | PCMCIA address bit 17           |

| 47      | A18         | 1   | PCMCIA address bit 18           |

| 48      | A19         | 1   | PCMCIA address bit 19           |

| 49      | A20         | I   | PCMCIA address bit 20           |

| 50      | A21         | I   | PCMCIA address bit 21           |

| 51      | VCC         | -   | Host VCC                        |

| 52      | VPP2        | -   | Not supported                   |

| 53      | A22         | I   | PCMCIA address bit 22           |

| 54      | A23         | I   | PCMCIA address bit 23           |

| 55      | A24         | I   | PCMCIA address bit 24           |

| 56      | A25         | I   | PCMCIA address bit 25           |

| 57      | RFU         |     | Reserved for future use         |

| 58      | RST         | I   | PCMCIA reset                    |

| 59      | WAIT        | 0   | PCMCIA wait                     |

| 60      | IPACK       | 0   | Input port ack                  |

| 61      | REG         | I   | Reg memory attribute            |

| 62      | SPKR        | -   | Not supported                   |

| 63      | SCHG~       | I   | PCMCIA status changed           |

| 64      | D8          | I/O | PCMCIA data bit 8               |

| 65      | D9          | I/O | PCMCIA data bit 9               |

| 66      | D10         | I/O | PCMCIA data bit 10              |

| 67      | CD2~        | 0   | PCMCIA card detect 2 (Grounded) |

| 68      | GND         | -   | Board common ground             |

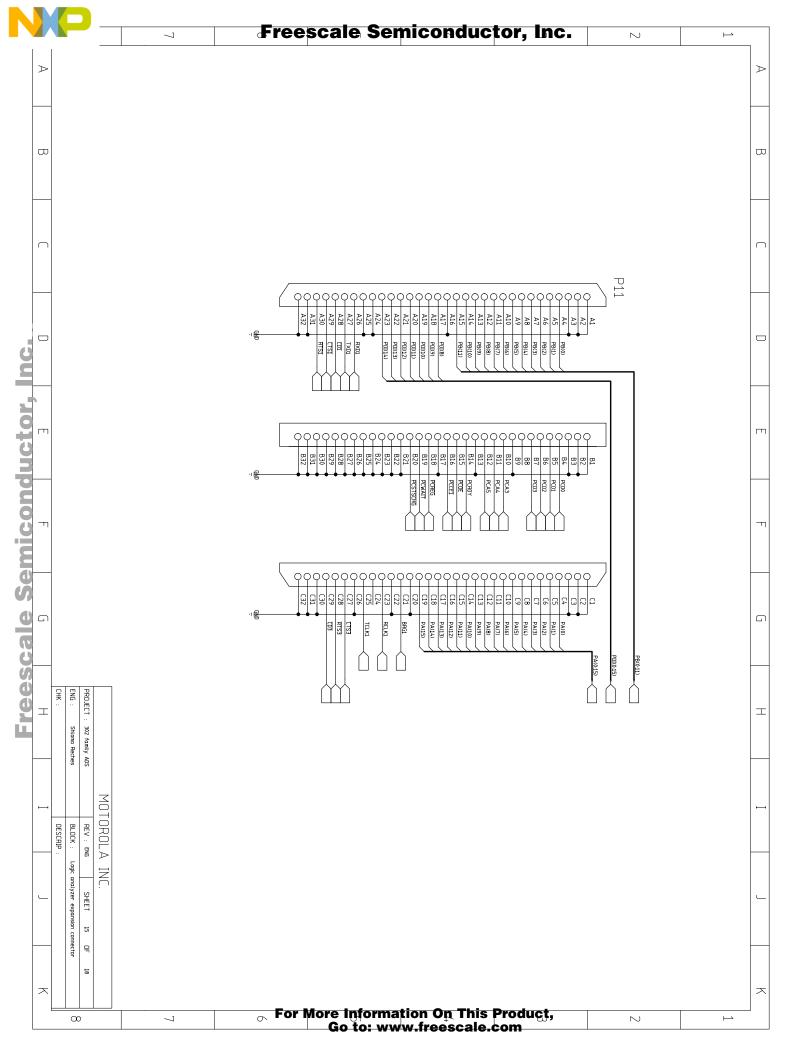

## 4•2•4•1 Connector P5 Interconnect Signals

P10 is a dual row, 20 pin, male connector. The upper address bus and control signals of the processor, appear on this connector, for easy monitoring by a logic analyzer. P5 connector signals are listed in Table 2-13.

Table 2-13 P5 connector interconnect signals

| Pin NO | Signal name | Description                         |  |

|--------|-------------|-------------------------------------|--|

| 1      | NC          | No connection                       |  |

| 2      | NC          | No connection                       |  |

| 3      | WEH~/UDS~   | write enable high/upper data strobe |  |

| 4      | A15         | address line 15                     |  |

| 5      | A14         | address line 14                     |  |

| 6      | A13         | address line 13                     |  |

| 7      | A12         | address line 12                     |  |

| 8      | A11         | address line 11                     |  |

| 9      | A10         | address line 10                     |  |

| 10     | A9          | address line 9                      |  |

Table 2-13 P5 connector interconnect signals

| Pin NO | Signal name | Description                         |

|--------|-------------|-------------------------------------|

| 11     | A8          | address line 8                      |

| 12     | A7          | address line 7                      |

| 13     | A6          | address line 6                      |

| 14     | A5          | address line 5                      |

| 16     | A4          | address line 4                      |

| 16     | A3          | address line 3                      |

| 17     | A2          | address line 2                      |

| 18     | A1          | address line 1                      |

| 19     | WEH~/UDS~   | write enable high/upper data strobe |

| 20     | GND         | Board common ground                 |

# 4•2•5 Connector P6 Interconnect Signals

P9 is a dual row, 20 pin, male connector. The upper address bus and bus control signal of the processor, appear on this connector, for easy monitoring by a logic analyzer.P9 connector signals are listed in Table 2-14.

**Table 2-14 P6 connector interconnect signals**

| Pin NO. | Signal name | Description                         |

|---------|-------------|-------------------------------------|

| 1       | NC          | No connection                       |

| 2       | NC          | No connection                       |

| 3       | WEL~/LDS~   | write enable low/lower data storbe  |

| 4       | BGACK~      | bus grant acknowledge               |

| 5       | FC2         | function code 2                     |

| 6       | FC1         | function code 1                     |

| 7       | FC0         | function code 0                     |

| 8       | IAC         | internal access                     |

| 9       | WEH~/UDS~   | write enable high/upper data strobe |

| 10      | WEL~/LDS~   | write enable low/lower data strobe  |

| 11      | OE~/R/W~    | output enable/read write            |

| 12      | A23         | address line 23                     |

| 13      | A22         | address line 22                     |

| 14      | A21         | address line 21                     |

| 15      | A20         | address line 20                     |

| 16      | A19         | address line 19                     |

| 17      | A18         | address line 18                     |

| 18      | A17         | address line 17                     |

| 19      | A16         | address line 16                     |

| 20      | GND         | Board common ground                 |

## 4•2•6 Connector P7 interconnect Signals

P7 is a dual row, 20 pin, male connector. The processor data bus appears on this connector, for easy monitoring by a logic analyzer. P7 signals are listed in Table 2-16.

Table 2-15 P7 interconnect signals

| Pin NO | Signal name | Description         |

|--------|-------------|---------------------|

| 1      | NC          | No connection       |

| 2      | NC          | No connection       |

| 3      | AS~         | address strobe      |

| 4      | D15         | data line 15        |

| 5      | D14         | data line 14        |

| 6      | D13         | data line 13        |

| 7      | D12         | data line 12        |

| 8      | D11         | data line 11        |

| 9      | D10         | data line 10        |

| 10     | D9          | data line 9         |

| 11     | D8          | data line 8         |

| 12     | D6          | data line 7         |

| 13     | D7          | data line 6         |

| 14     | D5          | data line 5         |

| 15     | D4          | data line 4         |

| 16     | D3          | data line 3         |

| 17     | D2          | data line 2         |

| 18     | D1          | data line 1         |

| 19     | D0          | data line 0         |

| 20     | GND         | Board common ground |

## 4•2•7 Connector P8 interconnect Signals

P8 is a dual row, 20 pin, male connector. The processor data bus appears on this connector, for easy monitoring by a logic analyzer. P8 signals are listed in Table 2-16

Table 2-16 P8 interconnect signals

| Pin NO | Signal name | Description        |

|--------|-------------|--------------------|

| 1      | NC          | No connection      |

| 2      | NC          | No connection      |

| 3      | CLKO        | clock out          |

| 4      | CS3~        | chip select line 3 |

| 5      | CS2~        | chip select line 2 |

| 6      | AVEC~       | auto vector        |

| 7      | BERR~       | bus error          |

| 8      | RST~        | reset              |

## Table 2-16 P8 interconnect signals

| Pin NO | Signal name | Description                |

|--------|-------------|----------------------------|

| 9      | CLKO        | clock out                  |

| 10     | DTACK~      | data transfer acknowledge  |

| 11     | HALT~       | halt control               |

| 12     | BR~         | bus request                |

| 13     | CS1~        | chip select line 1         |

| 14     | IPL2~       | interrupt priority level 2 |

| 15     | IPL1~       | interrupt priority level 1 |

| 16     | IPL0~       | interrupt priority level 0 |

| 17     | BG~         | bus grant                  |

| 18     | CS0~        | chip select line 0         |

| 19     | AS~         | address strobe             |

| 20     | GND         | Board common ground        |

## 4•2•8 Connector P9 interconnect signals

P9 is a 3 row, 96 pin female DIN connector. All processors signals, are routed directly to P9 and P12, for user hardware applications. P9 signals are listed in Table 2-17.

## **Table 2-17 Connector P9 interconnect signals**

| Pin NO | Signal name | Description              |

|--------|-------------|--------------------------|

| A1     | GND         | Board common ground      |

| A2     | GND         | Board common ground      |

| А3     | GND         | Board common ground      |

| A4     | A7          | address line bit 7       |

| A5     | A4          | address line bit 4       |

| A6     | A9          | address line bit 9       |

| A7     | A14         | address line bit 14      |

| A8     | A19         | address line bit 19      |

| A9     | A16         | address line bit 16      |

| A10    | A21         | address line bit 21      |

| A11    | FC2         | function code bit 2      |

| A12    | RMC~        | read modify write cycle  |

| A13    | CS3~        | chip select 3            |

| A14    | PB3         | port B bit 3             |

| A15    | IAC         | internal access          |

| A16    | GND         | common                   |

| A17    | PB1         | port B bit 1             |

| A18    | FC1         | function code bit 1      |

| A19    | D14         | data bit 14              |

| A20    | D11         | data bit 11              |

| A21    | OE~/R/W~    | output enable/read write |

**Table 2-17 Connector P9 interconnect signals**

| Pin NO | Signal name | Description                         |

|--------|-------------|-------------------------------------|

| A22    | D6          | data bit 6                          |

| A23    | DTACK~      | data transfer acknowledge           |

| A24    | BERR~       | bus error                           |

| A25    | IPL1~       | interrupt priority level 1          |

| A26    | IPL2~       | interrupt priority level 1          |

| A27    | PA15        | port A bit 15                       |

| A28    | BGACK~      | bus grant acknowledge               |

| A29    | FRZ~        | freeze                              |

| A30    | PA13        | port A bit 13                       |

| A31    | BG~         | bus grant                           |

| A32    | VCC         | board common +5V supply             |

| B1     | GND         | Board common ground                 |

| B2     | A1          | address bit 1                       |

| B3     | GND         | Board common ground                 |

| B4     | A2          | address bit 2                       |

| B5     | A5          | address bit 5                       |

| B6     | A10         | address bit 10                      |

| B7     | A15         | address bit 15                      |

| B8     | A12         | address bit 12                      |

| B9     | A17         | address bit 17                      |

| B10    | A22         | address bit 22                      |

| B11    | FC0         | function code 0                     |

| B12    | CS0~        | chip select bit 0                   |

| B13    | PB11        | port B bit 11                       |

| B14    | PB10        | port B bit 10                       |

| B15    | PB2         | port B bit 2                        |

| B16    | PB8         | port B bit 8                        |

| B17    | PB4         | port B bit 4                        |

| B18    | WEH~/UDS~   | write enable high/upper data strobe |

| B19    | D10         | data bit 10                         |

| B20    | D13         | data bit 13                         |

| B21    | AS~         | address strobe                      |

| B22    | D9          | data bit 9                          |

| B23    | D2          | data bit 2                          |

| B24    | AVEC~       | auto vector                         |

| B25    | IPL0~       | interrupt priority 0                |

| B26    | BR~         | bus request                         |

| B27    | EXTAL       | external clock input/crystal        |

| B28    | RST~        | reset                               |

| B29    | PA12        | port A bit 12                       |

**Table 2-17 Connector P9 interconnect signals**

| Pin NO | Signal name | Description                        |

|--------|-------------|------------------------------------|

| B30    | D3          | data bit 3                         |

| B31    | busw        | bus width                          |

| B32    | VCC         | board common +5V supply            |

| C1     | GND         | board common ground                |

| C2     | GND         | board common ground                |

| C3     | GND         | board                              |

| C4     | A3          | address bit 3                      |

| C5     | A6          | address bit 6                      |

| C6     | A11         | address bit 11                     |

| C7     | A8          | address bit 8                      |

| C8     | A13         | address bit 13                     |

| C9     | A18         | address bit 18                     |

| C10    | A23         | address bit 23                     |

| C11    | A20         | address bit 20                     |

| C12    | CS1~        | chip select 1                      |

| C13    | CS2~        | chip select 2                      |

| C14    | PB6         | port B bit 6                       |

| C15    | PB5         | port B bit 5                       |

| C16    | PB7         | port B bit 7                       |

| C17    | PB9         | port B bit 9                       |

| C18    | PB0         | port B bit 0                       |

| C19    | D15         | data bit 15                        |

| C20    | D12         | data bit 12                        |

| C21    | WEL~/LDS    | write enable low/lower data strobe |

| C22    | D8          | data bit 8                         |

| C23    | D7          | data bit 7                         |

| C24    | D1          | data bit 1                         |

| C25    | CLKO        | clock out                          |

| C26    | D5          | data bit 5                         |

| C27    | BCLR~       | bus clear                          |

| C28    | D4          | data bit 4                         |

| C29    | D0          | data bit 0                         |

| C30    | HALT~       | halt control                       |

| C31    | PA14        | port A bit 14                      |

| C32    | VCC         | board common +5V supply            |

## 4•2•9 Connector P10 Interconnect Signals

P18 is 3 pin connector for 5v power supply. The connector is supplied with 3 pin plug for convenient

connection to the power supply. P10 connector signals, are listed in Table 2-9.

**Table 2-18 Connector P10 interconnect Signals**