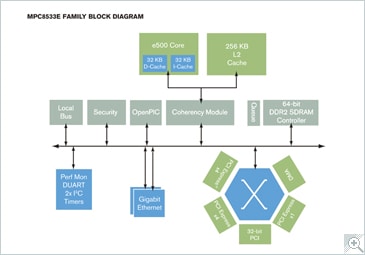

The MPC8533E PowerQUICC® III communications processor

offers high level of integration and performance for Ethernet-only or PCIe

interworking applications, such as enterprise networking and advanced

multi-function printer (MFP) and imaging applications.

- Includes

enhanced peripherals, an integrated security engine, and a wide range of

high-speed connectivity options

- Supports complex,

computationally demanding control plane processing tasks

- Comes

optimized for power sensitive applications

- Provides a flexible

SoC platform to accelerate time-to-market

- Simplifies board

design

Access to the

errata document for this device requires an NDA. Contact your local

NXP® Sales Office or NXP Authorized Distributor.