## **Freescale Semiconductor**

**Application Note**

Document Number: AN3445

Rev. 0, 10/2007

# Migrating from e300- to e500-Based Integrated Devices

by Jerry Young

Networking and Multimedia Group

Freescale Semiconductor, Inc.

Austin, TX

This application note outlines general, high-level, architectural differences between the e300 and e500 family processors. It does not address microarchitectural differences, such as the sizes of caches, bus architecture, or instruction pipeline design. It does not attempt to describe all differences among the members of these two families of processors, but is intended as a general guideline for programmers and system designers who are assessing the efforts required in migrating to e500-based devices.

For specific details, refer to the user documents for the respective devices.

#### Contents

| 1. | The e300, the e500, and Changes to the            |

|----|---------------------------------------------------|

|    | Architecture Definition                           |

| 2. | Differences between e300 and e500 Cores: Overview |

| 3. | Power Architecture Details                        |

| 4. | Instruction Model                                 |

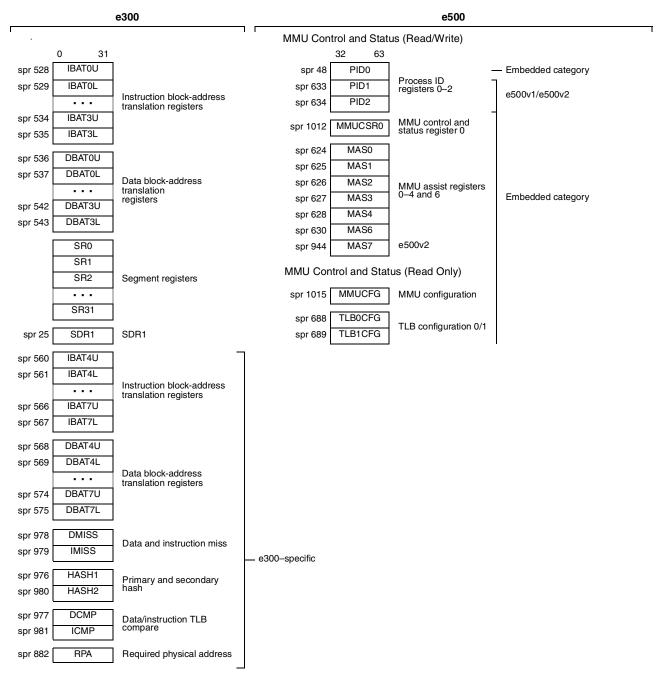

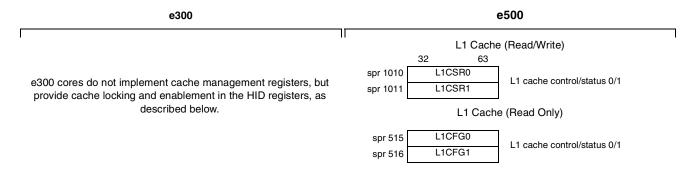

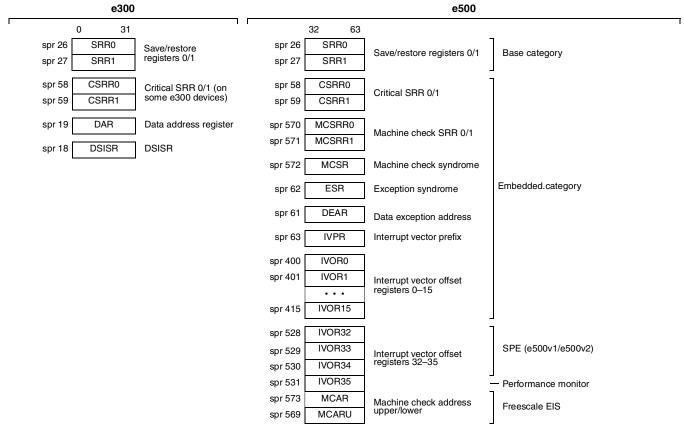

| 5. | Register Model                                    |

| 6. | Interrupt Model                                   |

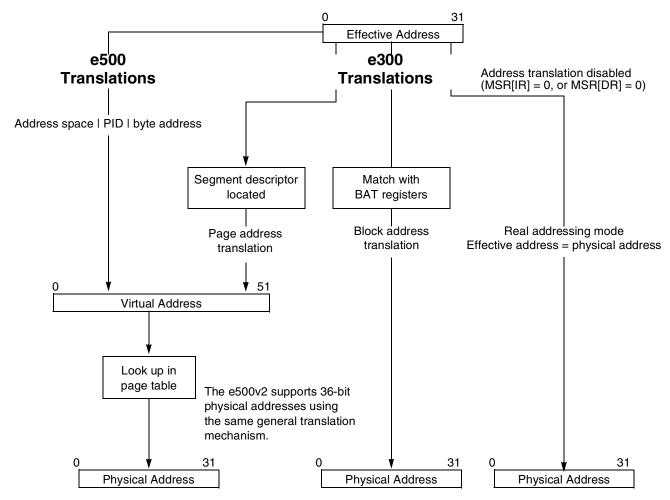

| 7. | Memory Management Unit (MMU) Model 42             |

| 8. | Revision History                                  |

The e300, the e500, and Changes to the Architecture Definition

## 1 The e300, the e500, and Changes to the Architecture Definition

This section describes the changes to the architectural specifications especially as they relate to the e300 and e500 processor families.

#### **NOTE**

The term 'PowerPC<sup>TM</sup> architecture' has come to refer strictly to the original architecture definition for desktop processors that is implemented on the e300, e600, and others and sometimes is referred to as the classic or AIM (Apple, IBM, Motorola) version of the architecture.

The term 'Power ISA<sup>TM</sup>' refers to the current architecture specification that is implemented on e500 cores.

Both the PowerPC architecture and the Power ISA are part of the more general Power Architecture<sup>TM</sup> model, as described below.

Many of the differences between the e300 and e500 processor families exist because they were designed to somewhat different versions of the PowerPC architecture, as follows:

- The e300 family (which are based on the original 603 design) was designed to the original PowerPC architecture definition. The functionality of the e300 family cores is described in the following Freescale documents:

- The *e300 Power Architecture*<sup>TM</sup> *Core Family Reference Manual*, which describes functionality specific to the e300.

- The *Programming Environments Manual for 32-Bit Implementations of the PowerPC*<sup>TM</sup> *architecture* (referred to as the PEM), which describes the functionality common to all PowerPC devices.

- The e500v1 and e500v2 processors are designed to what was originally the PowerPC Book E architecture and Freescale's embedded implementation standards (EIS). Together, they replaced many of the original architecture's desktop-centered features (most notably, operating system-level features such as the MMU and interrupt models, as well as true little-endian as part of a storage model in which byte ordering is configured on a per-page basis) with features more suited to the embedded environment for which Book E was intended. The functionality of the e500 family cores is described in the following Freescale documents:

- The e500 Power Architecture<sup>TM</sup> Core Family Reference Manual, which describes functionality specific to the e500 cores.

- The *EREF*: a *Programmer's Reference Manual for Freescale Embedded Devices*, which describes the functionality common to all Freescale Power ISA embedded devices.

Note that in this document, references to the e500 refer to all e500 devices. Any device-specific differences are noted.

#### NOTE

For any of the cores referenced in this document, resources that may be defined at the processor level may not be fully implemented, or implemented at all, in the system-on-a-chip (SoC) device that integrates the core. Also, in some cases, and in particular with register fields, functionality may be defined at a general level by the architecture and core reference manuals, and more specifically by the SoC. Because of such differences, it is important to consult the core register summary chapter in the reference manual for the integrated device.

Both families include many extensions to the architecture versions to which they were designed. In particular, the e300 family offered a software-based alternative to the more hardware-intensive MMU definition of the operating environment architecture (OEA, or Book III) of the original architecture. Book E and the EIS offered an architected alternative to such features as well as many architectural extensions, such as the performance monitor, cache management features, and the signal processing engine (SPE). The SPE, implemented on e500v1 and e500v2, defines an extensive set of 64-bit, two-element vector instructions and includes a set of floating-point instructions as an alternative to the one defined by the PowerPC architecture. To facilitate such special-purpose extensions, Book E introduced the concept of auxiliary processing units (APUs) and allocated resources such as instruction opcode space and SPRs that encouraged the development of such functionality.

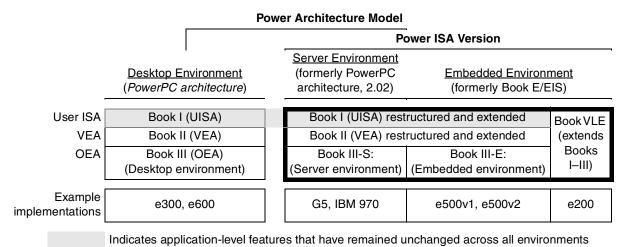

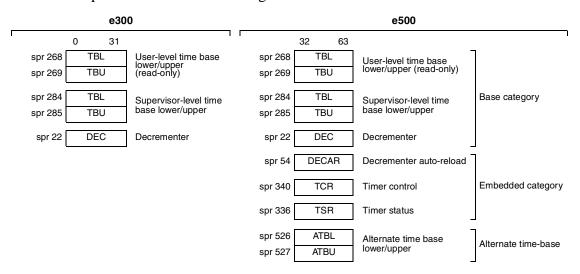

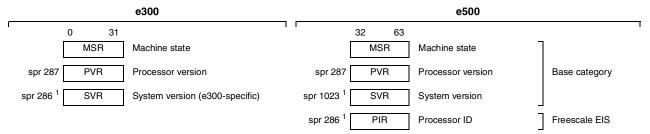

Since the restructuring of the architecture (now referred to collectively as the Power Architecture model), most of those APUs are now a formal part of the portion of the architecture designated for embedded devices and published in the Power ISA specification, released in 2006. Figure 1 shows the relationship between the different environments. Note that the e300 family is part of the Power Architecture model; the e500 family is part of the embedded environment of the Power ISA.

It is especially important to note that, although the structure of the architecture has changed considerably, most of the functionality changes have been relegated to operating system—level features (such as the MMU and interrupt models described above). As Figure 1 illustrates, the application-level programming model, that is the base set of instructions and registers, remains consistent across the e300, e500, and all other Power Architecture devices.

Figure 1. Power Architecture Relationships

Migrating from e300- to e500-Based Integrated Devices, Rev. 0

#### Differences between e300 and e500 Cores: Overview

The Power ISA extends the modularity of the layered architecture (Books I through III) by breaking the functionality of the architecture into components called 'categories,' the broadest of which define basic functionality common across computing environments, as follows:

- The base category defines all of those elements common to all Power Architecture processors. Although it includes functionality defined in all three books, the Base category preserves almost all of the user application-level resources defined in the original PowerPC Book I, the user instruction set architecture (UISA). Other features from the original UISA, such as the floating-point and move assist instructions, are treated as separate categories that are not required for every implementation.

- The embedded and server categories define mutually exclusive resources appropriate for those environments. The e500 family devices implement embedded category resources.

Other categories address more specific features, such as the signal processing engine. Some of these special features were optional in the PowerPC architecture. Others were previously defined as auxiliary processing units (APUs) and were not part of the architecture. Many of those former APUs, began life as part of Freescale's embedded implementation standards (EIS), a layer of architecture for features common to Freescale processors, but outside of the formal architecture specification. The EIS continues to define such features.

## 2 Differences between e300 and e500 Cores: Overview

This section provides an overview of differences between the e300 and e500 families and summarizes functionality specific to each; more detailed information about the instruction, register, interrupt, and MMU models is provided in the subsequent sections.

## 2.1 The Floating-Point Model and Signal Processing Engine (SPE)

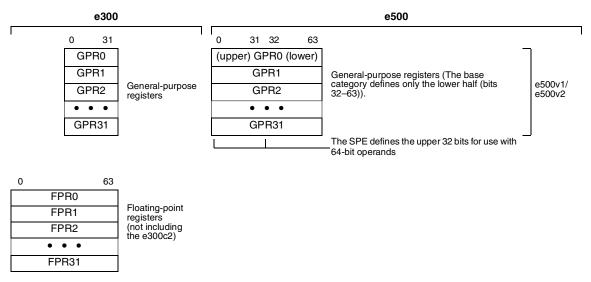

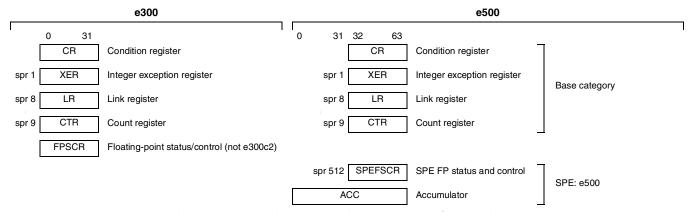

The e300 implements the floating-point instruction model defined by the PowerPC architecture, and included as a distinct category the Power ISA (not including e300c2). This floating-point model includes a separate register file of 32, 64-bit floating-point registers (FPRs) and a full suite of floating-point computational and load/store instructions that support both single- and double-precision operations. The floating-point status and control register (FPSCR) and condition register (CR) resources enable and track exception conditions.

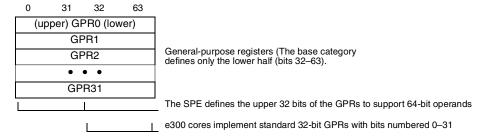

The e500v1 and e500v2 implement the signal processing engine (SPE), a comprehensive set of 64-bit, two-element, SIMD instructions that share the UISA-defined GPRs extended by the SPE to 64 bits, as shown in Figure 2.

Figure 2. Extended GPRs

Migrating from e300- to e500-Based Integrated Devices, Rev. 0

The SPE definition includes three dependent embedded floating-point categories:

- Embedded scalar, single-precision (e500v1/e500v2)

- Embedded scalar, double-precision (e500v2)

- Embedded vector, single-precision (e500v1/e500v2)

For systems that do not require high-end graphics and other floating-point intensive applications, providing a floating-point instruction set that shares the integer-based GPRs rather than requiring the implementation of FPRs simplifies the design of the processor.

## 2.2 e500-Only Features

The e500 implements the following features, not provided on the e300 and defined by the Power ISA:

- Multiple-level interrupt model. In addition to the standard set of save restore registers (SRR0 and SRR1) and the Return from Interrupt instruction (**rfi**), the Power ISA defines the following separate resources to shorten interrupt latency and provide greater control over interrupt behavior:

- Critical interrupts—Uses separate save and restore resources, CSSR0 and CSRR1 the Return from Critical Interrupt instruction (rfci). These resources allowed critical-type interrupts to be taken without having to save state of any concurrent non-critical interrupts. Some e300 family devices support critical interrupts using the fixed offset of 0xA00 rather than the IVOR/IVPR SPRs to determine the interrupt vector.

- The following interrupts use the critical interrupt resources: critical input and watchdog timer interrupts. On the e500, machine check interrupts may be configured to use critical interrupt resources.

- Machine check interrupt—Implements save and restore registers (MCSRR0/MCSRR1) used to save the return address and machine state when machine check interrupts are taken. The **rfmci** instruction is used to restore state.

- Programmable interrupt vectors. The Power ISA defines the following SPRs for setting up the interrupt vector table:

- Interrupt vector prefix register (IVPR). Provides the high-order bits for placing the interrupt table in memory.

- Interrupt vector offset registers (IVORs). Provides the low-order, interrupt-specific bits for placing each interrupt handler into the interrupt table.

- Byte ordering configured on a per-page basis (the E bit in the TLBs) instead of the moded byte ordering determined by the setting of MSR[LE,ILE]. These bits are not implemented on the e500. The Power ISA defines true little-endian byte ordering, replacing the version of little-endian byte ordering defined in the PowerPC architecture. The e300 also supports a true little-endian byte-ordering mode, configured through the MSR[LE,ILE] fields

- Cache-line locking. Allows instructions and data to be locked into their respective caches on a

cache line basis. Locking is performed by a set of touch and lock set instructions.

The e300 cache locking functionality allows separate locking of the data and instruction cache by

setting HID0[DLOCK,ILOCK]. The e300 provides locking on a cache-way basis using

HID2[IWLCK, DWLCK].

#### **Power Architecture Details**

Freescale MMU. The embedded MMU model defines page-based, software-managed address

translation and memory protection using translation lookaside buffers (TLBs). It consists primarily

of the storage architecture defined by Book E and the Freescale EIS.

The MMU model defines the following used to configure and update the TLBs:

- Machine state register (MSR) fields. MSR[DS] and MSR[IS] are defined as part of the address translation to designate address spaces for data and instruction storage. These bits replace MSR[DR] and MSR[IR], which the PowerPC architecture defined to enable memory translation. Note that translation is always enabled on Power ISA devices.

- Unlike the PowerPC model implemented on the e300, there is no support for real mode; that is, translation is always enabled.

- MMU assist registers:

- e500v1: MAS0-MAS4 and MAS6

- e500v2: MAS0–MAS4 and MAS6–MAS7

- Process identification registers PIDn.

- The TLB configuration registers, TLB0CFG-TLB3CFG

- The MMU control and status register, MMUCSR0

- The MMU configuration register MMUCFG

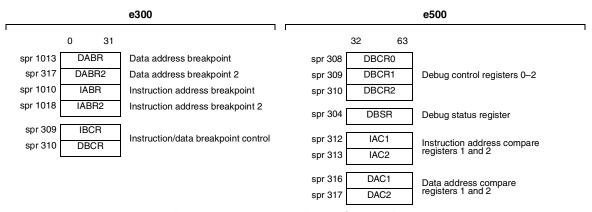

- Expanded hardware and software debug functions. These include instruction and data breakpoints

and program single stepping. The debug facilities include debug control registers

(DBCR0–DBCR2) and address compare registers (IACs and DACs) for enabling and recording

various kinds of debug events and registers that support the debug interrupt-type (DSRR0 and

DSRR1).

- Alternate time base. An additional time base analogous to the standard time base defined by both the Power ISA and the PowerPC architecture (Book II). The alternate time base is implemented on the e500v2.

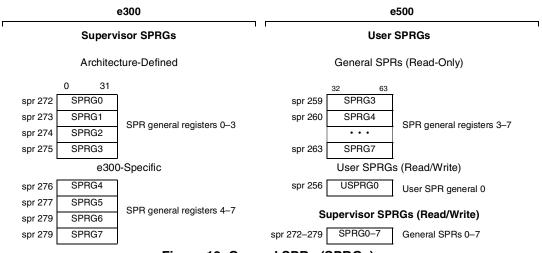

- Additional software-use SPRs. In the Power ISA, the base category defines SPRG0–SPRG3; the

embedded category defines SPRG4–SPRG7. The PowerPC architecture defines SPRG0–SPRG3;

e300 implements SPRG4–SPRG7, as described in Section 5.10, "Software-Use SPR Comparison."

## 3 Power Architecture Details

This section provides an overview of the programming, interrupt, cache, and MMU models as they are defined by the PowerPC architecture and Power ISA architecture, noting any differences either in how the resources are defined in the different versions of the architecture or in how those definitions are structured.

The original UISA, Book I, as it was defined in the PowerPC architecture, was consistent with the Book E user-level programming model and now comprises most of the base category. This ensures binary compatibility across the 15-year legacy of applications and across the many families of desktop, embedded, and server processors.

## 3.1 An Overview of Categories Implemented by the e500

This section provides an overview of the categories defined by the Power ISA and implemented on the e500.

All devices implement the facilities defined by the base category. This largest category encompasses all components common across the computing environments; for example, these include the integer computational and load/store instructions and the GPRs. These include devices such as the e300 cores based on the PowerPC architecture. Although the base category largely consists of the features defined in Book I (the user ISA), like many categories, it extends beyond Book I to include those Book II (VEA) and Book III (OEA) features common to all Power Architecture devices, such as the machine state register (MSR), the time base, the interrupt model's save and restore registers, and the instructions required for accessing them.

The Power ISA floating-point category consists of the resources originally defined by the PowerPC architecture to support single- and double-precision floating-point instructions. The e300c2, e500v1, and e500v2 do not implement this floating-point model. The functionality of these resources has not changed. Defining them as a separate category underscores the advantages of a modular architecture, providing greater leeway in balancing power, thermal, size, and price constraints for very specific environments.

The Integer Select instruction (**isel**), formerly a Freescale EIS instruction, is now part of the base category. This instruction can be used to more efficiently handle sequences with multiple conditional branches, and is not implemented on the e300.

The next largest categories are those that support the two computing environments to which the Power ISA is written, the embedded and server environments. The following section gives a high level description of the embedded category; the remaining categories are defined in the sections that follow.

## 3.1.1 The Embedded Category

As described above, the embedded category largely consists of features formerly defined by the PowerPC Book E architecture and the Freescale EIS. This section describes the components as defined by the Power ISA. Note that the high level embedded category incorporates some resources defined in Book E, including the following:

- Write MSR External Enable instructions (**wrtee**[i]), which is implemented on the e500 to update only MSR[EE].

- The software-use SPRs (SPRG4–SPRG9), which are implemented on the e300 as implementation-specific features.

## 3.1.2 Signal Processing Engine (SPE)

The SPE, implemented on the e500v1 and e500v2, is a 64-bit, two-element, single-instruction multiple-data (SIMD) ISA, originally designed to accelerate signal processing applications normally suited for digital signal processing (DSP) operations. The two-element vectors fit within the GPRs, which the SPE extends to 64 bits. SPE also defines an accumulator register (ACC) to allow for back-to-back operations without loop unrolling. The SPE is primarily an extension of Book I but identifies some resources for interrupt handling in Book III-E.

In addition to add- and subtract-accumulate operations, the SPE supports a number of multiply-accumulate operations, including negative-accumulate forms as summarized in Table 1. The SPE supports signed, unsigned, and fractional forms. For these instructions, the fractional form does not apply to unsigned forms, because integer and fractional forms are identical for unsigned operands.

Mnemonics for SPE instructions generally begin with the letters 'ev' (embedded vector).

**Table 1. SPE Vector Multiply Instruction Mnemonic Structure**

| Prefix | Multiply Element |                               | Data Type Element |                            | Accumulate Element |                                    |

|--------|------------------|-------------------------------|-------------------|----------------------------|--------------------|------------------------------------|

|        | ho               | half odd (16x16->32)          | usi               | unsigned saturate integer  | а                  | write to ACC                       |

|        | he               | half even (16x16->32)         | umi               | unsigned modulo integer    | aa                 | write to ACC & added ACC           |

|        | hog              | half odd guarded (16x16->32)  | ssi               | signed saturate integer    | an                 | write to ACC & negate ACC          |

|        | heg              | half even guarded (16x16->32) | ssf 1             | signed saturate fractional | aaw                | write to ACC & ACC in words        |

| evm    | wh               | word high (32x32->32)         | smi               | signed modulo integer      | anw                | write to ACC & negate ACC in words |

|        | wl               | word low (32x32->32)          | smf <sup>1</sup>  | signed modulo fractional   |                    |                                    |

|        | whg              | word high guarded (32x32->32) |                   |                            |                    |                                    |

|        | wlg              | word low guarded (32x32->32)  |                   |                            |                    |                                    |

|        | w                | word (32x32->64)              |                   |                            |                    |                                    |

Low word versions of signed saturate and signed modulo fractional instructions are not supported.

## 3.1.2.1 SPE Embedded Vector and Scalar Floating-Point Categories

The embedded floating-point categories are dependent categories of the SPE. These include the following:

- Single-precision scalar

- Single-precision vector

- Double-precision scalar

The embedded floating-point categories, compatible with IEEE Std. 754<sup>TM</sup>, provide floating-point operations to power- and space-sensitive embedded applications. As is true for all Signal Processing Engine categories, rather than implementing the FPRs defined by the PowerPC architecture, these categories share the GPRs used for integer operations, extending them to 64 bits to accommodate vector single-precision and scalar double-precision categories. These extended GPRs are described in Section 5.1, "Register File Comparison."

## 4 Instruction Model

This section describes the instructions and instruction classes as they are defined as part of the Power ISA definition. Features defined only for the PowerPC architecture are indicated as such.

The following instructions are implemented on both the e300 and e500 cores with minimal differences:

• Integer instructions—These include arithmetic, logical, and integer load/store instructions. See Section 4.2.1, "Integer Instructions." The Power ISA defines and the e500 implements the Integer Select instruction (**isel**), which is neither provided by the earlier PowerPC architecture nor is implemented on the e300.

• Branch and flow control instructions—These include branching instructions, CR logical instructions, trap instructions, and other instructions that affect instruction flow. See Section 4.2.3, "Branch and Flow Control Instructions."

The following groups of instructions are implemented on both e300 and e500 family devices, but with some differences:

- Floating-point instructions—The e300 family (excluding the e300c2) implements the base category floating-point instructions defined by the PowerPC architecture; the e500 family implements floating-point vector and scalar single-precision instructions defined as part of the SPE; the e500v2 implements the embedded double-precision instructions. See Section 4.2.2, "Floating-Point Instructions (e300)," and Section 2.1, "The Floating-Point Model and Signal Processing Engine (SPE)."

- Processor control instructions—These instructions, described in Section 4.3, "Processor Control Instructions," include the instructions that explicitly access registers such as SPRs, MSR, CR, and others. To reduce interrupt latency, the e500 implements the Write MSR External Enable instructions (wrtee[i]), which can be used instead of mtmsr to update only MSR[EE], which enables or disables external interrupt exception conditions. The wrtee instruction has fewer serialization requirements, and therefore shorter latency, than mtmsr.

- Memory synchronization instructions—These instructions, described in Section 4.3.1, "Memory Synchronization Instructions," ensure that accesses to memory and memory resources occur in correct order with respect to memory operations generated by other instructions or by other memory devices.

- Book E recast the PowerPC architecture—defined sync as msync. However, the Power ISA version defines msync as a simplified mnemonic for the sync instruction, configured to function as the Book E–defined msync for embedded category devices.

- The eieio instruction, Enforce In-Order Execution of I/O, which is defined by the PowerPC architecture and implemented on the e300 shares the same opcode with the mbar (Memory Barrier) instruction defined by the Power ISA embedded category.

Because eieio and mbar share the same opcode, software designed for both environments must assume that only the eieio functionality applies, because the functions provided by eieio are a subset of those provided by mbar. Refer to the EREF and PEM for details.

- Memory control instructions—These instructions provide control of caches and TLBs. See Section 4.3.2, "Memory Control Instructions."

The standard UISA floating-point instructions use FPRs for single- and double-precision floating-point operands. The SPE embedded floating point instructions, implemented on the e500v1 and e500v2, use GPRs widened to 64 bits to support vector single-precision and scalar double-precision operands.

## 4.1 Simplified Mnemonics

The simplified mnemonics for instructions common to both versions of the architecture are consistent in all implementations. Note that the Power ISA defines simplified mnemonics for some new instructions.

Also the **msync** instruction in the e500 is a simplified mnemonic for **sync** instruction. See Table 8.

Additional simplified mnemonics are provided to support access to both newly architected and implementation-specific SPRs.

#### 4.2 Instruction Set Overview

The tables in this section provide a general overview of the e500 instruction set, indicating those instructions that either are not supported by the e300 or whose implementations have changed.

#### 4.2.1 **Integer Instructions**

This section describes the integer instructions, all of which are defined in Book I. All are part of the base category except for the load/store string and multiple instructions.

These integer instructions are grouped as follows:

- Integer arithmetic instructions

- Integer compare instructions

- Integer logical instructions

- Integer rotate and shift instructions

- Integer select instruction (new in the Power ISA and implemented on the e500)

Integer instructions use GPRs for source operands and place results into GPRs and the XER and CR fields. Integer instructions are shown in Table 2.

| Instructions                                                  | Function                                           | Options                                                             |

|---------------------------------------------------------------|----------------------------------------------------|---------------------------------------------------------------------|

| Integer arithmetic (addx, divx, mulx, negx, subx)             | Add, divide, multiply, negate, subtract            | Unchanged                                                           |

| Integer compare (cmpx)                                        | Compare                                            | Unchanged                                                           |

| Integer logical (andx, cnt, eqv, extx, nand, norx, orx, xorx) | AND, count, equivalent, extend, NAND, NOR, OR, XOR | Unchanged                                                           |

| Integer rotate and shift (rlwx, slwx, srwx, srawx)            | Rotate left word, shift                            | Unchanged                                                           |

| Integer select ( <b>isel</b> )                                | Integer select                                     | Defined by the Power ISA, implemented by the e500 but not the e300. |

**Table 2. Integer Computational Instructions**

Integer load and store instructions, shown in Table 3, are issued and translated in program order; however, the accesses can occur out of order. Synchronizing instructions (see Table 8) are defined in Book II and are provided to enforce strict ordering.

Migrating from e300- to e500-Based Integrated Devices, Rev. 0 10 Freescale Semiconductor

| Table 3. Integer Load/Store Instructions |

|------------------------------------------|

|------------------------------------------|

| Instruction                                            | Function                                                                                                  | Comments                                                                                                                                                                                                                                                                             |

|--------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Integer load<br>(Ibx, Ihx, Iwx)                        | Load byte, word, half word,<br>algebraic (half word), byte<br>reverse, and zero, with update,<br>indexed. | <b>Note:</b> The SPE defines instructions for loading and storing double-word operands required for SPE vector instructions and embedded floating-point single-precision vector and double-precision scalar instructions.                                                            |

| Integer load                                           | Load multiple word                                                                                        | Base category. Implemented on both e300 and e500 cores.                                                                                                                                                                                                                              |

| multiple/string<br>word: <b>Imw</b> , <b>Iswi</b>      | Load string word                                                                                          | Move assist category. Implemented on the e300; not implemented on the e500.                                                                                                                                                                                                          |

| Integer store (stbx, sthx, stwx                        | Store                                                                                                     | <b>Note:</b> Byte, word, half word, byte-reverse, with update, indexed. The SPE defines instructions for loading and storing double-word operands required for SPE vector instructions and embedded floating-point single-precision vector and double-precision scalar instructions. |

| Integer store                                          | Store multiple word                                                                                       | Base category. Implemented on both e300 and e500 cores.                                                                                                                                                                                                                              |

| multiple/string<br>word: <b>stmw</b> ,<br><b>stswi</b> | Store string word                                                                                         | Move assist category. Implemented on the e300; not implemented on the e500.                                                                                                                                                                                                          |

## 4.2.2 Floating-Point Instructions (e300)

The floating-point model is written to IEEE 754, which defines conventions for single- and double-precision arithmetic. The standard requires that single-precision arithmetic be provided for single-precision operands. (Note that the floating-point instructions are not implemented on the e300c2.)

The signal processing engine (SPE), implemented on the e500v1 and e500v2, defines an alternative floating-point instruction set that uses GPRs rather than FPRs. See Section 3.1.2.1, "SPE Embedded Vector and Scalar Floating-Point Categories."

Table 4 provides an overview of the floating-point computational instructions.

**Table 4. Floating-Point Computational Instructions**

| Instructions                                                                                             | Instruction Name                                                                                                         | Comments                |

|----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|-------------------------|

| Floating-point elementary arithmetic (faddx, fdivx, fmulx, fsubx, fsqrtx, fresx, fabs, fmr, fnabs, fneg) | Add, divide, multiply, reciprocal, square root, subtract, absolute value, move register, negative absolute value, negate | Not on<br>e500v1/e500v2 |

| Floating-point multiply-add (fmaddx)                                                                     | Multiply-add, multiply-subtract, negative multiply-add, negative multiply-subtract                                       |                         |

| Floating-point rounding and conversion (fctix, frx)                                                      | Convert to/from integer, round to single-precision                                                                       |                         |

| Floating-point compare and select (fcmx)                                                                 | Compare, select                                                                                                          |                         |

| FPSCR (mtfx, mffx)                                                                                       | Move to/from FPSCR                                                                                                       |                         |

Table 5 shows that the floating-point load and store instructions are required to transfer operands between memory and the FPRs.

**Table 5. Floating-Point Load and Store Instructions**

| Instructions                         | Instruction Name     | Comments             |

|--------------------------------------|----------------------|----------------------|

| Floating-point load (Ifx)            | Load floating-point  | Not on e500v1/e500v2 |

| Floating-point store ( <b>stf</b> x) | Store floating-point |                      |

#### 4.2.3 Branch and Flow Control Instructions

Branch instruction functions include the following:

- Branch instructions redirect instruction execution conditionally based on the value of bits in the CR. For branch conditional instructions, the BO operand specifies the conditions under which the branch is taken.

- CR logical instructions perform logical operations on CR contents that help determine branching conditions.

- Trap instructions test for a specified set of conditions. If any of the tested conditions are met, a system trap type interrupt is taken.

- Executing a System Call (sc) instruction lets a user program call on the system to perform a service by invoking a system call interrupt. System Call instructions can be user- or supervisor-level.

For branch conditional instructions, the BO operand specifies the conditions under which the branch is taken. The BI operand specifies which of the 32 CR bits to test.

All processors support simplified mnemonics that allow conditions specified by BO and BI to be incorporated into the mnemonic. For example, the Branch Conditional instruction, **bc** BO,BI, *target address*, can be coded to decrement the count register (CTR) and branch as long as the CTR is not zero (closure of a loop controlled by a count loaded into CTR). To specify this condition, the BO field must be coded as 16. Alternatively, a simplified mnemonic is available, **bdnz**, that indicates "branch while the decremented value is non-zero." Using the simplified mnemonic eliminates the BO and BI operands, simplifying '**bc** 16,0,target' to the more easily remembered '**bdnz** *target*', which generates identical machine code.

The supervisor-level **rfi** instruction is used for returning from a standard interrupt handler.

The differences between the processor families are as follows:

- The **rfci** instruction, implemented on some e300 devices, is part of the embedded category and is used for critical interrupts on e500 cores.

- The e500 implements the Power ISA–defined **rfmci** for machine check interrupts. See Section 6, "Interrupt Model."

Branch and flow control instructions are shown in Table 6.

Table 6. Branch and Flow Control Instructions

| Instruction            | Name               | Comments                                                                                                                                   |  |

|------------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------|--|

| Branch (bx, bcx)       | Branch             | Unchanged                                                                                                                                  |  |

| CR logical (crx, mcrx) | Condition register | r Unchanged                                                                                                                                |  |

| Trap (tx, twx)         | Trap               | Unchanged                                                                                                                                  |  |

| System call (sc)       | System call        | Unchanged                                                                                                                                  |  |

| Return (rfx)           | Return from        | Interrupt, critical, and machine check interrupts. The <b>rfci</b> instruction is defined by the Power ISA but is implemented on the e300. |  |

### 4.3 Processor Control Instructions

Processor control instructions are used to read and write registers other than GPRs and FPRs that can be accessed specifically. These include CR, XER, MSR, and SPRs. The time base register and some SPRs are accessible at both the user and supervisor levels; separate SPR numbers are used for each.

Differences between implementations are as follows:

• The e500 implements the Power ISA-defined Write MSR External Enable instructions (**wrtee**[i]), which updates only MSR[EE] with fewer serialization requirements, and therefore shorter latency, than **mtmsr**.

Table 7 summarizes processor control instructions.

**Table 7. Processor Control Instructions**

| Instructions    | Name                                                              | Comments                                                                                                                                                             |

|-----------------|-------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Move (mtx, mfx) | Move to SPR, CR fields,<br>CR from XER, time<br>base, MSR, PMR    | <b>Note:</b> All devices support simplified mnemonics formed by adding the abbreviated name of any SPR to the prefix 'mf', for example mfmas0, mfivor3, and mfcssr1. |

|                 | Move from SPR, CR<br>fields, CR from XER,<br>time base, MSR, PMR. |                                                                                                                                                                      |

## 4.3.1 Memory Synchronization Instructions

Memory synchronization instructions control the order in which memory operations execute with respect to asynchronous events and the order in which operations are seen by other mechanisms that access memory. Differences between processors are highlighted in Table 8.

**Table 8. Memory Synchronization Instructions**

| Instructions Name                             |                             | Comments  |

|-----------------------------------------------|-----------------------------|-----------|

| lwarx                                         | Load word and reserve index | Unchanged |

| stwcx. Store word conditional index Unchanged |                             | Unchanged |

Migrating from e300- to e500-Based Integrated Devices, Rev. 0

**Table 8. Memory Synchronization Instructions (continued)**

| Instructions                     | Name                                                                 | Comments                                                                                                                                                                                      |

|----------------------------------|----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Synchronize (sync, eieio, isync, | Memory Synchronize                                                   | Book E recast PowerPC architecture—defined <b>sync</b> as <b>msync</b> . Power ISA defines <b>msync</b> as a simplified mnemonic, configured to function as the Book E—defined <b>msync</b> . |

| msync,<br>mbar)                  | Enforce In-Order Execution<br>of I/O (e300)/Memory Barrier<br>(e500) | PowerPC architecture-defined (e300)                                                                                                                                                           |

| ·                                |                                                                      | Embedded category <b>mbar</b> instruction implemented on the e500. The PowerPC architecture defines this opcode as <b>eieio</b> .                                                             |

|                                  | Instruction Synchronize                                              | isync synchronizes the instruction stream                                                                                                                                                     |

## 4.3.2 Memory Control Instructions

Memory control instructions include instructions for cache management and TLB management. Major differences are as follows:

- The segment register instructions defined by the PowerPC architecture to support the segmented MMU model and implemented on the e300 are not part of the embedded environment and are not implemented on the e500.

- TLB management instructions—Resources defined to support software address translation.

The e300 defines the Load Data TLB Entry (tlbld) and Load Instruction TLB Entry (tlbli) instructions to directly access TLBs. The Power ISA defines tlbwe and tlbre, which the e500 uses to directly configure TLBs with translation and memory protection information by loading and storing values defined in the memory assist (MAS) registers. Additional instructions are provided for searching and invalidating entries and for synchronizing TLB accesses.

Specific differences in these instruction sets are listed in Table 9.

**Table 9. Memory Control Instructions**

| Instructions                  | Name                                                                                | Comments                                                                                                                               |

|-------------------------------|-------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| User-level cache (dcbx, icbx) | Data cache block touch,<br>touch for store, allocate,<br>clear, zero, store, flush. | The Power ISA defines additional cache lock instructions, <b>icblc</b> and <b>dcblc</b> , implemented on the e500.                     |

|                               | Instruction cache block invalidate, touch                                           | The embedded category defines additional cache touch instructions implemented on the e500: icbtls, dcbtls, and dcbtstls.               |

| TLB                           | TLB invalidate, synchronize                                                         | Unchanged                                                                                                                              |

| management (tlbx)             | TLB read entry                                                                      | e500. Reads TLB parameters from the TLBs to the MAS registers.                                                                         |

|                               | TLB search indexed                                                                  | e500. Searches valid TLB arrays for an entry corresponding to the virtual address and reads appropriate values into the MAS registers. |

|                               | TLB write entry                                                                     | e500. Writes TLB parameters from the MAS registers to the TLBs.                                                                        |

|                               | Load data/instruction TLB                                                           | The e300 defines the Load Data/Instruction TLB Entry instructions (tlbld and tlbli) to directly update TLBs.                           |

## 4.3.3 Instruction Set Differences

Table 10 lists the instructions implemented in the e300 and e500 processors, where applicable, noting the architecture that defines the instruction.

**Table 10. List of Instructions**

| Mnemonic    | PowerPC   | Power ISA | e300      | e500         |

|-------------|-----------|-----------|-----------|--------------|

| addc[o][.]  | √         | V         | √         | V            |

| adde[o][.]  | √         | $\sqrt{}$ | √         | $\sqrt{}$    |

| addi        | <b>V</b>  | V         | √         | √            |

| addic[.]    | V         | V         | √         | V            |

| addis       | V         | V         | √         | V            |

| addme[o][.] | V         | V         | √         | V            |

| addze[o][.] | V         | V         | √         | V            |

| add[o].]    | <b>V</b>  |           | √         | V            |

| andc[.]     | V         | V         | √         | V            |

| andi.       | V         | V         | √         |              |

| andis.      | <b>V</b>  |           | √         | V            |

| and[.]      | √         | $\sqrt{}$ | V         | V            |

| b           | V         | V         | √         | V            |

| ba          | <b>V</b>  |           | √         | V            |

| bbelr       | _         | _         | _         | V            |

| bblels      | _         | _         | _         | V            |

| bc          | <b>V</b>  | √         | √         | V            |

| bca         | √         | V         | √         | V            |

| bcctr       | <b>√</b>  | $\sqrt{}$ | √         | $\sqrt{}$    |

| bcctrl      | <b>√</b>  | V         | √         | V            |

| bcl         | <b>V</b>  | $\sqrt{}$ | √         | $\checkmark$ |

| bcla        | $\sqrt{}$ | $\sqrt{}$ | $\sqrt{}$ | $\sqrt{}$    |

| bclr        | $\sqrt{}$ | $\sqrt{}$ | $\sqrt{}$ | $\checkmark$ |

| bclrl       | <b>√</b>  | $\sqrt{}$ | √         | $\sqrt{}$    |

| bl          | $\sqrt{}$ | $\sqrt{}$ | $\sqrt{}$ | $\sqrt{}$    |

| bla         | $\sqrt{}$ | $\sqrt{}$ | $\sqrt{}$ | $\sqrt{}$    |

| brinc       | _         |           | _         | v1/v2        |

| cmp         | √         | V         | √         | V            |

| cmpi        | V         |           | $\sqrt{}$ |              |

| cmpl        | $\sqrt{}$ | √         | $\sqrt{}$ | V            |

| cmpli       | V         | √         | $\sqrt{}$ | V            |

| cntlzw[.]   | V         | √         | $\sqrt{}$ | $\sqrt{}$    |

| crand       | V         | √         | $\sqrt{}$ | V            |

| crandc      | V         | √         | $\sqrt{}$ | $\sqrt{}$    |

| creqv       | V         | √         | $\sqrt{}$ | $\sqrt{}$    |

| crnand      | V         | √         | $\sqrt{}$ | V            |

| crnor       | V         | √         | $\sqrt{}$ | V            |

| cror        | $\sqrt{}$ | $\sqrt{}$ | $\sqrt{}$ | $\checkmark$ |

Table 10. List of Instructions (continued)

| Mnemonic    | PowerPC | Power ISA | e300     | e500  |

|-------------|---------|-----------|----------|-------|

| crorc       | √       | V         | √        | √     |

| crxor       | √       | V         | √        | √     |

| dcba        | √       | V         | √        | V     |

| dcbf        | √       | V         | √        | V     |

| dcbi        | √       | V         | √        | √     |

| dcblc       | _       | V         | _        | V     |

| dcbst       | √       | V         | √        | V     |

| dcbt        | √       | V         | √        | √     |

| dcbtls      | _       | $\sqrt{}$ | _        | V     |

| dcbtst      | √       | V         | √        | V     |

| dcbtstls    | _       | V         | _        | V     |

| dcbz        | V       | V         | √        | V     |

| divwu[o][.] | √       | $\sqrt{}$ | √        | V     |

| divw[o][.]  | V       | $\sqrt{}$ | √        | V     |

| eciwx       | V       | _         | <u> </u> | _     |

| ecowx       | V       | _         | _        | _     |

| efdabs      | _       | $\sqrt{}$ | _        | v2    |

| efdadd      | _       | V         | _        | v2    |

| efdcfs      | _       | $\sqrt{}$ | _        | v2    |

| efdcfsf     | _       | $\sqrt{}$ | _        | v2    |

| efdcfsi     | _       | V         | _        | v2    |

| efdcfuf     | _       | V         | _        | v2    |

| efdcfui     | _       | V         | _        | v2    |

| efdcmpeq    | _       | V         | _        | v2    |

| efdcmpgt    | _       | V         | _        | v2    |

| efdcmplt    | _       | V         | _        | v2    |

| efdctsf     | _       | V         | _        | v2    |

| efdctsi     | _       | $\sqrt{}$ | _        | v2    |

| efdctsiz    | _       | $\sqrt{}$ | _        | v2    |

| efdctuf     | _       | V         |          | v2    |

| efdctui     | _       | V         |          | v2    |

| efdctuiz    | _       | V         | _        | v2    |

| efddiv      | _       | $\sqrt{}$ | _        | v2    |

| efdmul      |         | V         | _        | v2    |

| efdnabs     |         | V         | _        | v2    |

| efdneg      | _       | $\sqrt{}$ | _        | v2    |

| efdsub      | _       | V         |          | v2    |

| efdtsteq    |         | V         | _        | v2    |

| efdtstgt    | _       | $\sqrt{}$ | _        | v2    |

| efdtstlt    | _       | V         |          | v2    |

| efsabs      |         | V         | _        | v1/v2 |

| efsadd      | -       | $\sqrt{}$ |          | v1/v2 |

Table 10. List of Instructions (continued)

| Mnemonic                                                                                                                          | PowerPC                                                       | Power ISA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | e300                                                               | e500                                                                                                                    |

|-----------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|

| efscfsf                                                                                                                           | _                                                             | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | _                                                                  | v1/v2                                                                                                                   |

| efscfsi                                                                                                                           | _                                                             | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | _                                                                  | v1/v2                                                                                                                   |

| efscfuf                                                                                                                           | _                                                             | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | _                                                                  | v1/v2                                                                                                                   |

| efscfui                                                                                                                           | _                                                             | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | _                                                                  | v1/v2                                                                                                                   |

| efscmpeq                                                                                                                          | _                                                             | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | _                                                                  | v1/v2                                                                                                                   |

| efscmpgt                                                                                                                          | _                                                             | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | _                                                                  | v1/v2                                                                                                                   |

| efscmplt                                                                                                                          | _                                                             | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | _                                                                  | v1/v2                                                                                                                   |

| efsctsf                                                                                                                           | _                                                             | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | _                                                                  | v1/v2                                                                                                                   |