P1024 and P1015 devices are "Not recommended for new designs", please use the replacement families Power Architecture (T1013, T1023),

Arm Architecture (LS1012, LS1023).

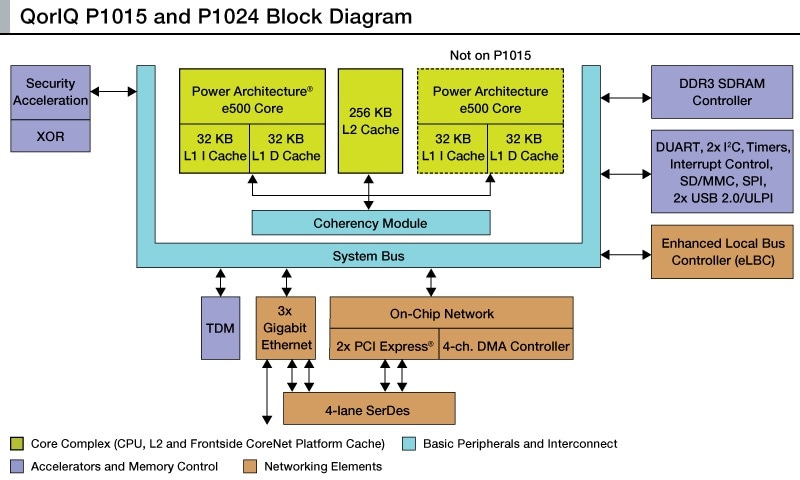

The QorIQ® P1 family, which includes the P1015 and P1024 communications processors, offers extensive integration and extreme power for a wide variety of applications in the networking, telecom, defense and industrial markets. Based on 45 nm technology for low-power implementation, the P1015 and P1024 processors provide single- and dual-core solutions for the 400 MHz to 667 MHz performance range, along with advanced security and a rich set of interfaces.

The QorIQ P1015 and P1024 processors are pin-compatible with the QorIQ P1016, P1025 products, and software-compatible with the P1011/P1020 and P2010/P2020 offering a six-chip range of cost-effective solutions. Scaling from a single core at 400 MHz (P1015) to a dual core at 1.2 GHz per core (P2020), the two QorIQ platforms deliver an impressive 4.5x aggregate frequency range.