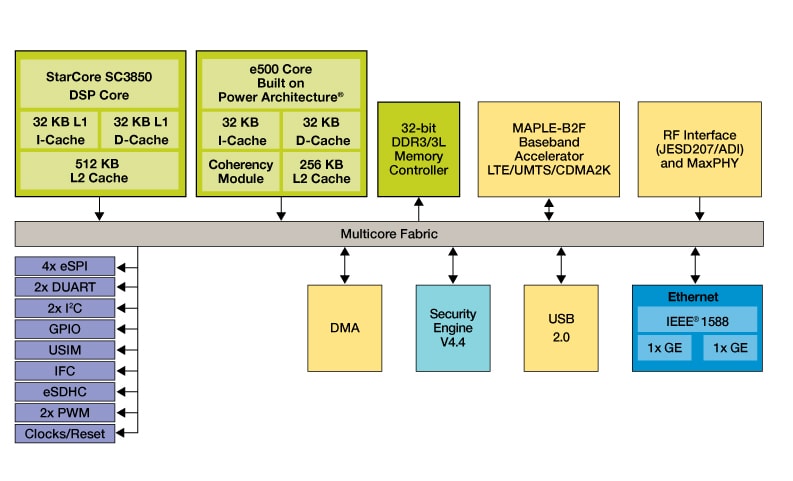

The QorIQ® Qonverge BSC9131 processor is a highly integrated device targeting small cell base station, enterprise VoIP, smart grid control, military/defense and industrial applications.

The BSC9131 device combines Power e500 and StarCore® SC3850 core technologies with MAPLE-B2F specialist DSP acceleration processing, addressing the need for a high-performance, low-cost, integrated solution, that handles a broad range of specialist DSP functions with complimentary high-performance general purpose processing.

.png?imwidth=300)

.png?imwidth=300)