Application Note (8)

-

Display eGUI using TWR-LCD board[AN4452]

Data Sheet (1)

-

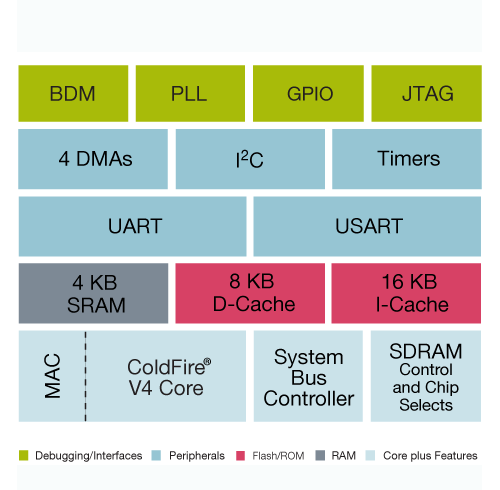

MCF5407 User's Manual[MCF5407UM]Featured

Errata (1)

-

MCF5407 Device Errata[MCF5407DE]

Fact Sheet (2)

-

MCF5407 Integrated ColdFire Microprocessor Product Brief[MCF5407PB]Featured

-

MCF5407FACT MCF5407 ColdFire® Embedded Controllers[MCF5407FACT]Featured

Product Change Notice (1)

Reference Manual (6)

-

ColdFire® ® Family Programmer’s - Reference Manual[CFPRM]Featured

Selector Guide (1)

-

32-bit ColdFire MCU and MPU Product Summary Page[BRCOLDFIRESUM]

Supporting Information (1)

-

MCF5407 Power Dissipation[5407PWR]