# AN13507

# 如何基于μTrace和Trace32对LPC55(S)xx进行边界扫描

## 1 概述

LPC55(S)xx是一款面向嵌入式应用的基于Arm Cortex®-M33的微控制器。 它支持JTAG边界扫描。本文介绍了:

- 如何进入边界扫描模式。

- 如何基于边界扫描描述语言 (BSDL) 对LPC55(S)xx系列进行 边界扫描测试。

- JTAG和边界扫描技术的概述。

为了更好地理解本文档,需要具备JTAG和边界扫描的基本知识。

## 2 JTAG和边界扫描

### 2.1 介绍

JTAG/边界扫描是一个包含四个端口的接口。该接口允许对大多数芯片上的特殊嵌入式逻辑进行访问。JTAG/边界扫描可提供多种功能,可能包含如下的部分或所有功能:

- 无探针器件连接测试。

- 对闪存、CPLD和FPGA的逻辑编程。

- 微处理器和微控制器中用于软件调试的调试逻辑, 或者在无嵌入式软件的情况下测试与外设器件在某个速度下的连接。

#### 2.2 发展历程

测试访问端口(TAP)和边界扫描的架构在IEEE标准1149.1中进行了定义。该标准的发展历程的概述如下:

- 1985年,成立了欧洲联合测试行动组(JETAG)。

- 1986年,欧洲联合测试行动组(JETAG)更名为联合测试行动组(JTAG)。

- 1986-1988年,JTAG 技术组委员会制定并发布了一系列关于边界扫描标准化形式的建议。

- 1988年,此提案的最后一次更新,即JTAG 2.0版本,被提交给IEEE可测试性总线标准委员会(P1149), 并获得了P1149的认可。JTAG提案成为了可测试性总线系列标准的基础。

- 1990年, JTAG从1990年开始制定了一系列补充版本, 用于修正、澄清和增强原有标准。

- 1993年,发布了IEEE标准1149.1aTM-1993

- 1994年,发布了IEEE标准1149.1b-1994

- 2001年,发布了IEEE标准1149.1-2001

- 2013年,发布了IEEE标准1149.1-2013

## 目录

| 1                             | 概述1                                   |

|-------------------------------|---------------------------------------|

| 2                             | JTAG和边界扫描1                            |

| 2.1                           | 介绍1                                   |

| 2.2                           | 发展历程1                                 |

| 2.3                           | 基本原理2                                 |

| 2.4                           | 指令集2                                  |

| 2.5                           | JTAG的测试访问端口(TAP)3                     |

| 2.6                           | 边界扫描描述语言 (BSDL)4                      |

| 2.7                           | 有关JTAG和边界扫描的更多信息 4                    |

| _                             |                                       |

| 3                             | 构建边界扫描的测试环境5                          |

| <b>3</b><br>3.1               | <b>构建边界扫描的测试环境5</b><br>边界扫描测试工具套件的简介5 |

| -                             |                                       |

| 3.1                           | 边界扫描测试工具套件的简介5                        |

| 3.1<br>3.2                    | 边界扫描测试工具套件的简介5<br>硬件连接7               |

| 3.1<br>3.2<br>3.3             | 边界扫描测试工具套件的简介5<br>硬件连接7<br>进入边界扫描模式8  |

| 3.1<br>3.2<br>3.3<br><b>4</b> | 边界扫描测试工具套件的简介5 硬件连接                   |

| 3.1<br>3.2<br>3.3<br><b>4</b> | 边界扫描测试工具套件的简介5 硬件连接                   |

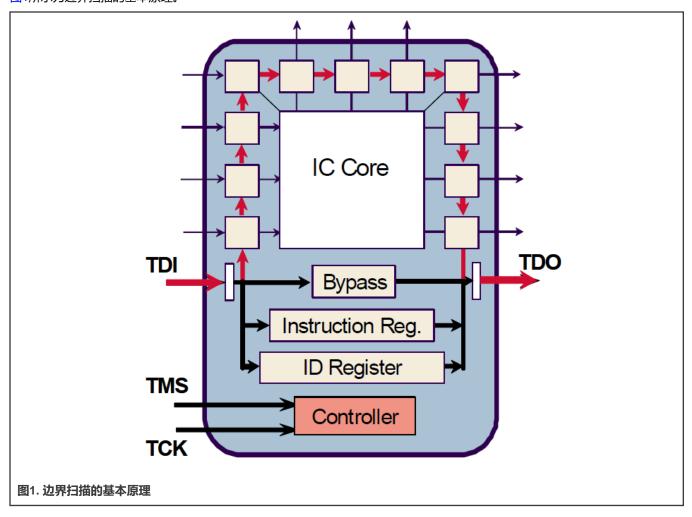

### 2.3 基本原理

边界扫描是一种测试PCB和IC内部子模块之间的互连的方法。为了进行边界扫描测试,在器件中添加了额外的逻辑。边界扫描单元置于核心逻辑和端口之间。

在边界扫描测试中,器件上每个主要的输入和输出信号都要辅以一个名为边界扫描单元的多用途存储元件。这些单元连接到一个 移位寄存器,后者被称为边界扫描寄存器。这个寄存器可用于读写端口的状态。

在正常模式下,这些单元是透明的,而内核与这些端口是相连的。在边界扫描模式下,内核与这些端口是隔离的,且端口信号由 JTAG接口控制。

图1所示为边界扫描的基本原理。

### 2.4 指令集

表1介绍了IEEE 1149.1标准中定义的边界扫描指令。

#### 表1. 标准指令集

| 指令       | 必选/可选 | 说明                                                |

|----------|-------|---------------------------------------------------|

| BYPASS   | 必选    | TDI通过单个移位寄存器连接到TDO。                               |

| SAMPLE   | 必选    | 对集成电路(IC)的标准操作进行快照。                               |

| PRELOAD  | 必选    | 向边界扫描寄存器加载数据。                                     |

| EXTEST   | 必选    | 将边界扫描寄存器的预加载数据应用到端口。                              |

| INTEST   | 可选    | 将边界扫描寄存器的预加载数据应用到内核逻辑。                            |

| RUNBIST  | 可选    | 执行IC的独立自测试。                                       |

| CLAMP    | 可选    | 将边界扫描寄存器的预加载数据应用到端口,并选择旁路寄存器作为TDI和<br>TDO之间的串行路径。 |

| IDCODE   | 可选    | 读取器件的识别寄存器。                                       |

| USERCODE | 可选    | 读写用户可编程的识别寄存器。                                    |

| HIGHZ    | 可选    | 将IC置于非活动驱动状态(例如,将所有端口均设置为高阻状态)。                   |

## 2.5 JTAG的测试访问端口 (TAP)

TAP是一个通用端口,可提供对组件内置的很多测试支持功能的访问,包括测试逻辑。它**至少由三个输入连接**(即**TCK、TMS**和**TDI**)和**一个输出连接**(即**TDO**)组成。还提供了可选的第四个输入连接,TRST,用于测试逻辑的异步初始化。

#### 表2列出了TAP信号

#### 表2. TAP信号的说明

| W III 28200-0 |         |                                                  |  |  |

|---------------|---------|--------------------------------------------------|--|--|

| 信号名称          | 输入/输出类型 | 说明                                               |  |  |

| TCK           | 输入      | 为测试逻辑提供时钟。                                       |  |  |

| TMS           | 输入      | 在TCK上升沿时,呈为TMS信号的值决定了TAP控制器的下一个状态。<br>控制测试操作的电路。 |  |  |

| TDI           | 输入      | 测试逻辑在TDI接收的串行测试指令和数据。                            |  |  |

| TDO           | 输出      | 来自测试逻辑的测试指令和数据的串行输出。                             |  |  |

| TRST          | 输入      | 供异步初始化,低电平有效。                                    |  |  |

注意

JTAG在LPC55(S)xx器件上仅用于边界扫描和生产测试,不能用于调试目的。

### 2.6 边界扫描描述语言 (BSDL)

边界扫描描述语言(BSDL)立足于超高速集成电路硬件描述语言(VHDL)的句法和语法。BSDL不是一种通用的硬件描述语言。它描述了在特定组件内实现边界扫描的关键要素。

表3列出了BSDL文件中包含的要素。

#### 表3. BSDL的要素

| 要素        | 说明                                         |

|-----------|--------------------------------------------|

| 实体说明      | 芯片名称或功能说明。                                 |

| 通用参数      | 封装或引脚映射说明。                                 |

| 逻辑端口说明    | 引脚类型说明,如输入、输出、输入输出、联动。                     |

| 标准使用说明    | 引用外部定义。                                    |

| 元器件一致性声明  | 遵循的标准。                                     |

| 器件封装引脚映射  | 引脚映射说明。                                    |

| 扫描端口识别    | 器件上用于JTAG TAP的引脚说明,包括TCK、TMS、TDI和TDO。      |

| 合规性使能说明   | 进入边界扫描模式所涉及的引脚以及应用于引脚的电平的说明。可用于芯片进入边界扫描模式。 |

| 指令寄存器说明   | 指令长度和指令代码的说明。有时也包括器件特有的指令,也称为私有指令。         |

| 寄存器访问说明   | 与特有指令相对应的寄存器的说明                            |

| 边界扫描寄存器说明 | 记录边界扫描单元和这些边界扫描单元的功能的列表。                   |

#### 通过以下链接下载LPC55(S)xx的BSDL文件:

- LPC55(S)6x: https://www.nxp.com/downloads/en/bsdl/LPC55S6X-BSDL.zip

- LPC55(S)2x: https://www.nxp.com/downloads/en/bsdl/LPC55S2X-BSDL.zip

- LPC55(S)1x: https://www.nxp.com/downloads/en/bsdl/LPC55S1X-BSDL.zip

具体芯片的最新BSDL文件可以从恩智浦官网下载。以LPC55(S)6x的BSDL文件为例,请执行以下步骤:

- 访问恩智浦官网,在搜索框中输入产品型号。本例中为LPC55S69。

- 要转到相应型号的主页,请单击搜索结果列表中的特定型号。本例中为LPC55S69JBD100。

- 要转到目标型号介绍页面上的"工具和软件"选项卡,请单击"工具和软件"快速链接。

- 从 "工具和软件" 部分的名为 "设计工具和文件" 的条目中下载BSDL文件。

#### 2.7 有关JTAG和边界扫描的更多信息

如需了解有关JTAG和边界扫描的更多信息,请参阅以下链接:

• JTAG和边界扫描主页: https://www.jtag.com/

• IEEE标准1149.1

— 1990年版本: https://standards.ieee.org/standard/1149\_1-1990.html

— 2001年版本: https://standards.ieee.org/standard/1149\_1-2001.html

— 2013年版本: https://standards.ieee.org/standard/1149\_1-2013.html

## 3 构建边界扫描的测试环境

### 3.1 边界扫描测试工具套件的简介

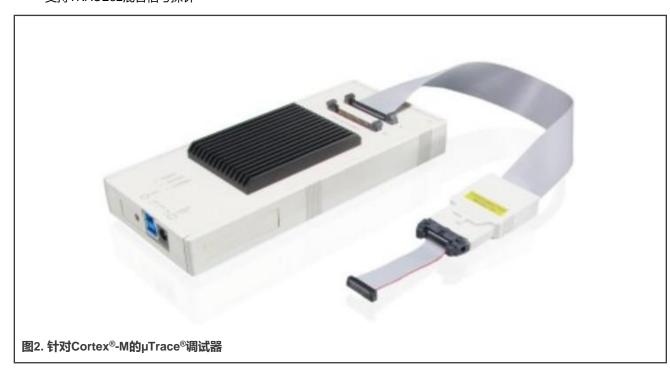

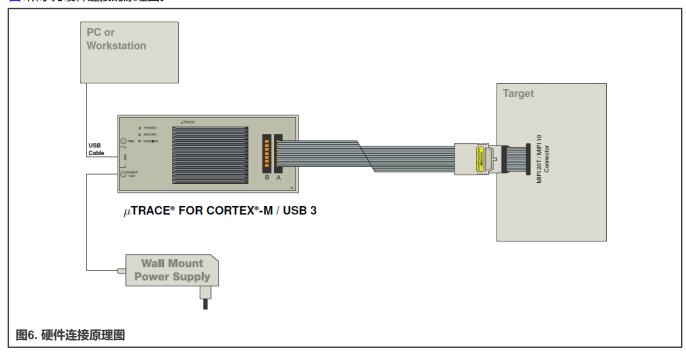

在本应用笔记中,边界扫描测试使用Lauterbach的工具套件,该套件是针对Cortex-M的一体化调试和跟踪解决方案。这套工具包括以下两个部分:

针对Cortex<sup>®</sup>-M的µTrace<sup>®</sup>

针对Cortex®-M的µTrace®是Lauterbach的一种面向特定架构的产品。其特点如下:

- 一 片上/外部闪存编程、调试、跟踪和JTAG边界扫描

- 推荐用于带Cortex-M的单核微控制器

- 推荐用于仅有Cortex-M的多核微控制器 (单调试端口)

- 256M字节的跟踪存储器

- 连接主机的USB 3接口

- TRACE32的数据流速度高达每秒150M字节

- 支持TRACE32混合信号探针

如需了解有关针对Cortex®-M的µTrace®的更多信息,请参见图3。

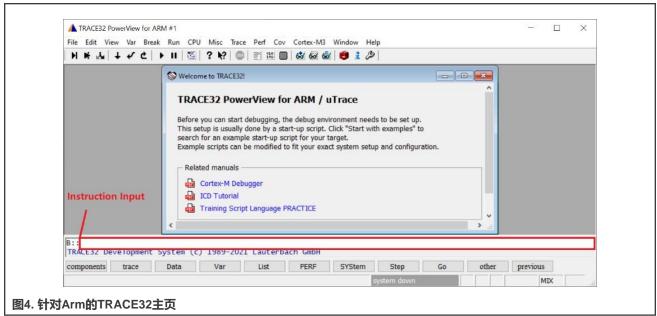

#### • TRACE32

TRACE32是由Lauterbach开发的一套仿真测试工具。它在PC上运行,与针对Cortex®-M的µTrace®一起使用,用于片上/外部闪存的编程、调试、跟踪和JTAG边界扫描。它支持各种处理器架构,包括Arm、MIPS、PowerPC和DSP等标准处理器、软内核以及协处理器。

对于边界扫描,TRACE32提供了GUI操作进行交互式测试,并支持用于自动测试的脚本。要执行多个命令,如系统设置、 JTAG和BSDL等,可制作一个包含这些命令的脚本。要完成测试,执行此脚本即可。这种执行方式的效率高,减少了在命令 行模式下出错的可能性。

TRACE32支持命令行的输入。命令行输入位于TRACE32主页面的底部,以B::开头。要完成操作,需输入命令,如系统重置、系统设置、BSDL文件加载和边界扫描测试等。

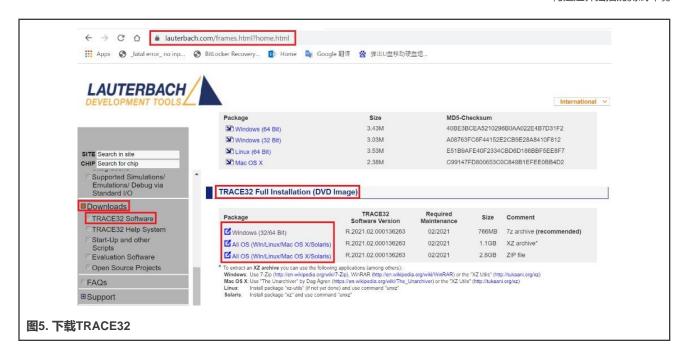

要下载TRACE32,请参见图5。

### 3.2 硬件连接

针对Cortex®-M的µTrace®包括:

- 通用调试器硬件

- 处理器架构特定的调试电缆

#### 图6所示为硬件连接的原理图。

#### 下面列出了给用户的建议:

• 为防止调试器或目标器件损坏,请勿在目标器件带电时插拔调试器。上电/掉电的顺序如下:

- 上电:调试器>目标器件掉电:目标器件>调试器

- 调试器接口包含引脚1。为防止调试器或目标器件损坏,请反复检查其方向。

以LPC55S36 EVK板为例,其硬件连接如图8所示。

- 1. 通过MIPI20T JTAG接口将针对Cortex®-M的µTrace®调试器连接到EVK板。

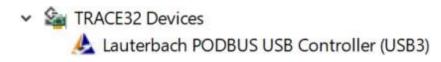

- 2. 通过USB电缆将针对Cortex®-M的µTrace®调试器连接到PC。使用5 V电源适配器为调试器供电。打开PC上的"设备管理器"。 Lauterbach设备会出现在Trace32器件中,如图7所示。如果未显示Lauterbach设备,请检查连接。

图7. Lauterbach设备出现在设备管理器中

3. 要为EVK板上电,请连接EVK板上标有J1或J2的USB端口,如图8所示。

图8. LPC55S36 EVK板的硬件连接

### 3.3 进入边界扫描模式

对于MCU系列,包括LPC55(S)0x、LPC55(S)1x、LPC55(S)2x、LPC55(S)6x等,要进入边界扫描模式,请执行以下步骤:

- 将引脚 PO 2 (TRST) 和 PO 11 (SWCLK) 连接至电源,将引脚 PO 12 (SWDIO) 连接至接地。

- 按住 ISP(PIO0\_5) 按钮 (PIO0\_5 = 0)。

- 按住RESET按钮 (复位 = 0)。

- 释放RESET按钮 (复位 = 1)。

- 释放ISP按钮 (PIO0\_5 = 1)。

- 断开引脚 PO 2 (TRST) 和 PO 11 (SWCLK) 与电源的连接,并断开引脚 PO 12 (SWDIO) 与接地的连接。

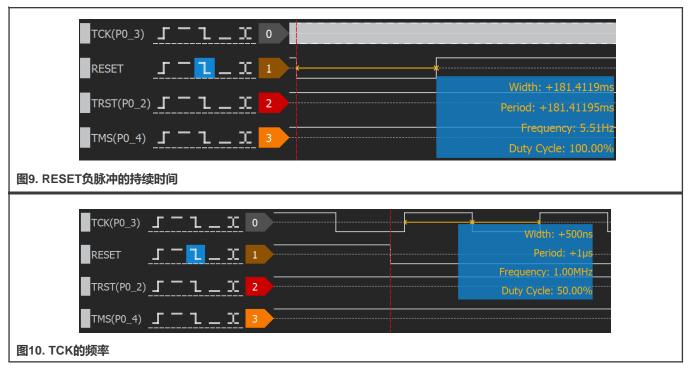

LPC55(S)3x进入边界扫描模式的方式与0x、1x、2x和6x等其他LPC55(S)xx系列不同。要使LPC55(S)3x进入边界扫描模式,请执行以下步骤:

- 向 PO 3 (TCK) 施加一个频率为1 MHz (大于等于500 KHz)、**占空比为50%**的矩形信号。信号发生器可提供该信号。

- 将引脚 PO 2 (TRST) 和 PO 4 (TMS) 与**电源**连接。

- 将RESET引脚拉低保持在低电平状态超过5.5 µS, 然后将RESET引脚释放为高电平。

- 将矩形信号从 PO 3 (TCK) 移除。这一步非常重要。

图9和图10所示为LPC553x进入边界扫描的时序。RESET负脉冲的持续时间为181 ms,满足大于5.5 μs的条件,如图9所示。 **TCK**的频率为1 MHz,满足大于500 KHz的条件,如图10所示。

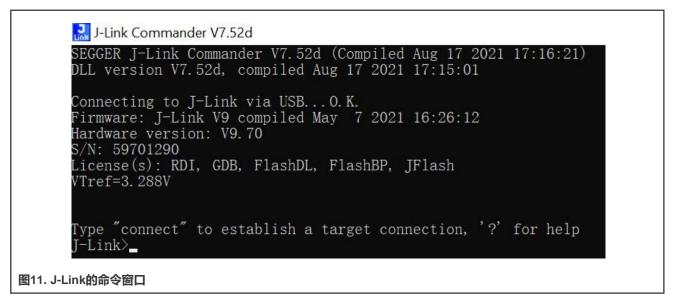

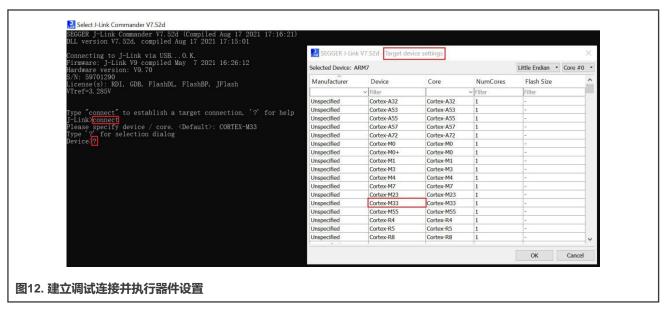

在执行完上述顺序进入边界扫描模式后,使用一个硬件调试器(如Jlink)检查地址为0x50020004的字节内容,以确定 LPC55(S)xx是否真正进入了边界扫描模式。如果**0x50020004**寻址的字节为**0x07**,则芯片处于边界扫描模式。下面以LPC55S36为例介绍这一过程。

- 使用Jlink调试器将LPC55S36 EVK板上的SWD端口连接到PC的USB端口。

- 打开J-Link的命令窗口。图11所示为其操作界面。

- 输入connect,以在J-Link的命令窗口和LPC55S36之间建立连接。

- 输入?, 弹出目标器件设置对话框, 如图12所示。选择Cortex-M33。

• 选择调试接口。在本示例中为SWD。

11 / 24

```

J-Link Commander V7.52d

Connecting to J-Link via USB...O.K.

Firmware: J-Link V9 compiled May 7 2021 16:26:12

Hardware version: V9.70

S/N: 59701290

License(s): RDI, GDB, FlashDL, FlashBP, JFlash

VTref=3.285V

Type "connect" to establish a target connection, '?' for help

J-Link>connect

Please specify device / core. <Default>: CORTEX-M33

Type '?' for selection dialog

Device>?

Please specify target interface:

J) JTAG (Default)

S) SWD

F) FINE

I) ICSP

C) C2

T) cJTAG

TIF>S.

图13. 将目标接口指定为SWD

```

• 指定目标接口速度。在本例中使用默认值。要继续,请按回车键。

```

J-Link Commander V7.52d

SEGGER J-Link Commander V7.52d (Compiled Aug 17 2021 17:16:21)

DLL version V7.52d, compiled Aug 17 2021 17:15:01

Connecting to J-Link via USB...O.K.

Firmware: J-Link V9 compiled May 7 2021 16:26:12

Hardware version: V9.70

S/N: 59701290

License(s): RDI, GDB, FlashDL, FlashBP, JFlash

VTref=3.280V

Type "connect" to establish a target connection, '?' for help

J-Link>connect

Please specify device / core. <Default>: CORTEX-M33

Type '?' for selection dialog

Device>

Please specify target interface:

J) JTAG (Default)

S) SWD

T) cJTAG

Specify target interface speed [kHz]. <Default>: 4000 kHz

Speed>_

you can type your desired speed or use

default speed by press enter

图14. 指定目标接口速度

```

如何基于µTrace和Trace32对LPC55(S)xx进行边界扫描,第0版 — 2022年1月7日

• 在正常模式下, 检查地址0x50020004处的字节值。在本例中为0x01。

```

Connecting to target via SWD

Found SW-DP with ID 0x6BA02477

DPIDR: 0x6BA02477

Scanning AP map to find all available APS

AP[1]: Stopped AP scan as end of AP map has been reached

AP[0]: AHB-AP (IDR: 0x84770001)

Iterating through AP map to find AHB-AP to use

AP[0]: Core found

AP[0]: AHB-AP ROM base: 0x500FE000

CPUID register: 0x410FD214. Implementer code: 0x41 (ARM)

Feature set: Mainline

Found Cortex-M33 r0p4, Little endian.

FPUnit: 8 code (BP) slots and 0 literal slots

Sccurity extension: not implemented

Coresight components:

ROMTDb[0] E E00F5000

ROMTDb[0] E E00F5000

ROMTDb[0] E E00F5000

ROMTDb[1] E E00F5000

ROMTDb[1] [1]: E000E000, CID: B105100D, PID: 000BBD21 Cortex-M33

ROMTDb[1] [1]: E000E000, CID: B105900D, PID: 000BBD21 DWT

ROMTDb[1] [2]: E0002000, CID: B105900D, PID: 000BBD21 ITM

ROMTDb[1] [3]: E0002000, CID: B105900D, PID: 000BBD21 ITM

ROMTDb[1] [3]: E0041000, CID: B105900D, PID: 000BBD21 ITM

ROMTDb[1] [6]: E0041000, CID: B105900D, PID: 000BBD21 ETM

ROMTDb[1] [6]: E0041000, CID: B105900D, PID: 000BBD21 ETM

ROMTDb[1] [6]: E0040000, CID: B105900D, PID: 000BBD21 Cortex-M33

COrtex-M33 identified. — memory check command

J-Link/mems 0x50020004 1

50020004 = 01]

J-Link/mems 0x50020004处的字节值

```

• 让LPC55S36进入边界扫描模式,并检查地址0x50020004处的字节值。在边界扫描模式下,为0x07。

```

Connecting to target via SWD

Found SM-DP with ID 0x6BA02477

DPIDR: 0x6BA02477

AP map detection skipped. Manually configured AP map found.

AP[0]: AHB-AP (IDR: Not set)

AP[0]: Core found

AP[0]: Core found

AP[0]: AFR AR BOM base: 0xE00FE000

CPUID register: 0x410FD214. Implementer code: 0x41 (ARM)

Feature set: Mainline

Found Cortex-M33 rop4. Little endian.

FPUnit: 8 code (BP) slots and 0 literal slots

Security extension: not implemented

Coresight components:

ROWTBI[0] @ E00FB000

ROWTBI[0] [0]: E00FB000

ROWTBI[0] [0]: E00FB000

ROWTBI[1] [0]: E00FB000

ROWTBI[1] [1]: E000FB000

ROWTBI[1] [1]: E000FB000

ROWTBI[1] [2]: E000FB000

ROWTBI[1] [3]: E000FB000

ROWTBI[1] [4]: E00FB000

ROWTBI[1] [5]: E000FB000

ROWTBI[1] [6]: E00GED000, CID: B105900D, PID: 000BBD21 Cortex-M33

ROWTBI[1] [5]: E000FB000

ROWTBI[1] [5]: E000FB000

ROWTBI[1] [5]: E004DB000, CID: B105900D, PID: 000BBD21 FMB

ROWTBI[1] [5]: E004DB000, CID: B105900D, PID: 000BBD21 FMB

ROWTBI[1] [6]: E004DB000, CID: B105900D, PID: 000BBD21 FMB

ROWTBI[1] [6]: E004DB000, CID: B105900D, PID: 000BBD21 Cortex-M33

Cortex-M33 identified.

J-Link>memb 0x50020004 1

S0020004 = 07]

J-Link>

In boundary scan mode,byte value at address 0x50020004 is 0x07

```

## 4 交互式边界扫描测试

要使用针对Cortex®-M的µTrace®调试器和TRACE32软件执行边界扫描测试,请按照以下步骤操作:

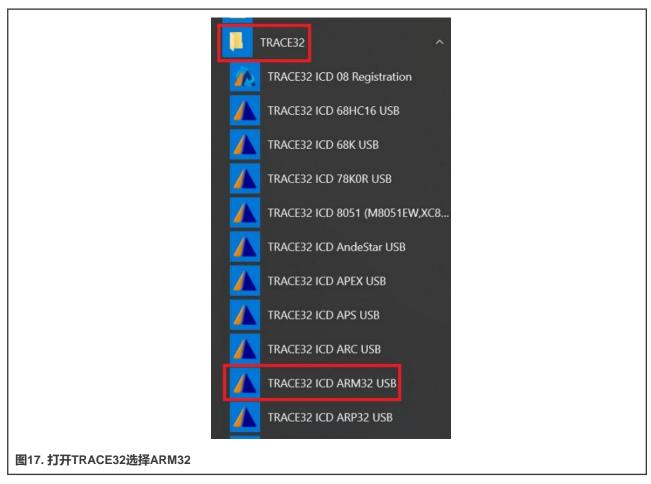

1. 打开TRACE32软件,选择ARM32 USB。

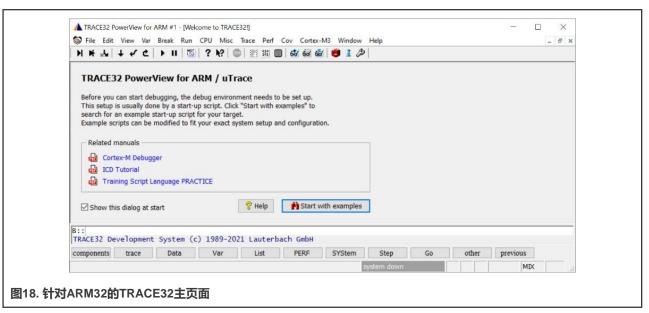

2. 图18所示为TRACE32对于ARM32的主页面。如果主页面底部的状态栏显示"掉电"而不是"系统停止",请检查调试器的电源以及它与EVK板的JTAG接口的连接。

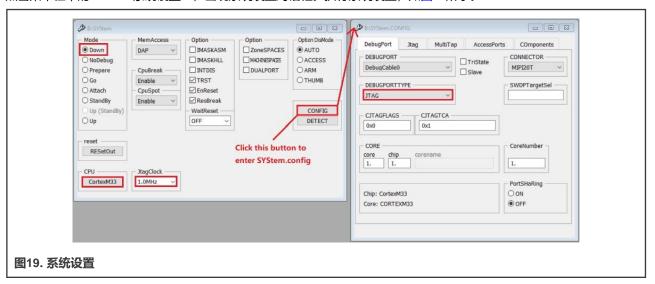

3. 点击菜单栏中的CPU -> 系统设置...,出现系统设置对话框。执行系统设置,如图19所示。

4. 输入以下命令,并在每个命令后按下回车键:

```

BSDL.RESet

BSDL.ParkState Select-DR-Scan

BSDL.state

```

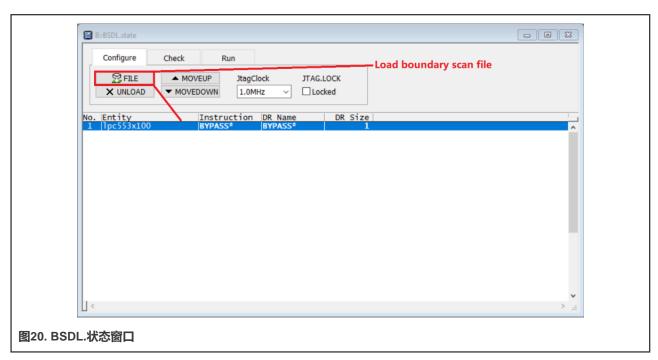

5. 弹出BSDL.状态窗口,如图20所示。单击文件(FILE)按钮,并加载要验证的BSDL文件。

6. 在加载完该文件后,输入如下的命令:

BSDL.SOFTRESET

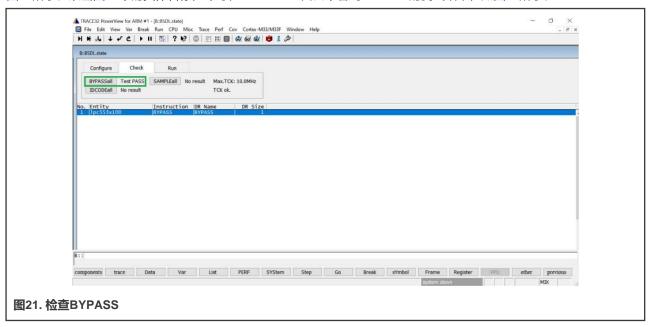

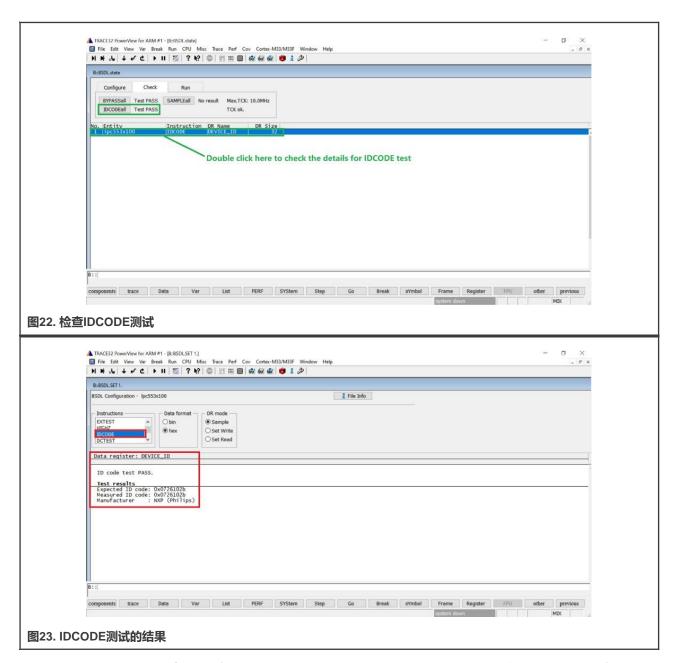

7. 切换到BSDL.状态窗口的"检查"选项卡。要查看两个结果是否都能通过,请单击BYPASSall和IDCODEall,如图21和图22所示。双击图22中的实体名称,即可在BSDL.SET窗口中看到IDCODE的测试结果,如图23所示。

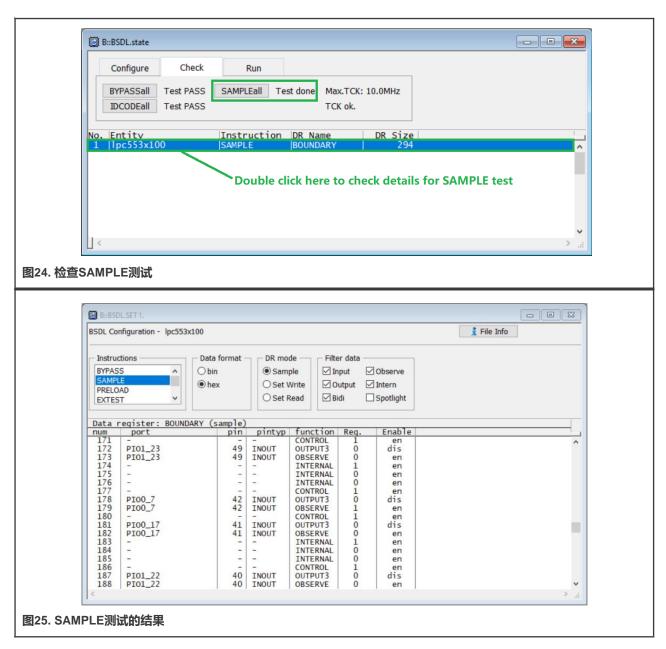

8. 单击SAMPLEall按钮,"无结果"变为("测试已完成")。双击如图24所示的实体名称,在BSDL.SET窗口中可以看到SAMPLE的测试结果,如图25所示。

应用笔记

17 / 24

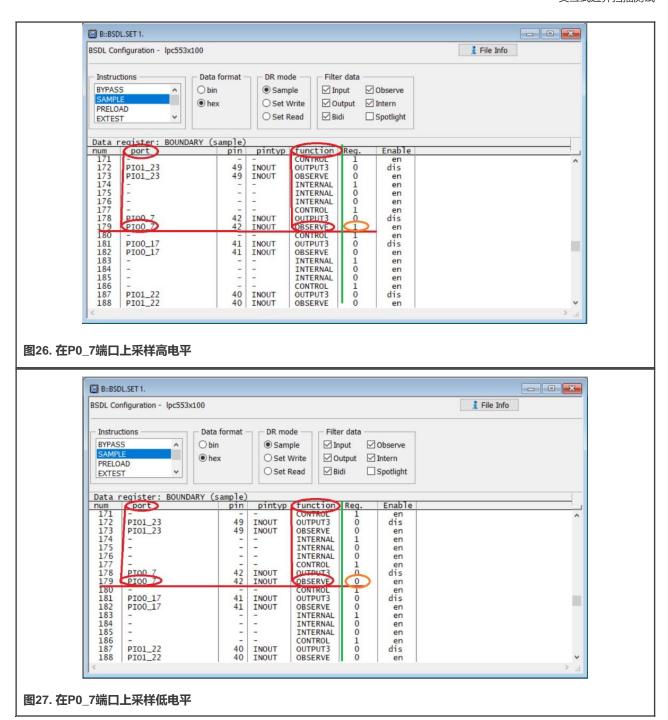

要判断SAMPLE测试是否通过,以引脚PO 7为例,请执行以下步骤:

- a. 给该引脚施加高电平。使用BSDL.RUN命令运行SAMPLE测试。搜索端口为PIOO\_7、功能为OBSERVE的行。读取Reg.列中的寄存器值,值为1,如图26所示。

- b. 给该引脚施加低电平。查看采样结果,结果为 0, 如图27所示。

因此,引脚PO\_7通过了SAMPLE测试。

使用上述方法遍历BSDL文件中定义的所有IO引脚。如果所有的IO引脚都通过了测试,则BSDL的SAMPLE测试通过。

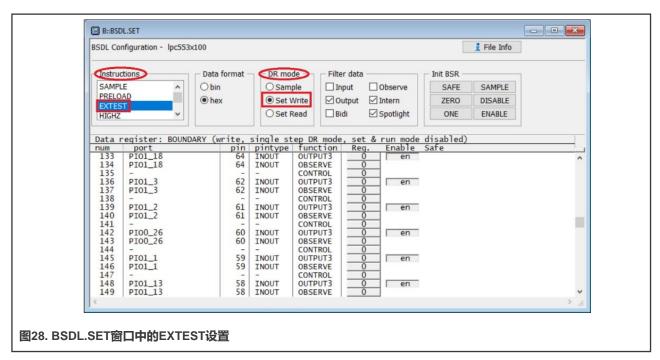

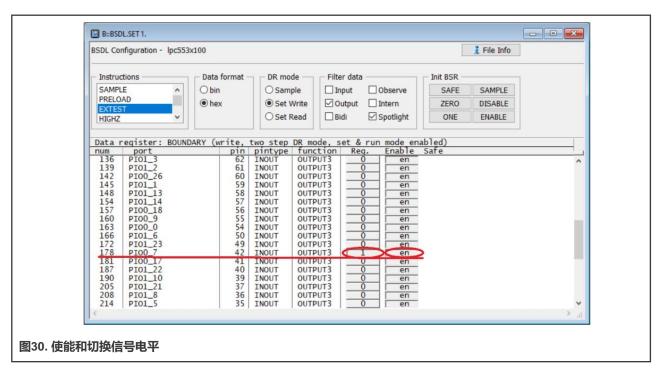

9. 在TRACE32的命令行中输入BSDL.SET命令,弹出BSDL.SET窗口。在"指令"信息栏中单击"EXTEST",在"DR模式"信息栏中选择"设置写入",如图28所示。

切换到BSDL.状态窗口并选中SetAndRun和TwoStepDR,如图29所示。

切换回BSDL.SET窗口。以引脚F0\_7为例说明如何执行EXTTEST。通过单击Enable (使能) 列中的按钮,使能引脚F0\_7的输出。通过单击Reg.列中的按钮,切换该引脚的输出逻辑状态为0或1,如图30所示。使用万用表测量该引脚的逻辑状态是否已真正切换。

使用上述方法遍历BSDL文件中定义的所有IO引脚。如果所有的IO引脚都通过了测试,则BSDL的EXTTEST测试通过。

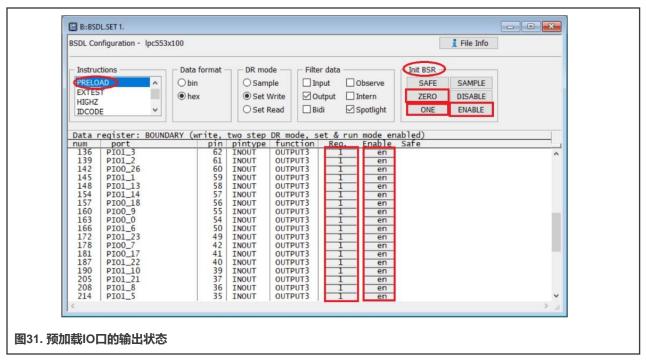

10.将PRELOAD测试与EXTTEST测试结合使用。要使能所有IO引脚的驱动缓冲区并预设为1或0,请单击ONE或ZERO,然后单击Init BSR(初始化BSR)信息栏中的ENABLE(使能),如图31所示。

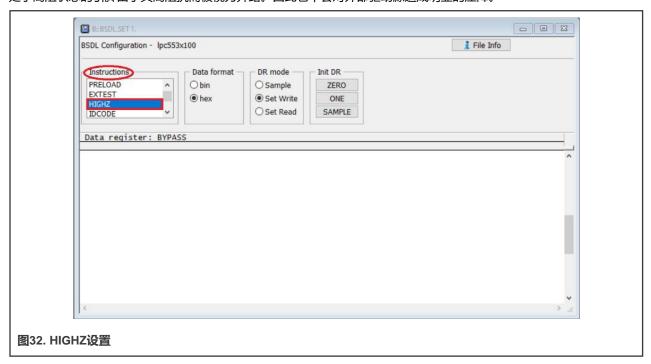

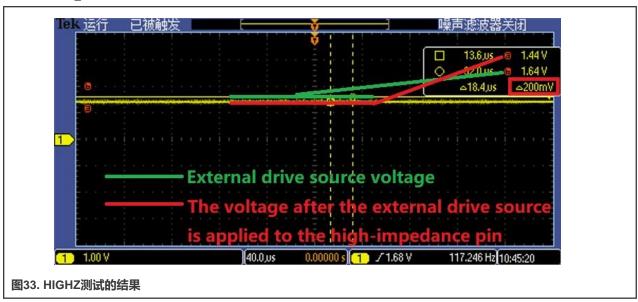

运行PRELOAD测试,然后运行EXTTEST测试。使用万用表测量所有IO引脚的逻辑状态是否与预加载值一致。 使用上述方法遍历BSDL文件中定义的所有IO引脚。如果所有的IO引脚都通过了测试,则BSDL的PRELOAD测试通过。 11.在**BSDL.SET**窗口的指令信息栏中选择**HIGHZ**,然后运行**HIGHZ**测试。BSDL文件中定义的所有IO引脚均处于高阻状态。以3.3 V逻辑为例,给处于高阻状态的引脚施加一个中间电平(例如1.65 V),使用万用表测量该引脚。测量结果为1.65 V,处于高阻状态的引脚由于其高阻抗而被视为开路。因此它不会对外部驱动源造成明显的压降。

HIGHZ测试开始后,所有引脚均处于高阻状态。然后选择一个引脚并施加一个中间电平。以1.64 V为例,使用万用表测量引脚电平。po 7引脚的HIGHZ测试结果如图33所示。

如图33所示,当外部驱动源施加到P0\_7引脚时,仅会导致200 mV的压降。P0\_7确实处于高阻状态。使用上述方法遍历BSDL文件中定义的所有IO引脚。如果所有的IO引脚都通过了测试,则BSDL的**HIGHZ**测试通过。

## 5 让LPC55(S)xx通过边界扫描的SAMPLE测试

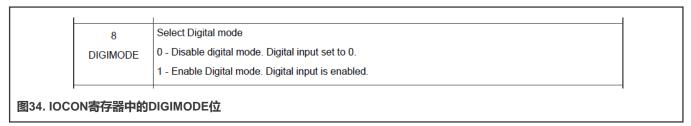

在LPC55(S)xx复位后,某些引脚的数字输入功能被禁用。如果直接在这些引脚上执行SAMPLE测试,这些引脚将不会通过测试。对于LPC55(S)xx,IOCON寄存器的DIGIMODE位控制其数字输入功能,如图34所示。

以LPC55(S)3x为例,说明如何在芯片处于边界扫描模式时使能引脚₽0\_1的数字输入功能。其他引脚的设置方法与此类似。具体步骤如下:

- 1. 打开Jlink命令窗口。

- 2. 对于LPC55(S)3x, IOCON的时钟使能位是地址为0x40000200的AHBCLKCTRL0寄存器中的位13。如果将该位设置为1,则IOCON的时钟被使能。

```

| Cortex_M33 | Identified | Id

```

3. P0\_1引脚对应的IOCON寄存器地址为0x40001004。要使能数字输入功能,请将该寄存器的位8 (DIGIMODE)设置为1。要将引脚设置为浮动输入、下拉输入和上拉输入,请根据需要将位域[4:5]设置为0x00、0x01和0x02。

## 6 自动边界扫描测试

通过以上对交互式边界扫描测试的介绍,有些交互式测试步骤不利于快速测试。为了提高测试效率,TRACE32支持实操脚本。要执行自动边界扫描测试,请编写脚本程序。

在TRACE32的主页面,**"文件"**菜单提供了三个与脚本相关的子菜单项:**新建脚本、打开脚本...**和**运行脚本...**。它们分别用于创建、打开和运行脚本。

#### 下面介绍了一个用于自动化边界扫描测试的脚本示例。

```

;System setup

; Disables the debug mode.

SYStem.Mode Down

SYStem.CPU CortexM33

;Tells TRACE32 the exact CPU type

;used on your target, CPU core of

;LPC553x is Cortex-M33.

SYStem.CONFIG.DEBUGPORTTYPE JTAG ; Specifies which probe cable shall

; be used, here, JTAG is selected

SYStem.JtagClock 1MHz

; Selects JTAG frequency (TCK)

;BSDL Settings

; Initialize the boundary scan engine

BSDL.RESet

BSDL.ParkState Select-DR-Scan

;Set PartState as Select-DR-Scan

;Open BSDL.state window

BSDL.state

;Configure boundary scan chain

BSDL.FILE lpc553x100.bsdl

; your BSDL file name

;Check boundary scan chain

BSDL.SOFTRESET

IF !BSDL.CHECK.BYPASS()

;BYPASS Test

BSDL.BYPASSall

PRINT %ERROR "Bypass test failed"

ENDDO

IF !BSDL.CHECK.IDCODE()

;IDCODE Test

BSDL.IDCODEall

PRINT %ERROR "ID code test failed"

ENDDO

;Perform SAMPLE test

BSDL.SAMPLEall

;Perform EXTTEST

;Pin output settings, you can add other pin output settings

BSDL.SET 1. PORT PIO0 7 0 ;Set PIO0 7 output as 0

BSDL.RUN DR

;Only apply data register settings

; to the boundary scan chain

BSDL.SET 1. IR EXTEST

;Only apply instruction register

; settings to the boundary scan chain

BSDL.RUN

;BSDL run

;Perform HIGHZ test

BSDL.SET 1. IR HIGHZ

;Only apply instruction register

; settings to the boundary scan chain

BSDL.RUN

;BSDL run

```

## 7 修订历史

| 版本号 | 日期        | 说明   |

|-----|-----------|------|

| 第0版 | 2022年1月7日 | 初版发布 |

How To Reach Us

Home Page:

nxp.com.cn

Web Support:

nxp.com.cn/support

**Limited warranty and liability**—Information in this document is provided solely to enable system and software implementers to use NXP products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document. NXP reserves the right to make changes without further notice to any products herein.

NXP makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does NXP assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in NXP data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must be validated for each customer application by customer's technical experts. NXP does not convey any license under its patent rights nor the rights of others. NXP sells products pursuant to standard terms and conditions of sale, which can be found at the following address: nxp.com.cn/SalesTermsandConditions.

**Right to make changes** - NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Security — Customer understands that all NXP products may be subject to unidentified or documented vulnerabilities. Customer is responsible for the design and operation of its applications and products throughout their lifecycles to reduce the effect of these vulnerabilities on customer's applications and products. Customer's responsibility also extends to other open and/or proprietary technologies supported by NXP products for use in customer's applications. NXP accepts no liability for any vulnerability. Customer should regularly check security updates from NXP and follow up appropriately. Customer shall select products with security features that best meet rules, regulations, and standards of the intended application and make the ultimate design decisions regarding its products and is solely responsible for compliance with all legal, regulatory, and security related requirements concerning its products, regardless of any information or support that may be provided by NXP. NXP has a Product Security Incident Response Team (PSIRT) (reachable at PSIRT@nxp.com) that manages the investigation, reporting, and solution release to security vulnerabilities of NXP products.

NXP, the NXP logo, NXP SECURE CONNECTIONS FOR A SMARTER WORLD, COOLFLUX, EMBRACE, GREENCHIP, HITAG, ICODE, JCOP, LIFE, VIBES, MIFARE, MIFARE CLASSIC, MIFARE DESFire, MIFARE PLUS, MIFARE FLEX, MANTIS, MIFARE ULTRALIGHT, MIFARE4MOBILE, MIGLO, NTAG, ROADLINK, SMARTLX, SMARTMX, STARPLUG, TOPFET, TRENCHMOS, UCODE, Freescale, the Freescale logo, AltiVec, CodeWarrior, ColdFire, ColdFire+, the Energy Efficient Solutions logo, Kinetis, Layerscape, MagniV, mobileGT, PEG, PowerQUICC, Processor Expert, QorlQ, QorlQ Qonverge, SafeAssure, the SafeAssure logo, StarCore, Symphony, VortiQa, Vybrid, Airfast, BeeKit, BeeStack, CoreNet, Flexis, MXC, Platform in a Package, QUICC Engine, Tower, TurboLink, EdgeScale, EdgeLock, elQ, and Immersive3D are trademarks of NXP B.V. All other product or service names are the property of their respective owners. AMBA, Arm, Arm7, Arm7TDMI, Arm9, Arm11, Artisan, big.LITTLE, Cordio, CoreLink, CoreSight, Cortex, DesignStart, DynamIQ, Jazelle, Keil, Mali, Mbed, Mbed Enabled, NEON, POP, RealView, SecurCore, Socrates, Thumb, TrustZone, ULINK, ULINK2, ULINK-ME, ULINK-PLUS, ULINKpro, µVision, Versatile are trademarks or registered trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. The related technology may be protected by any or all of patents, copyrights, designs and trade secrets. All rights reserved. Oracle and Java are registered trademarks of Oracle and/or its affiliates. The Power Architecture and Power.org word marks and the Power and Power.org logos and related marks are trademarks and service marks licensed by Power.org. M, M Mobileye and other Mobileye trademarks or logos appearing herein are trademarks of Mobileye Vision Technologies Ltd. in the United States, the EU and/or other jurisdictions.

© NXP B.V. 2022.

All rights reserved.

For more information, please visit: http://www.nxp.com.cn

For sales office addresses, please send an email to: salesaddresses@nxp.com

Date of release: 7 January 2022 Document identifier: AN13507