# Freescale Semiconductor White Paper

Document Number: V1CFWP Rev. 0, 07/2006

# Version 1 ColdFire<sup>®</sup> White Paper

# 1 Introduction

### The microcontroller landscape is changing...

The bit boundaries that have traditionally defined MCU-based solutions are blurring as application performance in the 8-bit world is pushing migration upward at the same time reduced cost in the 32-bit segment is enabling increased access for these more-capable devices. Consider the following introductory statement from a recent *Microprocessor Report* article:

"Although Microprocessor Report focuses on higher-end CPUs whose microarchitectures continue to evolve, there's an interesting battle raging among microcontroller vendors. The semiconductor companies that make 32-bit MCUs—such as Atmel, Freescale, Oki, Philips, STMicroelectronics, and others—are fighting over the growing number of customers whose 8- and 16-bit CPUs are hitting a performance limit.

#### Contents

| 1 | Intr | oduction                                      | . 1 |

|---|------|-----------------------------------------------|-----|

|   | 1.1  | Overview                                      | . 4 |

|   | 1.2  | Features                                      | . 9 |

|   | 1.3  | Modes of Operation                            | 10  |

| 2 | Me   | mory Map and Register Definition              |     |

|   | 2.1  | Memory Map                                    |     |

|   | 2.2  | Register Descriptions                         |     |

| 3 | Inst | truction Set Architecture (ISA_C)             | 18  |

| 4 | Exc  | ception Processing Overview                   | 19  |

|   | 4.1  | Exception Stack Frame Definition              |     |

|   | 4.2  | S08 and ColdFire Exception Processing         |     |

|   |      | Comparison                                    | 23  |

|   | 4.3  | Processor Exceptions                          | 24  |

| 5 | Del  | bug Overview                                  | 32  |

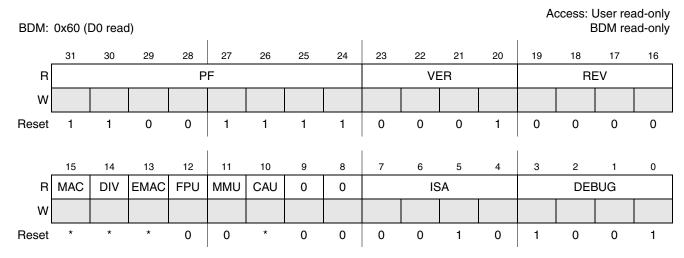

|   | 5.1  | Debug Register Descriptions.                  | 32  |

|   | 5.2  | Background Debug Mode (BDM)                   | 34  |

|   | 5.3  | Processor Status (PST)/Debug Data (DDATA) and |     |

|   |      | Trace Support                                 |     |

| 6 | V1   | ColdFire Core Hardware Details                | 52  |

|   | 6.1  | Core Microarchitecture                        | 52  |

|   | 6.2  | Power Dissipation                             | 65  |

|   | 6.3  | Code Density and Performance                  |     |

|   |      |                                               |     |

© Freescale Semiconductor, Inc., 2006. All rights reserved.

Often overlooked by the microprocessor cognoscenti, the MCU market is enormous: more than \$12 billion in 2005. Of this, more than \$10 billion consisted of 8- and 16-bit devices. However, the relative size and power consumption of 32-bit MCUs have dropped dramatically in recent years, so 32-bit vendors are vigorously attempting to lure system designers away from the smaller devices." ["Freely Scaling from 8 to 32 Bits," J. Scott Gardner, *Microprocessor Report*, May 1, 2006]

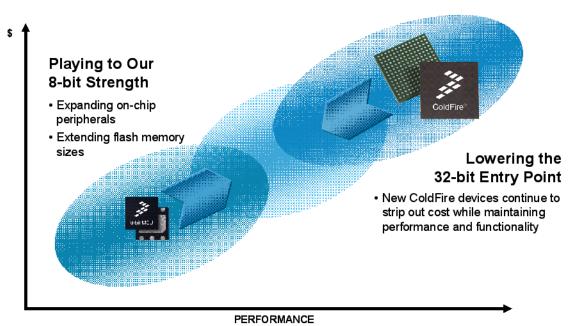

The Freescale Controller Continuum outlines a roadmap that will provide pin-for-pin compatible 8-bit and 32-bit devices that share peripherals and a common set of tools.

Demand for increased performance and functionality continues to push designs up the microcontroller food chain. For 8-bit veterans, Freescale plans expansion at the high-end of the 8-bit portfolio with enhanced peripherals and expanded memory options.

Freescale is continuing to make the transition to 32-bit easier through entry-level ColdFire microcontrollers with connectivity and security features for cost-sensitive applications. Freescale plans to roll out pin-for-pin compatible devices that will allow 8-bit designs to easily upgrade to 32-bit performance while maintaining the same peripheral interfaces during 2007.

Additionally, Freescale plans continued enhancements to its award-winning CodeWarrior<sup>™</sup> Development Studio with automatic code generation, which enables first-time users to create working projects in as few as seven clicks. Freescale is also defining a unified hardware development platform that will provide common board and cable interfaces across architectures. See Figure 1.

Figure 1. Freescale's Controller Continuum

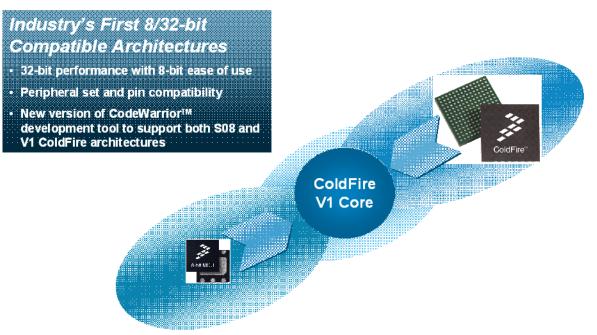

Critical to the controller continuum and the creation of the industry's first 8/32-bit compatible architectures is the Version 1 ColdFire core. As shown in Figure 2, the V1 ColdFire core can be viewed as the missing link bridging the continuum, providing 32-bit performance with 8-bit ease of use with devices that are peripheral set and pin compatible with their 8-bit "little brothers".

Figure 2. V1 ColdFire: Controller Continuum Missing Link

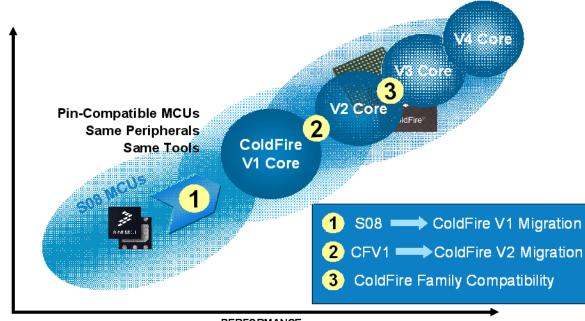

With the V1 ColdFire core providing the link between the 8- and 32-bit worlds, migration to 32-bits is greatly simplified as shown in Figure 3.

PERFORMANCE

Figure 3. Migration to 32-bit: As Easy As 1-2-3

The remainder of this document provides technical details on the V1 ColdFire core and platform, covering its instruction set architecture and debug architecture as well as information on the processor and platform microarchitecture.

# 1.1 Overview

In the creation of the V1 ColdFire core as the missing link in Freescale's Controller Continuum, the following principles guided the development:

- The design followed strict priorities when making core architecture and implementation trade-offs

- Minimal size

- Minimal power dissipation

- Maximum performance

- The peripheral set and pin compatibility with S08 devices had significant impacts on both the core and debug architectural definitions

- A simplified realization of the V2 ColdFire core pipeline was viewed as the appropriate microarchitecture foundation upon which to build the V1 core

## 1.1.1 Instruction Set Architecture

To begin, consider the peripheral set compatibility with S08 devices. Since most of the slave devices are 8-bit peripherals, support for Revision C of the ColdFire instruction set architecture (ISA\_C) was specified. ISA\_C is the most current ColdFire definition and, in particular, includes a number of instructions added as part of the incremental changes to ISA\_B and ISA\_C that improve the handling of 8- and 16-bit data values.

The original definition of the ColdFire Instruction Set Architecture (ISA\_A) was derived from M68K Family opcodes based on extensive analysis of embedded application code. The ISA was optimized for code compiled from high-level languages where the dominant operand size was the 32-bit int type. This approach minimized processor complexity and cost, while providing excellent performance for compiled applications.

After the initial ColdFire compilers were created, developers noted there were certain ISA additions that would enhance both code density as well as overall performance. Additionally, as users implemented ColdFire-based designs into a wide range of embedded systems, they noted certain frequently-used instruction sequences that could be improved by the creation of new instructions.

The original ISA definition minimized the support for instructions referencing byte- and word-sized operands compared to the M68K family. Full support for the move byte (MOVE.B) and move word (MOVE.W) instructions was provided, but the only other opcodes supporting these data types were clear (CLR) and test (TST). Based on the input from compiler writers and users, the ColdFire ISA has been improved with the ISA\_B and ISA\_C extensions. These expanded ISA definitions have improved performance and code density in three areas:

- 1. Enhanced support for byte and word-sized operands through added move and compare operations

- 2. Enhanced support for position-independent code

- 3. Improved support for certain types of bit manipulation operators

Accordingly, the ISA specification for the V1 ColdFire core is defined as ISA\_C since code size and performance associated with byte- and word-sized references to the S08 peripheral set is such an important

factor. For the specifics of the ISA\_C definition, see Chapter 3 of the *ColdFire Programmer's Reference Manual*, especially the instruction set cross-reference presented in Table 3-16.

It should also be noted that careful consideration and study was given to the possibility of supporting a reduced user programming model for the V1 core. In particular, a proposal to reduce the number of general-purpose registers (R*n*) from 16 to 8 was given serious consideration. In this proposal, the number of address (A*n*) and data (D*n*) registers was halved, so that the V1 core would only support the {D0, D1, D6, D7} and {A0, A1, A6, A7} registers. This proposal was driven by the fact that the register file is the largest single structure in the core and a sizable reduction in this function could have an interesting impact on the overall core size. However, in the final analysis it was decided that code compatibility across the entire ColdFire family and the ability to reuse the existing development tools (compilers, debuggers, etc.) was more important than the gate savings achievable through this program-visible redefinition of the register set.

# 1.1.2 Pin Compatibility with HCS08 Devices

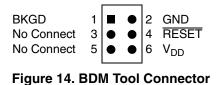

Next, consider the impact of pin compatibility with HCS08 devices. This requirement has significant ramifications on the ColdFire debug architecture, primarily in two distinct areas.

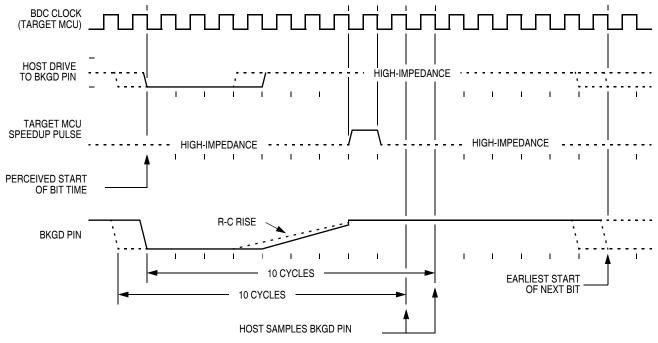

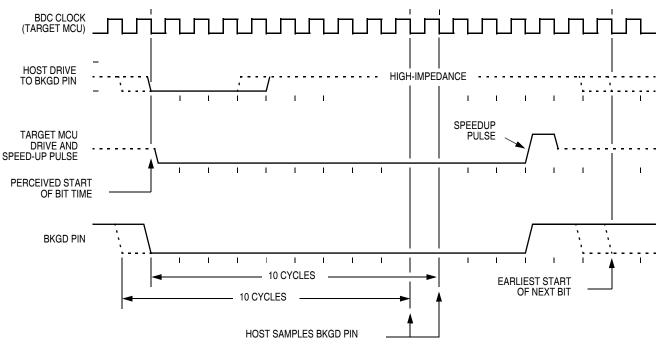

The "classic" Version 2 ColdFire debug architecture specifies a 12-pin interface: 3 pins for the serial background debug mode (BDM) communication channel (clock, data-in, data-out), 1 pin for a breakpoint function, and 8 pins associated with the processor status (PST) and debug data (DDATA) outputs that provide real-time instruction (and optional data) trace capabilities. In contrast, the HCS08 family of devices support all their debug functionality via a single-pin BDM interface. As expected, this reduced interface significantly affects the V1 debug definition. In particular, a single-pin BDM interface for the V1 core means:

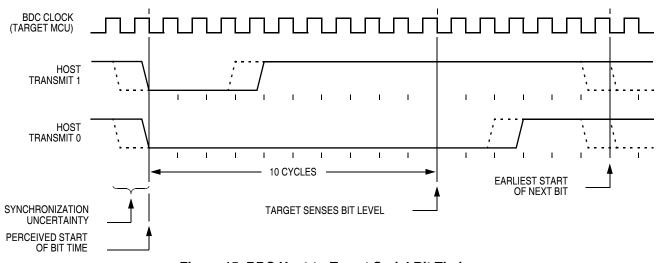

- The traditional 3-pin full-duplex BDM serial communication protocol is replaced with the HCS08 single-pin protocol. The classic ColdFire BDM mechanism is based on 17-bit full-duplex packet protocol. For V1, the HCS08 protocol is fully adopted where all BDM communications utilize a basic 8-bit data packet over a single package pin (BKGD).

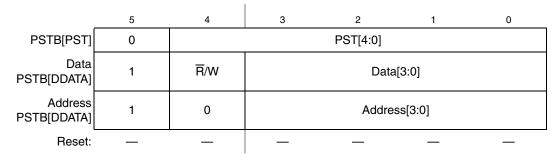

- The reduced debug package pin count also requires that the classic ColdFire program and data trace capabilities be completely redefined for the V1 core. The resulting implementation retains the basic notions of encoded processor status and captured debug data but introduces the notion of PST compression and recording the resulting stream of PST/DDATA values in an on-chip trace buffer. Once recorded in the debug module's trace buffer, the contents can be accessed as BDM-visible registers so the data can be post-processed to provide the needed trace information. Support for the WDDATA instruction, which allows the application code to write directly to the DDATA port, is retained as this provides a simple hardware "printf" capability.

Overall, this approach is significant since it enables a common development environment where the same tools (including the USB cables from the development system to the microcontroller) can be used for both HCS08 or V1 ColdFire devices.

Overview

# 1.1.3 Core Pipeline Organization

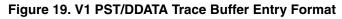

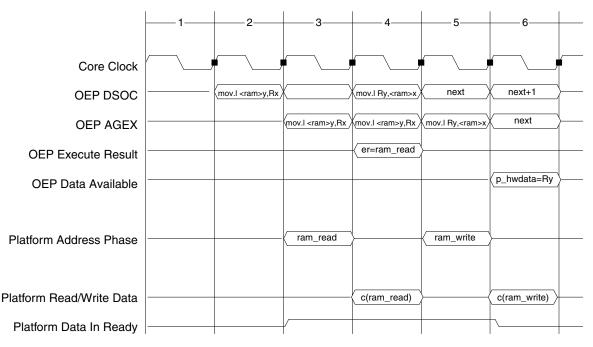

As previously noted, the pipeline organization and structure from the V2 core is significantly leveraged for the V1 implementation. The resulting V1 ColdFire processor core pipeline features two independent, decoupled pipeline structures with a unified bus interface to maximize performance while minimizing core size to strip out cost.

The instruction fetch pipeline (IFP) is a 2-stage pipeline for pre-fetching instructions. The pre-fetched instruction stream is then gated into the 2-stage operand execution pipeline (OEP), which decodes the instruction, fetches the required operands and then executes the required function. Since the IFP and OEP pipelines are decoupled by an instruction buffer which serves as a FIFO queue, the IFP is able to pre-fetch instructions in advance of their actual use by the OEP, thereby minimizing time stalled waiting for instructions.

The instruction fetch pipeline consists of two stages with an optional instruction buffer stage:

| -Instruction Address Generation | IAG Cycle |

|---------------------------------|-----------|

| -Instruction Fetch Cycle        | IC Cycle  |

| -Instruction Buffer             | IB Cycle  |

When the instruction buffer is empty, opcodes are loaded directly from the IC cycle into the operand execution pipeline. If the buffer is not empty, the IFP stores the contents of the fetch cycle in the FIFO queue until it is required by the OEP. In the Version 1 implementation, the instruction buffer contains three 32-bit longwords of storage.

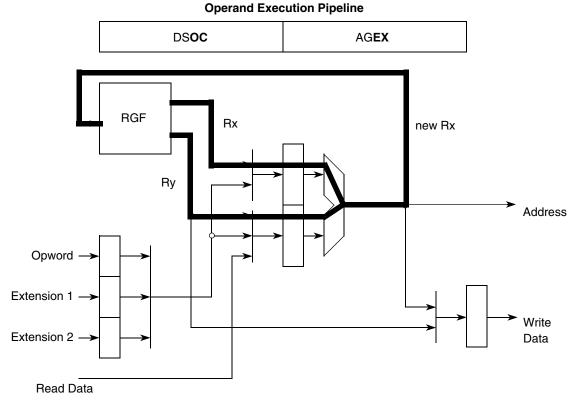

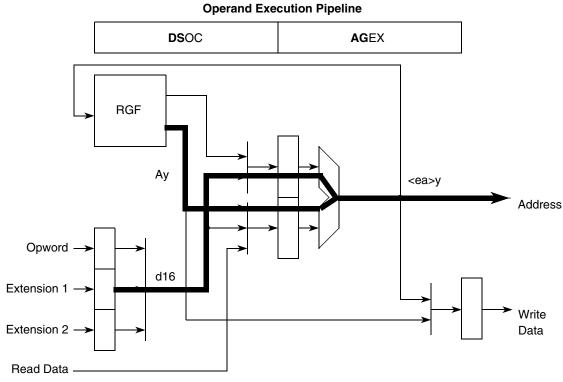

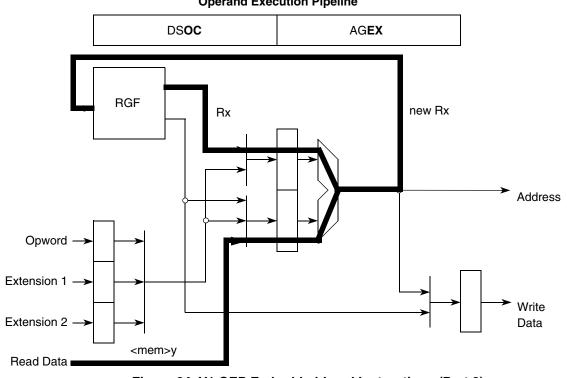

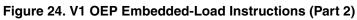

The operand execution pipeline is implemented in a two-stage pipeline featuring a traditional RISC datapath with a dual-read-ported register file (RGF) feeding an arithmetic/logic unit. In this design, the pipeline stages have multiple functions:

| -Decode & Select/Operand Cycle    | DSOC Cycle |

|-----------------------------------|------------|

| -Address Generation/Execute Cycle | AGEX Cycle |

In an effort to minimize gate cost, the address path is reduced from 32 to 24 bits, sufficient for a 16-Mbyte memory map for the V1 devices. Additionally, the V1 core includes design parameters to easily include/exclude various "execute engines" associated with specific instructions. These optional execute engines include an integer divider (DIV), {E}MAC multiply-accumulate engines, and a cryptographic acceleration unit (CAU).

The V1 OEP extends a pipeline optimization associated with 32-bit move (load) instructions to also apply to 8- and 16-bit moves, including the move-with-zero-fill and move-with-sign-extension instructions. The result is improved 2-cycle performance on this very important class of load instructions:

| <pre>mvs.b <mem>y,Dx // byte load with sign-extens</mem></pre> | sion |

|----------------------------------------------------------------|------|

| <pre>mvz.b <mem>y,Dx // byte load with zero-fill</mem></pre>   |      |

| <pre>move.w <mem>y,Rx // word load</mem></pre>                 |      |

| <pre>mvs.w <mem>y,Dx // word load with sign-extens</mem></pre> | sion |

| <pre>mvz.w <mem>y,Dx // word load with zero-fill</mem></pre>   |      |

| move.l <mem>y,Rx // long word</mem>                            |      |

where the source operand is memory, defined by the effective address <mem>y, and the destination is one of the general-purpose registers (Dx is a data register, Rx is either a data or address register). The TST.sz <mem>y instructions also have this same 2-cycle execution time.

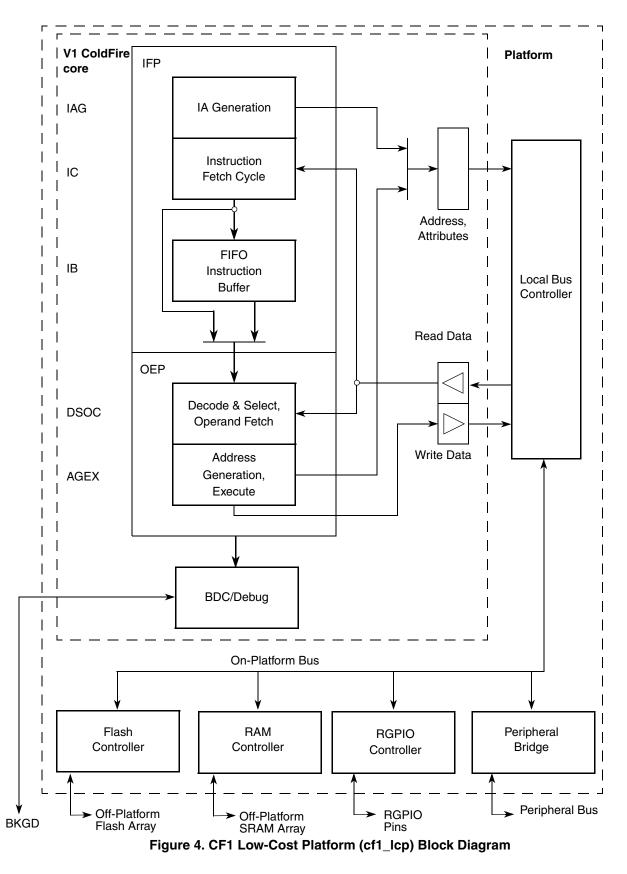

The resulting high-level block diagram of the V1 ColdFire core and the low-cost platform is shown in Figure 4. In this diagram, the following platform modules are included:

- V1 ColdFire CPU with optional execute engines plus the background debug controller (BDC) and debug module

- Local bus controller

- Platform flash memory controller

- Platform RAM memory controller

- Platform-to-peripheral bus controller

- Rapid GPIO (RGPIO) controller

The two platform memory controllers connect to off-platform memory arrays and each supports a wide range of storage capacities. The RGPIO controller connects to chip-level I/O pads and provides high-speed general purpose input/output functionality, since this module is connected to the core's high-speed platform bus. The peripheral bus bridge provides two functions. First, it converts the platform's system bus protocol into the simpler protocol for the slave peripheral modules. Second, it serves as the clock domain boundary, separating the core platform's high-speed domain from the slower peripheral domain. The peripheral bridge supports any *n*:1 clock ratio, where n = 1,2,3,...; for most device implementations, the core platform-to-peripheral speed ratio is fixed at 2:1.

Finally, as shown in Figure 4, the simplest CF1 low-cost platform includes a single bus master, the V1 core. It should also be noted that the low-cost core platform has been constructed to support a second bus mastering device for future SoC definitions. In particular, future V1 devices with other bus master devices with built-in DMA functionality are planned.

In addition to these platform modules, there is an interrupt controller (INTC) which is an off-platform slave module. Because its functionality is important to the core's operation, the features of the INTC are also detailed in this document.

Overview

Version 1 ColdFire White Paper, Rev. 0

# 1.2 Features

The Version 1 ColdFire core and platform include the following features:

- Version 1 ColdFire processor core

- Variable-length RISC architecture and implementation

- Supports Revision C of the ColdFire Instruction Set Architecture

- Supports the standard ColdFire user programming model with 16 general-purpose, 32-bit data and address registers

- Simplified supervisor programming model supporting a supervisor stack pointer, vector base register, and CPU configuration register

- Support for optional execute engines including integer divider, multiply-accumulate units (MAC, EMAC) and cryptography acceleration unit (CAU)

- Programmable response upon detection of certain illegal opcodes and illegal addresses (processor exception or system reset)

- Implementation contains 24-bit address and 32-bit data paths

- Up to 50 MHz core frequency in a low-voltage, low-power 0.25-micron process technology

- 0.85 Dhrystone 2.1 MIPS per MHz performance when executing from flash, 1.05 DMIPS when executing from RAM

- Aggressive clock gating for reducing power dissipation

- Version 1 ColdFire debug support

- Classic ColdFire Debug B+ functionality mapped into the single-pin BDM interface

- Capture of compressed processor status and debug data into on-chip trace buffer provides program (and optional slave bus data) trace capabilities

- On-chip trace buffer provides programmable start/stop recording conditions plus support for continuous or PC-profiling modes

- Real time debug support, with 6 hardware breakpoints (four PC, one address, and one data) that can be configured into a 1- or 2-level trigger with a programmable response (processor halt or interrupt)

- Debug resources are accessible via single-pin BDM interface or the privileged WDEBUG instruction from the core

- Platform memories

- Low-power 2-cycle flash memory for text and read-only data storage

- Flash controller implements address speculation features to reduce effective access time

- Single-cycle RAM on platform's internal high-speed bus

- Write buffer supports zero wait-state response, but does require a dummy write to push contents into RAM before entering any low-power mode

- High-speed GPIO

- Up to 16 bits of rapid GPIO connected to platform's bus for high-speed bit-banging

- Single-cycle accesses with ColdFire core

- Set, clear, toggle registers allow manipulation using simple store instructions

#### Version 1 ColdFire White Paper, Rev. 0

#### Modes of Operation

- Peripheral Bridge

- Converts from platform's system bus to external bus for off-platform slave devices

- Provides a standardized connection scheme for off-platform peripherals

- Support for byte- and word-sized accesses to peripheral space

- Programmable control for buffered writes for improved system performance

- Provides clock domain boundary from high-speed core platform to slower speed slave domain

- Support for *n*:1 platform:peripheral speed ratio, where *n* = 1,2,3, ... (typically fixed at 2:1 speed ratio)

- Interrupt Controller

- Peripheral-mapped off-platform slave module

- 64 byte space located at top end of memory: 0xFF\_FFC0-0xFF\_FFFF

- Programming model accessed via peripheral space

- Encoded interrupt level and vector sent directly to processor core

- Initial support of 30 peripheral I/O interrupt requests plus 7 software interrupt requests

- Fixed association between interrupt request source and level + priority

- 30 I/O requests assigned across seven available levels and nine priorities per level

- Exactly matches S08 interrupt request priorities

- Up to two requests can be re-mapped to the highest non-maskable level + priority

- Unique vector number for each interrupt source

- Default defined as: CF\_Vector\_# = S08\_Vector\_# + 62

- Support for service routine interrupt acknowledge (IACK) read cycles for improved system performance

- Combinatorial path provides wake-up signal from low-power sleep modes

# 1.3 Modes of Operation

The ColdFire Family programming model consists of two register groups, corresponding to the processor privilege level: user and supervisor. Applications executing in the user mode use only the programming model registers in the user group. System software executing in the supervisor mode can access all registers and use the control registers in the supervisor group to perform supervisory functions.

In addition, the V1 core supports the standard ColdFire definition of operating modes, where the processor can be running, stopped, or halted. The processor operating mode status is visible to the external world via the single-pin BDM interface by accessing one of the debug module's configuration/status registers. In particular, ColdFire cores source two bits which define the operating mode, both as output signals as well as program-visible status. These bits are *cpu\_is\_stopped* and *cpu\_is\_halted* and the operating mode is defined as:

| Core Mode | cpu_is_stopped | cpu_is_halted |

|-----------|----------------|---------------|

| Running   | 0              | 0             |

| Stopped   | 1              | 0             |

| Halted    | 0              | 1             |

# 2 Memory Map and Register Definition

This section defines the standardized V1 system memory map and provides an overview of the processor and debug module programming models.

# 2.1 Memory Map

The definition of the system memory map is an important consideration as the platform's local bus controller must be able to quickly route requests to the appropriate slave destination. As the V1 core (or other masters) generate platform bus requests, the local bus controller must be able to very quickly identify the targeted slave so that the request can be properly evaluated and routed to the appropriate device. The net result is the address steering mechanism must be very simple and very fast, since any incremental delay in this function adds directly to the critical timing paths of the core platform design.

Each bus mastering module includes a connection to the input side of the local bus controller for initiating platform bus transactions. As shown in Figure 4, the core platform includes a number of local controllers as well as a bridge controller to the standardized peripheral bus. The slave interface is typically used to access the program-visible registers of the off-platform peripherals.

The platform bus is a 2-stage pipelined protocol, where the bus master drives the address and attribute signals during the first stage (the address phase) and the bus slave responds with data and termination signals in the second stage (the data phase). A single data-phase termination signal is negated to insert wait-states into the slave response, and effectively stall both stages of the bus pipeline. Conversely, the peripheral bus is a simple non-pipelined protocol, where address, attributes, data and termination signals are all valid within a machine cycle.

Recall the memory space defined by the V1 core uses a 24-bit address, providing support for a 16-MByte definition. The resulting Version 1 ColdFire core system memory map is shown in Table 2.

| Address Range         | Destination Slave               | Slave Region Size    |

|-----------------------|---------------------------------|----------------------|

| 0x00_0000 – 0x7F_FFFF | Platform flash                  | 8 Mbytes             |

| 0x80_0000 – 0xBF_FFFF | Platform RAM                    | 4 Mbytes             |

| 0xC0_0000 - 0xDF_FFFF | Platform modules, e.g., RGPIO   | 2 Mbytes             |

| 0xE0_0000 - 0xFF_7FFF | Reserved                        | 2 Mbytes – 32 Kbytes |

| 0xFF_8000 – 0xFF_FFFF | Off-platform Peripheral Modules | 32 Kbytes            |

Table 2. V1 ColdFire System Memory Map

### **Register Descriptions**

Since the physical memory space is often considerably smaller than the allocated space, the actual memory space begins at the lower (starting) address, and creates memory holes in the 16 Mbyte definition. For example, a 128 Kbyte flash resides at address range  $0x00\_0000-0x01\_FFFF$  and an 8 Kbyte RAM resides at  $0x80\_0000-0x80\_1FFF$ . In general, attempted accesses to memory holes generate error terminations and the bus cycle is aborted.

The allowable access types to the different regions in the system memory map also vary. See Table 3.

| Base      | Region      |      | Read |      | Write |      |      |

|-----------|-------------|------|------|------|-------|------|------|

| Address   | negion      | Byte | Word | Long | Byte  | Word | Long |

| 0x00_0000 | Flash       | х    | х    | х    |       |      | х    |

| 0x80_0000 | RAM         | х    | х    | х    | х     | х    | х    |

| 0xC0_0000 | RGPIO       | х    | х    | х    | х     | х    | х    |

| 0xFF_8000 | Peripherals | х    | х    | _    | х     | х    |      |

Table 3. Supported Access Types by Region

Bus cycles which attempt to access a region with an unsupported reference size are terminated with an error.

The use of certain operand addressing modes by the V1 core was also considered during the definition of the system memory map. Specifically, it is suggested that the short-A5-relative addressing mode {addressing register indirect with a 16-bit signed displacement: d16(A5)} be used for data accesses to the RAM. This can often be enabled with a small data area compiler option. It is also suggested that the use of the 16-bit absolute short addressing mode (XXX.W) be used for peripheral accesses. With both suggestions utilized, the resulting code image produces best code density and highest performance.

# 2.2 Register Descriptions

The following sections describe the V1 ColdFire processor core registers in the user and supervisor programming models. The appropriate programming model is selected based on the privilege level (user mode or supervisor mode) of the processor as defined by the S bit of the status register (SR).

The user programming model is the same as the M68000 family microprocessors, consisting of the following registers:

- 16 general-purpose 32-bit registers (D0–D7, A0–A7)

- 32-bit program counter (PC)

- 8-bit condition code register (CCR)

The supervisor programming model is intended to be used only by system control software to implement restricted operating system functions, I/O control, and memory management. All accesses that affect the control features of ColdFire processors are in the supervisor programming model, which consists of registers available in user mode as well as the following control registers:

- 16-bit status register (SR)

- 32-bit supervisor stack pointer (SSP)

- 32-bit vector base register (VBR)

• 32-bit CPU configuration register (CPUCR)

Table 4 provides a summary of the V1 CPU programming model, including the BDM command to access each register.

| BDM<br>Command <sup>1</sup>       | Register                                       | Width<br>(bits) | Access | Reset Value                          | Written with<br>MOVEC <sup>2</sup> | Section/Page |  |  |

|-----------------------------------|------------------------------------------------|-----------------|--------|--------------------------------------|------------------------------------|--------------|--|--|

|                                   | Supervisor/User Registers                      |                 |        |                                      |                                    |              |  |  |

| Read: 0x60<br>Write: 0x40         | Data Register 0 (D0)                           | 32              | R/W    | 0xCF1*_**29                          | No                                 | 2.2.1/-13    |  |  |

| Read: 0x61<br>Write: 0x41         | Data Register 1 (D1)                           | 32              | R/W    | 0x010*0_10*0                         | No                                 | 2.2.1/-13    |  |  |

| Read: 0x6{2-7}<br>Write: 0x4{2-7} | Data Register 2–7 (D2–D7)                      | 32              | R/W    | Undefined                            | No                                 | 2.2.1/-13    |  |  |

| Read: 0x6{8–E}<br>Write: 0x4{8–E} | Address Register 0–6 (A0–A6)                   | 32              | R/W    | Undefined                            | No                                 | 2.2.2/-14    |  |  |

| Read: 0x6F<br>Write: 0x4F         | Supervisor/User A7 Stack Pointer (A7)          | 32              | R/W    | Undefined                            | No                                 | 2.2.3/-14    |  |  |

| Read: 0xEF<br>Write: 0xCF         | Program Counter (PC)                           | 32              | R/W    | Contents of<br>memory @<br>0x00_0004 | No                                 | 2.2.4/-15    |  |  |

| Read: 0xEE<br>Write: 0xCE         | Condition Code Register (CCR)                  | 8               | R/W    | Undefined                            | No                                 | 2.2.5/-15    |  |  |

|                                   | Supervi                                        | sor Regi        | sters  |                                      |                                    |              |  |  |

| Read: 0xEE<br>Write: 0xCE         | Status Register (SR)                           | 16              | R/W    | 0x27                                 | No                                 | 2.2.6/-16    |  |  |

| Read: 0xE0<br>Write: 0xC0         | User/Supervisor A7 Stack Pointer<br>(OTHER_A7) | 32              | R/W    | Contents of<br>memory @<br>0x00_0000 | No                                 | 2.2.3/-14    |  |  |

| Read: 0xE1<br>Write: 0xC1         | Vector Base Register (VBR)                     | 32              | W      | 0x0000_0000                          | Yes;<br>Rc = 0x801                 | 2.2.7/-17    |  |  |

| Read: 0xE2<br>Write: 0xC2         | CPU Configuration Register (CPUCR)             | 32              | W      | 0x0000_0000                          | Yes;<br>Rc = 0x802                 | 2.2.8/-17    |  |  |

### Table 4. Version 1 ColdFire CPU Programming Model

The values listed in this column represent the 8-bit BDM command code used when accessing core registers via the1-pin port. For more information see Section 5.2, "Background Debug Mode (BDM)."

<sup>2</sup> If the given register is written using the MOVEC instruction, the 12-bit control register address (Rc) is also specified.

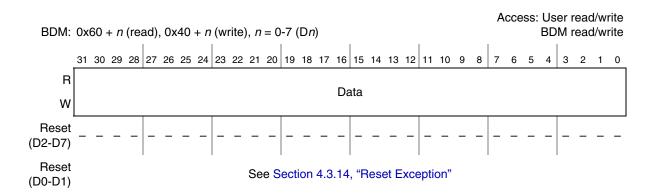

# 2.2.1 Data Registers (D0–D7)

Registers D0–D7 are used as data registers for bit (1-bit), byte (8-bit), word (16-bit) and longword (32-bit) operations; they can also be used as index registers.

### NOTE

Registers D0 and D1 contain hardware configuration details after reset. See Section 4.3.14, "Reset Exception," for more details.

### Version 1 ColdFire White Paper, Rev. 0

**Register Descriptions**

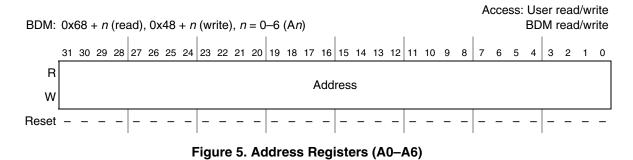

# 2.2.2 Address Registers (A0–A6)

These registers can be used as software stack pointers, index registers, or base address registers; they can also be used for word and longword operations.

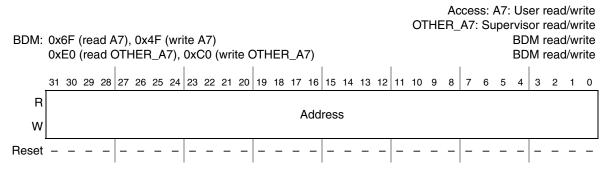

# 2.2.3 Supervisor/User Stack Pointers (A7 and OTHER\_A7)

The ColdFire architecture supports two independent stack pointer (A7) registers—the supervisor stack pointer (SSP) and the user stack pointer (USP). The hardware implementation of these two programmable-visible 32-bit registers does not identify one as the SSP and the other as the USP. Instead, the hardware uses one 32-bit register as the active A7 and the other as OTHER\_A7. Thus, the register contents are a function of the processor operation mode, as shown in the following:

```

if SR[S] = 1

then A7 = Supervisor Stack Pointer

OTHER_A7 = User Stack Pointer

else A7 = User Stack Pointer

OTHER_A7 = Supervisor Stack Pointer

```

The BDM programming model supports direct reads and writes to A7 and OTHER\_A7. It is the responsibility of the external development system to determine, based on the setting of SR[S], the mapping of A7 and OTHER\_A7 to the two program-visible definitions (SSP and USP).

To support the dual stack pointers, the following two supervisor instructions are included in the ColdFire instruction set architecture to load/store the USP:

move.l Ay, USP; move to USP move.l USP, Ax; move from USP

These instructions are described in the ColdFire Family Programmer's Reference Manual.

### NOTE

The USP must be initialized using the move.l Ay, USP instruction before any entry into user mode. The SSP is loaded during reset exception processing with the contents of location  $0x00_0000$ .

Figure 6. Stack Pointer Registers (A7 and OTHER\_A7)

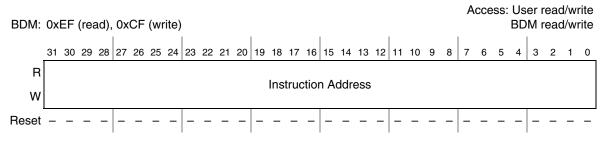

## 2.2.4 Program Counter (PC)

The PC contains the address of the currently executing instruction. During instruction execution and exception processing, the processor automatically increments the contents of the PC or places a new value in the PC, as appropriate. The PC is used as a base address for PC-relative operand addressing.

Figure 7. Program Counter Register (PC)

The PC is initially loaded during reset exception processing with the contents of location 0x00\_0004.

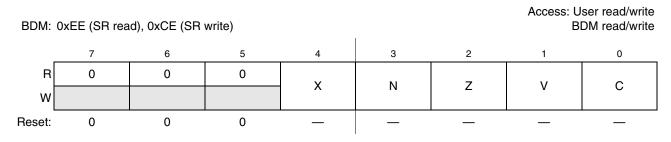

# 2.2.5 Condition Code Register (CCR)

The CCR is the LSB of the processor status register (SR). Bits 4–0 act as indicator flags for results generated by processor operations. The extend bit (X) is also used as an input operand during multiprecision arithmetic computations. The CCR register must be explicitly loaded after reset and before any compare (CMP), Bcc, or Scc instructions are executed.

**Register Descriptions**

### Table 5. CCR Field Descriptions

| Field  | Description                                                                                                                                              |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7–5    | Reserved, should be cleared.                                                                                                                             |

| 4<br>X | Extend condition code bit. Set to the value of the C-bit for arithmetic operations; otherwise not affected or set to a specified result.                 |

| 3<br>N | Negative condition code bit. Set if the most significant bit of the result is set; otherwise cleared.                                                    |

| 2<br>Z | Zero condition code bit. Set if the result equals zero; otherwise cleared.                                                                               |

| 1<br>V | Overflow condition code bit. Set if an arithmetic overflow occurs implying that the result cannot be represented in the operand size; otherwise cleared. |

| 0<br>C | Carry condition code bit. Set if a carry out of the operand msb occurs for an addition, or if a borrow occurs in a subtraction; otherwise cleared        |

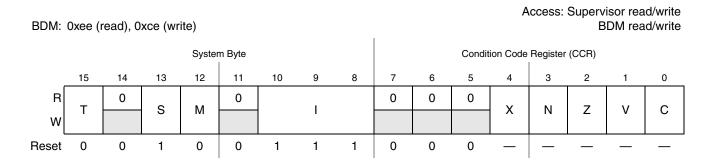

# 2.2.6 Status Register (SR)

The SR stores the processor status and includes the CCR, the interrupt priority mask, and other control bits. In supervisor mode, software can access the entire SR. In user mode, only the lower 8 bits are accessible (CCR). The control bits indicate these states for the processor: trace mode (T bit), supervisor or user mode (S bit), and master or interrupt state (M bit). All defined bits in the SR have read/write access when in supervisor mode. The SR register (actually the CCR) must be explicitly loaded after reset and before any compare (CMP), Bcc, or Scc instructions are executed.

### Table 6. SR Field Descriptions

| Field      | Description                                                                                                                                                                                                                     |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15<br>T    | Trace enable. When set, the processor performs a trace exception after every instruction.                                                                                                                                       |

| 14         | Reserved, should be cleared.                                                                                                                                                                                                    |

| 13<br>S    | Supervisor/user state.<br>0 User mode<br>1 Supervisor mode                                                                                                                                                                      |

| 12<br>M    | Master/interrupt state. This bit is cleared by an interrupt exception, and can be set by software during execution of the <b>RTE</b> or <b>move-to-SR</b> instructions.                                                         |

| 11         | Reserved, should be cleared.                                                                                                                                                                                                    |

| 10–8<br>I  | Interrupt level mask. Defines the current interrupt level. Interrupt requests are inhibited for all priority levels less than or equal to the current level, except the edge-sensitive level 7 request, which cannot be masked. |

| 7–0<br>CCR | Refer to Section 2.2.5, "Condition Code Register (CCR)."                                                                                                                                                                        |

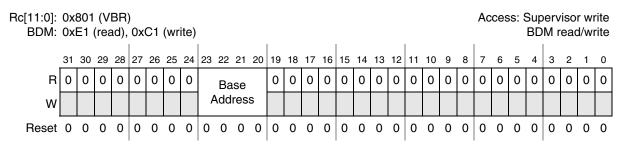

### 2.2.7 Vector Base Register (VBR)

The VBR contains the base address of the exception vector table in memory. To access the vector table, the displacement of an exception vector is added to the value in VBR. The lower 20 bits of the VBR are not implemented by any ColdFire processors; they are assumed to be zero, forcing the table to be aligned on a 1-MByte boundary. In addition, since the V1 ColdFire core supports a 16 Mbyte address space, the upper byte of the VBR is also forced to zero. The VBR can be used to relocate the exception vector table from its default position in the flash memory (address 0x00\_0000) to the base of the RAM (address 0x80\_0000) if needed.

Figure 8. Vector Base Register (VBR)

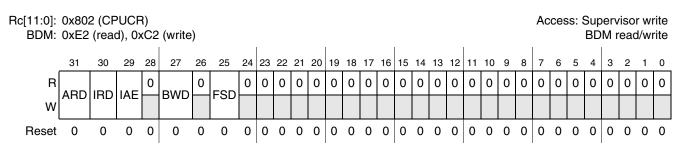

# 2.2.8 CPU Configuration Register (CPUCR)

The CPUCR provides supervisor mode configurability of specific core functionality. Certain hardware features can be enabled/disabled individually based on the state of the CPUCR.

### Figure 9. CPU Configuration Register (CPUCR)

### **Table 7. CPUCR Field Descriptions**

| Field     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31<br>ARD | <ul> <li>Address-related reset disable. Used to disable the generation of a reset event in response to a processor exception caused by an address error, a bus error, an RTE format error or a fault-on-fault halt condition.</li> <li>0 The detection of these types of exception conditions or the fault-on-fault halt condition generate a reset event.</li> <li>1 No reset is generated in response to these exception conditions.</li> </ul>                                                                           |

| 30<br>IRD | Instruction-related reset disable. Used to disable the generation of a reset event in response to a processor exception caused by the attempted execution of an illegal instruction (except for the ILLEGAL opcode), illegal line A, illegal line F instructions, or a privilege violation.<br>0 The detection of these types of exception conditions generate a reset event.<br>1 No reset is generated in response to these exception conditions.                                                                         |

| 29<br>IAE | Interrupt acknowledge (IACK) enable. Forces the processor to generate an IACK read cycle from the interrupt controller during exception processing to retrieve the vector number of the interrupt request being acknowledged. The processor's execution time for an interrupt exception is slightly improved when this bit is cleared.<br>0 The processor uses the vector number provided by the interrupt controller at the time the request is signaled.<br>1 IACK read cycle from the interrupt controller is generated. |

| 28        | Reserved, should be cleared.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 27<br>BWD | <ul> <li>Buffered peripheral bus write disable.</li> <li>Peripheral bus writes are buffered and the platform bus cycle is terminated immediately and does not wait for the peripheral bus termination status.</li> <li>Disables the buffering of peripheral bus writes and does not terminate the platform bus cycle until a registered version of the peripheral bus termination is received.</li> <li>Note: If buffered writes are enabled (BWD = 0), any peripheral bus error status is lost.</li> </ul>                 |

| 26        | Reserved, should be cleared.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 25<br>FSD | <ul> <li>Flash speculation disabled. Disables certain performance-enhancing features related to address speculation in the platform flash memory controller.</li> <li>0 The platform flash controller tries to speculate on read accesses to improve processor performance by minimizing the exposed flash memory access time. Recall the basic flash access time is two processor cycles.</li> <li>1 Certain flash address speculation is disabled.</li> </ul>                                                             |

| 24–0      | Reserved, should be cleared.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

# 3 Instruction Set Architecture (ISA\_C)

The original ColdFire instruction set architecture (ISA) was derived from the M68000-family opcodes based on extensive analysis of embedded application code. After the initial ColdFire compilers were created, developers identified ISA additions that would enhance both code density and overall performance. Additionally, as users implemented ColdFire-based designs into a wide range of embedded

systems, they identified frequently used instruction sequences that could be improved by the creation of new instructions. This observation was especially prevalent in development environments that made use of substantial amounts of assembly language code.

Table 8 summarizes the instructions added to revision ISA\_A to form revision ISA\_C. For more details see the *ColdFire Family Programmer's Reference Manual*.

| Instruction                  | Description                                                                                                                                                                                                                                                                 |

|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BITREV                       | The contents of the destination data register are bit-reversed; that is, new Dn[31] = old Dn[0], new Dn[30] = old Dn[1],, new Dn[0] = old Dn[31].                                                                                                                           |

| BYTEREV                      | The contents of the destination data register are byte-reversed; that is, new Dn[31:24] = old Dn[7:0],, new Dn[7:0] = old Dn[31:24].                                                                                                                                        |

| FF1                          | The data register, Dn, is scanned, beginning from the most-significant bit (Dn[31]) and ending with the least-significant bit (Dn[0]), searching for the first set bit. The data register is then loaded with the offset count from bit 31 where the first set bit appears. |

| INTOUCH                      | Loads blocks of instructions to be locked in the instruction cache.                                                                                                                                                                                                         |

| MOV3Q.L                      | Moves 3-bit immediate data to the destination location.                                                                                                                                                                                                                     |

| Move from USP<br>Move to USP | Loads and stores user stack pointer                                                                                                                                                                                                                                         |

| MVS.{B,W}                    | Sign-extends the source operand and moves it to the destination register.                                                                                                                                                                                                   |

| MVZ.{B,W}                    | Zero-fills the source operand and moves it to the destination register.                                                                                                                                                                                                     |

| SATS.L                       | Performs a saturation operation for signed arithmetic and updates the destination register depending on CCR[V] and bit 31 of the register.                                                                                                                                  |

| TAS.B                        | Performs an indivisible read-modify-write cycle to test and set the addressed memory byte.                                                                                                                                                                                  |

| Bcc.L                        | Branch conditionally, longword                                                                                                                                                                                                                                              |

| BSR.L                        | Branch to sub-routine, longword                                                                                                                                                                                                                                             |

| CMP.{B,W}                    | Compare, byte and word                                                                                                                                                                                                                                                      |

| CMPA.W                       | Compare address, longword                                                                                                                                                                                                                                                   |

| CMPI.{B,W}                   | Compare immediate, byte and word                                                                                                                                                                                                                                            |

| MOVEI                        | Move immediate, byte and word to Ax with displacement                                                                                                                                                                                                                       |

### Table 8. Instruction Enhancements over Revision ISA\_A

# 4 Exception Processing Overview

Exception processing for ColdFire processors is streamlined for performance. The ColdFire processors differ from the M68K family in that they include:

- A simplified exception vector table

- Reduced relocation capabilities using the vector base register

- A single exception stack frame format

- Use of separate system stack pointers for user and supervisor modes

### **Register Descriptions**

All ColdFire processors use an instruction restart exception model. Exception processing includes all actions from the detection of the fault condition to the initiation of fetch for the first handler instruction. Exception processing is comprised of four major steps.

- 1. The processor makes an internal copy of the SR and then enters supervisor mode by setting the S bit and disabling trace mode by clearing the T bit. The occurrence of an interrupt exception also forces the M bit to be cleared and the interrupt priority mask to be set to the level of the current interrupt request.

- 2. The processor determines the exception vector number. For all faults except interrupts, the processor performs this calculation based on the exception type. For interrupts, the processor performs an interrupt-acknowledge (IACK) bus cycle to obtain the vector number from the interrupt controller if CPUCR[IAE] = 1. The IACK cycle is mapped to special locations within the interrupt controller's address space with the interrupt level encoded in the address. If CPUCR[IAE] = 0, then the processor uses the vector number supplied by the interrupt controller at the time the request was signaled for improved performance.

- 3. The processor saves the current context by creating an exception stack frame on the system stack. As a result, the exception stack frame is created at a 0-modulo-4 address on top of the system stack pointed to by the supervisor stack pointer (SSP). As shown in Figure 10, the processor uses a simplified fixed-length stack frame for all exceptions. The exception type determines whether the program counter placed in the exception stack frame defines the location of the faulting instruction (fault) or the address of the next instruction to be executed (next).

- 4. The processor calculates the address of the first instruction of the exception handler. By definition, the exception vector table is aligned on a 1 Mbyte boundary. This instruction address is generated by fetching an exception vector from the table located at the address defined in the vector base register. The index into the exception table is calculated as (4 × vector number). Once the exception vector has been fetched, the contents of the vector determine the address of the first instruction of the desired handler. After the instruction fetch for the first opcode of the handler has been initiated, exception processing terminates and normal instruction processing continues in the handler.

All ColdFire processors support a 1024-byte vector table aligned on any 1 Mbyte address boundary (see Table 9). For the CF1 core, the only practical locations for the vector table are based at 0x00\_0000 in the flash or 0x80\_0000 in the RAM. The table contains 256 exception vectors; the first 64 are defined by Freescale and the remaining 192 are user-defined interrupt vectors. For the V1 ColdFire core, the table is partially populated with the first 64 reserved for internal processor exceptions, while vectors 64-102 are reserved for the peripheral I/O requests and the 7 software interrupts. The IRQ assignments are device-specific as they depend on the exact set of peripherals for any given device.

| Vector<br>Number(s) | Vector<br>Offset (Hex) | Stacked<br>Program<br>Counter | Assignment                       |

|---------------------|------------------------|-------------------------------|----------------------------------|

| 0                   | 0x000 — Initial su     |                               | Initial supervisor stack pointer |

| 1                   | 0x004                  | —                             | Initial program counter          |

| 2                   | 0x008                  | Fault                         | Access error                     |

| 3                   | 0x00C                  | Fault                         | Address error                    |

#### **Register Descriptions**

| Vector<br>Number(s) | Vector<br>Offset (Hex) | Stacked<br>Program<br>Counter | Assignment                   |

|---------------------|------------------------|-------------------------------|------------------------------|

| 4                   | 0x010                  | Fault                         | Illegal instruction          |

| 5                   | 0x014                  | Fault                         | Divide by zero               |

| 6–7                 | 0x018-0x01C            | —                             | Reserved                     |

| 8                   | 0x020                  | Fault                         | Privilege violation          |

| 9                   | 0x024                  | Next                          | Trace                        |

| 10                  | 0x028                  | Fault                         | Unimplemented line-a opcode  |

| 11                  | 0x02C                  | Fault                         | Unimplemented line-f opcode  |

| 12                  | 0x030                  | Next                          | Debug interrupt              |

| 13                  | 0x034                  | —                             | Reserved                     |

| 14                  | 0x038                  | Fault                         | Format error                 |

| 15–23               | 0x03C-0x05C            | —                             | Reserved                     |

| 24                  | 0x060                  | Next                          | Spurious interrupt           |

| 25–31               | 0x064-0x07C            | —                             | Reserved                     |

| 32–47               | 0x080-0x0BC            | Next                          | Trap # 0-15 instructions     |

| 48–63               | 0x0C0-0x0FC            | —                             | Reserved                     |

| 64–95               | 0x100-0x17c            | Next                          | Reserved for Peripheral IRQs |

| 96                  | 0x180                  | Next                          | Level 7 Software Interrupt   |

| 97                  | 0x184                  | Next                          | Level 6 Software Interrupt   |

| 98                  | 0x188                  | Next                          | Level 5 Software Interrupt   |

| 99                  | 0x18c                  | Next                          | Level 4Software Interrupt    |

| 100                 | 0x190                  | Next                          | Level 3 Software Interrupt   |

| 101                 | 0x194                  | Next                          | Level 2 Software Interrupt   |

| 102                 | 0x198                  | Next                          | Level 1Software Interrupt    |

| 103–255             | 0x19c-0x3FC            | —                             | Reserved; unused for V1      |

Table 9. V1 ColdFire Exception Vector Assignments (continued)

<sup>1</sup> "Fault" refers to the PC of the instruction that caused the exception; "Next" refers to the PC of the next instruction that follows the instruction that caused the fault.

All ColdFire processors inhibit interrupt sampling during the first instruction of all exception handlers. This allows any handler to effectively disable interrupts, if necessary, by raising the interrupt mask level contained in the status register. In addition, the V1 instruction set architecture (ISA\_C) includes an instruction (STLDSR) that stores the current interrupt mask level and loads a value into the SR. This instruction is specifically intended for use as the first instruction of an interrupt service routine that services multiple interrupt requests with different interrupt levels. For more details, see the *ColdFire Family Programmer's Reference Manual*.

**Exception Stack Frame Definition**

# 4.1 Exception Stack Frame Definition

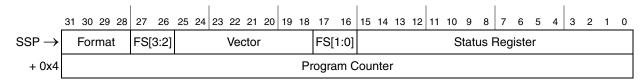

The exception stack frame is shown in Figure 10. The first longword of the exception stack frame contains the 16-bit format/vector word (F/V) and the 16-bit status register, and the second longword contains the 32-bit program counter address.

### Figure 10. Exception Stack Frame Form

The 16-bit format/vector word contains 3 unique fields:

• A 4-bit format field at the top of the system stack is always written with a value of 4, 5, 6, or 7 by the processor indicating a two-longword frame format. See Table 10.

| Original SSP @ Time<br>of Exception, Bits 1:0 | SSP @ 1st Instruction<br>of Handler | Format Field |

|-----------------------------------------------|-------------------------------------|--------------|

| 00                                            | Original SSP - 8                    | 0100         |

| 01                                            | Original SSP - 9                    | 0101         |

| 10                                            | Original SSP - 10                   | 0110         |

| 11                                            | Original SSP - 11                   | 0111         |

Table 10. Format Field Encodings

• There is a 4-bit fault status field, FS[3:0], at the top of the system stack. This field is defined for access and address errors only and written as zeros for all other types of exceptions. See Table 11.

| FS[3:0]      | Definition                               |

|--------------|------------------------------------------|

| 00 <i>xx</i> | Reserved                                 |

| 0100         | Error on instruction fetch               |

| 0101         | Reserved                                 |

| 011-         | Reserved                                 |

| 1000         | Error on operand write                   |

| 1001         | Attempted write to write-protected space |

| 101-         | Reserved                                 |

| 1100         | Error on operand read                    |

| 1101         | Reserved                                 |

| 111x         | Reserved                                 |

Table 11. Fault Status Encodings

• The 8-bit vector number, vector[7:0], defines the exception type and is calculated by the processor for all internal faults and represents the value supplied by the interrupt controller in the case of an interrupt. Refer to Table 9.

# 4.2 S08 and ColdFire Exception Processing Comparison

This section presents a brief summary comparing the exception processing differences between the S08 and ColdFire processor families.

| Attribute                     | S08                                                       | V1 ColdFire                                                                                                             |

|-------------------------------|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|

| Exception Vector Table        | 32, 2-byte entries, fixed location at upper end of memory | 103, 4-byte entries, located at lower end of memory at reset, relocatable with the VBR                                  |

| More on Vectors               | 2 for CPU + 30 for IRQs, reset at upper<br>address        | 64 for CPU + 39 for IRQs, reset at lowest address                                                                       |

| Exception Stack Frame         | 5-byte frame: CCR, A, X, PC                               | 8-byte frame: F/V, SR, PC; General-purpose<br>registers (An, Dn) must be saved/restored by<br>the ISR                   |

| Interrupt Levels              | 1 = f(CCR[I])                                             | 7= f(SR[I]) with automatic hardware support for nesting                                                                 |

| Non-Maskable IRQ Support      | No                                                        | Yes with level 7 interrupts                                                                                             |

| Core-enforced IRQ Sensitivity | No                                                        | Level 7 is edge sensitive, else level sensitive                                                                         |

| INTC Vectoring                | Fixed priorities and vector assignments                   | Fixed priorities and vector assignments, plus<br>any 2 IRQs can be remapped as the highest<br>priority level 6 requests |

| Software IACK                 | No                                                        | Yes                                                                                                                     |

| Exit Instruction from ISR     | RTI                                                       | RTE                                                                                                                     |

Table 12. Exception Processing Comparison

The notion of a software IACK refers to the ability to query the interrupt controller near the end of an interrupt service routine (after the current interrupt request has been cleared) to determine if there are any pending (but currently masked) interrupt requests. If the response to the software IACK's byte operand read is non-zero, then the service routine uses the value as the vector number of the highest pending interrupt request and passes control to the appropriate new handler. This process avoids the overhead of a context restore and RTE instruction execution followed immediately by another interrupt exception and context save. In system environments with high rates of interrupt activity, this mechanism can improve overall performance noticeably.

Emulation of the S08's 1-level IRQ processing can easily be handled by software convention within the ColdFire interrupt service routines. For this type of operation, only two of the seven interrupt levels are used:

- SR[I] = 0 indicates interrupts are enabled

- SR[I] = 7 indicates interrupts are disabled

Recall that ColdFire treats true level 7 interrupts as edge-sensitive, non-maskable requests. Typically, only the IRQ input pin and a low-voltage detect are assigned as level 7 requests. All the remaining interrupt requests (levels 1-6) are masked when SR[I] = 7. In any case, all ColdFire processors guarantee that the first instruction of any exception handler is executed before interrupt sampling resumes. By making the first instruction of the ISR either a store/load status register (STLDSR #0x2700) or a move-to-SR (MOVE.W #2700, SR) instruction, interrupts can be safely disabled until the service routine is exited with an RTE instruction that lowers the SR[I] back to level 0.

Processor Exceptions

# 4.3 Processor Exceptions

# 4.3.1 Access Error Exception

The default operation of the V1 ColdFire processor is the generation of an illegal address reset event if an access error (also known as a bus error) is detected. If CPUCR[ARD] = 1, then the reset is disabled and a processor exception is generated as detailed below.

The exact processor response to an access error depends on the type of memory reference being performed. For an instruction fetch, the processor postpones the error reporting until the faulted reference is needed by an instruction for execution. Therefore, faults that occur during instruction prefetches that are then followed by a change of instruction flow do not generate an exception. When the processor attempts to execute an instruction with a faulted opword and/or extension words, the access error is signaled and the instruction aborted. For this type of exception, the programming model has not been altered by the instruction generating the access error.

If the access error occurs on an operand read, the processor immediately aborts the current instruction's execution and initiates exception processing. In this situation, any address register updates attributable to the auto-addressing modes, {for example, (An)+,-(An)}, have already been performed, so the programming model contains the updated An value. In addition, if an access error occurs during the execution of a MOVEM instruction loading from memory, any registers already updated before the fault occurs contain the operands from memory.

The V1 ColdFire processor uses an imprecise reporting mechanism for access errors on operand writes. Because the actual write cycle may be decoupled from the processor's issuing of the operation, the signaling of an access error appears to be decoupled from the instruction that generated the write. Accordingly, the PC contained in the exception stack frame merely represents the location in the program when the access error was signaled. All programming model updates associated with the write instruction are completed. The NOP instruction can collect access errors for writes. This instruction delays its execution until all previous operations, including all pending write operations, are complete. If any previous write terminates with an access error, it is guaranteed to be reported on the NOP instruction.

# 4.3.2 Address Error Exception

The default operation of the V1 ColdFire processor is the generation of an illegal address reset event if an address error is detected. If CPUCR[ARD] = 1, then the reset is disabled and a processor exception is generated as detailed below.

Any attempted execution transferring control to an odd instruction address (that is, if bit 0 of the target address is set) results in an address error exception.

Any attempted use of a word-sized index register (Xn.w) or a scale factor of eight on an indexed effective addressing mode generates an address error, as does an attempted execution of a full-format indexed addressing mode which is defined by bit 8 of extension word 1 being set.

If an address error occurs on an RTS instruction, the Version 1 ColdFire processor overwrites the faulting return PC with the address error stack frame.

# 4.3.3 Illegal Instruction Exception

The default operation of the V1 ColdFire processor is the generation of an illegal opcode reset event if an illegal instruction is detected. If CPUCR[IRD] = 1, then the reset is disabled and a processor exception is generated as detailed below. There is one special case involving the ILLEGAL opcode (0x4afc); attempted execution of this instruction always generates an illegal instruction exception, regardless of the state of the CPUCR[IRD] bit.

Recall the ColdFire variable-length instruction set architecture supports three instruction sizes: 16, 32, or 48 bits. The first instruction word is known as the operation word (or opword), while the optional words are known as extension word 1 and extension word 2. The opword is further subdivided into three sections: the upper four bits segment the entire ISA into 16 instruction lines, the next 6 bits define the operation mode (opmode), and the low-order 6 bits define the effective address. See Figure 11. The opword line definition is shown in Table 13.

| 15 | 14   | 13 | 12 | 11     | 10 | 9 | 8       | 7                 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----|------|----|----|--------|----|---|---------|-------------------|---|---|---|---|---|---|---|

|    | Line |    |    | OpMode |    |   |         | Effective Address |   |   |   |   |   |   |   |

|    |      |    |    | Mode   |    |   | Registe | r                 |   |   |   |   |   |   |   |

Figure 11. ColdFire Instruction Operation Word (Opword) Format

| Opword[15:12],<br>Line | Instruction Class                                                                                                     |

|------------------------|-----------------------------------------------------------------------------------------------------------------------|

| 0x0                    | Bit manipulation, Arithmetic and Logical Immediate                                                                    |

| 0x1                    | Move Byte                                                                                                             |

| 0x2                    | Move Long                                                                                                             |

| 0x3                    | Move Word                                                                                                             |

| 0x4                    | Miscellaneous                                                                                                         |

| 0x5                    | Add (ADDQ) and Subtract Quick (SUBQ), Set according to Condition Codes (Scc)                                          |

| 0x6                    | PC-relative change-of-flow instructions<br>Conditional (Bcc) and unconditional (BRA) branches, subroutine calls (BSR) |

| 0x7                    | Move Quick (MOVEQ), Move with sign extension (MVS) and zero fill (MVZ)                                                |

| 0x8                    | Logical OR (OR)                                                                                                       |

| 0x9                    | Subtract (SUB), Subtract Extended (SUBX)                                                                              |

| 0xA                    | {E}MAC, Move 3-bit Quick (MOV3Q)                                                                                      |

| 0xB                    | Compare (CMP), Exclusive-OR (EOR)                                                                                     |

| 0xC                    | Logical AND (AND), Multiply Word (MUL)                                                                                |

| 0xD                    | Add (ADD), Add Extended (ADDX)                                                                                        |

| 0xE                    | Arithmetic and logical shifts (ASL, ASR, LSL, LSR)                                                                    |

| 0xF                    | Floating-point Instructions, Cache Push (CPUSHL), Write DDATA (WDDATA), Write Debug (WDEBUG)                          |

### Table 13. ColdFire Opword Line Definition

#### **Processor Exceptions**

In the original M68K ISA definition, lines A and F were effectively reserved for user-defined operations (line A) and co-processor instructions (line F). Accordingly, there are two unique exception vectors associated with illegal opwords in these two lines.

Any attempted execution of an illegal 16-bit opcode (except for line-A and line-F opcodes) generates an illegal instruction exception (vector 4). Additionally, any attempted execution of any illegal line-A or line-F opcode generates their unique exception types, vector numbers 10 and 11, respectively. ColdFire cores do not provide illegal instruction detection on the extension words on any instruction, including MOVEC.

The V1 ColdFire processor also detects two special cases involving illegal instruction conditions:

- 1. If execution of the STOP instruction is attempted and neither low-power stop nor wait modes are enabled, then the processor signals an illegal instruction.

- 2. If execution of the HALT instruction is attempted and BDM is not enabled (XCSR[ENBDM] = 0), then the processor signals an illegal instruction.

In both cases, the processor response is then dependent on the state of CPUCR[IRD]—either a reset event or a processor exception.

### 4.3.4 Divide-By-Zero

If the optional integer divide execute engine is present, an attempt to divide by zero causes an exception (vector 5, offset = 0x014).

### 4.3.5 **Privilege Violation**

The default operation of the V1 ColdFire processor is the generation of an illegal opcode reset event if a privilege violation is detected. If CPUCR[IRD] = 1, then the reset is disabled and a processor exception is generated as detailed below.

The attempted execution of a supervisor mode instruction while in user mode generates a privilege violation exception. See the *ColdFire Programmer's Reference Manual* for a list of supervisor-mode instructions.

# 4.3.6 Trace Exception

To aid in program development, all ColdFire processors provide an instruction-by-instruction tracing capability. While in trace mode, indicated by setting of the SR[T] bit, the completion of an instruction execution (for all but the STOP instruction) signals a trace exception. This functionality allows a debugger to monitor program execution.

The STOP instruction has the following effects:

- 1. The instruction before the STOP executes and then generates a trace exception. In the exception stack frame, the PC points to the STOP opcode.

- 2. When the trace handler is exited, the STOP instruction is executed, loading the SR with the immediate operand from the instruction.

3. The processor then generates a trace exception. The PC in the exception stack frame points to the instruction after the STOP, and the SR reflects the value loaded in the previous step.

If the processor is not in trace mode and executes a STOP instruction where the immediate operand sets SR[T], hardware loads the SR and generates a trace exception. The PC in the exception stack frame points to the instruction after the STOP, and the SR reflects the value loaded in step 2.

Because ColdFire processors do not support any hardware stacking of multiple exceptions, it is the responsibility of the operating system to check for trace mode after processing other exception types. As an example, consider the execution of a TRAP instruction while in trace mode. The processor will initiate the TRAP exception and then pass control to the corresponding handler. If the system requires that a trace exception be processed, it is the responsibility of the TRAP exception handler to check for this condition (SR[T] in the exception stack frame set) and pass control to the trace handler before returning from the original exception.

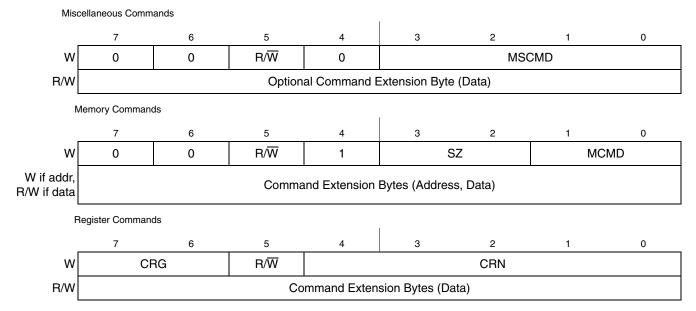

# 4.3.7 Unimplemented Line-A Opcode