## **UM11942** PN5190 instruction layer Rev. 3.9 — 17 June 2024

**User manual**

#### **Document information**

| Information | Content                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Keywords    | PN5190, NFC, NFC frontend, controller, instruction layer                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Abstract    | This document describes the instruction layer commands and responses to work from a host controller, for evaluating the operation of NXP PN5190 NFC frontend controller. PN5190 is a next generation NFC frontend controller. The scope of this document is to describe the interface commands to work with PN5190 NFC frontend controller. For more information on the operation of PN5190 NFC frontend controller, refer to the data sheet and its complementary information. |

## 1 Introduction

## 1.1 Introduction

This document describes the PN5190 Host Interface and the APIs. The physical host interface used in the documentation is SPI. SPI physical characteristic is not considered in the document.

Frame separation and flow control are part of this document.

## 1.1.1 Scope

The document describes the logical layer, instruction code, APIs which are relevant for the customer.

UM11942 PN5190 instruction layer

## 2 Host communication overview

PN5190 has two main modes of operation to communicate with the host controller.

- 1. HDLL-based communication is used when the device is triggered to enter:

- a. Encrypted Secure download Mode to update its firmware

- 2. TLV command-response-based communication (given as an example).

## 2.1 HDLL mode

HDLL mode is used for packet exchange format to work with below IC operating modes:

1. Secure firmware download mode (SFWU), see Section 3

## 2.1.1 Description of HDLL

HDLL is the link layer developed by NXP to ensure a reliable FW download.

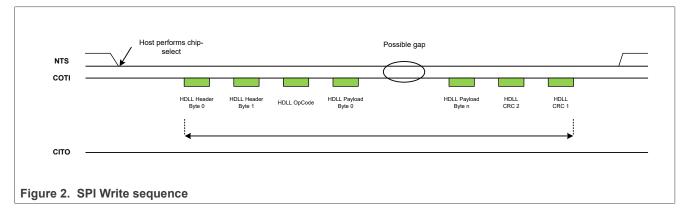

An HDLL message is made of a 2 byte header, followed by a frame, comprising the opcode and the Payload of the command. Each message ends with a 16-bit CRC, as described on the picture below:

| HDLL              | header            |           | Frame             | E          | nd<br>L    |

|-------------------|-------------------|-----------|-------------------|------------|------------|

| –5-bit—           |                   | ← 8-bit → | (L-1) Bytes       | ν<br>→  16 | -bit       |

| RFU Ch S<br>unk B | Packet Length (L) | Op Code   | Payload           | CF         | RC         |

| Byte 0            | Byte 1            | Byte 2    | Byte 3 Byte [1+L] | Byte [2+L] | Byte [3+L] |

Figure 1. HDLL Frame

The HDLL header contains:

- A chunk bit. Which indicates if this message is the only or last chunk of a message (chunk = 0). Or if, at least, one other chunk follows (chunk = 1).

- The length of the Payload coded on 10 bits. So, the HDLL Frame Payload can go up to 1023 Bytes.

The byte order has been defined as big-endian, meaning Ms Byte first.

The CRC16 is compliant to X.25 (CRC-CCITT, ISO/IEC13239) standard with polynomial x^16 + x^12 + x^5 +1 and pre-load value 0xFFFF.

It is calculated over the whole HDLL frame, that is, Header + Frame.

#### Sample C-code implementation:

```

static uint16_t phHal_Host_CalcCrc16(uint8_t* p, uint32_t dwLength)

{

uint32_t i ;

uint16_t crc_new ;

uint16_t crc = 0xffffU;

for (I = 0; i < dwLength; i++)

{

crc new = (uint8 t)(crc >> 8) | (crc << 8 );

}

}

```

UM11942

}

```

crc_new ^= p[i];

crc_new ^= (uint8_t)(crc_new & 0xff) >> 4;

crc_new ^= crc_new << 12;

crc_new ^= (crc_new & 0xff) << 5;

crc = crc_new;

}

return crc;

```

## 2.1.2 Transport mapping over the SPI

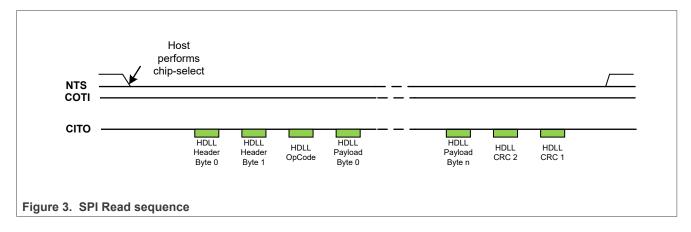

For every NTS assertion, the first byte is always a HEADER (flow indication byte), it can be either 0x7F/0xFF with respect to write/read operation.

## 2.1.2.1 Write Sequence from the host (direction DH => PN5190)

## 2.1.2.2 Read Sequence from the host (Direction PN5190 => DH)

## 2.1.3 HDLL protocol

HDLL is a command-response protocol. All the operations mentioned above are triggered through a specific command and validated based on the response.

Commands and responses follow HDLL message syntax, the command being sent by the device host, the response by the PN5190. The opcode indicates the command and response type.

HDLL-based communications, only used when the PN5190 is triggered to enter the "Secure firmware download" mode.

## 2.2 TLV mode

TLV stands for Tag Length Value.

#### 2.2.1 Frame definition

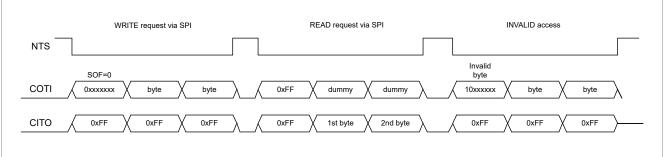

A SPI frame starts with the falling edge of NTS and ends with the rising edge of NTS. SPI is per physical definition full duplex but PN5190 uses SPI in a half-duplex mode. SPI mode is limited to CPOL 0 and CPHA 0 with a max clock speed as specified in [2]. Every SPI frame is composed of a 1 byte header and n-bytes of body.

## 2.2.2 Flow indication

#### Figure 4. Flow indication

The HOST always sends as a first byte the flow indication byte, whether it wants to write or read data from the PN5190.

If there is a read request and no data is available, the response contains 0xFF.

The data after the flow indication byte is one or several messages.

For every NTS assertion, the first byte is always a HEADER (flow indication byte), it can be either 0x7F/0xFF with respect to write/read operation.

## 2.2.3 Message type

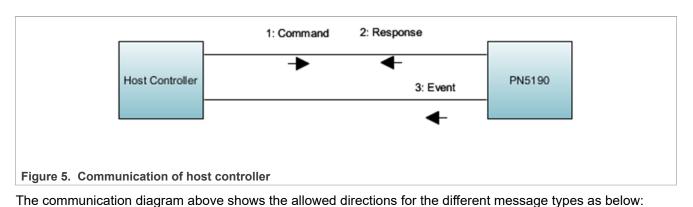

A host controller shall communicate with PN5190 using messages which are transported within SPI frames.

There are three different message types:

- Command

- Response

- Event

## **NXP Semiconductors**

## UM11942

## PN5190 instruction layer

- Command and response.

- Commands are only sent from host controller to PN5190.

- Responses and events are only sent from PN5190 to host controller.

- Command responses are synchronized using the IRQ pin.

- Host can send the commands only when IRQ is low.

- Host can read the response/event only when IRQ is high.

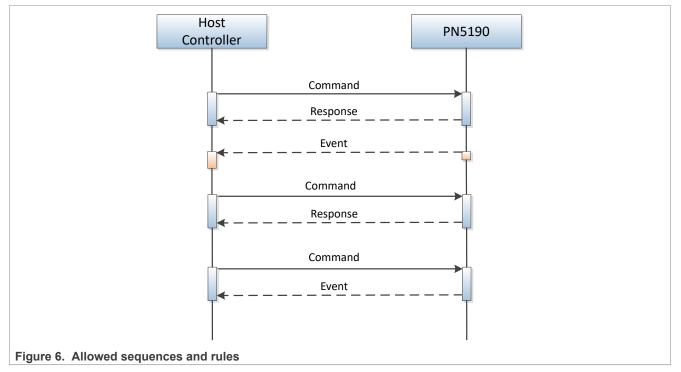

## 2.2.3.1 Allowed sequences and rules

Allowed sequences of command, response, and events

- A command is always acknowledged by a response, or an event, or both.

- Host controller is not allowed to send another command before have not received a response to the previous command.

- Events may be sent asynchronously at any time (NOT interleaved within a command/response pair).

- EVENT messages are never combined with the RESPONSE messages within one frame.

**Note:** The availability of a message (either RESPONSE or EVENT) is signalized with the IRQ going high, from low. IRQ stays high until all the response or event frame is read. Only after IRQ signal is low, the host can send the next command.

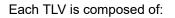

#### 2.2.4 Message format

Each message is coded in a TLV structure with n-bytes payload for each message except for SWITCH\_MODE\_NORMAL command.

| Body                     | TLV1 | X TLV2 // X | TLVn-1 | ( TLVn |

|--------------------------|------|-------------|--------|--------|

| _                        |      |             |        |        |

|                          |      |             |        |        |

| Figure 7. Message format |      |             |        |        |

## Type (T) => 1 byte

Bit[7] Message Type

0: COMMAND or RESPONSE message

#### 1: EVENT message

Bit[6:0]: Instruction code

#### Length (L) => 2 bytes (should be in big-endian format)

Value (V) => N bytes of value/data of the TLV (Command Parameters / Response data) based on Length field (big-endian format)

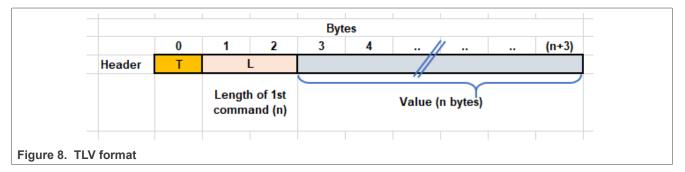

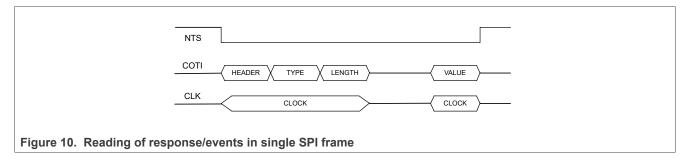

## 2.2.4.1 Split frame

COMMAND message must be sent in one SPI frame.

RESPONSE and EVENT messages can be read in multiple SPI frames, e.g. to read out the length byte.

PN5190 instruction layer

RESPONSE or EVENT messages can be read in single SPI frame but delayed by NO-CLOCK in between, e.g., to read out the length byte.

## 3 IC operating boot mode - secured FW download mode

## 3.1 Introduction

Part of the PN5190 firmware code is permanently stored in the ROM, while the rest of the code and the data are stored in the embedded flash. User data is stored in flash and is protected by anti-tearing mechanisms that ensure the integrity and availability of the data. In order to provide NXPs' customers with features that are compliant with the latest standards (EMVCo, NFC Forum, and so on), both the code and user data in FLASH can be updated.

The authenticity and integrity of the encrypted firmware is protected by asymmetric/symmetric key signature and reverse chained hash mechanism. The first DL\_SEC\_WRITE command contains the hash of the second command and is protected by an RSA signature on the payload of first frame. PN5190 firmware uses the RSA public key to authenticate the first command. The chained hash in each command is used to authenticate the subsequent command, to ensure that the firmware code and data are not accessed by third parties.

The payloads of the DL\_SEC\_WRITE commands are encrypted with an AES-128 key. After authentication of each command, the payload content is decrypted and written to flash by PN5190 firmware.

For NXP firmware, NXP is in charge of delivering new secure firmware updates, together with new User data. The update procedure is equipped with a mechanism to protect the authenticity, integrity, and confidentiality of NXP code and data.

HDLL-based frame packet schema is used for all command and responses for secured firmware upgrade mode. The <u>Section 2.1</u> provides the overview of HDLL frame packet schema used.

PN5190 ICs supports both legacy encrypted secured FW download and hardware crypto assisted encrypted secure FW download protocol depending upon the variant used.

The two types are:

- Legacy secure FW download protocol that works with PN5190 B0/B1 IC version only.

- Hardware crypto assisted secure FW download protocol that works with **PN5190B2 IC** version only, that uses the on-chip hardware crypto blocks

The following sections explain the commands and responses of **Secure firmware download** mode.

## 3.2 How to trigger the "Secured firmware download" mode

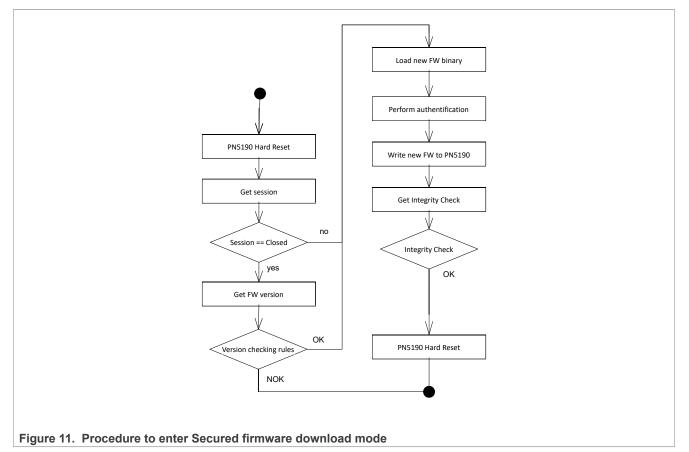

Below diagram, and subsequent steps, show on how to trigger Secured firmware download mode.

UM11942

PN5190 instruction layer

Pre-condition: PN5190 is in Operation state.

Main scenario:

- 1. Entry condition where DWL\_REQ pin is used to enter "Secured firmware download" mode.

- a. Device host pulls DWL\_REQ pin high (valid only if secure firmware update through DWL\_REQ pin) OR

- b. Device host performs a hard-reset to boot the PN5190

- 2. Entry condition where DWL\_REQ pin is not used for entering into "Secured firmware download" mode (pinless download).

- a. Device host performs a hard-reset to boot the PN5190

- b. Device host sends SWITCH\_MODE\_NORMAL (Section 4.5.4.5) to enter into normal application mode.

- c. Now when IC is in normal mode of application, Device host sends SWITCH\_MODE\_DOWNLOAD (<u>Section 4.5.4.9</u>) to enter into secure download mode.

- 3. Device host sends DL\_GET\_VERSION (<u>Section 3.4.4</u>), or DL\_GET\_DIE\_ID (<u>Section 3.4.6</u>), or DL\_GET\_SESSION\_STATE (<u>Section 3.4.5</u>) command.

- 4. Device host reads the current hardware and firmware version, session, Die-id from the device.

- a. Device host checks session status if last download was completed

- b. Device host applies the version checking rules to decide whether to start the download or exit download.

- 5. Device host loads from a file the firmware binary code to be downloaded

- 6. Device host provides a first DL\_SEC\_WRITE (<u>Section 3.4.8</u>) command that contains:

- a. The version of the new firmware,

- b. A 16-byte nonce of arbitrary values used for encryption key obfuscation

- c. A digest value of the next frame,

- d. The digital signature of the frame itself

**PN5190** instruction layer

- 7. The device host loads the secure download protocol sequence to the PN5190 with DL\_SEC\_WRITE (<u>Section 3.4.8</u>) commands

- When the last DL\_SEC\_WRITE (<u>Section 3.4.8</u>) command has been sent, the device host executes the DL\_CHECK\_INTEGRITY (<u>Section 3.4.7</u>) command to check if the memories have been successfully written.

- 9. Device host reads the new firmware version and checks the session status if closed for reporting to the upper layer

- 10. Device host pulls the DWL\_REQ pin to low (if DWL\_REQ pin is used to enter download mode)

- 11. Device host performs hard reset (toggling VEN pin) on the device to reboot the PN5190

Post-condition: The firmware is updated; new firmware version number is reported.

## 3.3 Firmware signature and version control

In the PN5190 firmware download mode, a mechanism ensures that only a firmware signed and delivered by NXP will be accepted for NXP firmware.

Following is applicable only for the encrypted secure NXP firmware.

During a download session, a new 16 bits firmware version is sent. It is composed of a major and a minor number:

- Major number: 8 bits (MSB)

- Minor number: 8 bits (LSB)

**Note:** The PN5190 checks if the new major version number is bigger or equal to the current one. If not, the secured firmware download is rejected, and the session is kept closed.

# 3.4 HDLL commands for legacy encrypted download and hardware crypto assisted encrypted download

This section provides the information about the commands and responses that were used for both types of downloads for NXP firmware download.

## 3.4.1 HDLL Command OP codes

Note: HDLL command frames are 4 bytes aligned. Unused payload bytes are left nil.

| PN5190 B0/<br>B1 (Legacy<br>download) | PN5190 B2<br>(Crypto assisted<br>download) | Command Alias        | Description                                                                                    |

|---------------------------------------|--------------------------------------------|----------------------|------------------------------------------------------------------------------------------------|

| 0xF0                                  | 0xE5                                       | DL_RESET             | Performs a soft reset                                                                          |

| 0xF1                                  | 0xE1                                       | DL_GET_VERSION       | Returns the version numbers                                                                    |

| 0xF2                                  | 0xDB                                       | DL_GET_SESSION_STATE | Returns the current session state                                                              |

| 0xF4                                  | 0xDF                                       | DL_GET_DIE_ID        | Returns the die ID                                                                             |

| 0xE0                                  | 0xE7                                       | DL_CHECK_INTEGRITY   | Checks and return the CRCs over the different areas as well as pass/fail status flags for each |

| 0xC0                                  | 0x8C                                       | DL_SEC_WRITE         | Writes <b>x</b> bytes to memory starting at absolute address y                                 |

Table 1. List of HDLL command OP codes

## 3.4.2 HDLL Response Opcodes

**Note:** HDLL response frames are 4 bytes aligned. Unused payload bytes are left nil. Only DL\_OK responses can contain payload values.

Table 2. List of HDLL response OP codes

| Opcode | Response Alias             | Description                     |

|--------|----------------------------|---------------------------------|

| 0x00   | DL_OK                      | Command passed                  |

| 0x01   | DL_INVALID_ADDR            | Address not allowed             |

| 0x0B   | DL_UNKNOW_CMD              | Unknown command                 |

| 0x0C   | DL_ABORTED_CMD             | Chunk sequence is too large     |

| 0x1E   | DL_ADDR_RANGE_OFL_ERROR    | Address out of range            |

| 0x1F   | DL_BUFFER_OFL_ERROR        | Buffer is too small             |

| 0x20   | DL_MEM_BSY                 | Memory busy                     |

| 0x21   | DL_SIGNATURE_ERROR         | Signature mismatch              |

| 0x24   | DL_FIRMWARE_VERSION_ERROR  | Current version equal or higher |

| 0x28   | DL_PROTOCOL_ERROR          | Protocol error                  |

| 0x2A   | DL_SFWU_DEGRADED           | Flash data corruption           |

| 0x2D   | PH_STATUS_DL_FIRST_CHUNK   | First chunk received            |

| 0x2E   | PH_STATUS_DL_NEXT_CHUNK    | Wait for the next chunk         |

| 0xC5   | PH_STATUS_INTERNAL_ERROR_5 | Length mismatch                 |

## 3.4.3 DL\_RESET command

Frame exchange:

PN5190 B0/B1: [HDLL] -> [0x00 0x04 0xF0 0x00 0x00 0x00 0x18 0x5B]

**PN5190 B2:** [HDLL] -> [0x00 0x04 0xE5 0x00 0x00 0x00 0xBF 0xB9]

[HDLL] <- [0x00 0x04 STAT 0x00 CRC16]

The reset prevents the PN5190 from sending the DL\_STATUS\_OK answer. Therefore, only erroneous status can be received.

$\ensuremath{\mathtt{STAT}}$  is the return status.

## 3.4.4 DL\_GET\_VERSION command

Frame exchange:

PN5190 B0/B1: [HDLL] -> [0x00 0x04 0xF1 0x00 0x00 0x06 0xEF]

**PN5190 B2:** [HDLL] -> [0x00 0x04 0xE1 0x00 0x00 0x75 0x48]

[HDLL] <- [0x00 0x08 STAT HW\_V RO\_V MODEL\_ID FM1V FM2V RFU1 RFU2 CRC16]

| The payload frame of the GetVersion response is: |

|--------------------------------------------------|

|                                                  |

| Table 3. Respon                                                                                                        | able 3. Response to the GetVersion command |             |  |  |  |

|------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|-------------|--|--|--|

| Field                                                                                                                  | Byte                                       | Description |  |  |  |

| STAT                                                                                                                   | 1                                          | Status      |  |  |  |

| UM11942 All information provided in this document is subject to legal disclaimers. © 2024 NXP B.V. All rights reserved |                                            |             |  |  |  |

## PN5190 instruction layer

| Field     | Byte | Description                          |

|-----------|------|--------------------------------------|

| HW_V      | 2    | Hardware version                     |

| RO_V      | 3    | ROM code                             |

| MODEL_ID  | 4    | Model ID                             |

| FMxV      | 5-6  | Firmware version (used for download) |

| RFU1-RFU2 | 7-8  | -                                    |

#### Table 3. Response to the GetVersion command ...continued

Expected values of different fields of response and their mapping is as below:

#### Table 4. Expected values of the response of the GetVersion command

| ІС Туре   | HW Version (hex) | ROM Version (hex) | Model ID<br>(hex) | FW Version (hex) |

|-----------|------------------|-------------------|-------------------|------------------|

| PN5190 B0 | 0x51             | 0x02              | 0x00              | хх.уу            |

| PN5190 B1 | 0x52             | 0x02              | 0x00              | хх.уу            |

| PN5190 B2 | 0x53             | 0x03              | 0x00              | хх.уу            |

## 3.4.5 DL\_GET\_SESSION\_STATE command

Frame exchange:

**PN5190 B0/B1:** [HDLL] -> [0x00 0x04 0xF2 0x00 0x00 0xF5 0x33]

**PN5190 B2:** [HDLL] -> [0x00 0x04 0xDB 0x00 0x00 0x00 0x31 0x0A]

[HDLL] <- [0x00 0x04 STAT SSTA RFU CRC16]

The payload frame of the GetSession response is:

#### Table 5. Response to the GetSession command

| Field | Byte | Description                                                                                  |

|-------|------|----------------------------------------------------------------------------------------------|

| STAT  | 1    | Status                                                                                       |

| SSTA  |      | Session state<br>• 0x00: closed<br>• 0x01: open<br>• 0x02: locked (download no more allowed) |

| RFU   | 3-4  |                                                                                              |

## 3.4.6 DL\_GET\_DIE\_ID command

Frame exchange:

**PN5190 B0/B1:** [HDLL] -> [0x00 0x04 0xF4 0x00 0x00 0x00 0xD2 0xAA]

**PN5190 B2:** [HDLL] -> [0x00 0x04 0xDF 0x00 0x00 0xFB 0xFB]

[HDLL] <- [0x00 0x14 STAT 0x00 0x00 0x00 ID0 ID1 ID2 ID3 ID4 ID5 ID6 ID7 ID8 ID9 ID10 ID11 ID12 ID13 ID14 ID15 CRC16]

#### The payload frame of the GetDield response is:

| Field | Byte | Description              |  |

|-------|------|--------------------------|--|

| STAT  | 1    | Status                   |  |

| RFU   | 2-4  |                          |  |

| DIEID | 5-20 | ID of the die (16 bytes) |  |

#### Table 6. Response to the GetDield command

## 3.4.7 DL\_CHECK\_INTEGRITY command

Frame exchange:

**PN5190 B0/B1:** [HDLL] -> [0x00 0x04 0xE0 0x00 0x00 0x00 CRC16]

**PN5190 B2:** [HDLL] -> [0x00 0x04 0xE7 0x00 0x00 0x00 0x52 0xD1]

[HDLL] <- [0x00 0x20 STAT LEN\_DATA LEN\_CODE 0x00 [CRC\_INFO] [CRC32] CRC16]

The payload frame of the CheckIntegrity response is:

#### Table 7. Response to the CheckIntegrity command

| Field      | Byte                                                              |                                                                                                                                                                                            | Value/Description                                                                                       |  |  |

|------------|-------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|--|--|

| STAT       | 1                                                                 | Status                                                                                                                                                                                     |                                                                                                         |  |  |

| LEN_DATA   | 2                                                                 | Total num                                                                                                                                                                                  | Total number of data sections                                                                           |  |  |

| LEN_CODE   | 3                                                                 | Total num                                                                                                                                                                                  | ber of code sections                                                                                    |  |  |

| RFU        | 4                                                                 | Reserved                                                                                                                                                                                   |                                                                                                         |  |  |

| [CRC_INFO] | 5-8                                                               |                                                                                                                                                                                            | 32 bits (little-endian). If a bit is set, the CRC of the corresponding section is OK, otherwise Not OK. |  |  |

|            |                                                                   | Bit                                                                                                                                                                                        | Area integrity status                                                                                   |  |  |

|            |                                                                   | [31:28]                                                                                                                                                                                    | Reserved [3]                                                                                            |  |  |

|            |                                                                   | [27:23]                                                                                                                                                                                    | Reserved [1]                                                                                            |  |  |

|            | [22] Reserved [ <u>3]</u>                                         |                                                                                                                                                                                            | Reserved [3]                                                                                            |  |  |

|            |                                                                   | [21:20]                                                                                                                                                                                    | Reserved [1]                                                                                            |  |  |

|            |                                                                   | [19] RF configuration area (PN5190 B0/B1) [2]<br>Reserved (PN5190 B2) [3]                                                                                                                  |                                                                                                         |  |  |

|            |                                                                   | [18]                                                                                                                                                                                       | Protocol configuration area (PN5190 B0/B1) [2]<br>RF configuration area (PN5190 B2) [2]                 |  |  |

|            |                                                                   | [17]                                                                                                                                                                                       | Reserved (PN5190 B0/B1) [3]<br>User configuration area (PN5190 B2) [2]                                  |  |  |

|            |                                                                   | [16:6]                                                                                                                                                                                     | Reserved [3]                                                                                            |  |  |

|            | [5:4] Reserved For PN5190 B0/B1 [3]<br>Reserved For PN5190 B2 [1] |                                                                                                                                                                                            |                                                                                                         |  |  |

|            | [3:0] Reserved [1]                                                |                                                                                                                                                                                            |                                                                                                         |  |  |

| [CRC32]    | 9-136                                                             | CRC32 of the 32 sections. Each CRC is of 4 bytes stored in little-endian format.<br>First 4 bytes of CRC is of bit CRC_INFO[31], next 4 bytes of CRC is of bit CRC_<br>INFO[30] and so on. |                                                                                                         |  |  |

#### Note:

- [1] This bit must be 1 for the PN5190 to function properly (with features and or encrypted FW download).

- [2] This bit is set to 1 by default, but user modified settings invalidate the CRC. No effect on PN5190 functionality..

- [3] This bit value, even if it is 0, is not relevant. This bit value can be ignored..

## 3.4.8 DL\_SEC\_WRITE command

The DL\_SEC\_WRITE command is to be considered in the context of a sequence of secure write commands: the encrypted "secured firmware download" (often referred to as eSFWu).

The secure write command first opens the download session and passes the RSA authentication. The next ones are passing encrypted addresses and bytes to write into the PN5190 Flash. All but the last one contains the next ones hash, therefore informing they are not the last, and cryptographically bonding the sequence frames together.

Other commands (except DL\_RESET and DL\_CHECK\_INTEGRITY) can be inserted between the secured write commands of a sequence without breaking it.

#### 3.4.8.1 First DL\_SEC\_WRITE command

A secured write command is the first one if and only if:

- 1. The frame length is 312 bytes

- 2. No secured write command has been received since last reset.

- 3. The embedded signature is successfully verified by the PN5190.

The response to the first frame command would be as below:

[HDLL] <- [0x00 0x04 STAT 0x00 0x00 0x00 CRC16]

$\ensuremath{\texttt{STAT}}$  is the return status.

**Note:** At least one chunk of data must be written during a eSFWu even though the data written may only be one-byte long. Therefore, the first command will always contain the hash of the next command, since there will at least be two commands.

## 3.4.8.2 Middle DL\_SEC\_WRITE commands

A secured write command is a 'middle one' if and only if:

- 1. The opcode is as described in <u>Section 3.4.1</u> for DL\_SEC\_WRITE command.

- 2. A first secured write command has already been received and successfully verified before

- 3. No reset has occurred since receiving the first secured write command

- 4. The frame length is equal to the data size + header size + hash size: FLEN = <u>SIZE</u> + 6 + 32

- 5. The digest of the whole frame is equal to the hash value received in the previous frame

The response to the first frame command would be as below:

[HDLL] <- [0x00 0x04 STAT 0x00 0x00 0x00 CRC16]

STAT is the return status.

## 3.4.8.3 Last DL\_SEC\_WRITE command

A secured write command is the last one if and only if:

- 1. The opcode is as described in <u>Section 3.4.1</u> for DL\_SEC\_WRITE command.

- 2. A first secured write command has already been received and successfully verified before

#### **PN5190** instruction layer

- 3. No reset has occurred since receiving the first secured write command

- 4. The frame length is equal to the data size + header size: FLEN = SIZE + 6

- 5. The digest of the whole frame is equal to the hash value received in the previous frame

The response to the first frame command would be as below:

[HDLL] <- [0x00 0x04 STAT 0x00 0x00 0x00 CRC16]

STAT is the return status.

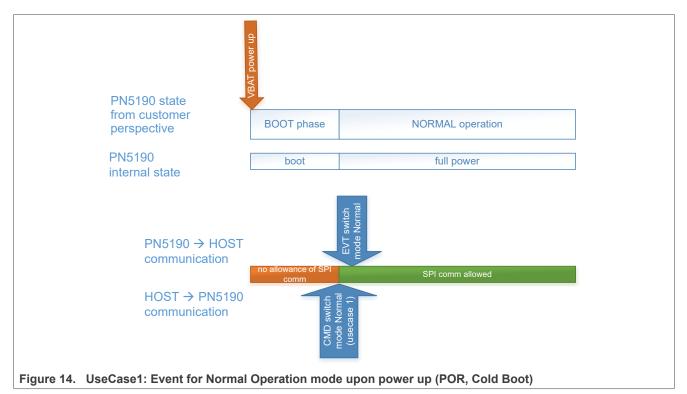

## 4 IC operating boot mode - Normal Operation mode

## 4.1 Introduction

Generally PN5190 IC must be in normal mode of operation to get the NFC functionality from it.

When PN5190 IC boots, it is always waiting for commands to be received from a host to perform operation, unless events generated within PN5190 IC resulted in PN5190 IC boot.

## 4.2 Commands list overview

| Command code | Command name                                       |

|--------------|----------------------------------------------------|

| 0x00         | WRITE_REGISTER                                     |

| 0x01         | WRITE_REGISTER_OR_MASK                             |

| 0x02         | WRITE_REGISTER_AND_MASK                            |

| 0x03         | WRITE_REGISTER_MULTIPLE                            |

| 0x04         | READ_REGISTER                                      |

| 0x05         | READ_REGISTER_MULTIPLE                             |

| 0x06         | WRITE_E2PROM                                       |

| 0x07         | READ_E2PROM                                        |

| 0x08         | TRANSMIT_RF_DATA                                   |

| 0x09         | RETRIEVE_RF_DATA                                   |

| 0x0A         | EXCHANGE_RF_DATA                                   |

| 0x0B         | MFC_AUTHENTICATE                                   |

| 0x0C         | EPC_GEN2_INVENTORY                                 |

| 0x0D         | LOAD_RF_CONFIGURATION                              |

| 0x0E         | UPDATE_RF_CONFIGURATION                            |

| 0x0F         | GET_RF_CONFIGURATION                               |

| 0x10         | RF_ON                                              |

| 0x11         | RF_OFF                                             |

| 0x12         | CONFIGURE TESTBUS_DIGITAL                          |

| 0x13         | CONFIGURE_TESTBUS_ANALOG                           |

| 0x14         | CTS_ENABLE                                         |

| 0x15         | CTS_CONFIGURE                                      |

| 0x16         | CTS_RETRIEVE_LOG                                   |

| 0x17-0x18    | RFU                                                |

| 0x19         | up to FW v2.01: RFU                                |

|              | from FW v2.03 onwards: RETRIEVE_RF_FELICA_EMD_DATA |

| 0x1A         | RECEIVE_RF_DATA                                    |

| 0x1B-0x1F    | RFU                                                |

|              |                                                    |

Table 8. PN5190 command list

User manual

PN5190 instruction layer

| Command code | Command name                                              |

|--------------|-----------------------------------------------------------|

| 0x20         | SWITCH_MODE_NORMAL                                        |

| 0x21         | SWITCH_MODE_AUTOCOLL                                      |

| 0x22         | SWITCH_MODE_STANDBY                                       |

| 0x23         | SWITCH_MODE_LPCD                                          |

| 0x24         | RFU                                                       |

| 0x25         | SWITCH_MODE_DOWNLOAD                                      |

| 0x26         | GET_DIEID                                                 |

| 0x27         | GET_VERSION                                               |

| 0x28         | RFU                                                       |

| 0x29         | up to FW v2.05: RFU                                       |

|              | from FW v2.06 onwards: GET_CRC_USER_AREA                  |

| 0x2A         | up to FW v2.03: RFU                                       |

|              | from FW v2.05 onwards: CONFIGURE_MULTIPLE_TESTBUS_DIGITAL |

| 0x2B-0x3F    | RFU                                                       |

| 0x40         | ANTENNA_SELF_TEST (Not Supported)                         |

| 0x41         | PRBS_TEST                                                 |

| 0x42-0x4F    | RFU                                                       |

## Table 8. PN5190 command list...continued

## 4.3 Response status values

Following are the response status values, that are returned as part of the response from PN5190 after the command is operationalized.

| Table 9. I | PN5190 | response | status | values |

|------------|--------|----------|--------|--------|

|------------|--------|----------|--------|--------|

| Response status                  | Response<br>status value | Description                                                                                             |

|----------------------------------|--------------------------|---------------------------------------------------------------------------------------------------------|

| PN5190_STATUS_SUCCESS            | 0x00                     | Indicates that operation completed successfully                                                         |

| PN5190_STATUS_TIMEOUT            | 0x01                     | Indicates that the operation of the command resulted in timeout                                         |

| PN5190_STATUS_INTEGRITY_ERROR    | 0x02                     | Indicates that the operation of the command resulted in RF data integrity error                         |

| PN5190_STATUS_RF_COLLISION_ERROR | 0x03                     | Indicates that the operation of the command resulted in RF collision error                              |

| PN5190_STATUS_RFU1               | 0x04                     | Reserved                                                                                                |

| PN5190_STATUS_INVALID_COMMAND    | 0x05                     | Indicates that the given command is invalid/not implemented                                             |

| PN5190_STATUS_RFU2               | 0x06                     | Reserved                                                                                                |

| PN5190_STATUS_AUTH_ERROR         | 0x07                     | Indicates that MFC authentication failed (permission denied)                                            |

| PN5190_STATUS_MEMORY_ERROR       | 0x08                     | Indicates that the operation of the command resulted<br>in a programming error or internal memory error |

PN5190 instruction layer

| Table 9. PN5190 response status valuescontinue           Response status | Response<br>status value | Description                                                                                                                                                                                                     |

|--------------------------------------------------------------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PN5190_STATUS_RFU4                                                       | 0x09                     | Reserved                                                                                                                                                                                                        |

| PN5190_STATUS_NO_RF_FIELD                                                | 0x0A                     | Indicates that there no or error in internal RF field presence (applicable only if initiator/reader mode)                                                                                                       |

| PN5190_STATUS_RFU5                                                       | 0x0B                     | Reserved                                                                                                                                                                                                        |

| PN5190_STATUS_SYNTAX_ERROR                                               | 0x0C                     | Indicates that invalid command frame length is received                                                                                                                                                         |

| PN5190_STATUS_RESOURCE_ERROR                                             | 0x0D                     | Indicates that an internal resource error occurred                                                                                                                                                              |

| PN5190_STATUS_RFU6                                                       | 0x0E                     | Reserved                                                                                                                                                                                                        |

| PN5190_STATUS_RFU7                                                       | 0x0F                     | Reserved                                                                                                                                                                                                        |

| PN5190_STATUS_EXTERNAL_RF_FIELD                                          | 0x10                     | In reader mode, it indicates that external RF field is present.<br>In card/target mode, this indicates that external RF is not present during the execution of the command.                                     |

| PN5190_STATUS_RX_TIMEOUT                                                 | 0x11                     | Indicates that data is not received after RFExchange is initiated and RX is timed out.                                                                                                                          |

| PN5190_STATUS_USER_CANCELLED                                             | 0x12                     | Indicates that the present command in-progress is aborted                                                                                                                                                       |

| PN5190_STATUS_PREVENT_STANDBY                                            | 0x13                     | Indicates that PN5190 is prevented to go into Standby mode                                                                                                                                                      |

| PN5190_STATUS_RFU9                                                       | 0x14                     | Reserved                                                                                                                                                                                                        |

| PN5190_STATUS_CLOCK_ERROR                                                | 0x15                     | Indicates that clock to the CLIF did not start                                                                                                                                                                  |

| PN5190_STATUS_RFU10                                                      | 0x16                     | Reserved                                                                                                                                                                                                        |

| PN5190_STATUS_PRBS_ERROR                                                 | 0x17                     | Indicates that the PRBS command returned an error                                                                                                                                                               |

| PN5190_STATUS_INSTR_ERROR                                                | 0x18                     | Indicates that operation of the command is<br>failed (it may include, the error in instruction<br>parameters, syntax error, error in operation itself,<br>pre-requirements for the instruction is not met etc.) |

| PN5190_STATUS_ACCESS_DENIED                                              | 0x19                     | Indicates that access to internal memory is denied                                                                                                                                                              |

| PN5190_STATUS_TX_FAILURE                                                 | 0x1A                     | Indicates that TX over RF is failed                                                                                                                                                                             |

| PN5190_STATUS_NO_ANTENNA                                                 | 0x1B                     | Indicates that no antenna is connected/present                                                                                                                                                                  |

| PN5190_STATUS_TXLDO_ERROR                                                | 0x1C                     | Indicates that there is an error in TXLDO when the VUP is not available and RF is switched ON.                                                                                                                  |

| PN5190_STATUS_RFCFG_NOT_APPLIED                                          | 0x1D                     | Indicates that RF configuration is not loaded when RF is switched ON                                                                                                                                            |

| PN5190_STATUS_TIMEOUT_WITH_EMD_ERROR                                     | 0x1E                     | up to FW 2.01: not expected                                                                                                                                                                                     |

|                                                                          |                          | from FW 2.03 onwards:                                                                                                                                                                                           |

|                                                                          |                          | Indicates that during Exchange with LOG ENABLE<br>BIT is set in FeliCa EMD register, FeliCa EMD Error<br>was observed                                                                                           |

| PN5190_STATUS_INTERNAL_ERROR                                             | 0x7F                     | Indicates that the NVM operation failed                                                                                                                                                                         |

| PN5190_STATUS_SUCCSES_CHAINING                                           | 0xAF                     | Indicates that, furthermore data is pending to be read                                                                                                                                                          |

#### Table 9. PN5190 response status values...continued

## 4.4 Events Overview

There are two ways events are notified to the host.

## 4.4.1 Normal events over IRQ pin

These events are categories as below:

- 1. Always enabled Host is always notified

- Controlled by Host Host is notified, if the respective Event Enable bit is set in the register (EVENT\_ENABLE (01h)).

Low-level interrupts from the peripheral IPs including the CLIF shall be completely handled within the firmware and host shall be notified only of the events listed in the events section.

Firmware implements two event registers as RAM registers that can be written / Read using <u>Section 4.5.1.1</u> / <u>Section 4.5.1.5</u> commands.

The register EVENT\_ENABLE  $(0 \times 01)$  => Enable specific/all event notifications.

The register EVENT\_STATUS  $(0 \times 02)$  => Part of the Event message payload.

Events shall be cleared by the host once the event message is read-out by the host.

Events are asynchronous in nature and are notified to the host, if they are enabled within the EVENT\_ENABLE register.

Following is the list of events that shall be available to the host as part of event message.

#### Table 10. PN5190 events (contents of EVENT\_STATUS)

| Bit - R | lange | Field [1]                   | Always<br>Enabled (Y/N) |

|---------|-------|-----------------------------|-------------------------|

| 31      | 12    | RFU                         | NA                      |

| 11      | 11    | CTS_EVENT [2]               | N                       |

| 10      | 10    | IDLE_EVENT                  | Y                       |

| 9       | 9     | LPCD_CALIBRATION_DONE_EVENT | Y                       |

| 8       | 8     | LPCD_EVENT                  | Y                       |

| 7       | 7     | AUTOCOLL_EVENT              | Y                       |

| 6       | 6     | TIMER0_EVENT                | N                       |

| 5       | 5     | TX_OVERCURRENT_EVENT        | N                       |

| 4       | 4     | RFON_DET_EVENT [2]          | N                       |

| 3       | 3     | RFOFF_DET_EVENT [2]         | N                       |

| 2       | 2     | STANDBY_PREV_EVENT          | Y                       |

| 1       | 1     | GENERAL_ERROR_EVENT         | Y                       |

| 0       | 0     | BOOT_EVENT                  | Y                       |

#### Note:

[1] Note that no two events are clubbed except in case of errors. In case of errors during the operation, functional event (e.g. BOOT\_EVENT, AUTOCALL\_EVENT etc.) and GENERAL\_ERROR\_EVENT will be set.

[2] This event will automatically be disabled after it is posted to the host. The host should enable again these events if it wishes to get these events notified to it.

#### 4.4.1.1 Event message formats

The event message format differs depending upon the occurrences of an event and different state of the PN5190.

Host must read tag (T) and length of the message (L) and then read the corresponding number of bytes as value (V) of the events.

In general, the event message (see Figure 12) contains the EVENT\_STATUS as defined in Table 11 and event data corresponds to the respective event bit set in EVENT\_STATUS.

Note:

For some events, payload does not exist. For e.g. If TIMER0\_EVENT is triggered, only EVENT\_STATUS is provided as part of the event message.

The <u>Table 11</u> also details out whether the event data is present for the corresponding event in the event message.

|        | 0    | 1         | 2                           | 3 | 4      | 5      | 6 | <br> |        | 11. |

|--------|------|-----------|-----------------------------|---|--------|--------|---|------|--------|-----|

| Header | Т    |           | L                           |   | EVENT_ | STATUS |   | EVEN | r_data |     |

|        | 0x80 | (V) = 4 · | of Data<br>+ EVENT<br>\size |   |        |        |   |      |        |     |

|        |      |           |                             |   |        |        |   |      |        |     |

Figure 12. Event message format when no errors occurred

GENERAL\_ERROR\_EVENT may also occur with other events.

In this scenario, the event message (see <u>Figure 13</u>) contains the EVENT\_STATUS as defined in <u>Table 11</u> and GENERAL\_ERROR\_STATUS\_DATA as defined in <u>Table 14</u> and then the event data corresponds to the respective event bit set in EVENT\_STATUS as defined in <u>Table 11</u>.

| 0        | 1 2                                                  | 3 4 5 6      | //         |                      |

|----------|------------------------------------------------------|--------------|------------|----------------------|

| Header T | L                                                    | EVENT_STATUS | EVENT_DATA | GENERAL_ERROR_STATUS |

| 0x80     | Length of Data<br>(V) = 0x08 +<br>EVENT_DATA<br>size |              | 17         | 4 bytes              |

Figure 13. Event message format when an error occurred

#### Note:

Only after the BOOT\_EVENT or after POR, STANDBY, ULPCD, the host will be able to work in the normal operation mode by issuing the commands listed above.

In case of aborting an existing running command, only after IDLE\_EVENT, the host will be able to work in the normal operation mode by issuing the commands listed above.

## 4.4.1.2 Different EVENT status definitions

## 4.4.1.2.1 Bit definitions for EVENT\_STATUS

#### Table 11. Definitions for EVENT\_STATUS bits

|    | it (To –<br>From) | Event                                                                                  | Description                                                                                                                                                                                                                               | Event data of the corresponding event (if any) |

|----|-------------------|----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|

| 31 | 12                | RFU                                                                                    | Reserved                                                                                                                                                                                                                                  |                                                |

| 11 | 11                | CTS_EVENT                                                                              | This bit is set, when CTS event is generated.                                                                                                                                                                                             | Table 86                                       |

| 10 | 10                | IDLE_EVENT                                                                             | This bit is set, when the ongoing command is canceled due to issue of SWITCH_MODE_NORMAL command.                                                                                                                                         | No event data                                  |

| 9  | 9                 | LPCD_CALIBRATION_DONE_<br>EVENT                                                        | This bit is set when the LPCD calibration-<br>done event is generated.                                                                                                                                                                    | Table 16                                       |

| 8  | 8                 | LPCD_EVENT                                                                             | This bit is set, when the LPCD event is generated.                                                                                                                                                                                        | Table 15                                       |

| 7  | 7                 | AUTOCOLL_EVENT                                                                         | This bit is set, when the AUTOCOLL operation is completed.                                                                                                                                                                                | Table 52                                       |

| 6  | 6                 | TIMER0_EVENT                                                                           | This bit is set, when the TIMER0 event is occurred.                                                                                                                                                                                       | No event data                                  |

| 5  | 5                 | TX_OVERCURRENT_ERROR_<br>EVENT                                                         | This bit is set, when the current on the TX driver is higher than the defined threshold in the EEPROM. Upon this condition, the field is automatically switched OFF before the notification to the host. Please refer to Section 4.4.2.2. | No event data                                  |

| 4  | 4                 | RFON_DET_EVENT                                                                         | This bit is set, when the external RF field is detected.                                                                                                                                                                                  | No event data                                  |

| 3  | 3                 | B RFOFF_DET_EVENT This bit is set, when already existing external RF field disappears. |                                                                                                                                                                                                                                           | No event data                                  |

| 2  | 2                 | STANDBY_PREV_EVENT                                                                     | This bit is set, when standby is prevented because of prevention conditions exist                                                                                                                                                         | Table 13                                       |

| 1  | 1                 | GENERAL_ERROR_EVENT                                                                    | This bit is set, when any general error conditions exist                                                                                                                                                                                  | Table 14                                       |

| 0  | 0                 | BOOT_EVENT                                                                             | This bit is set, when PN5190 is booted with POR/Standby                                                                                                                                                                                   | Table 12                                       |

## 4.4.1.2.2 Bit definitions for BOOT\_STATUS\_DATA

## Table 12. Definitions for BOOT\_STATUS\_DATA bits

| Bit to | Bit<br>From | Boot status | Boot reason due to                             |

|--------|-------------|-------------|------------------------------------------------|

| 31     | 27          | RFU         | Reserved                                       |

| 26     | 26          | ULP_STANDBY | Bootup Reason due to exiting from ULP_STANDBY. |

| 25     | 23          | RFU         | Reserved                                       |

PN5190 instruction layer

| Bit to | Bit<br>From | Boot status      | Boot reason due to                                                                                                      |

|--------|-------------|------------------|-------------------------------------------------------------------------------------------------------------------------|

| 22     | 22          | BOOT_RX_ULPDET   | RX ULPDET resulted in boot in ULP-Standby mode                                                                          |

| 21     | 21          | RFU              | Reserved                                                                                                                |

| 20     | 20          | BOOT_SPI         | Bootup Reason due to SPI_NTS signal being pulled low                                                                    |

| 19     | 17          | RFU              | Reserved                                                                                                                |

| 16     | 16          | BOOT_GPIO3       | Bootup Reason due to transitioning of GPIO3 from low to high.                                                           |

| 15     | 15          | BOOT_GPIO2       | Bootup Reason due to transitioning of GPIO2 from low to high.                                                           |

| 14     | 14          | BOOT_GPIO1       | Bootup Reason due to transitioning of GPIO1 from low to high.                                                           |

| 13     | 13          | BOOT_GPIO0       | Bootup Reason due to transitioning of GPIO0 from low to high.                                                           |

| 12     | 12          | BOOT_LPDET       | Bootup Reason due to external RF field presence during STANDBY/SUSPEND                                                  |

| 11     | 11          | RFU              | Reserved                                                                                                                |

| 10     | 8           | RFU              | Reserved                                                                                                                |

| 7      | 7           | BOOT_SOFT_RESET  | Bootup Reason due to soft reset of IC                                                                                   |

| 6      | 6           | BOOT_VDDIO_LOSS  | Bootup Reason due to loss of VDDIO. Refer to Section 4.4.2.3                                                            |

| 5      | 5           | BOOT_VDDIO_START | Bootup Reason if STANDBY entered with VDDIO LOSS.<br>Refer to <u>Section 4.4.2.3</u>                                    |

| 4      | 4           | BOOT_WUC         | Bootup Reason due to wake-up counter elapsed during either STANDBY operation.                                           |

| 3      | 3           | BOOT_TEMP        | Bootup Reason due to IC temperature is more than the configured threshold limit. Please refer to <u>Section 4.4.2.1</u> |

| 2      | 2           | BOOT_WDG         | Bootup Reason due to watchdog reset                                                                                     |

| 1      | 1           | RFU              | Reserved                                                                                                                |

| 0      | 0           | BOOT_POR         | Bootup Reason due power-on reset                                                                                        |

|        |             |                  |                                                                                                                         |

Table 12. Definitions for BOOT\_STATUS\_DATA bits...continued

## 4.4.1.2.3 Bit definitions for STANDBY\_PREV\_STATUS\_DATA

Table 13. Definitions for STANDBY\_PREV\_STATUS\_DATA bits

| Bit to | Bit From | Standby prevention | Standby prevented due to                      |

|--------|----------|--------------------|-----------------------------------------------|

| 31     | 26       | RFU                | RESERVED                                      |

| 25     | 25       | RFU                | RESERVED                                      |

| 24     | 24       | PREV_TEMP          | ICs operating temperature is out of threshold |

| 23     | 23       | RFU                | RESERVED                                      |

| 22     | 22       | PREV_HOSTCOMM      | Host interface communication                  |

| 21     | 21       | PREV_SPI           | SPI_NTS signal being pulled low               |

| 20     | 18       | RFU                | RESERVED                                      |

## PN5190 instruction layer

| Bit to | Bit From | Standby prevention | Standby prevented due to                                                                                 |

|--------|----------|--------------------|----------------------------------------------------------------------------------------------------------|

| 17     | 17       | PREV_GPIO3         | GPIO3 signal transitioning from low to high                                                              |

| 16     | 16       | PREV_GPIO2         | GPIO2 signal transitioning from low to high                                                              |

| 15     | 15       | PREV_GPIO1         | GPIO1 signal transitioning from low to high                                                              |

| 14     | 14       | PREV_GPIO0         | GPIO0 signal transitioning from low to high                                                              |

| 13     | 13       | PREV_WUC           | Wake-up counter elapsed                                                                                  |

| 12     | 12       | PREV_LPDET         | Low-power detection. Occurs when an external RF signal is detected in the process of going into standby. |

| 11     | 11       | PREV_RX_ULPDET     | RX ultra-low power detection. Occurs when RF signal is detected in the process of going to ULP_STANDBY.  |

| 10     | 10       | RFU                | RESERVED                                                                                                 |

| 9      | 5        | RFU                | RESERVED                                                                                                 |

| 4      | 4        | RFU                | RESERVED                                                                                                 |

| 3      | 3        | RFU                | RESERVED                                                                                                 |

| 2      | 2        | RFU                | RESERVED                                                                                                 |

| 1      | 1        | RFU                | RESERVED                                                                                                 |

| 0      | 0        | RFU                | RESERVED                                                                                                 |

#### Table 13. Definitions for STANDBY\_PREV\_STATUS\_DATA bits...continued

## 4.4.1.2.4 Bit definitions for GENERAL\_ERROR\_STATUS\_DATA

#### Table 14. Definitions for GENERAL\_ERROR\_STATUS\_DATA bits

| Bit to | Bit from | Error status              | Description                                                                                                                                               |

|--------|----------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31     | 6        | RFU                       | Reserved                                                                                                                                                  |

| 5      | 5        | XTAL_START_ERROR          | XTAL start failed during boot                                                                                                                             |

| 4      | 4        | SYS_TRIM_RECOVERY_ERROR   | Internal system trim memory error occurred,<br>but recovery is failed. System works in<br>downgraded mode.                                                |

| 3      | 3        | SYS_TRIM_RECOVERY_SUCCESS | Internal system trim memory error occurred,<br>and recovery was successful. Host must<br>perform reboot of the PN5190 for the<br>recovery to take effect. |

| 2      | 2        | TXLDO_ERROR               | TXLDO error                                                                                                                                               |

| 1      | 1        | CLOCK_ERROR               | Clock error                                                                                                                                               |

| 0      | 0        | GPADC_ERROR               | ADC error                                                                                                                                                 |

## 4.4.1.2.5 Bit definitions for LPCD\_STATUS\_DATA

#### Table 15. Definitions for LPCD\_STATUS\_DATA bytes

| Bit to |   | Status bits applicability as per the underlying operation of LPCD or ULPCD |      |       | Description for the corresponding bit is set in status byte. |

|--------|---|----------------------------------------------------------------------------|------|-------|--------------------------------------------------------------|

|        |   |                                                                            | LPCD | ULPCD |                                                              |

| 31     | 7 | RFU                                                                        |      |       | Reserved                                                     |

#### PN5190 instruction layer

| Bit to | Bit From | Status bits applicability as per the underlying operation of LPCD or ULPCD |   |   | Description for the corresponding bit is set in status byte. |

|--------|----------|----------------------------------------------------------------------------|---|---|--------------------------------------------------------------|

| 6      | 6        | Abort_HIF                                                                  | Y | N | Aborted due to HIF activity                                  |

| 5      | 5        | CLKDET error                                                               | N | Y | Aborted due to CLKDET error occurred                         |

| 4      | 4        | XTAL Timeout                                                               | N | Y | Aborted due to XTAL Timeout occurred                         |

| 3      | 3        | VDDPA LDO Overcurrent                                                      | N | Y | Aborted due to VDDPA LDO overcurrent occurred                |

| 2      | 2        | External RF field                                                          | Y | Y | Aborted due to external RF field                             |

| 1      | 1        | GPIO3 Abort                                                                | N | Y | Aborted due to GPIO3 level change                            |

| 0      | 0        | Card Detected                                                              | Y | Y | Card is detected                                             |

#### Table 15. Definitions for LPCD\_STATUS\_DATA bytes...continued

## 4.4.1.2.6 Bit definitions for LPCD\_CALIBRATION\_DONE Status data

#### Table 16. Definitions for LPCD\_CALIBRATION\_DONE status data bytes for ULPCD

| Bit to | Bit From | Status of LPCD_CALIBRATION DONE event  | Description for the corresponding bit is set in status byte.                             |

|--------|----------|----------------------------------------|------------------------------------------------------------------------------------------|

| 31     | 11       |                                        | Reserved                                                                                 |

| 10     | 0        | Reference value from ULPCD calibration | The measured RSSI value during ULPCD calibration which is used as reference during ULPCD |

#### Table 17. Definitions for LPCD\_CALIBRATION\_DONE status data bytes for LPCD

| Bit to | Bit From | Status of LPCD_CALIBRATION DONE event | Description for the corresponding bit is set in status byte. |

|--------|----------|---------------------------------------|--------------------------------------------------------------|

| 31     | 16       | Channel 1 reference                   | The measured channel 1 values during LPCD calibration        |

| 15     | 0        | Channel 0 reference                   | The measured channel 0 values during LPCD calibration        |

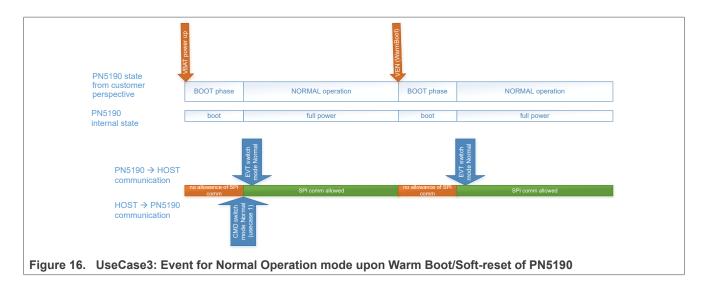

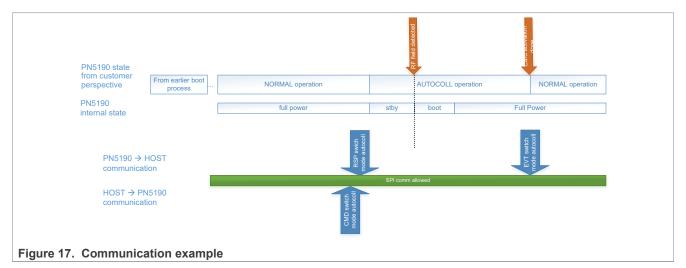

#### 4.4.2 Handling of different boot scenarios

The PN5190 IC handles different error conditions related to IC parameters as below.

#### 4.4.2.1 Handling of over temperature scenario when PN5190 is under operation

Whenever the PN5190 IC's internal temperature is reaching to the threshold value as configured in the EEPROM field TEMP\_WARNING [2], the IC enters into the standby. And consequently if EEPROM field ENABLE\_GPIO0\_ON\_OVERTEMP [2] is configured to raise a notification to the host, then GPIO0 will be pulled high to notify the IC over temperature.

As and when the IC temperature falls below the threshold value as configured in the EEPROM field TEMP\_WARNING [2], the IC will bootup with BOOT\_EVENT as in <u>Table 11</u> and BOOT\_TEMP boot status bit is set as in <u>Table 12</u> and GPIO0 will be pulled low.

## 4.4.2.2 Handling of overcurrent

If PN5190 IC senses the overcurrent condition, the IC switches off RF power and sends the TX\_OVERCURRENT\_ERROR\_EVENT as in <u>Table 11</u>.

The duration of the overcurrent condition can be controlled by modifying the EEPROM field TXLDO\_CONFIG [2].

For information on IC over current threshold, refer to document [2].

#### Note:

If there are any other pending events or response, they will be sent to the host.

## 4.4.2.3 Loss of VDDIO during operation

If PN5190 IC encounters that there is no VDDIO (VDDIO loss), the IC enters into standby.

IC boots only when the VDDIO is available, with BOOT\_EVENT as in <u>Table 11</u> and BOOT\_VDDIO\_START boot status bit is set as in <u>Table 12</u>.

For information on PN5190 IC static characteristics, refer to document [2].

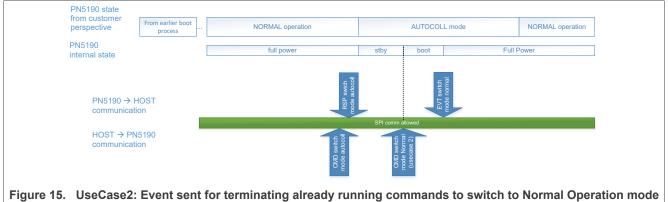

## 4.4.3 Handling of abort scenarios

The PN5190 IC has a support of aborting the present executing commands and the behavior of the PN5190 IC, when such abort command such as <u>Section 4.5.4.5.2</u> is sent to PN5190 IC is as shown in <u>Table 18</u>.

#### Note:

When PN5190 IC is in ULPCD and ULP-Standby mode, it cannot be aborted either by sending a <u>Section 4.5.4.5.2</u> OR by starting a SPI transaction (by pulling low on SPI\_NTS signal).

Table 18. Expected event response when different commands terminated with Section 4.5.4.5.2

| Commands                                                                                                   | Behavior when Switch Mode Normal command is sent                                                      |

|------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| All commands where low power is not entered                                                                | EVENT_STAUS is set to "IDLE_EVENT"                                                                    |

| Switch Mode LPCD                                                                                           | EVENT_STATUS is set to "LPCD_EVENT" with "LPCD_<br>STATUS_DATA" indicating status bits as "Abort_HIF" |

| Switch Mode Standby                                                                                        | EVENT_STAUS is set to "BOOT_EVENT" with "BOOT_<br>STATUS_DATA" indicating bits "BOOT_SPI"             |

| Switch Mode Autocoll(No Autonomous mode, autonomous mode with standby and autonomous mode without standby) | EVENT_STAUS is set to "AUTOCOLL_EVENT" with STATUS_DATA bits indicating command was user canceled.    |

## 4.5 Normal Mode Operation Instruction Details

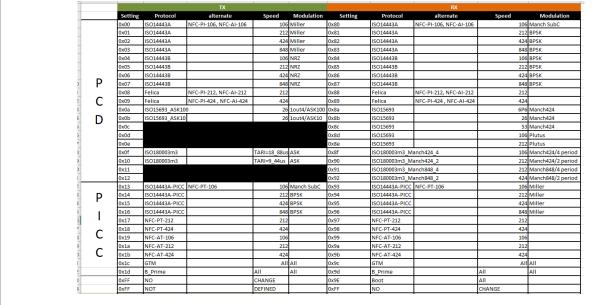

## 4.5.1 Register Manipulation

Instructions of this section are used to access the logical registers of PN5190.

## 4.5.1.1 WRITE\_REGISTER