**User manual**

#### **Document information**

| Information | Content                                                                                                                                                                                                                                                                                         |  |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Keywords    | battery junction box measurement, isolation, current redundancy, pack, contactor, shunt, accuracy, temperature, precharge resistor, chassis, DCLINK CAN, CANFD, CAN-FD                                                                                                                          |  |

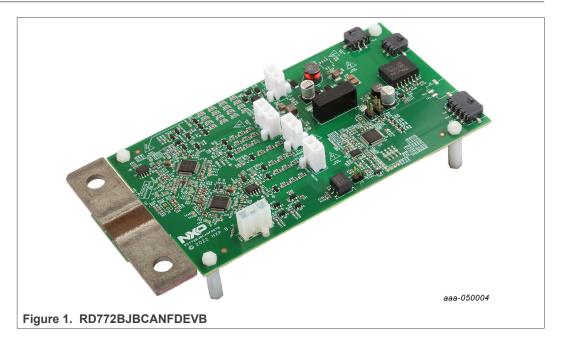

| Abstract    | This user manual targets the RD772BJBCANFDEVB board. The<br>RD772BJBCANFDEVB is a typical battery junction box (BJB) solution that<br>can be used in high-voltage battery management systems (BMS). The<br>RD772BJBCANFDEVB is part of the high-voltage BMS reference design<br>offered by NXP. |  |

## RD772BJBCANFDEVB battery junction box

#### **Revision history**

| Rev | Date     | Description     |

|-----|----------|-----------------|

| 1.0 | 20230125 | Initial release |

## 1 Important notice

# WARNING Lethal voltage and fire ignition hazard Image: State of the ignit hazard Image: State

## RD772BJBCANFDEVB battery junction box

# 2 RD772BJBCANFDEVB

## 3 Introduction

The RD772BJBCANFDEVB is a BJB reference design for high-voltage battery management systems. The solution features high-voltage, current, and isolation-resistance measurements. The RD772BJBCANFDEVB has a communication port using CAN protocol.

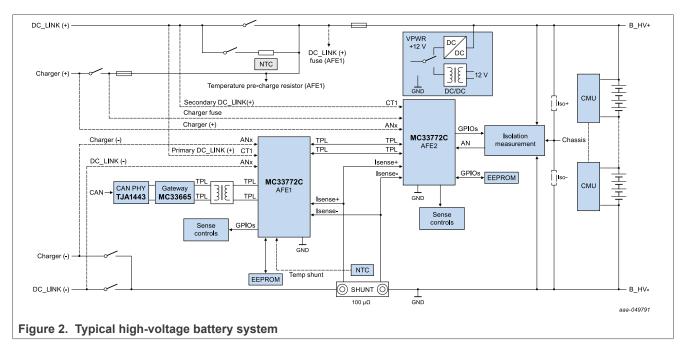

Figure 2 shows a typical BJB with functions allocated to it and the context in a battery management system.

#### 3.1 Kit contents/packing list

The kit includes:

- Assembled and tested board in antistatic bag

- High-voltage measurement cables

- External thermistor connection cable

- Power supply and CAN communication cable

## 4 Getting to know the hardware

#### 4.1 Board overview

The RD772BJBCANFDEVB supports all typical functions of a BJB.

The RD772BJBCANFDEVB is supplied either with an isolated DC-DC from low-voltage domain (12 V) or directly from the high-voltage battery with a self-supply circuitry.

The RD772BJBCANFDEVB includes a galvanic isolation enabling communication between the high-voltage domain of the RD772BJBCANFDEVB and low-voltage domain of the controller.

#### 4.2 Board features

Main features of the RD772BJBCANFDEVB:

- Five inputs high-voltage positive measurement up to 500 V

- Two inputs high-voltage negative measurement down to −500 V

- Single shunt for current measurement ±1500 A

- Shunt temperature measurement from −40 °C to +105 °C

- · Connection to the precharge resistor for temperature measurement

- Passive isolation resistance measurement between high-voltage and low-voltage domains

- Two EEPROMs for data and calibration data storage

- Controller Area Network (CAN) line followed by an isolated gateway for communication with other systems

- Additional galvanically isolated electrical transport protocol link (ETPL) for communication with other systems

#### 4.3 Block diagram

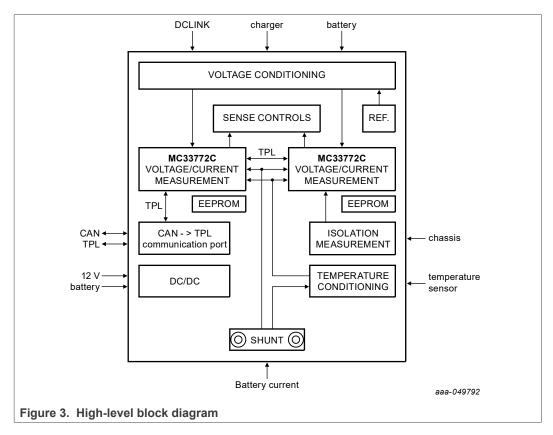

Figure 3 shows the main functions as well as the input and output of the battery junction box.

The voltage conditioning block is scaling down the high voltage from 0 V to 500 V to 0 V to 4.85 V range for analog-to-digital conversion by the MC33772C analog input.

Sense control function enables the voltage divider. A general-purpose input/output (GPIO) enables the switch in the voltage divider through a level shifter. This function prevents consumption of the voltage divider when the measurement is not performed (see <u>Section 6.1</u> for an example of the sense control).

The resistance measurement function enables a connection to the chassis of the vehicle. Then several measurements are performed with different parallel resistor configurations. The isolation resistance between high-voltage domain and low-voltage domain is further computed in the main controller based on the voltage measurement (see <u>Section 5</u>).

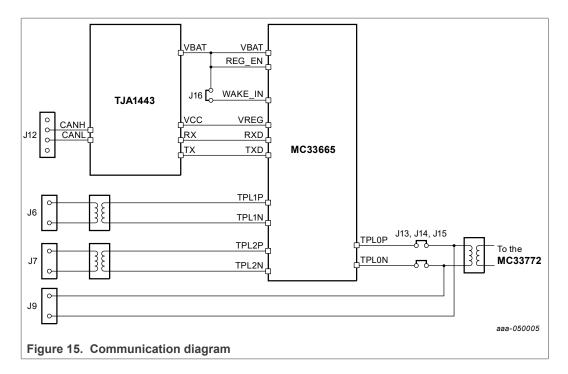

The communication is based on a Controller Area Network (CAN) line. A MC33665 acts as a gateway and transfers the information to the MC33772C in TPL.

An additional communication line is based on the TPL working up to 2 Mbit/s. It is an NXP isolated communication protocol.

Two negative temperature coefficient resistors (NTCs) monitor the shunt temperature and the precharge resistor temperature. The analog inputs are configured as ratiometric analog inputs with reference to a voltage delivered by the MC33772C.

The battery junction box is supplied by a 12 V (typ.) either from the high-voltage battery with a buck converter or from a 12 V battery from low-voltage (LV) domain through an isolated DC-DC (see <u>Section 4.11</u> for details).

The MC33772C performs analog-to-digital conversions of the sensed voltages and current, as well as battery coulomb counting.

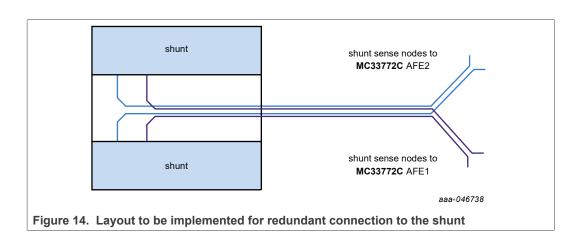

The shunt is a 100  $\mu\Omega$  resistor with ±1500 A capability measurement. The resulting shunt voltage is redundantly measured by the two MC33772C.

#### 4.4 Board detailed features

The RD772BJBCANFDEVB embeds two MC33772C ICs. <u>Table 1</u> and <u>Table 2</u> show the measurement signal allocation per MC33772C:

| Signal                         | MC33772C AFE1 |

|--------------------------------|---------------|

| DCLINK(+) primary              | CT1           |

| DCLINK(-)                      | AN0 (GPIO0)   |

| Charger(–)                     | AN1 (GPIO1)   |

| DCLINK fuse                    | AN2 (GPIO2)   |

| precharge resistor temperature | AN3 (GPIO3)   |

#### Table 2. Battery junction box signal allocation to MC33772C AFE2

| Signal              | MC33772C AFE2 |

|---------------------|---------------|

| DCLINK(+) secondary | CT1           |

| Iso_R_mon           | AN0 (GPIO0)   |

| Charger(+)          | AN1 (GPIO1)   |

| Charger fuse        | AN2 (GPIO2)   |

| Shunt thermal sense | AN3 (GPIO3)   |

The GPIO4, GPIO5, and GPIO6 from AFE1 and AFE2 are selecting the signals for measurement. <u>Table 3</u> shows the control signal allocation per MC33772C:

Table 3. GPIO control table

| GPIO  | AFE1                                          | AFE2                                |

|-------|-----------------------------------------------|-------------------------------------|

| GPIO4 | DCLINK(+) primary<br>DCLINK fuse<br>DCLINK(–) | Charger(+)<br>Charger(–)<br>ISO_QL2 |

| GPIO5 | ISO_Opto                                      | DCLINK(+) secondary                 |

| GPIO6 | ISO_QL1                                       | ISO_Q1                              |

#### 4.5 Board description

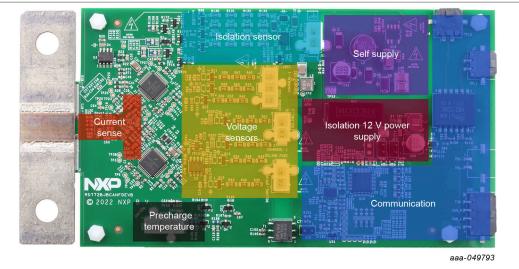

Figure 4 shows the location of functions over the board:

**RD772BJBCANFDEVB** battery junction box

Figure 4. Location of functions over the board

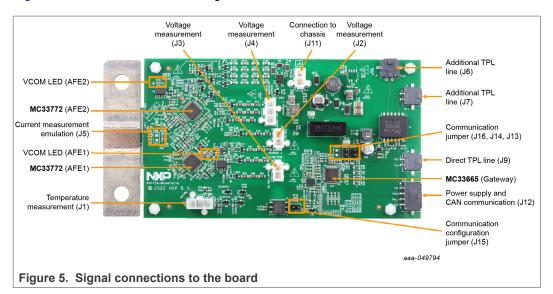

Figure 5 shows the allocation of signals in different board connectors:

#### 4.6 VCOM LED

The VCOM LED is on the board, as shown in Figure 5. The VCOM LED indicates when the device is in normal mode. Upon reset, the MC33772C enters into normal mode (VCOM turns on). If there is no activity on the bus after a timeout period of 60 s, the device enters low-power idle mode (VCOM turns off). Once the device is initialized, if no communication occurs on the TPL bus after 1 s, the device resets and the LED turns off (VCOM off). Depending on the device settings, the VCOM LED may flash with 8 s interval during cyclic acquisition.

#### 4.7 Connectors

<u>Figure 5</u> shows the location of connectors on the board. <u>Table 4</u> to <u>Table 8</u> list the pinouts for each connector.

#### **RD772BJBCANFDEVB** battery junction box

#### Table 4. Precharge resistor temperature connector (J1)

| Pin | Connection     | Description        |

|-----|----------------|--------------------|

| 1   | PRECHARGE_TEMP | NTC connection (+) |

| 2   | n.c.           | not connected      |

| 3   | GND            | NTC connection (-) |

#### Table 5. Negative signal connector (J2)

| Pin | Connection     | Description                        |

|-----|----------------|------------------------------------|

| 1   | HV_DCLINK_NEG  | DCLINK(-), negative voltage node   |

| 2   | HV_CHARGER_NEG | charger (−), negative voltage node |

#### Table 6. High-voltage DCLINK(+) connector (J3)

| Pin | Connection        | Description                              |

|-----|-------------------|------------------------------------------|

| 1   | HV_DCLINK_POS_PRM | DCLINK(+) primary, positive voltage node |

| 2   | HV_DCLINK_FUSE    | DCLINK fuse, positive voltage node       |

#### Table 7. High-voltage charger connector (J4)

| Pin | Connection        | Description                                |

|-----|-------------------|--------------------------------------------|

| 1   | HV_DCLINK_POS_SEC | DCLINK(+) secondary, positive voltage node |

| 2   | HV_CHARGER_POS    | charger(+), positive voltage node          |

| 3   | HV_CHARGER_FUSE   | charger fuse, positive voltage node        |

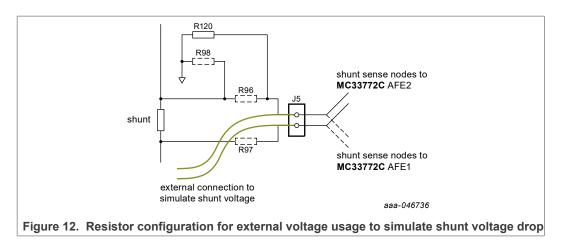

#### Table 8. Shunt voltage connector (J5)

| Pin | Connection | Description                                    |

|-----|------------|------------------------------------------------|

| 1   | Sense_p    | differential voltage to simulate shunt voltage |

| 2   | Sense_n    | differential voltage to simulate shunt voltage |

Table 9. Additional TPL line connector (J6)

| Pin | Connection | Description                              |

|-----|------------|------------------------------------------|

| 1   | TPL_P      | positive signal of the TPL communication |

| 2   | TPL_N      | negative signal of the TPL communication |

#### Table 10. Additional TPL line connector (J7)

| Pin                                                                        | Connection | Description                              |                                      |  |

|----------------------------------------------------------------------------|------------|------------------------------------------|--------------------------------------|--|

| 1                                                                          | TPL_P      | positive signal of the TPL communication |                                      |  |

| 2                                                                          | TPL_N      | negative signal of the TPL communication |                                      |  |

| All information provided in this document is subject to legal disclaimers. |            |                                          | © 2023 NXP B.V. All rights reserved. |  |

Table 11. Direct TPL line connector (J9)

| Pin | Connection | Description                              |

|-----|------------|------------------------------------------|

| 1   | TPL_P      | positive signal of the TPL communication |

| 2   | TPL_N      | negative signal of the TPL communication |

| Table ' | 12. | Chassis | connector | (J11) |

|---------|-----|---------|-----------|-------|

|---------|-----|---------|-----------|-------|

| Pin | Connection | Description                                      |

|-----|------------|--------------------------------------------------|

| 1   | chassis    | connection to chassis for resistance measurement |

| 2   | n.c.       | not connected                                    |

#### 4.8 Temperature measurement

The RD772BJBCANFDEVB offers two temperature measurements: one temperature measurement of the shunt and one temperature measurement of the precharge resistor. The NTC used is B57232V5103F360. The voltage divider is supplied by VCOM from MC33772C.

#### 4.9 Cell terminal voltage measurement

CT1 of each MC33772C is used for voltage measurement. The other CT pins are unused. To comply with the maximum differential rating between pins, the unused CTx and CBx pins are externally biased with a voltage divider. The resistor values for the CTx/CBx biasing have been calculated to comply with maximum ratings and to comply with the supply voltage range specified in <u>Section 4.11</u>.

#### 4.10 Bus terminal communication

The 1:1 transformer galvanically isolates the superior control unit on LV domain to the MC33772C AFE1 on High-Voltage (HV) domain. The TPL bus has a direct connection between AFE1 and AFE2. Isolation is not required, as both devices share GND and supply. For additional information about the TPL protocol and external components, refer to MC33772C data sheet<sup>[1]</sup>.

#### 4.11 Power supply

The battery junction box offers two options for the supply:

- 12 V from a DC-DC converter from low-voltage domain

- 12 V from the high-voltage domain with a step-down converter

| Symbol          | Parameter      | Conditions                                                                     | Min | Тур | Мах  | Unit |

|-----------------|----------------|--------------------------------------------------------------------------------|-----|-----|------|------|

| V <sub>CC</sub> | supply voltage | high-voltage domain                                                            | 9   | 12  | 13.5 | V    |

| I <sub>CC</sub> | supply current | normal mode; ADC active; TPL communication active; 12 V supplied without DC-DC |     | 21  | _    | mA   |

|                 |                | sleep mode                                                                     | _   | 430 | _    | μA   |

|                 |                | normal mode; ADC active; TPL communication active; 12 V supplied from DC-DC    | _   | 37  | _    | mA   |

Table 13. Power supply

© 2023 NXP B.V. All rights reserved

The default supply is from the DC-DC converter. On RD772BJBCANFDEVB, an industrial integrated DC-DC converter is used. If the BJB is used in an automotive environment, an automotive-qualified, isolated DC-DC is recommended. Four resistors connect or disconnect the power supply options. <u>Table 14</u> details the resistor connections for the supply selection source.

Table 14. Power supply selection

| Power source                                      | R65                | R95 | R63 | R64 |

|---------------------------------------------------|--------------------|-----|-----|-----|

| 12 V from DC-DC converter from low-voltage domain | Do Not Place (DNP) | 0 Ω | 0 Ω | DNP |

| 12 V from high-voltage battery                    | 0 Ω                | DNP | DNP | 0 Ω |

## 5 Isolation measurement

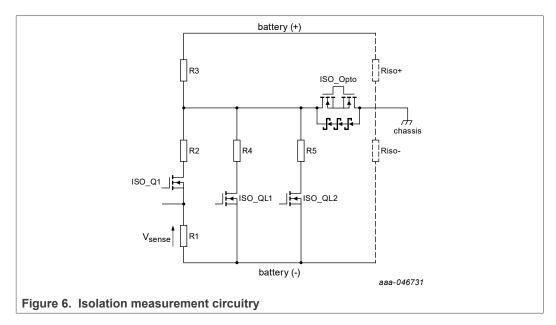

The BJB features a passive isolation resistance measurement circuit. A dedicated circuitry connects the chassis to specific resistor networks. This connection unbalances the network as a function of the resistance between the chassis and the battery. Figure 6 shows the resistor networks and chassis connections.

The ISO\_Q1, ISO\_QL1, and ISO\_QL2 prevent continuous current leakage between the battery rails. ISO\_Opto connects or disconnects the chassis to the isolation resistance measurement circuit. The principle of operation is to close ISO\_Q1 then to measure  $V_{sense}$ . This measurement is called *V1*. Then, ISO\_QL1 closes and  $V_{sense}$  is measured again. This second measurement is called *V2*. After the second measurement, the two voltages, V1 and V2, are used in the formulas Equation 1 and Equation 2, assumed to be implemented in the battery management unit (BMU), to compute Riso+ and Riso-. To ease the computation, the Y1 to Y4 conductances of the R1 to R4 resistances are considered.  $V_{bat}$  is the battery voltage. The last low branch, that includes R5 and is enabled by ISO\_QL2, is a redundant branch of the one enabled by ISO\_QL1. This last branch can be used instead of ISO\_QL1 one or to make a third measurement.

$$Y_{iso+} = -\frac{V_1}{V_{bat}} \times \frac{V_2}{V_2 - V_1} \times \frac{Y_1 + Y_2}{Y_2} \times Y_4 - Y_3$$

<sup>(1)</sup>

#### **RD772BJBCANFDEVB** battery junction box

$$Y_{iso-} = -Y_3 - \frac{Y_1 Y_2}{Y_1 + Y_2} - Y_4 \times \frac{V_2}{V_2 - V_1} - Y_{iso+}$$

(2)

## 6 High-voltage measurement

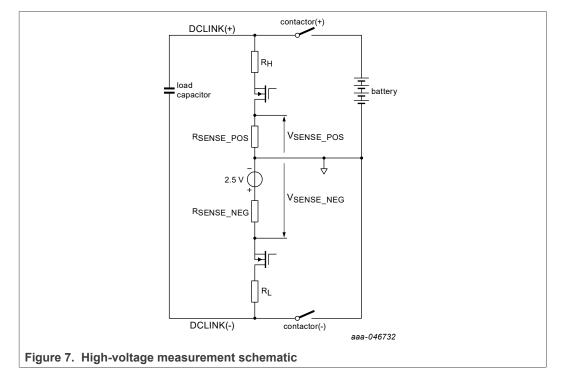

The high-voltage nodes are sensed through a voltage divider to scale the voltage down to a range suitable for the input of the MC33772C. Figure 7 represents the DCLINK(+) and DCLINK(-) measurements. The capacitor represents the total traction inverter load capacitance.

A reference is in the negative measurement path to allow negative voltage measurement.

Sense voltages are computed in the BMU with Equation 3 and Equation 4:

$$V_{\text{SENSE}_POS} = \text{DCLINK}(+) \times \frac{R_{\text{SENSE}_POS}}{R_{\text{SENSE}_POS} + R_{\text{H}}}$$

(3)

$$V_{\text{SENSE_NEG}} = V_{\text{REF}} \times \frac{R_{\text{L}}}{R_{\text{SENSE_NEG}} + R_{\text{L}}} + \text{DCLINK(-)} \times \frac{R_{\text{SENSE_NEG}}}{R_{\text{SENSE_NEG}} + R_{\text{L}}}$$

(4)

UM11846 User manual

#### 6.1 Blanking time

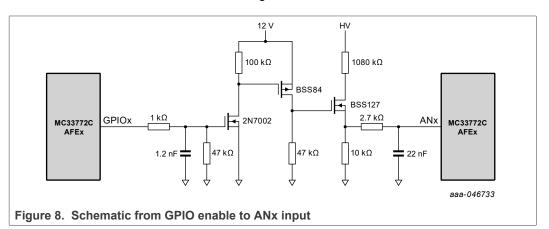

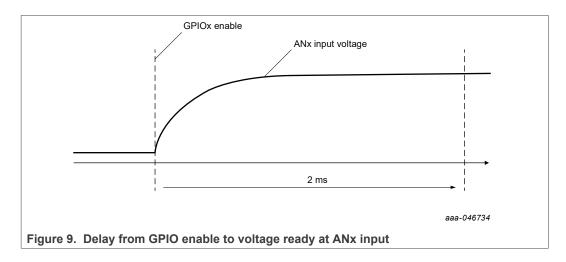

Before doing any measurement with the MC33772C, a blanking time is required to secure that the voltage is stabilized before the analog-to-digital conversion. Figure 8 shows the complete path from GPIO output enable to ANx input. Figure 9 shows the time needed before measurement. This blanking time is 2 ms minimum.

#### 6.2 Low-voltage input signals emulation

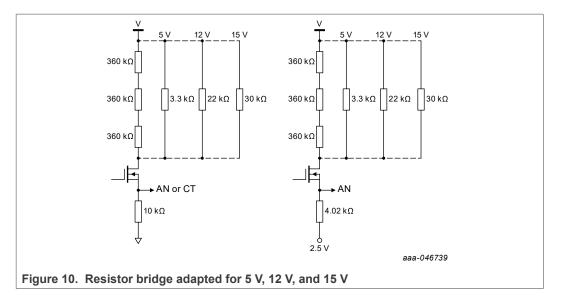

All high-voltage nodes are sensed with a voltage divider to lower the voltage in a range suitable for the MC33772C analog input (4.85 V max). If the solution must be tested with lower voltage (5 V, 12 V, or 15 V), the voltage divider ratio has to be adapted. In Figure 10, the resistor has been chosen for 3.75 V at MC33772C inputs.

**RD772BJBCANFDEVB** battery junction box

## 7 Current measurement

#### 7.1 Current sense input selection

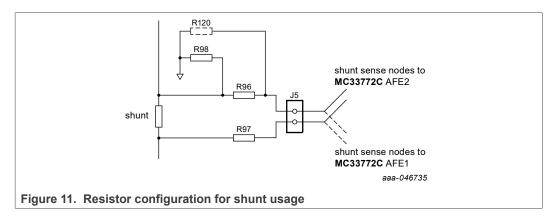

The battery junction box board allows the customer to apply an external voltage to simulate the current across the shunt. The maximum differential voltage is  $\pm 150$  mV at MC33772C current sense inputs.

<u>Figure 11</u> shows the resistor configuration for shunt usage and <u>Figure 12</u> shows the configuration for external voltage usage.

#### RD772BJBCANFDEVB battery junction box

## 7.2 Layout note

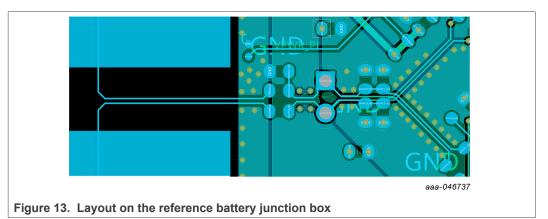

The layout of the current sense has been designed to connect an external voltage source to simulate the battery current. The connection to the shunt is not redundant, as it should be. Figure 13 shows the layout on the BJB reference board and Figure 14 shows the layout to be implemented on the final application to secure the redundant connection to the shunt.

User manual

# 8 Battery junction box filters

A low-pass filter is implemented on each measurement input. <u>Table 15</u> summarizes the cutoff frequencies of all input signals.

| Parameter                          | Cutoff frequency (-3 dB) |

|------------------------------------|--------------------------|

| DCLINK(+)                          | 600 Hz                   |

| DCLINK(-)                          | 600 Hz                   |

| DCLINK fuse                        | 600 Hz                   |

| Charger(+)                         | 600 Hz                   |

| Charger(-)                         | 600 Hz                   |

| Charger fuse                       | 600 Hz                   |

| Isolation to chassis               | 530 Hz                   |

| Shunt temperature                  | 600 Hz                   |

| precharge resistor temperature     | 600 Hz                   |

| Current sense differential voltage | 600 Hz                   |

| Current sense common-mode voltage  | 26.7 kHz                 |

**Note:** The safety mechanism SM05 (OT/UT diagnostic on ANx) shall not be used with the capacitor computed for above cutoff frequencies. If SM05 is used, then the capacitor shall be below 10 nF. This limitation applies to pins set as analog inputs. For SM05 safety mechanism details, refer to the MC33772C safety manual.

## 9 Communication

By default, the reference design communicates with the Battery Management Unit (BMU) with a Controller Area Network protocol (CAN), as detailed in <u>Figure 15</u>.

#### **RD772BJBCANFDEVB** battery junction box

#### 9.1 CAN communication

The CAN lines coming from the BMU are connected to J12. The TJA1443 acts as a transceiver and interfaces the CAN lines with the MC33665. The MC33665 is a gateway that can be configured to forward all the messages between the BMU (CAN) and the MC33772 (TPL).

The user must put jumpers on J13, J14 and J15 to communicate in CAN with the RD772BJBCANFDEVB.

The jumper J16 keeps the MC33665 awake. This feature is useful when using a software tool with a delay between messages longer than the MC33665 timeout. If the MC33665 sleep feature is necessary, the jumper can be removed.

#### 9.2 TPL communication

The RD772BJBCANFDEVB can be converted to a TPL Battery Junction Box by removing J14, J14, and J15. Then, the TPL line connected to J9 bypasses the MC33665 and is connected to the MC33772.

Two additional TPL lines are available on J6 and J9. These lines are directly connected to the MC33665 and could be used to interface the RD772BJBCANFDEVB with other TPL boards. The MC33665 could then distribute the messages from the BMU to any TPL line.

# RD772BJBCANFDEVB battery junction box

# 10 Available accessories

| Part number | Description                                                            |

|-------------|------------------------------------------------------------------------|

| 600-77571   | -                                                                      |

|             | Figure 16. Cable for high-voltage connections, two positions, 500 mm   |

| 600-77659   | aaa-047371                                                             |

|             | Figure 17. Cable for high-voltage connections, three positions, 500 mm |

#### **RD772BJBCANFDEVB** battery junction box

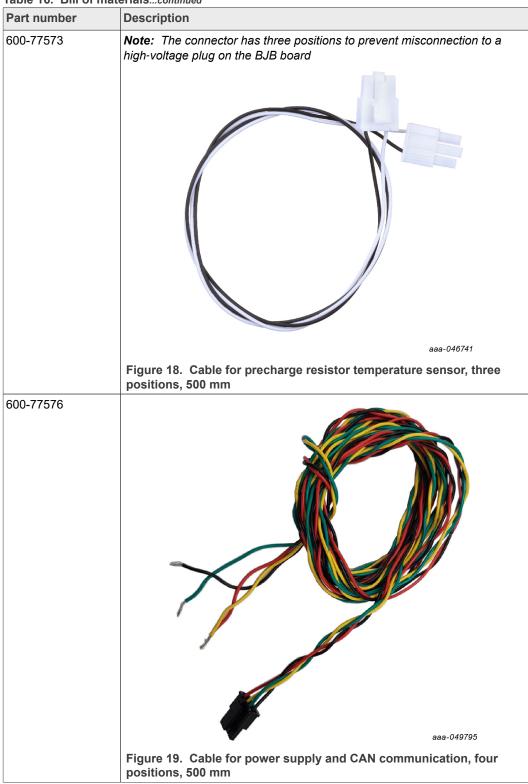

Table 16. Bill of materials...continued

# **11 References**

[1] Data sheet MC33772C http://www.nxp.com/MC33772C

#### **RD772BJBCANFDEVB** battery junction box

# 12 Legal information

#### 12.1 Definitions

**Draft** — A draft status on a document indicates that the content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included in a draft version of a document and shall have no liability for the consequences of use of such information.

#### 12.2 Disclaimers

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. NXP Semiconductors takes no responsibility for the content in this document if provided by an information source outside of NXP Semiconductors.

In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of NXP Semiconductors.

**Right to make changes** — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this respect.

Terms and conditions of commercial sale — NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at http://www.nxp.com/profile/terms, unless otherwise agreed in a valid written individual agreement. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. NXP Semiconductors hereby expressly objects to applying the customer's general terms and conditions with regard to the purchase of NXP Semiconductors products by customer.

Suitability for use in automotive applications — This NXP product has been qualified for use in automotive applications. If this product is used by customer in the development of, or for incorporation into, products or services (a) used in safety critical applications or (b) in which failure could lead to death, personal injury, or severe physical or environmental damage (such products and services hereinafter referred to as "Critical Applications"), then customer makes the ultimate design decisions regarding its products and security related requirements concerning its products, regardless of any information or support that may be provided by NXP. As such, customer assumes all risk related to use of any products in Critical Applications and NXP and its suppliers shall not be liable for any such use by customer. Accordingly, customer will indemnify and hold NXP harnless from any claims, liabilities, damages and associated costs and expenses (including attorneys' fees) that NXP may incur related to customer's incorporation of any product in a Critical Application.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

**Evaluation products** — This product is provided on an "as is" and "with all faults" basis for evaluation purposes only. NXP Semiconductors, its affiliates and their suppliers expressly disclaim all warranties, whether express, implied or statutory, including but not limited to the implied warranties of non-infringement, merchantability and fitness for a particular purpose. The entire risk as to the quality, or arising out of the use or performance, of this product remains with customer.

In no event shall NXP Semiconductors, its affiliates or their suppliers be liable to customer for any special, indirect, consequential, punitive or incidental damages (including without limitation damages for loss of business, business interruption, loss of use, loss of data or information, and the like) arising out the use of or inability to use the product, whether or not based on tort (including negligence), strict liability, breach of contract, breach of warranty or any other theory, even if advised of the possibility of such damages.

Notwithstanding any damages that customer might incur for any reason whatsoever (including without limitation, all damages referenced above and all direct or general damages), the entire liability of NXP Semiconductors, its affiliates and their suppliers and customer's exclusive remedy for all of the foregoing shall be limited to actual damages incurred by customer based on reasonable reliance up to the greater of the amount actually paid by customer for the product or five dollars (US\$5.00). The foregoing limitations, exclusions and disclaimers shall apply to the maximum extent permitted by applicable law, even if any remedy fails of its essential purpose.

**Translations** — A non-English (translated) version of a document, including the legal information in that document, is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.

Security — Customer understands that all NXP products may be subject to unidentified vulnerabilities or may support established security standards or specifications with known limitations. Customer is responsible for the design and operation of its applications and products throughout their lifecycles to reduce the effect of these vulnerabilities on customer's applications and products. Customer's responsibility also extends to other open and/or proprietary technologies supported by NXP products for use in customer's applications. NXP accepts no liability for any vulnerability. Customer should regularly check security updates from NXP and follow up appropriately. Customer shall select products with security features that best meet rules, regulations, and standards of the intended application and make the ultimate design decisions regarding its products and is solely responsible for compliance with all legal, regulatory, and security related requirements concerning its products, regardless of any information or support that may be provided by NXP.

NXP has a Product Security Incident Response Team (PSIRT) (reachable at <u>PSIRT@nxp.com</u>) that manages the investigation, reporting, and solution release to security vulnerabilities of NXP products.

## RD772BJBCANFDEVB battery junction box

NXP — wordmark and logo are trademarks of NXP B.V.

## 12.3 Trademarks

Notice: All referenced brands, product names, service names, and trademarks are the property of their respective owners.

## RD772BJBCANFDEVB battery junction box

## Contents

| 1    | Important notice                    | 3   |

|------|-------------------------------------|-----|

| 2    | RD772BJBCANFDEVB                    | . 4 |

| 3    | Introduction                        | . 5 |

| 3.1  | Kit contents/packing list           | . 5 |

| 4    | Getting to know the hardware        | . 6 |

| 4.1  | Board overview                      | 6   |

| 4.2  | Board features                      | . 6 |

| 4.3  | Block diagram                       | 6   |

| 4.4  | Board detailed features             | . 8 |

| 4.5  | Board description                   | 8   |

| 4.6  | VCOM LED                            | 9   |

| 4.7  | Connectors                          | 9   |

| 4.8  | Temperature measurement             | 11  |

| 4.9  | Cell terminal voltage measurement   |     |

| 4.10 | Bus terminal communication          | 11  |

| 4.11 | Power supply                        |     |

| 5    | Isolation measurement               |     |

| 6    | High-voltage measurement            | 13  |

| 6.1  | Blanking time                       |     |

| 6.2  | Low-voltage input signals emulation |     |

| 7    | Current measurement                 |     |

| 7.1  | Current sense input selection       | 15  |

| 7.2  | Layout note                         |     |

| 8    | Battery junction box filters        | 17  |

| 9    | Communication                       |     |

| 9.1  | CAN communication                   | 18  |

| 9.2  | TPL communication                   | 18  |

| 10   | Available accessories               |     |

| 11   | References                          |     |

| 12   | Legal information                   | 22  |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.

© 2023 NXP B.V.

All rights reserved.

For more information, please visit: http://www.nxp.com

Date of release: 25 January 2023 Document identifier: UM11846