uPower Firmware User's Guide Rev. 0 — 30 November 2022

User guide

#### **Document information**

| Information | Content                                                                                                                                                                                                                       |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Keywords    | uPower, i.MX 8ULP, Linux                                                                                                                                                                                                      |

| Abstract    | This document describes the i.MX 8ULP power management subsystem features, power domains, uPower interface, RTD and APD power mode transitions, PMIC driver, and APIs provided by uPower for Arm Cortex-M33/A35 runtime call. |

## 1 Overview

This document describes the i.MX 8ULP power management subsystem features, power domains, uPower interface, RTD and APD power mode transitions, PMIC driver, and APIs provided by uPower for Arm Cortex-M33/A35 runtime call.

## 2 Acronyms and Abbreviations

| Name      | Description                                      | Comment                                                                   |  |

|-----------|--------------------------------------------------|---------------------------------------------------------------------------|--|

| AD        | Application Domain                               | -                                                                         |  |

| AFBB      | Asymmetric Forward Body Bias                     | Used for high-performance modes.<br>Increases transistor switching speed. |  |

| AHB       | Arm Advanced High Performance<br>Bus             | -                                                                         |  |

| AMBA      | Arm Advanced Microcontroller Bus<br>Architecture | -                                                                         |  |

| AOGPOR    | General Purpose Output Register                  | Always on domain.                                                         |  |

| APB       | Arm Advanced Peripheral Bus                      | -                                                                         |  |

| APD       | Application Domain                               | -                                                                         |  |

| AVD       | Audio Video Domain                               | -                                                                         |  |

| СМС       | Core Mode Controller                             | Refer to the i.MX 8ULP Reference Manual.                                  |  |

| DGO       | Always ON domain                                 | -                                                                         |  |

| Dombias   | Domain bias                                      |                                                                           |  |

| HVD       | High Voltage Detector                            | -                                                                         |  |

| MU        | Message Unit                                     | -                                                                         |  |

| P-Channel | Arm P-Channel Interface                          | -                                                                         |  |

| PMC       | Power Management Controller                      | -                                                                         |  |

| PMIC      | Power Management IC                              | -                                                                         |  |

| PS        | Power Switch                                     | -                                                                         |  |

| RBB       | Reverse Body Bias                                | Used for low-power modes. Reduces leakage.                                |  |

| RTD       | Real Time Domain                                 | -                                                                         |  |

| SIC       | System Interface Control Module                  | -                                                                         |  |

| LVD       | Low Voltage Detector                             | -                                                                         |  |

#### Table 1. Acronyms and abbreviations

# 3 uPower Subsystem and Firmware Introduction

The uPower is a programmable subsystem based on a RISC-V CPU compatible with the RV32EMC instruction set. The uPower runs a dedicated firmware provided by NXP. It controls the i.MX 8ULP device power-related functions and provides power-related services to its clients. Its main functions notably include:

UPOWERUG

- Running pre-programmed control functions during device initialization.

- Abstracting power control services for its clients (application software).

- Managing device various power mode entry and exit, and wakeup sources.

- Exposing a set of information services, such as device temperature or power consumption measurement of a specific power domain.

Complex power control services may be provided, such as the determination of the optimal.

The uPower has a dedicated power supply, so it can stay operational even if all the other device power domains are powered off. The power supply has a low-power mode that is used when the uPower is in low-power state with its clock gated off. The subsystem has a dedicated 16/64 MHz configurable oscillator controlled by the uPower CPU. If required, the oscillator is switched to 64 MHz mode. For standard applications, the frequency of the uPower subsystem is 16 MHz. The oscillator is turned off in the uPower low-power mode.

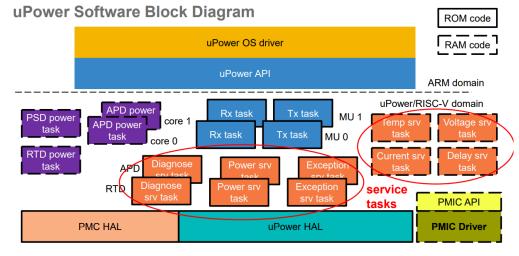

The following figure describes the main modules of the uPower firmware.

Figure 1. uPower software block diagram

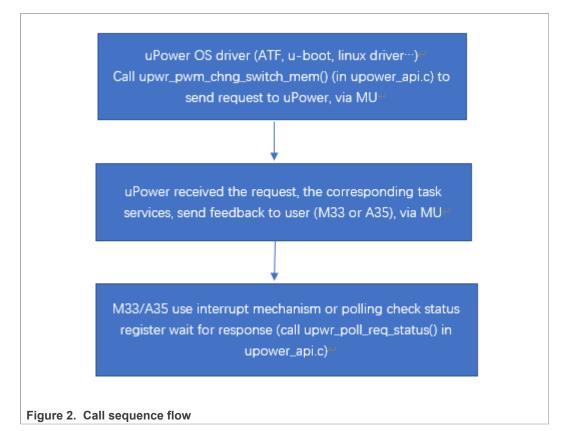

The call sequence flow for each API is similar. Take "turn on power switches" as an example.

### uPower Firmware User's Guide

## 4 Feature List

The uPower Firmware includes the following features:

- Process Monitor for device process corner evaluation

- Power Meter for device power domains consumption measurement

- Temperature Sensor for device temperature measurement

- Critical Path delay meter for critical path delay measurement

- · Messaging Units for communication with on-chip processors

- · I2C for communication with off-chip devices especially power sources

- Internal Voltage Meter (VMeter)

## 5 Release Package

#### Table 2. NXP uPower software release package

| 0.1              | <b>F</b> 11.11.1  |                                                                  |

|------------------|-------------------|------------------------------------------------------------------|

| Category         | File List         | Description                                                      |

| uPower_api_files | upower_defs.h     | The two header files contain the necessary                       |

|                  | upower_soc_defs.h | data structures for uPower API calls and power mode transitions. |

|                  | upower_api.h      | uPower API header file, listing all the supported APIs.          |

|                  | upower_api.c      | uPower API C language file.                                      |

© 2022 NXP B.V. All rights reserved.

### uPower Firmware User's Guide

| Category                           | File List                                                      | Description                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------------------------------------|----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| uPower_A1_firmware<br>_binary      | upower_fw.bin                                                  | uPower official release firmware binary:<br>upower_fw.bin, users need to integrate<br>this uPower firmware binary into OEM<br>container, same as the Cortex-M33 or<br>Cortex-A35 image, using different core<br>IDs. The uPower firmware image core ID<br>is 4. (The Cortex-M33 core ID is 1, and<br>the Cortex-A35 core ID is 2). For how to<br>build an OEM container, see the <i>i.MX Linux</i><br><i>User's Guide</i> (IMXLUG). |

| uPower_firmware_<br>porting_kit_A1 | pmicdrv                                                        | PMIC driver directory, including PCA9460<br>PMIC driver source code and necessary<br>uPower header files.                                                                                                                                                                                                                                                                                                                           |

|                                    | lib_upower_fw.a                                                | uPower firmware static library.                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                    | Release_note.txt                                               | Release Notes.                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                    | <pre>nxp_official_upower_ firmware_binary/u power_fw.bin</pre> | NXP official release upower firmware binary.                                                                                                                                                                                                                                                                                                                                                                                        |

|                                    | a1_rom_rc3_3.sym                                               | uPower ROM A1 symbol table.                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                    | linker_ram_final.ld                                            | uPower firmware linker file.                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                    | Makefile                                                       | Build command: make clean; make                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                    | Makefile_combine_<br>upower_fw_pmic                            | Use this Makefile to combine the uPower<br>firmware static library and PMIC driver<br>static library to generate the uPower<br>firmware binary.                                                                                                                                                                                                                                                                                     |

|                                    | Makefile_pmic_lib                                              | Use this Makefile to generate the PMIC driver static library.                                                                                                                                                                                                                                                                                                                                                                       |

### Table 2. NXP uPower software release package...continued

## 6 Power Domains

Power domains

- RealTime domain (RTD)

- Fusion DSP

- Fusion Always-on

- Fuses

- Cortex-M33

- Application domain (AD)

- Fast NIC

- Cortex-A35[0]

- Cortex-A35[1]

- Low Power Audio-Video domain (LPAVD)

- HiFi4

- DDR/DDR PHY

- PXP/EPDC

- GPU3D

- MIPI DSI

© 2022 NXP B.V. All rights reserved.

- MIPI CSI

- Always ON domain (DGO)

- VBAT domain

# 7 uPower Subsystem Block Diagram

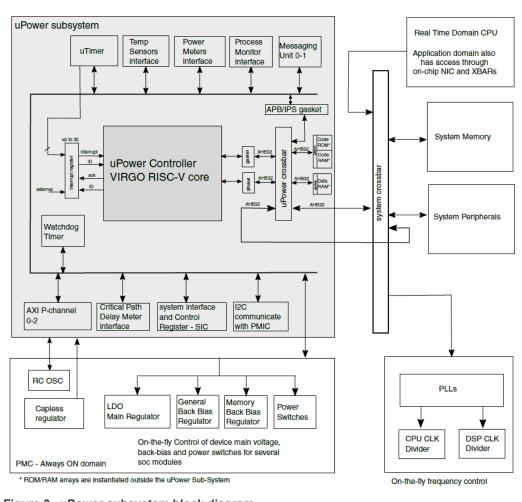

The following figure shows the uPower interface with emphasis on the system interface (AHB) and always on domain interface signals. It also shows the interrupt signals from various sources, internal to the subsystem and external.

Figure 3. uPower subsystem block diagram

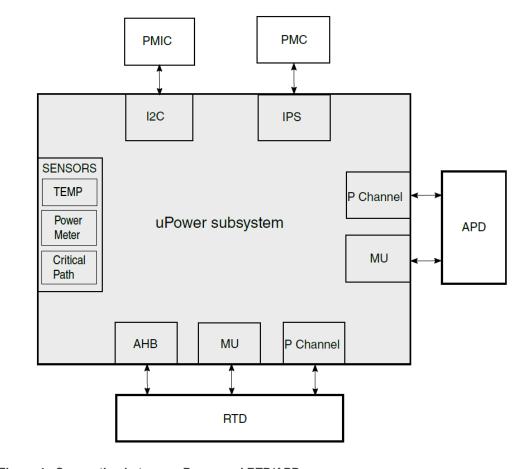

The following figure shows the uPower interfaces with other modules and power domains. Those interfaces are with the Real Time Domain (RTD), where the P-Channel, Messaging Unit (MU), and AHB interfaces are used. With the Application Domain (APD), the P Channel interface and MU interface are used. uPower interfaces with the Power Mode Controller (PMC) through an IPS interface and with an external PMIC through an I2C interface.

From the uPower subsystem block diagram, we can see that:

uPower has shared system memory (memory address: 0x28330000) to exchange data with Arm Cortex-M33/A35.

- uPower has a temperature sensor module to provide the measure temperature service.

- uPower has a Power meter module to provide the measure power consumption service.

- uPower has a VMeter module to provide measure voltage service.

- uPower has a process monitor module to provide the process monitor service.

- uPower communicates with the PMIC chip through I2C.

- uPower controls Power switches.

- uPower can write AOGPOR (General Purpose Output Register Always on domain).

The following figure shows the connection between uPower and RTD/APD.

Figure 4. Connection between uPower and RTD/APD

The MU module registers A and B sides are represented in the uPower subsystem, even though they are in the RTD and APD power domains. The uPower interface implements the MU IPS slave bus and other side band signals for both RTD and APD domains.

From the perspective of users (Arm Cortex-M33/A35), uPower mainly provides two functions:

- Provides APIs for Arm Cortex-M33/A35 runtime call.

- Assists Arm Cortex-M33/A35 to complete power mode transition tasks.

## 8 uPower API

uPower service requests are classified in Service Groups. Each Service Group has a set of related functions. The service groups are as follows:

- Exception Service Group upwr\_xcp\_\* Gathers functions that deal with errors and other processes outside the functional scope.

- Power Management Services Group upwr\_pwm\_\*

Functions to control switchs, configure power modes, and set internal voltages, etc.

- Delay Measurement Service Group upwr\_dlm\_\*

Delay measurement functions using the process monitor and delay meter.

- Voltage Measurement Servcie Group upwr\_vtm\_\* Functions for voltage measurements, power meter, and set/get PMIC rail voltage, etc

- Temperature Measurement Service Group upwr\_tpm\_\* Functions for temperature measurements.

For detailed function purposes and argument descriptions, see the *uPower API Reference Manual* (UPOWERAPIRM).

For the sample code of how to call the uPower API, see the SDK or BSP code.

For example, the sample code to initialize, see <u>Section 11.1</u>.

## 9 **Power Mode Transition**

i.MX 8ULP supports several different power modes for RTD and APD, including Active, Sleep, Deep Sleep, Power Down, Deep Power Down, and HOLD. These power mode transitions are initiated and controlled by Arm Cortex-M33/A35. Some transitions require the participation of uPower. Arm Cortex-M33/A35 can configure power switches, memory partitions, dombias mode, AFBB/RBB, PADs and PMIC under different power modes by configuring the power mode data structure stored in shared memory (memory address: 0x28330000).

This chapter describes the power modes, the connection between RTD/APD and uPower, and the meaning of the power mode data structure.

For how to do power mode transition on Arm Cortex-M33/A35 side, see the SDK/BSP source code and user guides.

### 9.1 RTD power mode transition

### 9.1.1 RTD connection

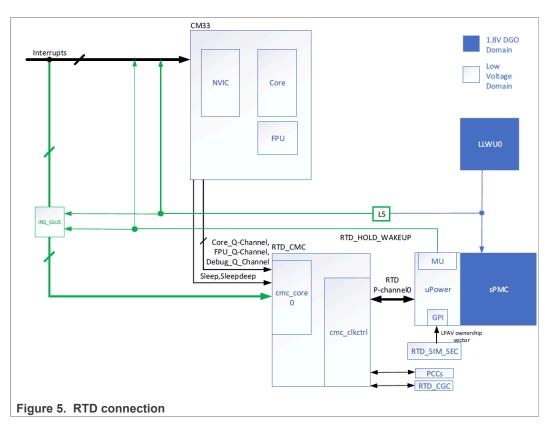

The following figure shows the connection between RTD and uPower, CMC, CGC, PCC, Interrupts WKUP.

uPower Firmware User's Guide

### 9.1.2 RTD clock mode

|        | Como     | Platform/AH | Bus/Slow |          |

|--------|----------|-------------|----------|----------|

| CKMODE | Core     | Master      | Slave    | Periph   |

| 0      | Clocking | Clocking    | NA       | Clocking |

| 1      | Gated    | Clocking    | NA       | Clocking |

| 3      | Gated    | Gated       | NA       | Clocking |

| 7      | Gated    | Gated       | NA       | Gated    |

**Note:** The clock mode is controlled by the CKMODE field of CMC register. See the Cortex-M33 SDK source code for details on how to program it.

### 9.1.3 RTD power modes

| LPMODE[4] | LPMODE[3] | LPMODE[2] | LPMODE[1] | LPMODE[0] | SoC Mode        |

|-----------|-----------|-----------|-----------|-----------|-----------------|

| 0         | 0         | 0         | 0         | 0         | Active          |

| 0         | 0         | 0         | 0         | 1         | Sleep           |

|           |           |           |           |           |                 |

| 0         | 0         | 0         | 1         | 1         | Deep Sleep      |

| 0         | 0         | 1         | 1         | 1         | Power Down      |

| 0         | 1         | 1         | 1         | 1         | Deep Power Down |

| 1         | 1         | 1         | 1         | 1         | HOLD            |

UPOWERUG

© 2022 NXP B.V. All rights reserved.

uPower Firmware User's Guide

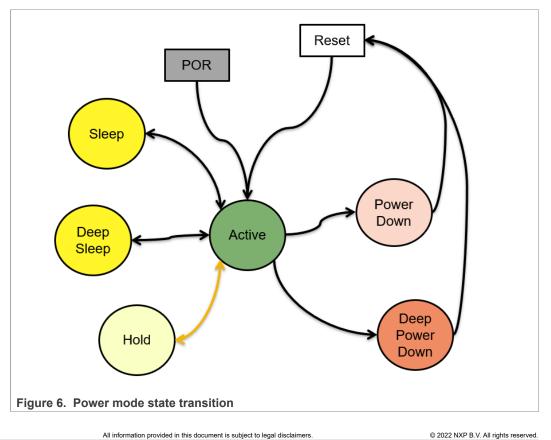

- Active

- Normal RUN mode

- All functional

- Low-power configuration using FW services

- Sleep

- Clock gating mode only

- No uPower engagement

- Low-power configuration using FW services before transitioning

- Fast entry and exit

- Deep Sleep

- uPower is engaged

- Low-power configuration using FW data structs (applied by FW)

- HOLD

- Transient state (automatic wakeup by uPower after configuration is applied)

- Used to safely apply low-power configuration

- Power Down

- Power gating mode

- All power switches are open

- Memories can be retained

- Deep Power Down

- Power gating mode

- All power switches are open

- External supplies are shut down

The following figure shows the power mode state transition diagrams for Cortex-M33.

### uPower Firmware User's Guide

### 9.1.4 Example of RTD low-power mode entry sequence

For example, the steps for RTD to enter lower-power mode are as follows:

- 1. Initialize uPower configuration data (RTD part), which is stored at (SSRAM) memory.

- See definition of struct ps\_pwr\_mode\_cfg\_t in the upower\_soc\_defs.h file for details.

- 2. Program CMC0 to notify the system (uPower) to enter Power Down mode.

- Write register CMC\_RTD.CKCTRL to control if the gate system clocks in low power mode.

- Write register CMC\_RTD.RTD\_PMPROT to remove write protection.

- Write register CMC\_RTD.DBGCTL.CMC\_DBGCTL\_SOD\_MASK to control whether to enable debug feature in low power mode.

- Write register CMC\_RTD.RTD\_PMCTRL.RTD\_LPMODE to configure which low power mode plan to enter.

- Write register SCB.SCR.SCB\_SCR\_SLEEPDEEP\_Msk to configure core SLEEPDEEP bit.

- \_\_DSB();

- WFI(); /\* RTD M33 pends here in low power mode

- \_\_ISB();

#### Note:

When Cortex-M33/A35 is triggered (by CMC) to enter low power mode, uPower starts the power mode transition task and the task loads the configuration data from SSRAM to set corresponding modules, e.g., power switches, memory partitions, PMIC registers, etc.

The global configuration data is initialized by uPower and users do not need to initialize it.

### 9.2 APD power mode transition

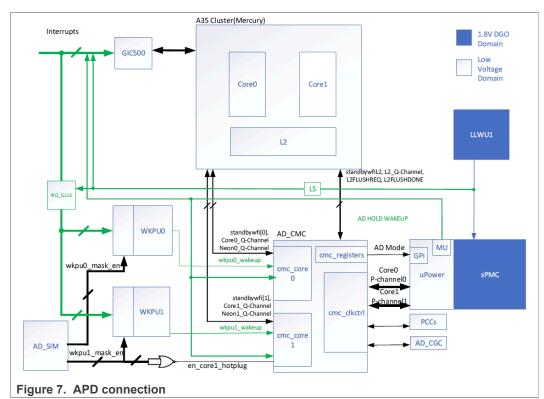

## 9.2.1 APD connection

### 9.2.2 APD clock modes

|        | Core     | Platform/AHI | Bus/Slow |          |

|--------|----------|--------------|----------|----------|

| CKMODE | Core     | Master       | Slave    | Periph   |

| 0      | Clocking | Clocking     | NA       | Clocking |

| 1      | Gated    | Clocking     | NA       | Clocking |

| 3      | Gated    | Gated        | NA       | Clocking |

| 7      | Gated    | Gated        | NA       | Gated    |

**Note:** The clock mode is controlled by the CKMODE field of CMC register. See the BSP source code for details on how to program it.

### 9.2.3 APD power modes

**Note:** Although ACTIVE DMA mode is listed here, but actually i.MX 8ULP does not support ACTIVE DMA mode at present. In addition, there is a bug in the uPower ROM, it uses ACTIVE MODE index instead of ACTIVE MODE. Therefore, as a workaround, when users need to use and configure ACTIVE mode, configure the shared memory pointed by the ACTIVE MODE index.

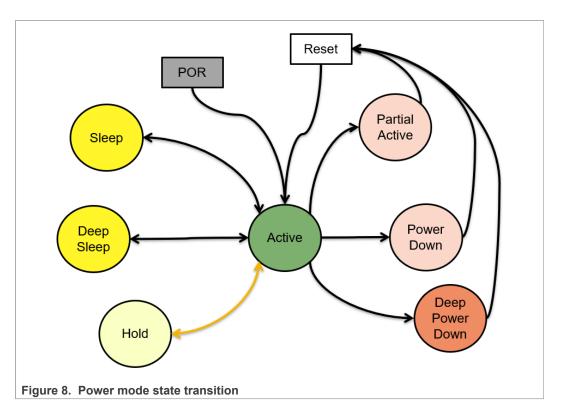

- Active

- Normal RUN mode

- All functional

uPower Firmware User's Guide

- Low-power configuration using FW services

- Sleep

- Clock gating mode only

- No uPower engagement

- Low-power configuration using FW services before transitioning

- Fast entry and exit

- Deep Sleep

- uPower is engaged

- Low-power configuration using FW data structs (applied by FW)

- Hold

- Temporary mode (automatic wakeup by uPower after configuration is applied)

- Used to safely apply low-power configuration

- Active DMA

- Transient state (automatic re-enter on previous low-power mode after handling the DMA)

- Partial Active

- Power gating mode

- Cortex-A35 complex and fast NIC domains are powered off

- Used to allow RTD using AD and AVD peripherals

- Power Down

- Power gating mode

- All power switches are open

- Memories can be retained

- Deep Power Down

- Power gating mode

- All power switches are open

- External supplies are shut down

The following figure shows the power mode state transition diagrams for Cortext-A35 domain.

uPower Firmware User's Guide

### 9.2.4 Example of APD low-power mode entry sequence

The steps for APD to enter lower-power mode are as follows:

- Initialize uPower configuration data (APD part), which is stored at (SSRAM) memory.

See definition of struct ps\_pwr\_mode\_cfg\_t in the upower\_soc\_defs.h file for details.

- Core sleep procedure:

- 1. Enable CA35 retention.

- 2. Disable data cache.

- 3. Clean and invalidate all data from L1 Data cache.

- 4. Disable data coherency with other cores in the cluster.

- 5. Mask interrupts on the core.

- 6. Execute an ISB instruction to ensure that all of the register changes from the previous steps have been committed.

- Execute a DSB SY instruction to ensure that all cache, TLB, and branch predictor maintenance operations issued by any core in the cluster device before the SMPEN bit is cleared have completed.

- 8. Execute a WFI instruction and wait until the STANDBYWFI output is asserted to indicate that the core is in idle and low-power state.

### 9.3 Domain power mode combinations

NR = Not recommended

No = Not supported in hardware

| CM33<br>CA35 <sup>1</sup> | Active <sup>2</sup> | Sleep           | Deep Sleep      | Power<br>Down    | Deep Power<br>Down |

|---------------------------|---------------------|-----------------|-----------------|------------------|--------------------|

| Active <sup>3</sup>       | YES                 | NR <sup>3</sup> | NR <sup>3</sup> | No <sup>5</sup>  | NO <sup>4,5</sup>  |

| Partial Active            | YES                 | YES             | YES             | No               | No                 |

| Sleep                     | YES                 | YES             | NR <sup>3</sup> | No <sup>5</sup>  | NO <sup>5</sup>    |

| Deep Sleep                | YES                 | YES             | YES             | No <sup>5</sup>  | NO <sup>5</sup>    |

| Power Down                | YES                 | YES             | YES             | YES <sup>6</sup> | YES                |

| Deep Power Down           | YES                 | YES             | YES             | YES <sup>6</sup> | YES                |

#### NOTES:

1. CA35 only supports static (w/o clock) RBB.

2. Active mode will also allow to enable RBB but will limit the operation frequency to 40Mhz.

- 3. No power advantage to keep CM33 in low power modes while CA35 is in active mode, though hardware supports this option

- No clock available for CA35 when CM33 is in "Deep Power Down" mode. There are also no power advantages using this mode.

- 5. 8ULP does not support any isolation from CM33 to CA35 domain so there is no possibility for CM33 to be kept in Power Down modes while CA35 in higher power modes.

- 6. CM33 domain can only enter Power Down mode once CA35 is in Power Down mode. CM33 must be active to be able to wake CA35 from Power Down mode. For the case where both CA35 and CM33 are in Deep Power Down and Power Down mode respectively, CM33 must wake-up first before CA35 can exit Power Down mode.

## 9.4 Power mode transition data structure

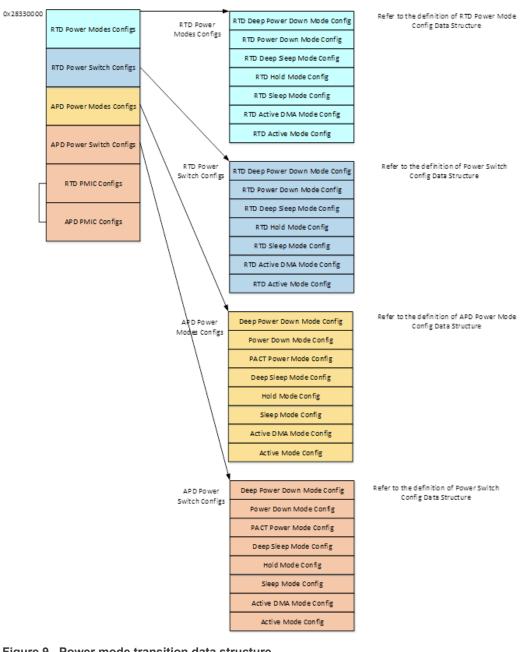

The following figure and tables describe the power mode configuration data structure, users (Arm Cortex-M33/A35) need to configure the power mode transition data located in shared memory. The memory address is 0x28330000. See struct ps\_pwr\_mode\_cfg in upower\_soc\_defs.h.

### uPower Firmware User's Guide

## Figure 9. Power mode transition data structure

For RTD power mode configuration, see upower\_soc\_defs.h, struct ps\_pwr\_mode\_ cfg\_t->ps\_rtd\_swt\_cfgs\_t.

#### Table 3. RTD power mode configuration

| Field     | ltem | Definition                            | Size<br>(byte) | Comment                                                                                                          |

|-----------|------|---------------------------------------|----------------|------------------------------------------------------------------------------------------------------------------|

| swt_board | -    | swt_board<br>configuration<br>pointer |                | The memory address of ps_pwr_mode_<br>cfg_t->ps_apd_pwr_mode_cfgs_t<br>(refer to Power Switch/Mem configuration) |

## uPower Firmware User's Guide

| Field      | Item            | Definition                            | Size<br>(byte) | Comment                                                                                                                                                                                       |

|------------|-----------------|---------------------------------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| swt_mem    | -               | swt-mem<br>configuration<br>pointer   | 4              | The memory address of ps_pwr_mode_<br>cfg_t->ps_apd_pwr_mode_cfgs_t -<br>>swt_mem (refer to Power Switch/Mem<br>configuration)                                                                |

| in_reg_cfg | volt            | Regulator<br>voltage<br>configuration | 4              | <ul> <li>Internal regulator configuration.</li> <li>Refer to the definition of data structure<br/>upwr_reg_cfg_t.</li> </ul>                                                                  |

|            | mode            | Regulator<br>mode<br>configuration    | 4              | HW register:<br>PMC.COREREG_CTRL.B.COREREGVL<br>PMC.COREREG_CTRL.B.COREREGM                                                                                                                   |

| pmic_cfg   | volt            | Regulator<br>voltage<br>configuration | 4              | <ul> <li>External regulator configuration.</li> <li>Refer to the definition of data structure upwr_reg_cfg_t.</li> </ul>                                                                      |

|            | mode            | Regulator<br>mode<br>configuration    | 4              | The Mode [3:0] field in this register controls<br>the PMIC signals: PMIC Stand-by Request,<br>PMIC Mode[2], PMIC Mode[1], and PMIC<br>Mode[0] respectively.<br>HW register:<br>SIC.AOPMICCR.R |

| pad_cfg    | pad_<br>close   | PMC PAD<br>close<br>configuration     | 4              | <ul> <li>Pad configuration for power transision.</li> <li>Refer to the definition of data structure<br/>upwr_pmc_pad_cfg_t.</li> </ul>                                                        |

|            | pad_<br>reset   | PMC PAD<br>reset<br>configuration     | 4              | Refer to "PAD Configuration".<br>HW register:<br>PMC.SYS_CTRL_PAD_0.PADRESET (4b)                                                                                                             |

|            | pad_<br>tqsleep | PMC PAD<br>TQ Sleep<br>configuration  | 4              | PMC.SYS_CTRL_PAD_0.PADCLOSE (4b)<br>PMC.SYS_CTRL_PAD_1.TQ_SLEEP (2b)                                                                                                                          |

| mon_cfg    | mon_hvd_<br>en  | PMC mon<br>HVD                        | 4              | <ul><li>Monitor configuration.</li><li>Refer to the definition of data structure</li></ul>                                                                                                    |

|            | mon_lvd_<br>en  | PMC mon<br>LVD                        | 4              | upwr_pmc_mon_rtd_cfg_t.<br>Actually, just use mon_hvd_en to represent<br>the entire power monitor configuration.                                                                              |

|            | mon_<br>lvdlvl  | PMC mon<br>LVDLVL                     | 4              | Do not use mon_lvd_en or mon_lvdlvl.<br>Set them to 0.<br>Refer to "Power Monitor Configuration".<br>HW register:<br>PMC.MON_CTRL_1<br>PMC.MON_INTC                                           |

### Table 3. RTD power mode configuration...continued

UPOWERUG User guide

### uPower Firmware User's Guide

| Field              | ltem     | Definition                             | Size<br>(byte) | Comment                                                                                                                                                                                                                                           |

|--------------------|----------|----------------------------------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| dombias_cfg        | mode     | Domain<br>bias mode<br>configuration   | 4              | <ul> <li>Domain Bias configuration.</li> <li>Refer to the definition of data structure<br/>UPWR_DOM_BIAS_CFG_T.</li> </ul>                                                                                                                        |

|                    | rbbn     | Reverse<br>back bias N<br>well         | 4              | HW register:<br>PMC.DOMBIAS_DCTRL_RTD.MODE 2b<br>(byte 0)                                                                                                                                                                                         |

|                    | rbbp     | Reverse<br>back bias P<br>well         | 4              | <pre>PMC.DOMBIAS_DCTRL_AVD.MODE 2b (byte 2) PMC.DOMBIAS_DCTRL_RTD.RBBNWVL 5b (byte 0) PMC.DOMBIAS_DCTRL_AVD.RBBNWVL 1b (byte 2) PMC.DOMBIAS_DCTRL_RTD.RBBPWVL 5b (byte 0) PMC.DOMBIAS_DCTRL_AVD.RBBPWVL 1b (byte 2) (refer to Dombias Mode)</pre> |

| membias_cfg        | en       | Memory<br>bias enable<br>configuration | 4              | <ul> <li>Memory Bias configuration.</li> <li>Refer to the definition of data structure<br/>UPWR_MEM_BIAS_CFG_T.</li> <li>HW register:</li> <li>PMC.MEMBIAS_DCTRL_0.MEMBIASEN<br/>(1b)</li> </ul>                                                  |

| pwrsys_lpm_<br>cfg | lpm_mode | Powersys<br>Iow-power<br>mode          | 4              | <ul> <li>pwrsys low power configuration.</li> <li>Refer to the definition of data structure<br/>upwr_powersys_cfg_t.</li> <li>Actually, do not use this item in the current<br/>i.MX 8ULP uPower.</li> </ul>                                      |

### Table 3. RTD power mode configuration...continued

For APD power mode configuration, see upower\_soc\_defs.h, struct ps\_pwr\_mode\_ cfg\_t->ps\_apd\_pwr\_mode\_cfgs\_t.

#### Table 4. APD power mode configuration

| Field              | ltem | Definition                        | Size<br>(byte) | Comment                                                                                   |

|--------------------|------|-----------------------------------|----------------|-------------------------------------------------------------------------------------------|

| swt_board_<br>offs | -    | swt_board<br>configuration offset | 4              | The offset of ps_apd_swt_<br>cfgs_t (refer to Power Switch/<br>Mem configuration)         |

| swt_mem_<br>offs   | -    | swt-mem configuration<br>offset   | 4              | The offset of ps_apd_swt_<br>cfgs_t->swt_mem (refer to<br>Power Switch/Mem configuration) |

UPOWERUG

## uPower Firmware User's Guide

| Field           | ltem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Definition                                                                                          | Size<br>(byte)                                                                                                                                                                                                                                                                                                          | Comment                                                                                                                                                                                                                  |  |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| pmic_cfg        | volt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Voltage configuration                                                                               | 4                                                                                                                                                                                                                                                                                                                       | External regulator configuration                                                                                                                                                                                         |  |

|                 | mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Mode configuration                                                                                  | 4                                                                                                                                                                                                                                                                                                                       | • Refer to the definition of data structure upwr pmic cfg t.                                                                                                                                                             |  |

|                 | mode_msk                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Mode mask                                                                                           | 4                                                                                                                                                                                                                                                                                                                       | The Mode[3:0] field in this<br>register controls the PMIC signal<br>PMIC Stand-by Request, PMIC<br>Mode[2], PMIC Mode[1], and<br>PMIC Mode[0] respectively.<br>Refer to vdetlvl in RM, SIC.<br>AOPMICCR and PMIC IC SPEC |  |

| pad_cfg         | pad_close                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | PMC PAD close<br>configuration                                                                      | 4                                                                                                                                                                                                                                                                                                                       | <ul> <li>Pad configuration for power<br/>transition.</li> </ul>                                                                                                                                                          |  |

|                 | pad_reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | PMC PAD reset configuration                                                                         | 4                                                                                                                                                                                                                                                                                                                       | <ul> <li>Refer to the definition of data<br/>structure upwr_pmc_pad_cfg_<br/>t.</li> </ul>                                                                                                                               |  |

|                 | pad_<br>tqsleep                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | PMC PAD TQ Sleep<br>configuration<br>Actually, this field is<br>reused to present<br>power monitor. | 4                                                                                                                                                                                                                                                                                                                       | <pre>t. HW register: PMC.SYS_CTRL_PAD_0.PADRES ET (4b) PMC.SYS_CTRL_PAD_0.PADCLC SE (4b) Note: pad_tqsleep is reused for power monitor.</pre>                                                                            |  |

| dombias_<br>cfg | mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Domain bias mode configuration                                                                      | 4                                                                                                                                                                                                                                                                                                                       | <ul><li>Domain Bias configuration.</li><li>Refer to the definition of data</li></ul>                                                                                                                                     |  |

|                 | rbbn                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Reverse back bias N<br>well                                                                         | 4                                                                                                                                                                                                                                                                                                                       | structure UPWR_DOM_BIAS_<br>CFG_T.<br>HW register:                                                                                                                                                                       |  |

|                 | rbbp       Reverse back bias P       4       PMC.DOMBIAS_APD.MODE       2b         well       PMC.DOMBIAS_AVD.MODE       2b       PMC.DOMBIAS_AVD.MODE       2b         PMC.DOMBIAS_AVD.MODE       2b       PMC.DOMBIAS_AVD.MODE       2b         PMC.DOMBIAS_AVD.MODE       2b       PMC.DOMBIAS_AVD.MODE       2b         PMC.DOMBIAS_APD.RBBNWVL       PMC.DOMBIAS_APD.RBBNWVL       PMC.DOMBIAS_APD.RBBNWVL         PMC.DOMBIAS_APD.RBBPWVL       PMC.DOMBIAS_APD.RBBPWVL       PMC.DOMBIAS_APD.RBBPWVL |                                                                                                     | PMC.DOMBIAS_DCTRL_<br>APD.MODE 2b (byte 0)<br>PMC.DOMBIAS_DCTRL_<br>AVD.MODE 2b (byte 2)<br>PMC.DOMBIAS_DCTRL_<br>APD.RBBNWVL 1b (byte 0)<br>PMC.DOMBIAS_DCTRL_<br>APD.RBBNWVL 1b (byte 2)<br>PMC.DOMBIAS_DCTRL_<br>APD.RBBPWVL 1b (byte 0)<br>PMC.DOMBIAS_DCTRL_<br>APD.RBBPWVL 1b (byte 2)<br>(refer to Dombias Mode) |                                                                                                                                                                                                                          |  |

| membias_<br>cfg | en                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Memory bias enable configuration                                                                    | 4                                                                                                                                                                                                                                                                                                                       | <ul> <li>Memory Bias configuration.</li> <li>Refer to the definition of data<br/>structure UPWR_MEM_BIAS_<br/>CFG_T.</li> <li>HW register:<br/>PMC.MEMBIAS_DCTRL_<br/>0.MEMBIASEN (1b)</li> </ul>                        |  |

### Table 4. APD power mode configuration...continued

### 9.4.1 Power Switch/Mem configuration

Refer to upower\_soc\_defs.h, struct ps\_pwr\_mode\_cfg\_t->ps\_rtd\_swt\_cfgs\_t and struct ps\_pwr\_mode\_cfg\_t->ps\_apd\_swt\_cfgs\_t, and refer to power switch and memory partition tables.

| Table 5. | Power | Switch/Mem | configuration |

|----------|-------|------------|---------------|

|----------|-------|------------|---------------|

| Field                  | Item                               | Definition                                    | Size<br>(byte)                                                | Comment                                                                                                                                 |

|------------------------|------------------------------------|-----------------------------------------------|---------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| swt_board              | on                                 | Switch on state, 1 bit per instance           | 4                                                             | • There is 1 instance of switch<br>board. 1 instance is a set of 32                                                                     |

|                        | mask                               | Actuation mask, 1 bit<br>per instance         | 4                                                             | <pre>switches. See Section 9.4.4. • See data structure upwr_ switch_board_t. • bit = 1 applies on bit HW register: PMC.PSW_CTRL_1</pre> |

| swt_mem                | array                              | RAM/ROM array<br>state, 1 bit per<br>instance | 4                                                             | <ul> <li>There are 2 instances of switch<br/>memory. 1 instance is a set of 32<br/>switches. See <u>Section 9.4.5</u>.</li> </ul>       |

|                        | state                              | RAM/ROM peripheral state, 1 bit per instance  | 4                                                             | <ul> <li>See data structure upwr_mem_<br/>switches_t.</li> <li>bit = 1 applies on bit</li> </ul>                                        |

| mask<br>array<br>perif | Actuation mask, 1 bit per instance | 4                                             | HW register:<br>PMC.SRAM_CTRL_ARRAY_0<br>PMC.SRAM_CTRL_PERI_0 |                                                                                                                                         |

|                        | array                              | RAM/ROM array<br>state, 1 bit per<br>instance | 4                                                             | PMC.SRAM_CTRL_ARRAY_1<br>PMC.SRAM_CTRL_PERI_1                                                                                           |

|                        | perif                              | RAM/ROM peripheral state, 1 bit per instance  | 4                                                             |                                                                                                                                         |

|                        | mask                               | Actuation mask, 1 bit per instance            | 4                                                             |                                                                                                                                         |

### 9.4.2 PAD configuration

#### Table 6. Pad configuration

| Pad signal | Description                                                                                                                                                      | Usage                                                                          | Bit correspondence                                                 |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|--------------------------------------------------------------------|

| PADRESET   | PADRESETn<br>This register describes<br>the behavior from PAD<br>signal the PADRESET.<br>0000b – Pad reset n is<br>released<br>0001b – Pad reset n is<br>active. | pad_reset, when asserted,<br>resets all this latching logic<br>within the pad. | Bit 0: PTA, PTA_<br>JTAG<br>Bit 1: PTB<br>Bit 2: PTE<br>Bit 3: PTF |

| UPOWERUG   |  |

|------------|--|

| User guide |  |

## uPower Firmware User's Guide

| Table 6. | Pad | configurationcontinued |

|----------|-----|------------------------|

|----------|-----|------------------------|

| Pad signal | Description                                                                                                                                              | Usage                                                                                       | Bit correspondence                                                 |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| PADCLOSE   | PADCLOSEn<br>This register describes<br>the behavior from PAD<br>signal the PADCLOSE.<br>0000b – Pad n is not<br>isolated<br>0001b – Pad n is isolated   | pad_close helps to latch the<br>IBE value in the pad – this is<br>the one enabling the PAD. | Bit 0: PTA, PTA_<br>JTAG<br>Bit 1: PTB<br>Bit 2: PTE<br>Bit 3: PTF |

| TQ_SLEEP   | TQ_SLEEPn<br>This register describes<br>the behavior from PAD<br>signal the TQ_SLEEP.<br>00b – Pad no change<br>01b – Pad n is in low<br>power condition | pad_tqsleep should have<br>a similar implementation for<br>HSGPIOs as pad_close.            | Bit 0: PTC<br>Bit 1: PTD                                           |

### Table 7. Pad reset

| POR             | Asserted with 1.8v Por and de-asserted after 1.1v > LVD.                                         |  |

|-----------------|--------------------------------------------------------------------------------------------------|--|

| Power Down      | If configured, asserts before domain switch is opened. De-asserts after domain switch is closed. |  |

| Deep Power Down | If configured, asserts before domain switch is opened. De-asserts after domain switch is closed. |  |

#### Table 8. Pad close

| POR             | Asserted with 1.8v Por and de-asserted after 1.1v > LVD.                                                                                                                                                                           |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Deep Sleep      | If configured, asserts with mode entry. Exits with mode exit.                                                                                                                                                                      |

| Power Down      | • If padreset is configured: asserts beforemode enters. De-assests after mode exits. (For APD/AVD: If an indication that VDD_DIG1 is off, it is preferrable to use it).                                                            |

|                 | • If padreset is not configured: asserts before mode enters. De-<br>assests after mode exits. (For APD/AVD: If an indication that VDD_<br>DIG1 is off, it is preferrable to use it) and application software writes to<br>ISO_ACK. |

|                 | RTD: padreset[0] affects padclose[0]; padreset[1] affects padclose[1].<br>APD/AVD: padreset[2] affects padclose[2]; padreset[3] affects<br>padclose[3].                                                                            |

| Deep Power Down | • If padreset is configured: asserts beforemode enters. De-assests after mode exits. (For APD/AVD: If an indication that VDD_DIG1 is off, it is preferrable to use it).                                                            |

|                 | • If padreset is not configured: asserts beforemode enters. De-assests after mode exits. (For APD/AVD: If an indication that VDD_DIG1 is off, it is preferrable to use it) and application software writes to ISO_ACK.             |

|                 | RTD: padreset[0] affects padclose[0]; padreset[1] affects padclose[1].                                                                                                                                                             |

|                 | APD/AVD: padreset[2] affects padclose[2]; padreset[3] affects<br>padclose[3].                                                                                                                                                      |

### uPower Firmware User's Guide

### Table 9. TQ\_Sleep

| Sleep           | De-asserted.                                                       |

|-----------------|--------------------------------------------------------------------|

| Deep Sleep      | If configured, asserts with mode entry. De-asserts with mode exit. |

| Power Down      | If configured, asserts with mode entry. De-asserts with mode exit. |

| Deep Power Down | If configured, asserts with mode entry. De-asserts with mode exit. |

## 9.4.3 Power monitor configuration

RTD: LVD1, HVD1

APD: LVD2, HVD2

AVD: LVD3, HVD3

LVD and HVD register description table

| Item    | Description                         | Value                                                                                  |

|---------|-------------------------------------|----------------------------------------------------------------------------------------|

| HVD1_EN | RTD High Voltage Detector<br>Enable | 0b - HVD1 disabled<br>1b - HVD1 enabled                                                |

| LVD1_EN | RTD Low Voltage Detector Enable     | 0b – LVD1 disabled<br>1b – LVD1 enabled                                                |

| LVD1LVL | LVD1 Failing Trip Voltage           | 0b0000 - 0.720V<br><value> - 0.650V + <value>x25mV<br/>0b1111 - 0.945V</value></value> |

| HVD1IE  | HVD1 Interrupt Enable               | 0b - Interrupt disabled<br>1b - Interrupt enabled                                      |

| LVD1IE  | LVD1 Interrupt Enable               | 0b - Interrupt disabled<br>1b - Interrupt enabled                                      |

| HVD1RE  | HVD1 Reset Enable                   | 0b - Reset disabled<br>1b - Reset enabled                                              |

| HVD1RE  | LVD1 Reset Enable                   | 0b - Reset disabled<br>1b - Reset enabled                                              |

| HVD2_EN | APD High Voltage Detector<br>Enable | 0b – HVD2 disabled<br>1b – HVD2 enabled                                                |

| LVD2_EN | APD Low Voltage Detector Enable     | 0b - LVD2 disabled<br>1b - LVD2 enabled                                                |

| LVD2LVL | LVD2 Failing Trip Voltage           | 0b0000 - 0.720V<br><value> - 0.650V + <value>x25mV<br/>0b1111 - 0.945V</value></value> |

| HVD2IE  | HVD2 Interrupt Enable               | 0b - Interrupt disabled<br>1b - Interrupt enabled                                      |

| LVD2IE  | LVD2 Interrupt Enable               | 0b - Interrupt disabled<br>1b - Interrupt enabled                                      |

| LVD3LVL | LVD3 Failing Trip Voltage           | 0b0000 - 0.720V<br><value> - 0.650V + <value>x25mV<br/>0b1111 - 0.945V</value></value> |

UPOWERUG

22 / 39

© 2022 NXP B.V. All rights reserved.

uPower Firmware User's Guide

| Item    | Description                         | Value                                             |

|---------|-------------------------------------|---------------------------------------------------|

| HVD3_EN | AVD High Voltage Detector<br>Enable | 0b – HVD2 disabled<br>1b – HVD2 enabled           |

| LVD3_EN | AVD Low Voltage Detector Enable     | 0b - LVD3 disabled<br>1b - LVD3 enabled           |

| HVD3IE  | HVD3 Interrupt Enable               | 0b - Interrupt disabled<br>1b - Interrupt enabled |

| LVD3IE  | LVD3 Interrupt Enable               | 0b - Interrupt disabled<br>1b - Interrupt enabled |

| HVD3RE  | HVD3 Reset Enable                   | 0b - Reset disabled<br>1b - Reset enabled         |

| LVD3RE  | LVD3 Reset Enable                   | 0b - Reset disabled<br>1b - Reset enabled         |

Table 10. Power monitor configuration...continued

The comment and code in upower soc defs.h:

```

/* LVD/HVD monitor config for a single domain */

/* Domain + AVD monitor config

* For RTD, mapped in mon cfg.mon hvd en

* For APD, mapped temporarily in pad cfg.pad tqsleep

*/

typedef union upwr mon cfg union t {

volatile uint32 t

R:

struct {

/* Original config, not change */

volatile uint32_t

rsrv 1

: 8;

/* DOM */

dom_lvd_irq_ena : 1;

dom_lvd_rst_ena : 1;

dom_hvd_irq_ena : 1;

dom_hvd_rst_ena : 1;

dom_lvd_lvl : 4;

dom_lvd_ena : 1;

volatile uint32 t

volatile uint32<sup>-</sup>t

volatile uint32<sup>-</sup>t

volatile uint32_t

volatile uint32_t

volatile uint32_t

volatile uint32<sup>-</sup>t

dom hvd ena

: 1;

/* AVD */

volatile uint32_t

avd_lvd_irq_ena : 1;

avd_lvd_rst_ena : 1;

avd_hvd_irq_ena : 1;

avd_hvd_rst_ena : 1;

avd_lvd_lvl_

volatile uint32 t

volatile uint32_t

volatile uint32_t

avd_lvd_lvl : 4;

avd_lvd_ena : 1;

avd_hvd_ena : 1;

volatile uint32_t

volatile uint32_t

volatile uint32<sup>t</sup>

}

в;

} upwr mon cfg t;

```

If Cortex-M33 configures power monitor during RTD power mode transition, dom\_lvd\* and dom\_hvd\* represent RTD (LVD1 and HVD1), and avd\_lvd\* and avd\_hvd\* represent AVD (LVD3 and HVD3). Only when RTD owns AVD, it takes effect.

If Cortex-A35 configures power monitor during APD power mode transition, dom\_lvd\* and dom\_hvd\* represent APD (LVD2 and HVD2), and avd\_lvd\* and avd\_hvd\* represent AVD (LVD3 and HVD3). Only when APD owns AVD, it takes effect.

For example, in RTD active mode configuration, configure the value to **0xdeb3a00**. The following table lists the meanings of the binary values: 1101 1110 1011 0011 1010 0000 0000.

| Table 11. Binary values       |                           |                                  |  |  |  |  |

|-------------------------------|---------------------------|----------------------------------|--|--|--|--|

| Structure Field               | Value                     | Description                      |  |  |  |  |

| rsrv_1                        | 0000 0000                 | Reserved                         |  |  |  |  |

| dom_lvd_irq_ena               | 0                         | Disables RTD LVD interrupt       |  |  |  |  |

| dom_lvd_rst_ena               | 1                         | Enables RTD LVD reset            |  |  |  |  |

| dom_hvd_irq_ena               | 0                         | Disables RTD HVD interrupt       |  |  |  |  |

| dom_hvd_rst_ena               | 1                         | Enables RTD HVD reset            |  |  |  |  |

| dom_lvd_lvl                   | 0011                      | RTD LVD1 Failing Trip<br>Voltage |  |  |  |  |

| dom_lvd_ena                   | 1                         | Enables HVD for RTD              |  |  |  |  |

| dom_hvd_ena                   | 1                         | Enables LVD for RTD              |  |  |  |  |

| If RTD owns AVD, apply the fo | llowing AVD configuration |                                  |  |  |  |  |

| avd_lvd_irq_ena               | 0                         | Disables AVD LVD interrupt       |  |  |  |  |

| avd_lvd_rst_ena               | 1                         | Enables AVD LVD reset            |  |  |  |  |

| avd_hvd_irq_ena               | 0                         | Disables AVD HVD interrupt       |  |  |  |  |

| avd_hvd_rst_ena               | 1                         | Enables AVD HVD reset            |  |  |  |  |

| avd_lvd_lvl                   | 0111                      | AVD LVD3 Failing Trip<br>Voltage |  |  |  |  |

| avd_lvd_ena                   | 1                         | Enables LVD for AVD              |  |  |  |  |

| avd_hvd_ena                   | 1                         | Enables HVD for AVD              |  |  |  |  |

Table 11. Binary values

### 9.4.4 Power switches

This power switches table is also included in the i.MX 8ULP Reference Manual.

| Table | 12. | Power switches |

|-------|-----|----------------|

| IGNIC |     |                |

| Function             | Logical Power Switch | Domain | POR      |

|----------------------|----------------------|--------|----------|

| RTD (A)              | PS0                  | RTD    | Enabled  |

| RTD (B)              |                      |        |          |

| Fusion               | PS1                  |        | Disabled |

| A35[0] Core          | PS2                  | APD    | Disabled |

| A35[1] Core          | PS3                  |        |          |

| Mercury L2 Cache [1] | PS4                  |        |          |

| Fast NIC / Mercury   | PS5                  |        |          |

| APD Periph.          | PS6                  |        |          |

| GPU3D                | PS7                  | AVD    | Disabled |

| HiFi4                | PS8                  |        |          |

| DDR Controller       | PS9,10,11,12         |        |          |

© 2022 NXP B.V. All rights reserved.

uPower Firmware User's Guide

| Function         | Logical Power Switch | Domain     | POR      |

|------------------|----------------------|------------|----------|

| PXP, EPDC        | PS13                 |            |          |

| MIPI DSI         | PS14                 |            |          |

| MIPI CSI         | PS15                 |            |          |

| NIC AV / Periph. | PS16                 |            |          |

| Fusion AO        | PS17                 | RTD        | Disabled |

| FUSE             | PS18                 |            | Enabled  |

| uPower           | PS19                 | RTD/uPower | Disabled |

#### Table 12 Dowe e wite k

## 9.4.5 Memory partitions

This memory partitions table is also included in the i.MX 8ULP Reference Manual.

| Partition # | IOs Supply<br>Source | Memory<br>Cell Suply<br>Source | Memories controlled                      | Domain          | POR      |

|-------------|----------------------|--------------------------------|------------------------------------------|-----------------|----------|

| 0           | PS2                  | PS2                            | CA35 Core 0 L1 cache                     | Application     | Disabled |

| 1           | PS3                  | PS3                            | CA35 Core 1 L1 cache                     |                 |          |

| 2           | PS5                  | PS5                            | L2 Cache 0                               |                 |          |

| 3           | PS4                  | PS4                            | L2 Cache 1                               |                 |          |

| 4           | PS5                  | PS5                            | L2 Cache victim/tag                      |                 |          |

| 5           | PS5                  | PS5                            | CAAM Secure RAM                          |                 |          |

| 6           | PS6                  | PS6                            | DMA1 RAM                                 |                 |          |

| 7           | PS6                  | PS6                            | FlexSPI2 FiFO, Buffer                    |                 |          |

| 8           | PS6                  | PS6                            | SRAM0                                    |                 |          |

| 9           | PS6                  | PS6                            | AD ROM                                   |                 |          |

| 10          | PS5                  | VDD_DIG1                       | USB0 TX/RX RAM                           |                 |          |

| 11          | PS6                  | VDD_DIG1                       | uSDHC0 FIFO RAM                          |                 |          |

| 12          | PS6                  | PS6                            | uSDHC1 FIFO RAM                          |                 |          |

| 13          | PS5                  | PS5                            | uSDHC2 FIFO and<br>USB1 TX/RX RAM        |                 |          |

| 14          | PS6                  | PS6                            | GIC RAM                                  |                 |          |

| 15          | PS5                  | PS5                            | ENET TX FIXO                             |                 |          |

| 16          | PS6                  | VDD_DIG1                       | Brainshift                               |                 |          |

| 17          | PS13                 | PS13                           | DCNano Tile2Linear<br>and RGB Correction | Audio-<br>Video | Disabled |

| 18          | PS13                 | PS13                           | DCNano Cursor and<br>FIFO                |                 |          |

| 19          | PS10                 | PS10                           | EPDC LUT                                 | 1               |          |

| 20          | PS10                 | PS10                           | EPDC FIFO                                | 1               |          |

Table 13. Memory partitions

## uPower Firmware User's Guide

| Partition # | IOs Supply<br>Source | Memory<br>Cell Suply<br>Source | Memories controlled         | Domain | POR |

|-------------|----------------------|--------------------------------|-----------------------------|--------|-----|

| 21          | PS13                 | PS13                           | DMA2 RAM                    |        |     |

| 22          | PS13                 | PS13                           | GPU2D RAM Group 1           |        |     |

| 23          | PS13                 | PS13                           | GPU2D RAM Group 2           |        |     |

| 24          | PS7                  | PS7                            | GPU3D RAM Group 1           |        |     |

| 25          | PS7                  | PS7                            | GPU3D RAM Group 2           |        |     |

| 26          | PS8                  | PS8                            | HiFi4 Caches, IRAM,<br>DRAM | -      |     |

| 27          | PS13                 | PS13                           | ISI Buffers                 |        |     |

| 28          | PS13                 | PS13                           | MIPI-CSI FIFO               |        |     |

| 29          | PS13                 | PS13                           | MIPI-DSI FIFO               |        |     |

| 30          | PS10                 | PS10                           | PXP Caches, Buffers         | 1      |     |

| 31          | PS13                 | PS13                           | SRAM1                       | 1      |     |

### Table 13. Memory partitions...continued

#### Table 14. Memory partitions

| Partition # | IOs Supply<br>Source | Memory<br>Cell Suply<br>Source | Memories controlled                      | Domain    | POR      |

|-------------|----------------------|--------------------------------|------------------------------------------|-----------|----------|

| 32          | PS0                  | PS0                            | Casper RAM                               | Real-Time | Disabled |

| 33          | PS0                  | PS0                            | DMA0 RAM                                 |           |          |

| 34          | PS0                  | PS0                            | FlexCAN RAM                              |           |          |

| 35          | PS0                  | PS0                            | FlexSPI0 FIFO, Buffer                    |           | Enabled  |

| 36          | PS0                  | PS0                            | FlexSPI1 FIFO, Buffer                    |           | Disabled |

| 37          | PS0                  | PS0                            | CM33 Cache Cache                         |           | Enabled  |

| 38          | PS0                  | PS0                            | PowerQuad RAM                            |           | Disabled |

| 39          | PS0                  | PS0                            | M33-ETF RAM                              | -         |          |

| 40          | PS0                  | PS0                            | Sentinel PKC, Data<br>RAM1, Inst RAM 0/1 | _         | Enabled  |

| 41          | PS0                  | PS0                            | Sentinel ROM                             |           |          |

| 42          | PS16/uPower          | PS16/uPower                    | uPower IRAM/DRAM                         |           | Enabled  |

| 43          | PS16/uPower          | PS16/uPower                    | uPower ROM                               | -         |          |

| 44          | PS0                  | PS0                            | CM33 ROM                                 | 1         | Enabled  |

| 45          | PS0                  | VDD_DIG0                       | SSRAM Partition 0                        | 1         |          |

| 46          | PS0                  | VDD_DIG0                       | SSRAM Partition 1                        | 1         |          |

| 47          | PS0                  | VDD_DIG0                       | SSRAM Partition 2,3,4                    | 1         |          |

| 48          | PS0                  | VDD_DIG0                       | SSRAM Partition 5                        | 1         |          |

| 49          | PS0                  | VDD_DIG0                       | SSRAM Partition 6                        | 1         |          |

UPOWERUG

uPower Firmware User's Guide

| Partition # | IOs Supply<br>Source | Memory<br>Cell Suply<br>Source | Memories controlled              | Domain | POR |

|-------------|----------------------|--------------------------------|----------------------------------|--------|-----|

| 50          | PS0                  | VDD_DIG0                       | SSRAM Partition 7_a<br>(128KB)   |        |     |

| 51          | PS0                  | VDD_DIG0                       | SSRAM Partition 7_b<br>(64KB)    |        |     |

| 52          | PS0                  | VDD_DIG0                       | SSRAM Partition 7_c<br>(64KB)    |        |     |

| 53          | PS0                  | VDD_DIG0                       | Sentinel Data RAM0,<br>Inst RAM2 |        |     |

Table 14. Memory partitions...continued

### 9.4.6 RTD and APD power mode PMIC configuration

User (Arm Cortex-M33/A35) can configure PMIC IC during power mode transition. For example, turn on/off one regulator, adjust the voltage of one regulator...

There are two situations:

- 1. RTD/APD enters lower power mode: uPower first operates power switches, memory partitions, pads, etc., and then configures PMIC.

- 2. RTD/APD exits lower power mode: uPower first configures PMIC, and then operates power switches, memory partitions, pads, etc.

For the sample code, see <u>Section 11.3</u>.

#### 9.4.7 DOMBIAS mode