# Freescale Semiconductor, Inc. User's Guide

Document Number: VYBRIDHDUG

Rev. 1, 05/2015

# Hardware Development Guide for Vybrid Family of MCUs

# 1 About This Document

#### 1.1 Overview

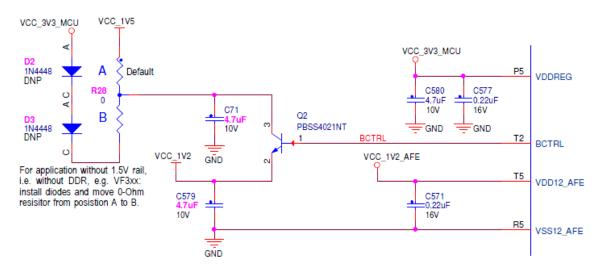

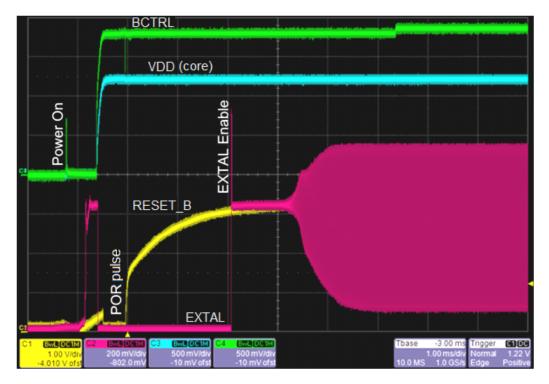

The purpose of this document is to help hardware engineers design and test their boards based on the Vybrid series of processors. It provides information on design checklists and board layout recommendations to ensure first-pass success and pave ways to avoid board bring-up problems. It also provides information on board-level testing and simulation such as properly configuring the JTAG tools, using BSDL for board-level testing, using the IBIS model for electrical integrity simulation, and more.

Engineers are expected to have a working understanding of board-layout principles and terminology, IBIS modeling, BSDL testing, and common board-hardware terminology.

# 1.2 Devices supported

This Hardware Development Guide currently supports the VF3xx, VF5xx, VF6xx, VF3xxR, and VF5xxR families of processors.

#### **Contents**

| 1.  | About This Document                  |

|-----|--------------------------------------|

| 2.  | Design Checklist 6                   |

| 3.  | Layout Recommendations               |

| 4.  | Requirements for Power Management 47 |

| 5.  | Root Clocks                          |

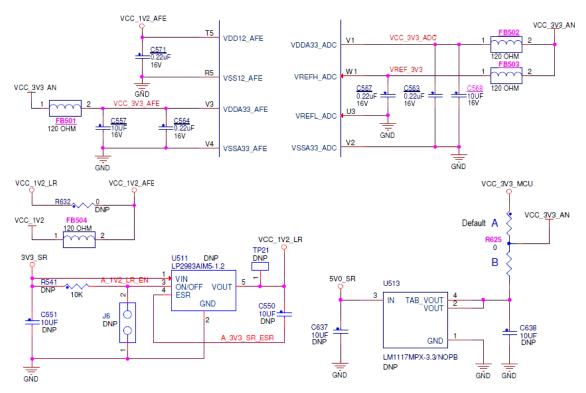

| 6.  | Processor Expert Tool                |

| 7.  | Debug Interfaces                     |

| 8.  | Avoiding Board Bring-up Problems 53  |

| 9.  | Understanding the IBIS Model 59      |

| 0.  | Using Manufacturing Tool 71          |

| 11. | Using BSDL for Board-level Testing   |

| 2.  | Using MAC (Ethernet) Interface       |

| 3.  | Revision history 76                  |

**About This Document**

#### 1.3 Essential reference

This guide is intended as a companion to the Vybrid-family chip reference manuals and data sheets. For reflow profile and thermal limits during soldering, see the *AN3298 "Solder Joint Temperature and Package Peak Temperature"* application note, which is available on <a href="https://www.freescale.com">www.freescale.com</a>.

# 1.4 Suggested reading

This section lists additional reading that provides background for the information in this guide as well as general information about the architecture.

#### 1.4.1 General information

The following documentation provides useful information about the ARM<sup>®</sup> processor architecture and computer architecture in general:

For information about the ARM® Cortex® A5 processor see:

• http://www.arm.com/products/processors/cortex-a/cortex-a5.phpo

For information about the ARM Cortex M4 processor see:

- http://www.arm.com/products/processors/cortex-m/cortex-m4-processor.php

- Computer Architecture: A Quantitative Approach (Fourth Edition) by John L. Hennessy and David A. Patterson

- Computer Organization and Design: The Hardware/Software Interface (Second Edition) by David A. Patterson and John L. Hennessy

The following documentation provides useful information about high-speed board design:

- Right the First Time A Practical Handbook on High Speed PCB and System Design Volumes I

& II Lee W. Ritchey (Speeding Edge) ISBN 0-9741936-0-72

- Signal and Power Integrity Simplified (2nd Edition) Eric Bogatin (Prentice Hall) ISBN 0-13-703502-0

- High Speed Digital Design A Handbook of Black Magic Howard W. Johnson & Martin Graham (Prentice Hall) ISBN 0-13-395724-1

- High Speed Signal Propagation Advanced Black Magic Howard W. Johnson & Martin Graham (Prentice Hall) ISBN 0-13-084408-X

- High Speed Digital System Design A handbook of Interconnect Theory and Practice Hall, Hall and McCall (Wiley Interscience 2000) ISBN 0-36090-2

- Signal Integrity Issues and Printed Circuit Design Doug Brooks (Prentice Hall) ISBN 0-13-141884-X

- PCB Design for Real-World EMI Control Bruce R. Archambeault (Kluwer Academic Publishers Group) ISBN 1-4020-7130-2

- Digital Design for Interference Specifications A Practical Handbook for EMI Suppression David L. Terrell & R. Kenneth Keenan (Newnes Publishing) ISBN 0-7506-7282-X

- Electromagnetic Compatibility Engineering Henry Ott (1st Edition John Wiley and Sons) ISBN 0-471-85068-3

- Introduction to Electromagnetic Compatibility Clayton R. Paul (John Wiley and Sons) ISBN 978-0-470-18930-6

- Grounding & Shielding Techniques Ralph Morrison (5th Edition John Wiley & Sons) ISBN 0-471-24518-6

- EMC for Product Engineers Tim Williams (Newnes Publishing) ISBN 0-7506- 2466-3

#### 1.5 Related documentation

For related Freescale documentation, see www.freescale.com. Additional literature is published as new Freescale products become available.

#### 1.6 Conventions

This document uses the following notational conventions:

- Courier used to indicate commands, command parameters, code examples, and file and directory names

- Italics italics indicates command or function parameters

- **Bold** function names are written in bold

- cleared / set when a bit takes the value zero, it is said to be cleared; when it takes a value of one, it is said to be set

- **mnemonics** instruction mnemonics are shown in lowercase bold; book titles in text are set in italics

- sig\_name internal signals are written in all lowercase

- *nnnn nnnn*h denotes hexadecimal number

- 0x alternate notation denoting hexadecimal number

- 0b denotes binary number

- rA, rB instruction syntax used to identify a source GPR

- rD instruction syntax used to identify a destination GPR

- REG[FIELD] abbreviations for registers are shown in uppercase text; specific bits, fields, or ranges appear in brackets; for example, MSR[LE] refers to the little-endian mode enable bit in the machine state register

- x in some contexts, such as signal encodings, an unitalicized x indicates a "Don't Care"

- x an italicized x indicates an alphanumeric variable

- n, m an italicized n indicates a numeric variable

#### **NOTE**

In this guide, notation for all logical, bit-wise, arithmetic, comparison, and assignment operations follow C Language conventions.

**About This Document**

# 1.7 Signal conventions

- $\bullet$  RESET an overbar indicates that a signal is active when low

- \_b, \_B alternate notation indicating an active-low signal

- *signal\_name* lowercase italics is used to indicate internal signals

# 1.8 Acronyms and abbreviations

Table 1 defines the acronyms and abbreviations used in this document.

Table 1. Definitions and acronyms

| Term  | Definition                                         |  |

|-------|----------------------------------------------------|--|

| AC    | Alternating Current                                |  |

| AFE   | Analog Front End                                   |  |

| ARM   | Advanced RISC Machines (processor architecture)    |  |

| ASCII | American Standard Code for Information Interchange |  |

| BGA   | Ball Grid Array (package)                          |  |

| ВОМ   | Bill Of Materials                                  |  |

| BSDL  | Boundary-Scan Description Language                 |  |

| BSP   | Board Support Package                              |  |

| CAN   | Controller Area Network (bus)                      |  |

| CCM   | Clock Controller Module                            |  |

| DC    | Direct Current                                     |  |

| DCU   | Display Control Unit                               |  |

| DDR   | Double Data Rate (DRAM type)                       |  |

| DDR2  | DDR type 2                                         |  |

| DDR3  | DDR type 3                                         |  |

| DRAM  | Dynamic Random-Access Memory                       |  |

| EMC   | Electro-Magnetic Compatibility                     |  |

| EMI   | Electro-Magnetic Interference                      |  |

| ENET  | Ethernet                                           |  |

| ESD   | Electro-Static Discharge                           |  |

| ESR   | Equivalent Series Resistance                       |  |

| FIRC  | Fast Internal RC Oscillator                        |  |

| FSL   | Freescale                                          |  |

| GND   | Ground                                             |  |

| GPIO  | General-Purpose Input / Output                     |  |

| HDMI  | High-Definition Multimedia Interface               |  |

Table 1. Definitions and acronyms (continued)

| Term             | Definition                                      |  |

|------------------|-------------------------------------------------|--|

| IC               | Integrated Circuit                              |  |

| I <sup>2</sup> C | Inter-Integrated Circuit (interface)            |  |

| IBIS             | Input / Output Buffer Information Specification |  |

| I/O              | Input / Output                                  |  |

| IOMUX            | Input / Output MUltipleXing (chip level)        |  |

| ISBN             | International Standard Book Number              |  |

| JTAG             | Joint Test Action Group                         |  |

| LDO              | Low Drop-Out (voltage regulator)                |  |

| LIN              | Local Interconnect Network                      |  |

| LPCG             | Low-Power Clock Gating                          |  |

| LPDDR2           | Low-Power DDR2                                  |  |

| LQFP             | Low-Profile Quad Flat Package                   |  |

| LVDS             | Low-Voltage Differential Signaling              |  |

| MAC              | Media Access Control                            |  |

| MAPBGA           | Molded Array Process Ball Grid Array (package)  |  |

| MII              | Media Independent Interface                     |  |

| MLB              | MediaLB (Media Local Bus)                       |  |

| ODT              | On-Die Termination                              |  |

| PC               | Personal Computer                               |  |

| PCB              | Printed-Circuit Board                           |  |

| PLL              | Phase-Locked Loop                               |  |

| ppm              | Parts per Million                               |  |

| RAM              | Random-Access Memory                            |  |

| RF               | Radio Frequency                                 |  |

| RISC             | Reduced Instruction Set Computer                |  |

| RMII             | Reduced MII                                     |  |

| ROM              | Read-Only Memory                                |  |

| RX               | Receive                                         |  |

| SIRC             | Slow Internal RC Oscillator                     |  |

| SMT              | Surface-Mount Technology                        |  |

| SPI              | Serial Peripheral Interface                     |  |

| TX               | Transmit                                        |  |

| TVS              | Transient Voltage Suppressor                    |  |

Table 1. Definitions and acronyms (continued)

| Term    | Definition                                    |  |

|---------|-----------------------------------------------|--|

| UART    | Universal Asynchronous Receiver / Transmitter |  |

| USB     | Universal Serial Bus                          |  |

| USB OTG | USB On-The-Go                                 |  |

| USB 2.0 | USB version 2.0                               |  |

# 2 Design Checklist

# 2.1 Design checklist overview

This chapter provides a design checklist for the following Vybrid series families of processors:

- VF3xx

- VF5xx

- VF6xx

- VF3xxR

- VF5xxR

The design checklist tables (see Section 2.2, "Design checklist tables") contain recommendations for optimal design. Where appropriate, the checklist tables also provide an explanation of the recommendation so that users have a better understanding of why certain techniques are recommended. All supplemental information referenced by the checklist appear in sections following the design checklist tables.

# 2.2 Design checklist tables

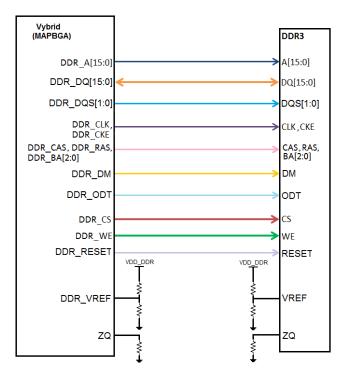

Table 2. DDR recommendations

| Checkbox | Recommendation                                                                                | Explanation / supplemental recommendation                                                                                                                                                                                             |

|----------|-----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | Connect ZQ pad to an external 240 $\Omega$ 1% resistor, whose other side is connected to GND. | This is a reference used during calibration of the DRAM output buffer driver.                                                                                                                                                         |

|          | Connect VREF to a source equal to 50% of the DDR power voltage value.                         | A precision external resistor divider may be used (see Section 2.6, "DDR reference circuit" for value selection). Using resistors with recommended tolerances ensures the ± 2% VREF tolerance per the LPDDR2 and DDR3 specifications. |

|          | Shunt the lower resistor with a closely-mounted small-size minimum 0.1 to 0.22 µF capacitor.  | Using a tracking voltage regulator is optional; it is recommended for memory configurations of more than four devices, which is not the case.                                                                                         |

Table 2. DDR recommendations (continued)

| Checkbox | Recommendation                                                                                      | Explanation / supplemental recommendation                                                                                                                |

|----------|-----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | Connect $\overline{\text{RESET}}$ to a 10 to 100 k $\Omega$ pull-up resistor to the DDR power rail. | Only applicable if DDR self-refresh mode is used when Vybrid is in the LPStop modes, in which its I/Os are in the                                        |

|          | Connect CKE to a 10 to 100 $k\Omega$ pull-down resistor to GND.                                     | high-impedance state. Any Vybrid's terminations (such as 50 $\Omega$ ) should not be present; simulation should be performed to ensure signal integrity. |

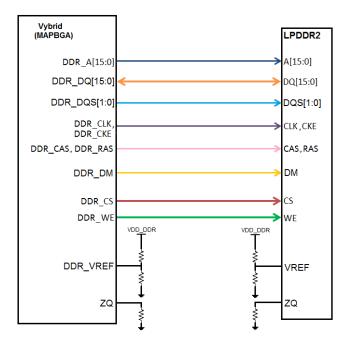

|          | When LPDDR2 is used, make sure it is connected to correct Vybrid I/Os.                              | The DRAM Controller's I/O names are for the DDR3 default and not necessarily match the LPDDR2 functionality.                                             |

#### **NOTE**

If none of the SDRAMC pins are connected on the board, the SDRAMC supply can be left floating.

Table 3. Boot-mode (BOOTMOD and RCON) recommendations

| Checkbox | Recommendation                                                                                                                                                                               | Explanation / supplemental recommendation                                                                                                                                                                                                                                                 |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | If peripherals are connected to the Vybrid I/Os also used for the boot-mode function, use peripherals with three-state outputs, otherwise connect them through three-state buffers.          | It should be ensured that the peripherals' (or their three-state buffers') outputs are in the high-impedance state during the boot-mode selection interval, for example, by utilizing the Vybrid RESET signal.                                                                            |

|          | RCON31 must be tied low during reset. When this pin is left floating, it may be registered as logic 1. In this case the BOOT ROM will enter an endless loop and not boot from any interface. | Entering the endless loop allows for testing watchdog behavior during development. This pin will have no effect when booting from fuses.                                                                                                                                                  |

|          | For the Vybrid I/Os used for both boot-mode function and high-speed peripherals, isolate the boot-mode circuits by inserting either series resistors or three-state buffers.                 | Depending on design specifics, the Vybrid I/Os bearing DCU signals might be a good example.  To keep the trace stubs short and prevent signal integrity issues, place the isolation components as close to the Vybrid I/Os as possible.  See schematic examples in Figure 2 and Figure 3. |

|          | Depending on the design specifics, feel free to mark either part of the boot-mode related circuits or all of them as "optional."                                                             | Depending on the development stages, these circuits become quite often fully or partially unnecessary, on the production stage, where the Vybrid processor boot details may be defined by its pre-programmed fuses.                                                                       |

#### **NOTE**

When not using HAB, RCON16 must be tied low during RESET. If this bit is registered as '1', the device will always boot from the boot device, even when exiting LPSTOP modes.

# Table 4. I<sup>2</sup>C recommendations

| Checkbox | Recommendation                                                                                                                                                                                                            | Explanation / supplemental recommendation                                                                                                                                                                                                                                                                                                  |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | Verify the target I <sup>2</sup> C interface clock rates.                                                                                                                                                                 | The bus can only operate as fast as the slowest peripheral on the bus. If faster operation is required, move the slow devices to another I <sup>2</sup> C port.                                                                                                                                                                            |

|          | Verify that the target I <sup>2</sup> C address range is supported and does not conflict with other peripherals. If there is an unavoidable address conflict, move the offending device to another I <sup>2</sup> C port. | The Vybrid processors support up to:  • three I <sup>2</sup> C ports for the VF3xx and VF3xxR families  • four I <sup>2</sup> C ports for the VF5xx, VF6xx, and VF5xxR families  If moving a conflicting device to another I <sup>2</sup> C port is undesirable, check if re-mapping of its address is possible.  See example in Table 13. |

|          | Do not place more than one set of pull-up resistors on the I <sup>2</sup> C lines.                                                                                                                                        | Placing one pair of pull-up resistors only to prevent excessive output loading is a good design practice.                                                                                                                                                                                                                                  |

#### **Table 5. JTAG recommendations**

| Checkbox | Recommendation                                                                                                                                                                                                       | Explanation / supplemental recommendation                                                                                                                                                                                                                                                                                                                                                                   |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | Do not use external pull-up or pull-down resistors on TDO.                                                                                                                                                           | TDO is configured in a way that the floating condition is actively eliminated if an external pull resistor is not present. An external pull resistor on TDO is detrimental.                                                                                                                                                                                                                                 |

|          |                                                                                                                                                                                                                      | See Table 15 for a summary of the JTAG interface.                                                                                                                                                                                                                                                                                                                                                           |

|          | Keep I <sup>2</sup> C traces aways from signals with fast edges, eventually use BLM chokes to filter out glitches on the clock I/O.                                                                                  | The I <sup>2</sup> C CLK input does not have a glitch filter. Due to the nature of I2C, clock edges are relatively slow and traces can be traversing the PCB, which makes them sensitive to EMC noise; that means glitches may be imposed upon a slow edge and this glitch can be seen as an additional clock. When that happens, the receiver and transmitter get out of sync and the transfer will stall. |

|          | If external pull resistors are used with JTAG signals, except for TDO, ensure that the on-chip pull-up / pull-down configuration is matched. For example, no external pull-down on an input with an on-chip pull-up. | External resistors may be used with all JTAG signals, except for TDO, but are not required.  See Table 15 for a summary of the JTAG interface.                                                                                                                                                                                                                                                              |

|          | Use a 10 $k\Omega$ pull-up resistor on the active-low JTAG connector reset pin (TRST).                                                                                                                               | A debugger uses this bi-directional open-drain pin to either reset the processor or to detect if it is in the reset state.                                                                                                                                                                                                                                                                                  |

|          | Tie the VTREF JTAG connector pin to 3.3 V.                                                                                                                                                                           | "Voltage Reference" is used by the debugger to create its logic-level reference (VTREF/2) for the input comparators and auto-adjust the output voltage levels.                                                                                                                                                                                                                                              |

|          | When using the JTAG system reset (SRST) signal is required, make it control the Vybrid system reset (RESET) pin.                                                                                                     | Since Vybrid has no separate JTAG system reset pin, its RESET pin should be used. In this case, the JTAG SRST signal should be connected either directly to it or combined with the external power-on reset circuitry.                                                                                                                                                                                      |

Table 6. Power and decouple recommendations

| Checkbox | Recommendation                                                                                                                                                                          | Explanation / supplemental recommendation                                                                                                                                                                                                                                                                                                |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | Comply with the power-up sequence guidelines as described in the data sheet to guarantee reliable operation of the device.                                                              | Any deviation from these sequences may result in the following situations:  • excessive current during power-up phase  • prevention of the device from booting  • irreversible damage (worst-case scenario)                                                                                                                              |

|          | Do not power any external loads from the built-in LDOs.                                                                                                                                 | These LDOs are for the internal loads only. For example, DECAP_V11_LDO_OUT is the on-chip LDO output used, among other blocks, to power the on-chip crystal oscillators; using it for external loads is not recommended because of its limited output capability and clock quality degradation due to noise generated by external loads. |

|          | Handle unused power inputs in one of the following ways:  Connect to power sources with relevant voltage values; to save power, disable the relevant blocks and / or gate their clocks. | Due to the internal structure of the pin multiplexer, proper care should be taken if a pin is shared by several Vybrid blocks; for example, if it can act as either a GPIO or an ADC input, it still has to be powered to keep the GPIO functionality, even if the ADC functionality is not required.                                    |

|          | Keep floating.                                                                                                                                                                          | For details on handling unused analog pins, including the power inputs, see Table 17 (based on the processor data sheet information).                                                                                                                                                                                                    |

|          | Keep the unused built-in LDOs' pins floating.                                                                                                                                           | If a built-in LDO is not powered, it needs no decoupling capacitors on its input and output.                                                                                                                                                                                                                                             |

|          | Provide each capacitor with a path to its power pin / via with impedance as low as possible. Use a via size appropriate for the expected current draw.                                  | Placing a capacitor no farther than 50 mils from its power pin / via is recommended as well as using as much copper as possible, for example, solid copper or a wide trace.                                                                                                                                                              |

|          | Only one 10 µF bulk capacitor should be connected to each of these on-chip LDO regulator outputs:  • DECAP_V25_LDO_OUT  • DECAP_V11_LDO_OUT  • USB_DCAP (if USB interface is used)      | If the nominal capacitance value is larger than recommended, power-up ramp time is excessive and proper operation is not guaranteed. Select a low-ESR capacitor type.                                                                                                                                                                    |

|          | In addition to a bulk capacitor, provide each power rail with small-value capacitors, for example, 0.1 $\mu\text{F}$ or 0.22 $\mu\text{F}.$                                             | With proper layout quality, there is no need for one capacitor per pin / via; one per each pair of adjacent pins / vias is sufficient.                                                                                                                                                                                                   |

|          | Meet the maximum voltage-ripple requirements on the power inputs.                                                                                                                       | Common peak-to-peak requirement is less than 5% of the average supply voltage value.                                                                                                                                                                                                                                                     |

|          | Select and connect the backup battery properly.                                                                                                                                         | The target battery is a 3 V coin cell. If a rechargeable type is used, the appropriate series resistor value must be used (see the data sheet for details).                                                                                                                                                                              |

Table 7. Oscillator and clock recommendations

| Checkbox | Recommendation                                                                                                                                                                                                                                                                                                                                              | Explanation / supplemental recommendation                                                                                                                                                                                                                                                                                                                             |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | Precision 32.768 kHz on-chip crystal oscillator:  Connect a crystal between XTAL32 and EXTAL32.  Select a crystal with the ESR value specified in the data sheet.  Follow the manufacturer's load-capacitance recommendation.  Use short traces between the crystal and Vybrid, with a GND plane under the crystal, load capacitors, and associated traces. | The capacitors implemented on either side of the crystal are about twice the crystal load capacitance. To hit the target oscillation frequency, board capacitors need to be reduced to compensate for the board and oscillator I/Os parasitic capacitance; typically 12-18 pF is employed.                                                                            |

|          |                                                                                                                                                                                                                                                                                                                                                             | The integrated oscillator has an on-chip self-biasing scheme but has high impedance (is relatively weak) to minimize power consumption. Care must be taken to limit parasitic leakage from XTAL32 to either power or GND (> 100 M $\Omega$ ) as this negatively affects the oscillator bias (~0.5 V for XTAL32 and EXTAL32) and causes the start-up margin reduction. |

|          |                                                                                                                                                                                                                                                                                                                                                             | If there is no oscillator signal at any time, the chip will automatically use the SIRC/4 clock as a 32 KHz source, provided the SIRC is not disabled by software.                                                                                                                                                                                                     |

|          | External kHz source:  • Drive XTAL32 directly (DC-coupled) within the swing s                                                                                                                                                                                                                                                                               | To prevent damage / malfunction, the input signal should not be driven if the DECAP_V11_LDO_OUT supply is off.                                                                                                                                                                                                                                                        |

|          | and frequency range specified in the data sheet, with EXTAL32 being floating or driven with a complimentary signal.                                                                                                                                                                                                                                         | If there is no external signal at any time, the chip will automatically use the SIRC/4 clock as a 32 KHz source, provided the SIRC is not disabled by software.                                                                                                                                                                                                       |

|          | Loose-tolerance 128 kHz on-chip ring oscillator (SIRC):  • Use it only for applications not requiring precise clock.                                                                                                                                                                                                                                        | The system uses 32 kHz, that is, 128 kHz divided by four by default, the frequency tolerance being specified in the data sheet.                                                                                                                                                                                                                                       |

|          |                                                                                                                                                                                                                                                                                                                                                             | The ring oscillator starts faster than the external-crystal oscillator and is used until the latter reaches stable oscillation.                                                                                                                                                                                                                                       |

|          |                                                                                                                                                                                                                                                                                                                                                             | It also starts automatically if no clock is detected at XTAL32 at any time, including the case when there is no crystal and XTAL32 is tied to GND (EXTAL32 floating).                                                                                                                                                                                                 |

Table 7. Oscillator and clock recommendations (continued)

| Checkbox | Recommendation                                                                                                                                                                                                                | Explanation / supplemental recommendation                                                                                                                                                                                                             |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          |                                                                                                                                                                                                                               | The Freescale BSP software expects this frequency to be 24 MHz.                                                                                                                                                                                       |

|          | Precision 24 MHz on-chip crystal oscillator:  Connect a fundamental-mode crystal between XTAL and EXTAL.  Select a crystal with:  ESR and maximum drive level specified in the data sheet                                     | This clock is used as a reference for USB, so there are strict frequency tolerance and jitter requirements. See Table 16 for guidelines and the "Crystal oscillator" chapter of the reference manual and the USB interface specification for details. |

|          | <ul> <li>load capacitance of 20 pF or lower</li> <li>Follow the manufacturer's load-capacitance recommendation.</li> <li>Bias the XTAL ball with a 2.2 MΩ resistor to GND placed as close to the ball as possible.</li> </ul> | The crystal drive level depends on the ESR value; the lower it is, the lower the maximum drive-level rating may be. For details, see Section 2.3, "24 MHz crystal drive level calculation."                                                           |

|          |                                                                                                                                                                                                                               | The XTAL bias must be adjusted externally to ensure reasonable start-up time. Without the resistor, start-up time may be 200 ms or more.                                                                                                              |

|          |                                                                                                                                                                                                                               | The Freescale BSP software expects this frequency to be 24 MHz.                                                                                                                                                                                       |

|          | External MHz source:  • Drive XTAL directly (DC-coupled) within the swing and frequency range specified in the data sheet, EXTAL being floating.                                                                              | This clock is used as a reference for USB, so there are strict frequency tolerance and jitter requirements. See Table 16 for guidelines, the "Crystal Oscillator" chapter of the reference manual, and the USB interface specification for details.   |

|          |                                                                                                                                                                                                                               | To prevent damage / malfunction, the input signal should not be driven if the DECAP_V11_LDO_OUT supply is off.                                                                                                                                        |

|          |                                                                                                                                                                                                                               | Low-voltage clock sources are quite uncommon; connection example of a 3.3 V powered clock is shown in Figure 1.                                                                                                                                       |

Table 7. Oscillator and clock recommendations (continued)

| Checkbox | Recommendation                                                                                                                                                                                                                                                                                                                                                                                                                  | Explanation / supplemental recommendation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | Loose-tolerance 24 MHz on-chip ring oscillator (FIRC):  • Use it only for applications not requiring precise clock.                                                                                                                                                                                                                                                                                                             | For frequency tolerance, refer to the data sheet.  The ring oscillator starts faster than the external-crystal oscillator and is used until the latter reaches stable oscillation. Then, depending on the ANADIG setting, the clocking scheme either switches to the external-crystal source (default) or keeps using FIRC (see the "Clock Generation and Distribution" block diagram from the processor reference manual for details). Thus, if the external-crystal 24 MHz source is selected but not physically provided, the processor operation fails.  Selecting loose-tolerance FIRC is not recommended if Vybrid PLLs are used.                                                                                               |

|          | Use high-speed LVDS0P / LVDS0N for clock input / output in the range from zero to the Vybrid A5 core frequency.  Alternatively, a single-ended signal can be used to drive the LVDS0P input. In this case, LVDS0N should be tied to a constant voltage level equal to 50% of its power domain value.  Provide termination for high-frequency signals taking the internal I/O impedance into account.  Leave floating if unused. | This differential pair is only used for clock, not data.  The electrical parameters are compatible with the TIA / EIA-644 standard.  Although designed to operate up to the Vybrid A5 core frequency, the block has only been tested up to 400 MHz at the date of publication. Signals above a few tens of MHz may be impractical due to board attenuation. Board simulation is strongly encouraged.  The LVDS I/Os belong to the DECAP_V25_LDO_OUT power group.  It may be configured:  as input to feed external reference clocks to the on-chip PLLs and / or modules  as output (without drive-strength or slew control) to be used as a reference or functional clock for peripherals  disabled after initialization (if unused) |

#### **Table 8. Reset recommendations**

| Checkbox | Recommendation                                                                                                                                    | Explanation / supplemental recommendation                                                                                                    |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

|          | For system reset, assert the Vybrid RESET pin low at power-up and keep it asserted until initialization process of the memory IC used for booting | If an external system reset signal is used, RESET acts as a cold-reset, active-low input, which resets all Vybrid modules and logic.         |

|          | is completed (for details, see Section 8.6.1, "Verifying boot-source readiness").                                                                 | RESET is recommended to be used in addition to the internally-generated power-on reset signal                                                |

|          | nush-button to RESET                                                                                                                              | (logical and both internal and external signals are considered active-low). See Section 8.5, "Avoiding power-on reset pitfalls" for details. |

|          | If using a reset IC is required, use one with an open-drain / collector type and a pull-up resistor to Vybrid's VDD33 power rail.                 | RESET in some occasions acts as an active-low output (see details in Figure 33).                                                             |

|          | If applicable, use the RESET pin for the JTAG interface operation.                                                                                | See Table 5 for details.                                                                                                                     |

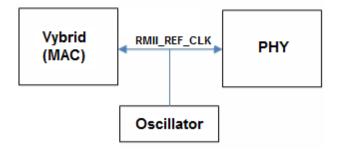

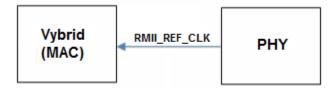

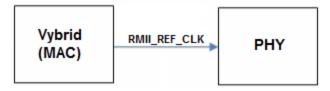

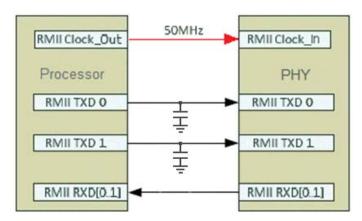

### Table 9. MAC (Ethernet) recommendations

| Checkbox | Recommendation                                                                                                          | Explanation / supplemental recommendation                                                                                     |

|----------|-------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

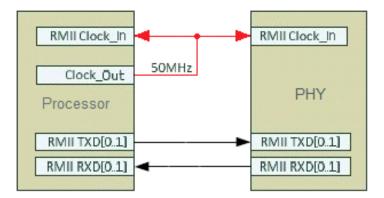

|          | If Vybrid generates and delivers the RMII reference clock, apply the e8052 Erratum workaround.                          | Without the workaround, the TX direction does not operate. See Section 12.3.0.2, "Internal RMII reference clock" for details. |

|          | For proper IEEE-1588 operation, provide sufficient wait time in the software code as described in the Reference Manual. | Without sufficient wait time, the time-stamp read operation returns incorrect data.                                           |

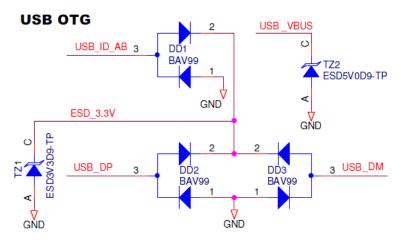

#### **Table 10. USB recommendations**

| Checkbox | Recommendation                                                                                                                                                                                | Explanation / supplemental recommendation                                                                                                                                                                                                                                                                                                                                            |  |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|          | If monitoring of the port's ID pin is required, for example, for "true USB OTG device" operation, use an additional processor's GPIO for that.                                                | The ID function is not built into Vybrid's USB PHYs' hardware, so it should be covered by its software.                                                                                                                                                                                                                                                                              |  |

|          | Turn VBUS on only when the port is operating as host.                                                                                                                                         | <ul> <li>It is recommended to use a VBUS power switch, which is explicitly turned on by software and is by default turned off during the processor power-on and boot.</li> <li>For host-only operation, VBUS on the connector may be connected to a 5 V supply directly, provided its current is limited to 5 A and it recovers automatically after the overload is over.</li> </ul> |  |

|          | Connect the VBUS pin of the connector to the Vybrid USBn_VBUS and USBn_VBUS_DETECT pins.                                                                                                      | Monitoring the VBUS level on the USB connector is a part of OTG signaling.                                                                                                                                                                                                                                                                                                           |  |

|          | To comply with the USB host specification, connect VBUS directly to a 5 V supply. Connect the VBUS supply on the connector to the Vybrid USBn_VBUS pin and, optionally, USBn_VBUS_DETECT pin. | In typical USB host cases, VBUS stays on permanently.                                                                                                                                                                                                                                                                                                                                |  |

Table 10. USB recommendations

| Checkbox | Recommendation                                                                               | Explanation / supplemental recommendation                                                                                                |

|----------|----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

|          | In case of the USB peripheral use, USB VBUS power from the connector may or may not be used. | As per the USB peripheral specification, two power options exist:  • bus-powered (power from USB)  • self-powered (its own power supply) |

|          | For USB versions 2.0 and later, use a high-frequency board material.                         | Such low-attenuation materials are rated for frequencies in GHz range (examples provided in Section 3.2, "Stackup recommendations").     |

**Table 11. Miscellaneous recommendations**

| Checkbox | Recommendation                                                                                  | Explanation / supplemental recommendation                                                                                         |

|----------|-------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

|          | Tie the Ext_POR pin to GND.                                                                     | This pin is for factory use only. Despite its name, do not use this pin for the "power-on reset" purposes, but use RESET instead. |

|          | Tie the TEST pin to GND.                                                                        | These pins are for factory use only.                                                                                              |

|          | Tie the FA_VDD pin to VDD.                                                                      | These pins are for factory use only.                                                                                              |

|          | For termination of unused analog interfaces, see Table 17.                                      | _                                                                                                                                 |

|          | As per <i>e7955</i> , add external pull-up resistors to 3.3 V on the LPStop modes' wakeup pins. | These pull-up resistors should have values between 10 and 100 k $\Omega$ .                                                        |

|          | Leave DDR_ODT1 pin floating.                                                                    | This pin is unused.                                                                                                               |

# 2.3 24 MHz crystal drive level calculation

As mentioned in Table 7 for the "Precision 24 MHz on-chip crystal oscillator," this chapter discusses the approach guaranteeing that the maximum drive level requirement for a 24 MHz crystal selected for use with Vybrid is met. If the crystal is overdriven, the potential failure effect is not immediately obvious. The crystal may either fail over time or its operating frequency may be affected.

An approached based on several parameters provided by the crystal supplier is offered. Without it, a crystal with a 250  $\mu$ W maximum drive level rating shall be used. At the same time, careful crystal selection allows lowering it down to 100  $\mu$ W.

The crystal described in Table 12 is chosen as an example because it is used in numerous Freescale development platforms.

Table 12. Crystal example<sup>1</sup>

| Manufacturer Part Number                |  | Package      | Maximum Drive |

|-----------------------------------------|--|--------------|---------------|

| Epson Toyocom TSX-3225 24.0000MF 15X-AC |  | 3.2 × 2.5 mm | 200 μW        |

<sup>1</sup> Freescale cannot recommend one supplier over another and does not suggest that this is the only crystal supplier

To minimize crystal drive level, the balance of load capacitance (CL1, CL2), motional resistance (Rs), and package capacitance (C0) must be kept low.

The C0 value of 5 pF is used for example only; the actual value depends on the package type and may be verified with the crystal supplier.

# 2.4 Connection of 3.3 V powered external 24 MHz clock source

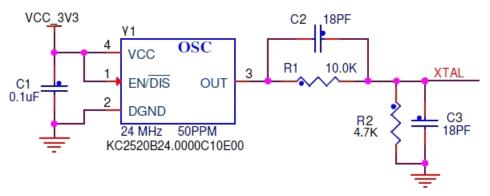

As referred to in Table 7 for the "External MHz source", Figure 1 shows how to connect a 3.3 V powered external 24 MHz clock source to the Vybrid XTAL pin. The board stray and the XTAL pin capacitances shall be taken into account while tuning the voltage-divider capacitors.

Figure 1. Connection of 3.3 V powered external 24 MHz clock source

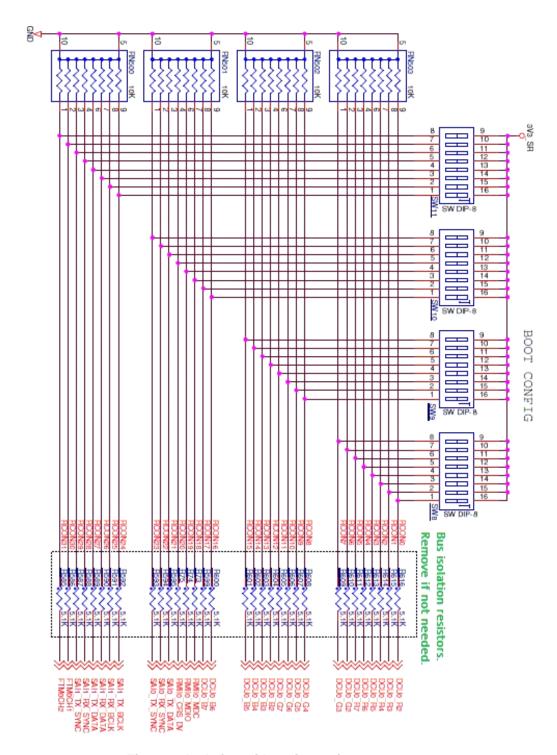

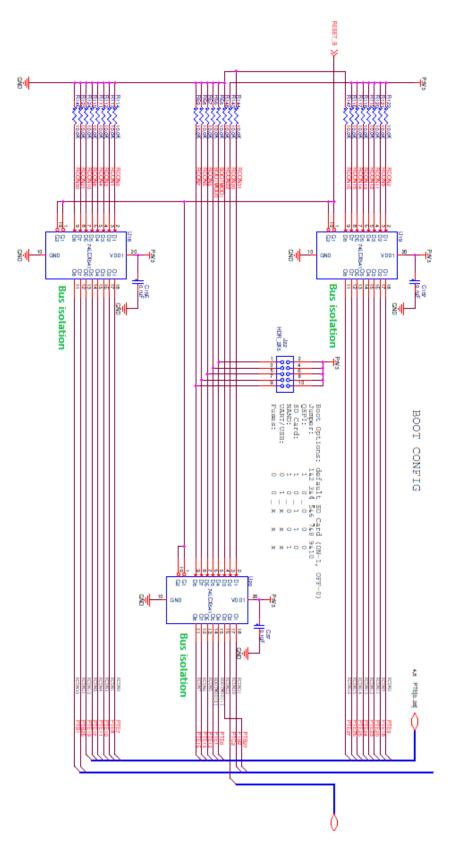

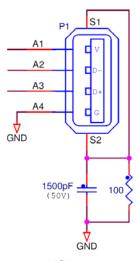

#### 2.5 Boot-mode circuit isolation

Provided below are two boot-mode circuit isolation options:

- based on series resistors (see Figure 2) inexpensive but with somewhat compromised performance due to non-zero conductivity of the series resistors

- based on three-state buffers (see Figure 3) more expensive classic approach with best performance:

- high drive-strength logic levels on the processor's I/Os while sampling the boot-mode configuration

- ideal isolation of the above-mentioned I/Os from the boot-mode circuit during normal operation

Figure 2. Isolation with series resistors

Figure 3. Isolation with three-state buffers

#### **NOTE**

These examples only illustrate the circuit isolation options; what processor's I/Os are involved in the boot-mode circuit is design-specific.

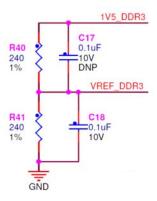

### 2.6 DDR reference circuit

A simple voltage divider based on two equal-value inexpensive 1% resistors is good enough to generate the DDR reference; see the DDR3 0.75 V reference example in Figure 4.

Figure 4. DDR3 0.75 V VREF supply

If a DDR memory device with  $2 \mu A$  VREF input current is used, the maximum recommended value is  $2.42 \text{ k}\Omega$  1%. For the BOM consolidation, a 1% resistor type already used somewhere else in the design might be utilized, for example, the one used for the ZQ pad (see Table 2 and Figure 4).

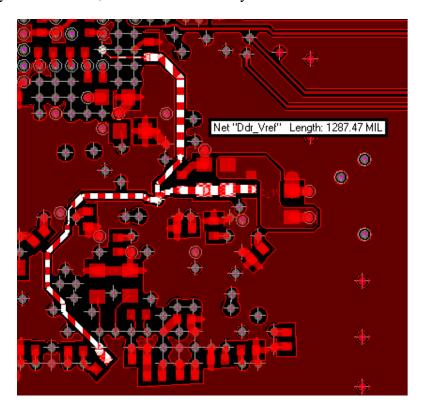

See the layout recommendations for this signal in Section 3.6.4, "VREF recommendations."

# 2.7 I<sup>2</sup>C ports usage

# 2.7.1 I<sup>2</sup>C address and speed

Table 13 shows a spreadsheet approach to avoid I<sup>2</sup>C conflicts as referenced in Table 4.

#### **NOTE**

The example in this section applies to a hypothetical Vybrid-based reference design.

Notice that the cells outlined in black in Table 13 highlight two different issue types:

- a potential bus-speed problem (of the RF Tuner)

- a potential slave-address conflict (between the MLB Card and the Analog-to-Digital Converter)

| Peripheral                     | Bus activity<br>level | Speed<br>(kbit/s) | Slave addresses<br>supported on<br>peripheral (hex) | Selected<br>system address<br>(hex) |

|--------------------------------|-----------------------|-------------------|-----------------------------------------------------|-------------------------------------|

| MLB Card                       | Low                   | 400               | 40                                                  | 40                                  |

| Port Expander                  | Low                   | 400               | 30, 32, 34                                          | 30                                  |

| RF Tuner                       | Med                   | 250               | C0, C2, C4, C6                                      | C0                                  |

| Analog-to-Digital<br>Converter | Med                   | 400               | 40, 42                                              | 42                                  |

| Audio codec                    | Low                   | 400               | 90, 92, 94, 96                                      | 90                                  |

Table 13. I<sup>2</sup>C bus example spreadsheet

### 2.7.1.1 Bus-speed issue resolution

The RF tuner is rated for up to 250 kbit/s, whereas all other peripherals are rated for up to 400 kbit/s. If all of them are placed on the same I<sup>2</sup>C bus, it forces to lower its speed, since it cannot exceed that of the slowest one.

If the I<sup>2</sup>C bus rate exceeded the RF tuner module's maximum bus rate, the I<sup>2</sup>C bus operation might fail or become unpredictable. The slow peripheral may unpredictably take over the bus or malfunction in some other way.

If utilizing the other peripherals' higher speed is preferred, the RF tuner must be isolated on a separate  $I^2C$  port (see Table 14).

#### 2.7.1.2 Slave-address conflict resolution

As mentioned in Table 4, this conflict may be easily avoided by remapping the address of one of the conflicting devices, in this specific case, the Analog-to-Digital Converter's address (see the "Selected system address" column in Table 13 and Table 14).

# 2.7.1.3 I<sup>2</sup>C port usage scenario

Assuming that the system can function properly with a reduced bus rate of 250 kbit/s, Table 14 provides a possible optimized I<sup>2</sup>C port usage.

| , -                              |                             |                               |                    |

|----------------------------------|-----------------------------|-------------------------------|--------------------|

| Vybrid<br>I <sup>2</sup> C Ports | Peripheral                  | Selected system address (hex) | Bus speed (kbit/s) |

| Port 1                           | MLB Card                    | 40                            | 400                |

| Port 1                           | Port Expander               | 30                            | 400                |

| Port 1                           | Analog-to-Digital Converter | 42                            | 400                |

| Port 1                           | Audio codec                 | 90                            | 400                |

| Port 2                           | RF Tuner                    | C0                            | 250                |

Table 14. I<sup>2</sup>C port usage scenario

# 2.7.2 I<sup>2</sup>C interface timing settings

Refer to the "Clock rate and IBFD Settings" chapter of the processor reference manual for details.

# 2.7.3 I<sup>2</sup>C interface operation in presence of noise

Complex boards quite often have high-frequency noise induced into their I<sup>2</sup>C lines:

- Power-hungry digital components may contaminate power and ground planes with significant amount of high-frequency ripple.

- Due to limited space, electromagnetic coupling of the I<sup>2</sup>C lines to the numerous high-speed traces is not unlikely, especially fast simultaneous switching of outputs like data buses can introduce noise.

The nature of the I2C bus with its relatively slow edges makes it susceptible to glitches forming on the clock edges. When these glitches are close to the threshold level of the input buffer, there is a fair chance that the glitch is considered an additional clock cycle. Due to this, the receiver and transmitter get out of sync. Some Freescale development platforms have series ferrite beads on the I<sup>2</sup>C data and clock lines; in this case, a low-pass LC filter on each line is formed by the bead inductance and the parasitic capacitance to ground, which consists of two parts – the board stray capacitance and the processor's I/O pin one.

# 2.8 JTAG signal termination

Table 15 is a JTAG termination chart.

Table 15. JTAG interface summary

| Signal | Vybrid I/O direction | Vybrid on-chip termination | External termination                                               |

|--------|----------------------|----------------------------|--------------------------------------------------------------------|

| тск    | Input                | Pull-down                  | Not required; $10 \text{ k}\Omega$ pull-down resistor may be used. |

| TMS    | Input / Output       | Pull-up                    | Not required; 10 k $\Omega$ pull-up resistor may be used.          |

| TDI    | Input                | Pull-up                    | Not required; 10 k $\Omega$ pull-up resistor may be used.          |

| TDO    | Output               | None                       | Do not use pull-up or pull-down resistors.                         |

## 2.9 24 MHz oscillator tolerance

The following table provides 24 MHz oscillator tolerance guidelines (see Table 16). Since these are guidelines, the designer must verify all tolerances are within the official specifications.

Table 16. 24 MHz crystal tolerance guidelines

| Interface         | Tolerance (± ppm) |

|-------------------|-------------------|

| MAC<br>(Ethernet) | 50                |

| USB2.0            | 500               |

# 2.10 Unused analog interfaces

Table 17 shows the recommended connections for unused analog interfaces (see Table 11).

Some I/O pins are shared by both the digital and analog Vybrid modules (for details, see the "Recommended Connections for Unused Analog Interfaces" section of the Vybrid data sheet). When shared pins are used as digital pins, their associated analog supply must also be powered. This also applies to boundary scan, if shared pins are used in boundary scan tests. If shared pins are not used in BSDL tests, the analog supplies can remain off during BSDL.

Table 17. Recommended connections for unused analog interfaces

| Module    | Pin name                              | Recommendations                                                                                                                                                                                                                                                               |

|-----------|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | VDDA33_ADC, VREFH_ADC                 | Both at the same time tied to 3.3 V or floating.                                                                                                                                                                                                                              |

| ADC / DAC | VREFL_ADC                             | Grounded if VREFH_ADC is tied to 3.3 V. Floating if VREFH_ADC is floating.                                                                                                                                                                                                    |

|           | ADC0SE8, ADC0SE9, ADC1SE8, ADC1SE9    | Grounded or floating.                                                                                                                                                                                                                                                         |

| CCM       | LVDS0P, LVDS0N                        | Floating.                                                                                                                                                                                                                                                                     |

| DAC       | DACO0, DACO1                          | Floating.                                                                                                                                                                                                                                                                     |

| USB       | USB_DCAP, USB0_VBUS,<br>USB1_VBUS     | Never ground directly due to latch-up risk. If only one USBx_VBUS remains unused, connect it to ground through a 10 k $\Omega$ resistor. If both USBx_VBUS remain unused, tie all three pins together and connect this common net to ground through a 10 k $\Omega$ resistor. |

|           | USB0_GND, USB1_GND                    | Grounded.                                                                                                                                                                                                                                                                     |

|           | USB0_VBUS_DETECT,<br>USB1_VBUS_DETECT | Floating.                                                                                                                                                                                                                                                                     |

|           | USB0_DM, USB0_DP,<br>USB1_DM,USB1_DP  | Floating.                                                                                                                                                                                                                                                                     |

|           | VDDA33_AFE                            | Tied to 3.3 V or floating.                                                                                                                                                                                                                                                    |

|           | VDD12_AFE                             | Tied to 1.2 V or floating.                                                                                                                                                                                                                                                    |

| Video ADC | VADC_AFE_BANDGAP                      | Floating.                                                                                                                                                                                                                                                                     |

|           | VADCSE0, VADCSE1, VADCSE2, VADCSE3    | Grounded or floating.                                                                                                                                                                                                                                                         |

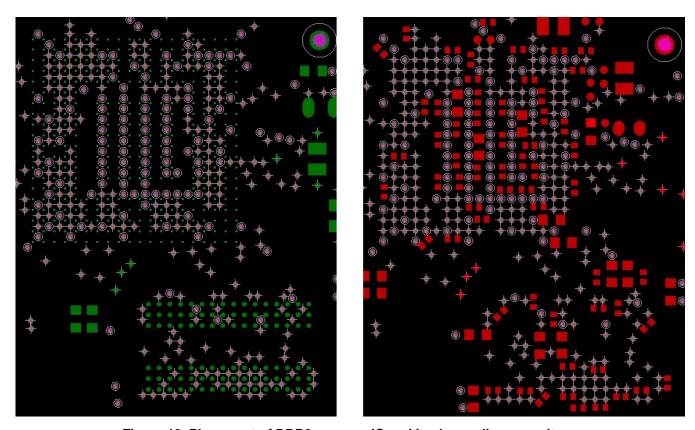

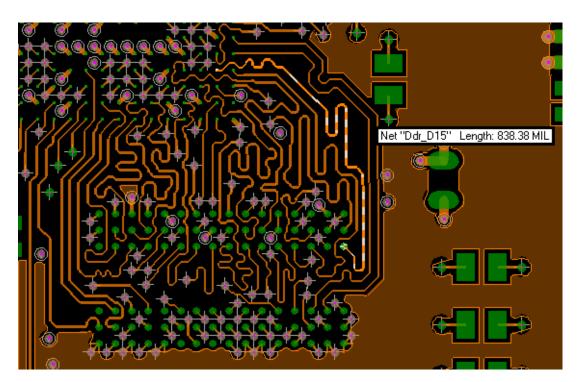

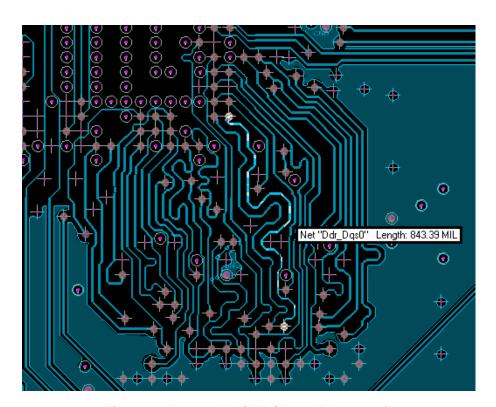

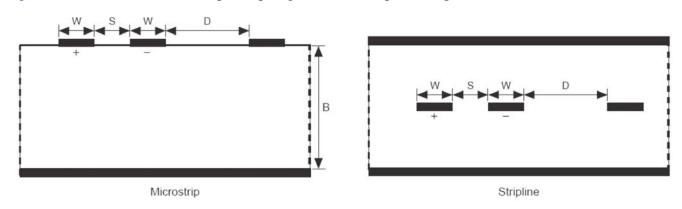

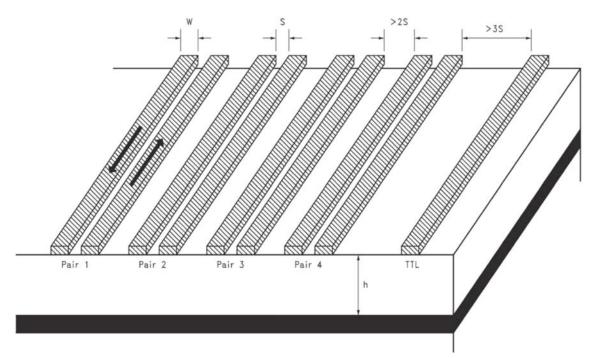

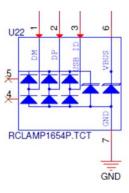

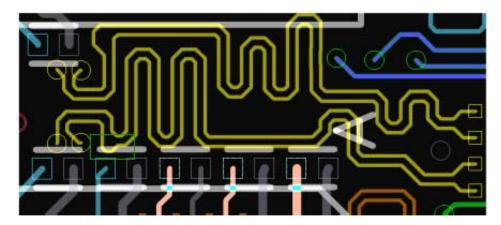

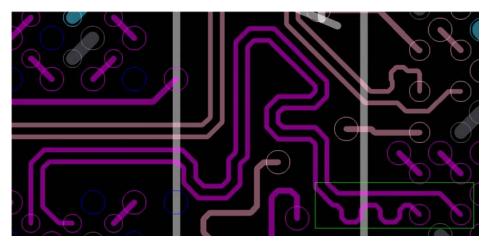

This chapter provides recommendations to assist design engineers with the correct layout of their Vybrid family-based system. The majority of this chapter discusses the implementation of the DDR interface, but it also provides recommendation for power, LVDS, USB, reference resistors and ESD, as well as related electromagnetic emission.

This chapter uses the Vybrid Tower module and the Vybrid Automotive platform to illustrate the key design concepts. See the relevant layout files as an addition to this chapter.

# 3.1 Basic design recommendations

The Vybrid processor comes either in the 364-ball MAPBGA (VF5xx, VF6xx, and VF5xxR) or the 176-lead LQFP (VF3xx and VF3xxR) package.

For detailed information about the packages, see the Vybrid Consumer and Automotive data sheets.

#### 3.1.1 Mechanical data

### 3.1.1.1 MAPBGA package

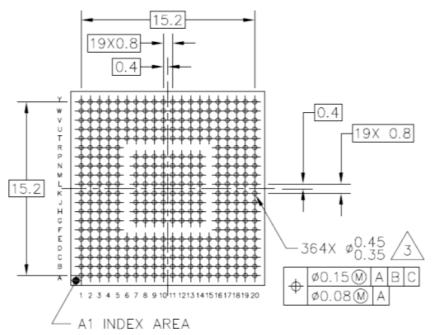

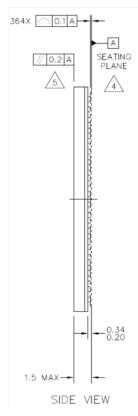

The VF5xx, VF6xx, and VF5xxR processors come in a  $17 \times 17$  mm MAPBGA package with 0.8 mm ball-pitch. The ball-grid array contains 20 rows and 20 columns; 36 empty pins in the rows F and R and columns 6 and 15 form a square-shaped gap around the center cluster, making it a 364-ball BGA package.

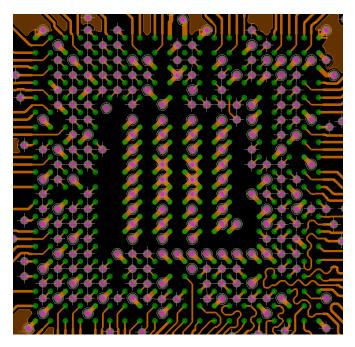

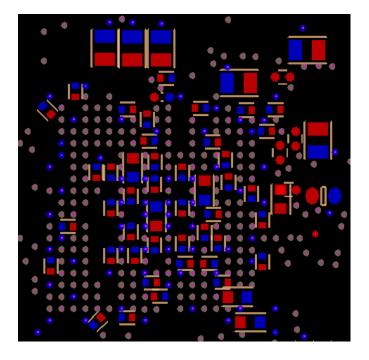

Figure 5 shows the ball-grid array. Figure 6 shows additional package information.

Figure 5. Vybrid MAPBGA ball-grid array

Figure 6. Vybrid 364 MAPBGA package information

It is critical to maintain the recommended footprint of a 13-mil pad with a 17-mil open solder mask for ease of fanout. In this case, the solder paste is the same as the pad with 13 mil, which allows an air gap of 18.49 mils between pads.

When using the Allegro tool, optimal practice is to use the footprint as created by Freescale. When not using the Allegro tool, use the Allegro footprint export feature (supported by numerous tools). If export is not possible, create the footprint as per the package mechanical dimensions outlined in the product data sheet.

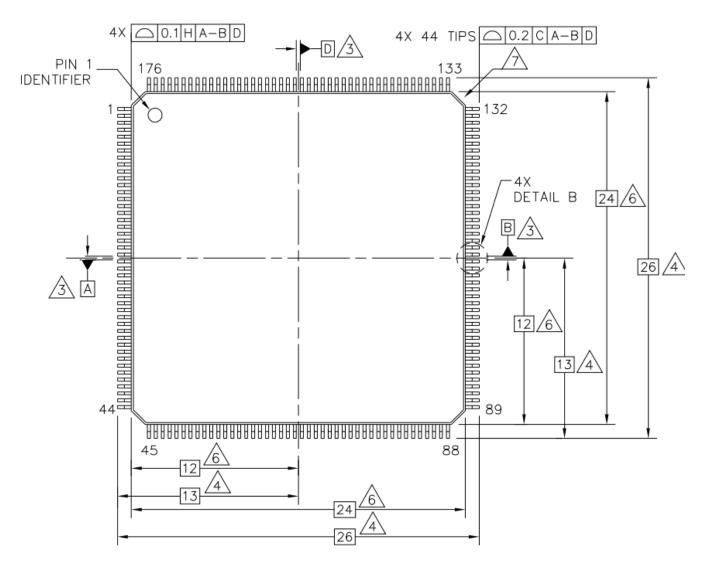

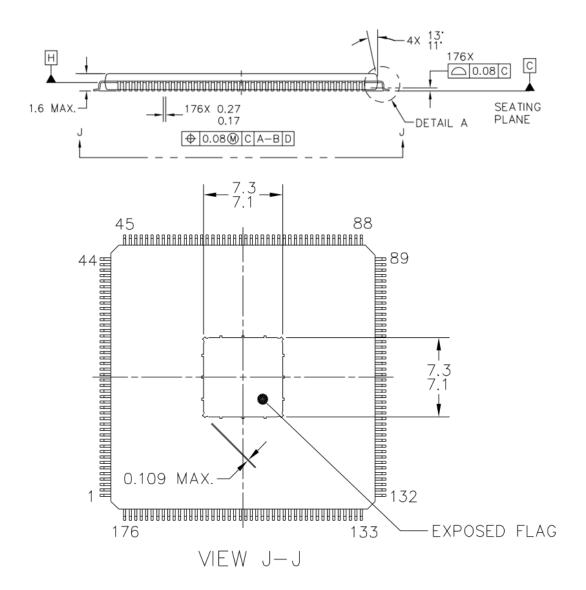

# 3.1.2 LQFP package

The VF3xx and VF3xxR processors come in a plastic  $24 \times 24 \times 1.40$  mm body with 0.5 mm lead-pitch. The "gull-wing" leads extend from each of the four sides, making it a 176-lead LQFP package.

Figure 7 and Figure 8 show the "gull-wing" array and additional package information, respectively.

Figure 7. Vybrid LQFP "gull-wing" lead array

Figure 8. Vybrid LQFP package information

#### NOTE

The bottom exposed pad (flag) is connected to VSS (GND) internally for both electrical and thermal purposes.

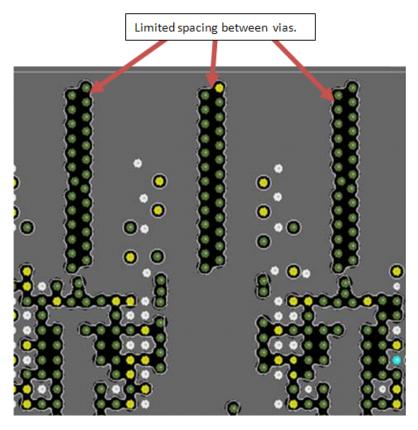

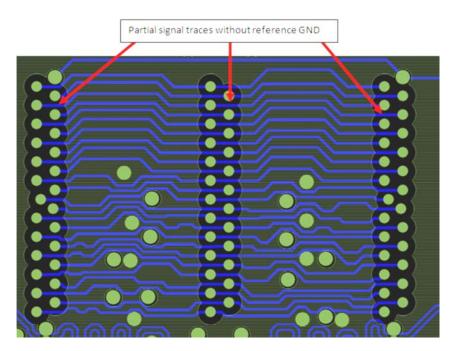

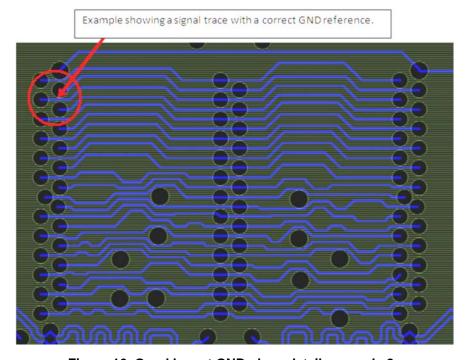

#### **NOTE**