# **REALTIMEEDGEUG**

# Real-time Edge Software User Guide Rev. 3.0 — 17 December 2024

User guide

### **Document information**

| Information | Content                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Keywords    | REALTIMEEDGEUG, Real-time Edge Software, Real-time Networking, Real-time System, Protocols, i.MX boards, QorlQ (Layerscape) boards, i.MX 6ULL EVK, i.MX 8DXL EVK, i.MX 8M Mini LPDDR4 EVK, i.MX 8M Plus LPDDR4 EVK, i.MX 93 EVK, i.MX RT1180 EVK, i.MX 93 9x9 QSB, i.MX 93 14x14 EVK, i.MX 91 9x9 LPDDR4 QSB, i.MX 91 11x11 LPDDR4 EVK, i.MX 95 15x15 LPDDR4 EVK, i.MX 95 19x19 EVK, LX2160ARDB Rev2, NXP hardware platforms |

| Abstract    | This document describes the features and implementation of Real-time Edge Software on NXP hardware platforms. The key technology components include Real-time System, Real-time Networking, Heterogeneous Multicore Framework, Heterogeneous Multi-SoC Framework, and Protocols.                                                                                                                                             |

# 1 Introduction

# 1.1 Real-time Edge software

Real-time Edge software is an evolved version of Open Industrial Linux (OpenIL) for real-time and deterministic systems in different fields. The key technology components include Real-time System, Heterogeneous Multicore Framework, Heterogeneous Multi-SoC Framework, Real-time Networking and Protocols.

- Real-time System includes PREEMPT\_RT Linux, Native RTOS on Cortex-A, Jailhouse, U-Boot based Baremetal framework, RTOS and Baremetal on Cortex-M, and different combinations of these systems.

- Heterogeneous Multicore Framework provides a general software framework to support Heterogeneous AMP. It enables AMP to be interconnected and provides a unified resource management and life-cycle management.

- Heterogeneous Multi-SoC Framework enables the usage of a combination of MPU and MCU. It extends the hardware components for the MCU as well as MPU.

- Real-time Networking includes TSN technology, TSN standards, management, configuration, and applications. This component also supports networking and redundancy features.

- Protocols component includes support for industry standard protocols such as EtherCAT, CoE, FlexCan, OPC-UA, and others.

This document describes the features and implementation of Real-time Edge Software on NXP hardware platforms.

# 1.2 Feature support matrix

<u>Table 1</u> shows the features that are supported in this release.

Table 1. Key features

| Feature            |                       |                                        |                   | i.MX<br>6ULL<br>14x14<br>EVK | i.MX<br>8DXL<br>LPDDR4<br>EVK | i.MX 8M<br>Mini<br>LPDDR4<br>EVK | i.MX 8M<br>Plus<br>LPDDR4<br>EVK | i.MX 93<br>EVK | i.MX<br>93 9x9<br>LPDDR4<br>QSB | i.MX 93<br>14x14<br>LPDDR4x<br>EVK | i.MX 95<br>19x19<br>LPDDR5<br>EVK | i.MX 95<br>15x15<br>LPDDR4<br>EVK | 11x11 | 91 9x9 | i.MX<br>RT1180<br>EVK | LS1028<br>ARDB | LS1043<br>ARDB | LS1046<br>ARDB | LX2160<br>ARDB |

|--------------------|-----------------------|----------------------------------------|-------------------|------------------------------|-------------------------------|----------------------------------|----------------------------------|----------------|---------------------------------|------------------------------------|-----------------------------------|-----------------------------------|-------|--------|-----------------------|----------------|----------------|----------------|----------------|

| Boot mode          | SD                    |                                        |                   | Y                            | Y                             | Y                                | Y                                | Y              | Y                               | Y                                  | Y                                 | Y                                 | Υ     | Y      |                       | Y              | Y              | Y              | Y              |

| Boot mode          | eMMC                  |                                        |                   |                              |                               | Y                                | Y                                | Y              | Y                               | Y                                  | Y                                 | Y                                 | Y     | Y      |                       | Y              |                | Y              |                |

| Real-time          | Preempt-RT            | Linux                                  |                   | Y                            | Y                             | Y                                | Y                                | Y              | Y                               | Y                                  | Y                                 | Y                                 | Y     | Y      |                       | Y              | Y              | Y              | Y              |

| System             |                       | ICC                                    |                   |                              |                               | Y                                | Y                                | Y              | Y                               |                                    |                                   |                                   |       |        |                       | Y              | Y              | Y              | Y              |

|                    |                       | PCle                                   |                   |                              |                               |                                  |                                  |                |                                 |                                    |                                   |                                   |       |        |                       | Y              | Y              | Y              |                |

|                    |                       | Ethernet                               |                   |                              |                               | Y                                | Y                                | Y              |                                 |                                    |                                   |                                   |       |        |                       | Y              | Y              | Y              |                |

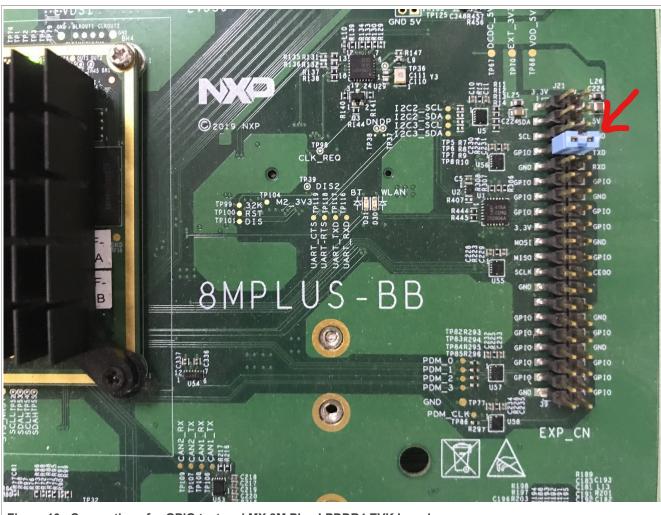

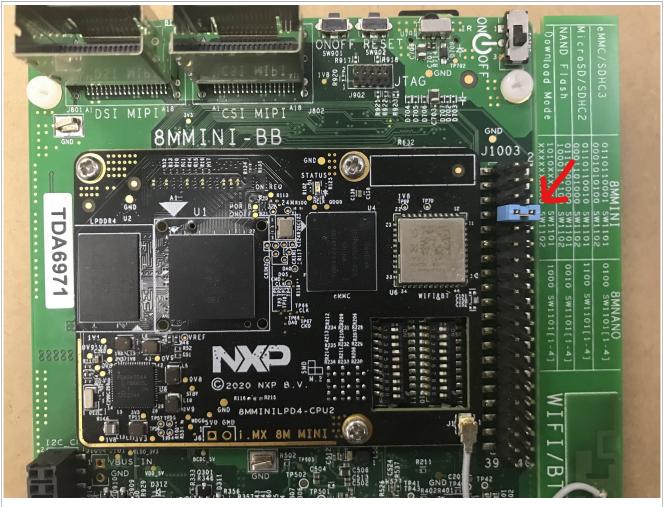

|                    |                       | GPIO                                   |                   |                              |                               | Y                                | Y                                |                |                                 |                                    |                                   |                                   |       |        |                       |                |                | Y              |                |

|                    |                       | IPI                                    |                   |                              |                               | Y                                | Y                                | Y              | Y                               |                                    |                                   |                                   |       |        |                       | Y              | Y              | Y              | Y              |

|                    |                       | UART                                   |                   |                              |                               | Y                                | Y                                | Y              | Y                               |                                    |                                   |                                   |       |        |                       | Y              | Y              | Y              | Y              |

|                    |                       | USB                                    |                   |                              |                               |                                  |                                  |                |                                 |                                    |                                   |                                   |       |        |                       |                | Y              | Y              |                |

|                    |                       | SAI                                    |                   |                              |                               |                                  |                                  |                |                                 |                                    |                                   |                                   |       |        |                       | Y              |                |                |                |

|                    |                       | CAN                                    |                   |                              |                               |                                  |                                  |                |                                 |                                    |                                   |                                   |       |        |                       |                |                |                |                |

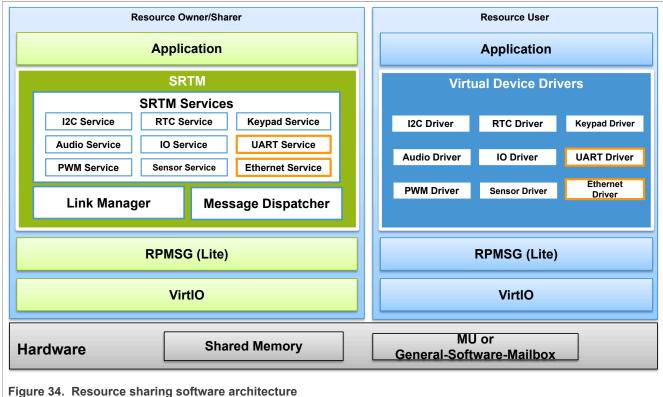

|                    |                       | I2C                                    |                   |                              |                               |                                  |                                  |                |                                 |                                    |                                   |                                   |       |        |                       | Y              | Y              | Υ              |                |

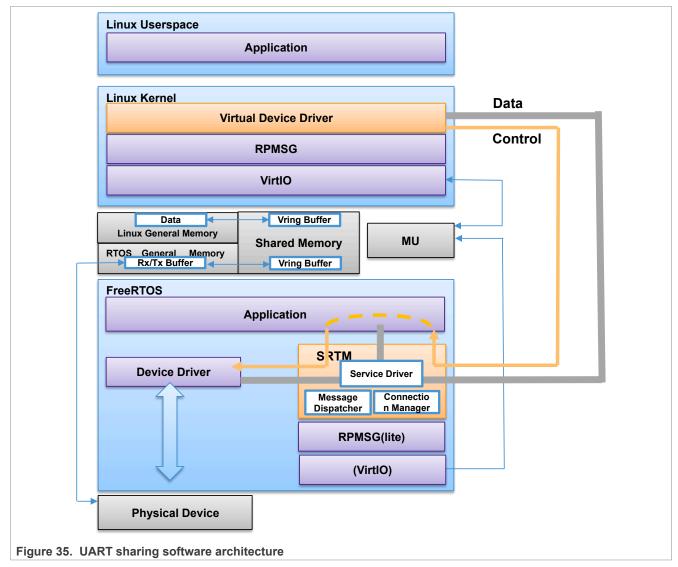

|                    | BareMetal             | QSPI                                   |                   |                              |                               |                                  |                                  |                |                                 |                                    |                                   |                                   |       |        |                       |                |                | Υ              |                |

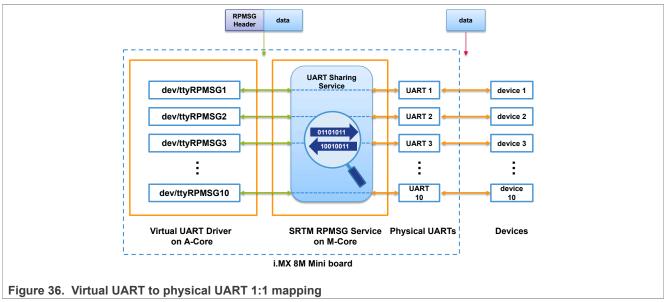

|                    |                       | IFC                                    |                   |                              |                               |                                  |                                  |                |                                 |                                    |                                   |                                   |       |        |                       |                |                | Υ              |                |

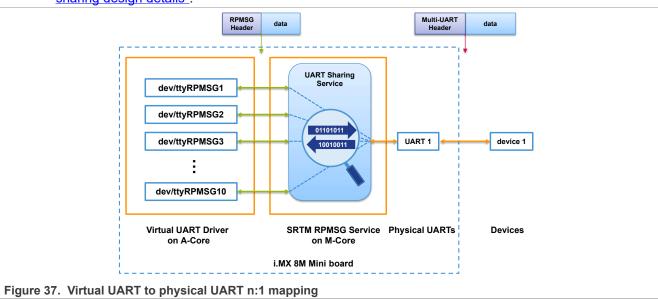

|                    |                       | Flextimer                              |                   |                              |                               |                                  |                                  |                |                                 |                                    |                                   |                                   |       |        |                       |                |                | Υ              |                |

|                    |                       | Linux                                  | ICC               |                              |                               | Y                                | Y                                | Y              | Y                               |                                    |                                   |                                   |       |        |                       | Y              | Y              | Y              | Y              |

|                    |                       | (communi-<br>cation with<br>Baremetal) | IPI               |                              |                               | Y                                | Y                                | Y              | Y                               |                                    |                                   |                                   |       |        |                       | Y              | Y              | Y              | Y              |

|                    |                       | Single HW Inte                         | errupt to         |                              |                               |                                  |                                  |                |                                 |                                    |                                   |                                   |       |        |                       |                |                | Y              |                |

|                    |                       | Newlib Math lib                        | orary             |                              |                               | Y                                | Y                                | Y              | Y                               |                                    |                                   |                                   |       |        |                       | Y              | Y              | Y              | Y              |

|                    |                       | All Cortex-A co                        | ores<br>Baremetal |                              |                               |                                  |                                  |                |                                 |                                    |                                   |                                   |       |        |                       | Y              |                | Y              |                |

|                    | Native                | FreeRTOS                               |                   |                              |                               | Y                                | Y                                | Y              |                                 | Y                                  | Y                                 |                                   |       |        |                       |                |                |                |                |

|                    | RTOS on<br>Cortex-A   | Zephyr                                 |                   |                              |                               | Y                                | Y                                | Y              |                                 | Y                                  | Y                                 |                                   |       |        |                       |                |                |                |                |

|                    | Jailhouse             | 1                                      |                   |                              |                               | Y                                | Y                                |                | Y                               |                                    | Y                                 |                                   |       |        |                       | Y              | Y              | Y              |                |

|                    | Harpoon               | FreeRTOS                               | _                 |                              |                               | Y                                | Y                                | Υ              |                                 |                                    | Y                                 |                                   |       |        |                       |                |                |                |                |

|                    | RTOS                  | Zephyr                                 |                   |                              |                               | Y                                | Y                                | Y              |                                 |                                    | Y                                 |                                   |       |        |                       |                |                |                |                |

| Heterogen-<br>eous | Flexible<br>Real-time | Flexible<br>Realtime                   | Free<br>RTOS      |                              |                               | Y                                | Y                                | Y              |                                 | Y                                  | Y                                 |                                   |       |        |                       |                |                |                |                |

| Multicore          | System                | System                                 | Zephyr            |                              |                               | Y                                | Y                                | Υ              |                                 | Y                                  | Y                                 |                                   |       |        |                       |                |                |                |                |

NXP Semiconductors

REALTIMEEDGEUG

# Real-time Edge Software User Guide

Table 1. Key features...continued

| Feature        |                                          |                                                                      |              | i.MX<br>6ULL<br>14x14<br>EVK | i.MX<br>8DXL<br>LPDDR4<br>EVK | i.MX 8M<br>Mini<br>LPDDR4<br>EVK | i.MX 8M<br>Plus<br>LPDDR4<br>EVK | i.MX 93<br>EVK | i.MX<br>93 9x9<br>LPDDR4<br>QSB | i.MX 93<br>14x14<br>LPDDR4x<br>EVK | i.MX 95<br>19x19<br>LPDDR5<br>EVK | i.MX 95<br>15x15<br>LPDDR4<br>EVK | i.MX 91<br>11x11<br>LPDDR4<br>EVK | i.MX<br>91 9x9<br>LPDDR4<br>QSB | i.MX<br>RT1180<br>EVK | LS1028<br>ARDB | LS1043<br>ARDB | LS1046<br>ARDB | LX2160<br>ARDB |

|----------------|------------------------------------------|----------------------------------------------------------------------|--------------|------------------------------|-------------------------------|----------------------------------|----------------------------------|----------------|---------------------------------|------------------------------------|-----------------------------------|-----------------------------------|-----------------------------------|---------------------------------|-----------------------|----------------|----------------|----------------|----------------|

| Frame-<br>work |                                          | RAM Console                                                          | Free<br>RTOS |                              |                               | Υ                                | Υ                                | Y              |                                 | Y                                  | Y                                 |                                   |                                   |                                 |                       |                |                |                |                |

|                |                                          | TVAW CONSOIC                                                         | Zephyr       |                              |                               | Y                                | Y                                | Υ              |                                 | Y                                  | Y                                 |                                   |                                   |                                 |                       |                |                |                |                |

|                |                                          | Networking<br>stack on A-<br>Core RTOS                               | Free<br>RTOS |                              |                               | Υ                                | Υ                                | Υ              |                                 | Y                                  |                                   |                                   |                                   |                                 |                       |                |                |                |                |

|                |                                          | U-Boot<br>booting Native                                             | Free<br>RTOS |                              |                               | Y                                | Υ                                | Υ              |                                 | Y                                  | Y                                 |                                   |                                   |                                 |                       |                |                |                |                |

|                |                                          | RTOS A-Core<br>Image                                                 | Zephyr       |                              |                               | Y                                | Y                                | Υ              |                                 | Y                                  | Y                                 |                                   |                                   |                                 |                       |                |                |                |                |

|                | Unified<br>Life Cycle<br>Manage-<br>ment | U-Boot<br>booting Native<br>RTOS M-Core<br>Image                     | Free<br>RTOS |                              |                               | Y                                | Y                                | Y              | Y                               | Y                                  |                                   |                                   |                                   |                                 |                       |                |                |                |                |

|                |                                          | Linux booting<br>Native RTOS<br>M-Core Image                         | Free<br>RTOS |                              |                               | Υ                                | Υ                                | Y              | Y                               | Y                                  |                                   |                                   |                                   |                                 |                       |                |                |                |                |

|                |                                          | RPMSG<br>between A-<br>Core<br>Linux and<br>M-Core RTOS              | Free<br>RTOS |                              |                               | Y                                | Υ                                | Y              | Y                               | Y                                  |                                   |                                   |                                   |                                 |                       |                |                |                |                |

|                |                                          | RPMSG<br>between A-<br>Core<br>Linux and<br>A-Core RTOS              | Free<br>RTOS |                              |                               | Y                                | Υ                                |                |                                 |                                    |                                   |                                   |                                   |                                 |                       |                |                |                |                |

|                | RPMSG                                    | RPMSG<br>between 2 A-<br>Core<br>RTOS                                | Free<br>RTOS |                              |                               |                                  | Y                                |                |                                 |                                    |                                   |                                   |                                   |                                 |                       |                |                |                |                |

|                |                                          | RPMSG between A- core Linux and M-core RTOS with enhanced 8MB buffer | Free<br>RTOS |                              |                               | Y                                |                                  |                |                                 |                                    |                                   |                                   |                                   |                                 |                       |                |                |                |                |

|                |                                          | RPMSG<br>Performance<br>Evaluation                                   | Free<br>RTOS |                              |                               |                                  | Υ                                |                |                                 |                                    |                                   |                                   |                                   |                                 |                       |                |                |                |                |

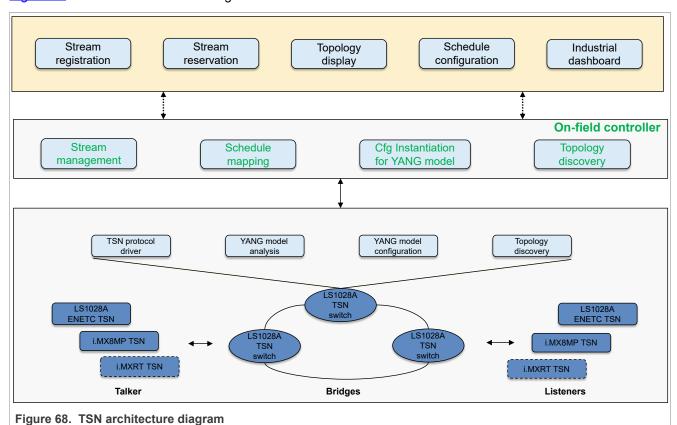

|                |                                          | UART Sharing based on RPMSG                                          | Free<br>RTOS |                              |                               | Y                                |                                  | Y              | Y                               | Y                                  |                                   |                                   |                                   |                                 |                       |                |                |                |                |

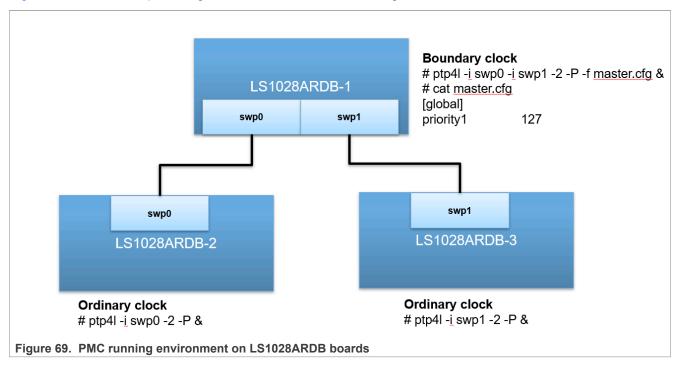

|                | Heterogene<br>-ous                       | Heterogeneous<br>Multicore<br>VirtIO                                 | Free<br>RTOS |                              |                               | Y                                | Y                                |                |                                 |                                    |                                   |                                   |                                   |                                 |                       |                |                |                |                |

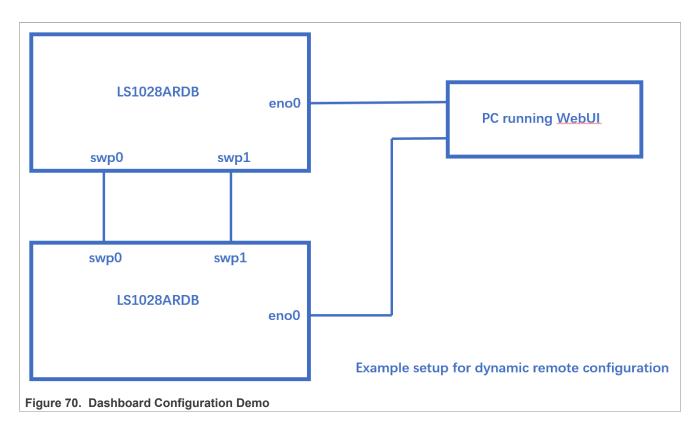

NXP Semiconductors

REALTIMEEDGEUG

# Real-time Edge Software User Guide

Table 1. Key features...continued

| Feature           |                            | arescomm                                                |                | i.MX<br>6ULL<br>14x14<br>EVK | i.MX<br>8DXL<br>LPDDR4<br>EVK | i.MX 8M<br>Mini<br>LPDDR4<br>EVK | i.MX 8M<br>Plus<br>LPDDR4<br>EVK | i.MX 93<br>EVK | i.MX<br>93 9x9<br>LPDDR4<br>QSB | i.MX 93<br>14x14<br>LPDDR4x<br>EVK | i.MX 95<br>19x19<br>LPDDR5<br>EVK | i.MX 95<br>15x15<br>LPDDR4<br>EVK | i.MX 91<br>11x11<br>LPDDR4<br>EVK | i.MX<br>91 9x9<br>LPDDR4<br>QSB | i.MX<br>RT1180<br>EVK | LS1028<br>ARDB | LS1043<br>ARDB | LS1046<br>ARDB | LX2160<br>ARDB |

|-------------------|----------------------------|---------------------------------------------------------|----------------|------------------------------|-------------------------------|----------------------------------|----------------------------------|----------------|---------------------------------|------------------------------------|-----------------------------------|-----------------------------------|-----------------------------------|---------------------------------|-----------------------|----------------|----------------|----------------|----------------|

|                   |                            | Performance<br>Evaluation                               |                |                              |                               |                                  |                                  |                |                                 |                                    |                                   |                                   |                                   |                                 |                       |                |                |                |                |

|                   | Multicore<br>VirtIO        | Heterogeneous<br>Multicore<br>VirtlO Network<br>Sharing | RTOS           |                              |                               | Y                                | Y                                | Y              |                                 | Y                                  |                                   |                                   |                                   |                                 |                       |                |                |                |                |

|                   | Industrial<br>Applications | SOEM<br>running on A-<br>core or M-core                 | Free<br>RTOS   |                              |                               | Υ                                | Y                                | Υ              |                                 |                                    |                                   |                                   |                                   |                                 |                       |                |                |                |                |

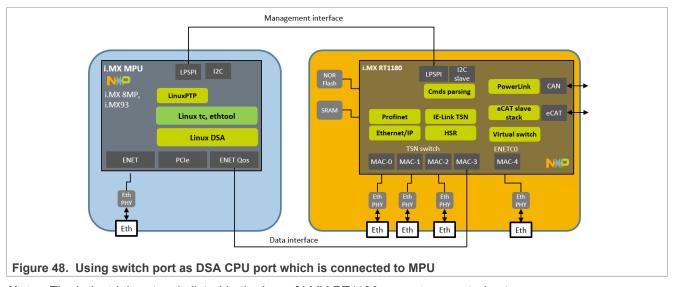

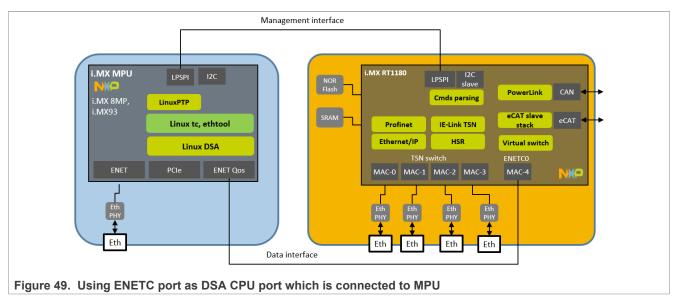

| Heterogen-        |                            | DSA single por                                          | t mode         |                              |                               |                                  | Υ                                | Υ              |                                 |                                    |                                   |                                   |                                   |                                 | Υ                     |                |                |                |                |

| eous<br>Multi-SoC |                            | DSA bridge mo                                           | de             |                              |                               |                                  | Υ                                | Y              |                                 |                                    |                                   |                                   |                                   |                                 | Υ                     |                |                |                |                |

| Framework         |                            | MTU configurat                                          | tion           |                              |                               |                                  | Y                                | Υ              |                                 |                                    |                                   |                                   |                                   |                                 | Υ                     |                |                |                |                |

|                   |                            | VLAN configura                                          | ation          |                              |                               |                                  | Υ                                | Υ              |                                 |                                    |                                   |                                   |                                   |                                 | Υ                     |                |                |                |                |

|                   | NETC TSN                   | FDB configurat                                          | ion            |                              |                               |                                  | Y                                | Υ              |                                 |                                    |                                   |                                   |                                   |                                 | Υ                     |                |                |                |                |

|                   | Switch                     | Port statistics                                         |                |                              |                               |                                  | Y                                | Υ              |                                 |                                    |                                   |                                   |                                   |                                 | Υ                     |                |                |                |                |

|                   |                            | PTP stack                                               |                |                              |                               |                                  | Y                                | Υ              |                                 |                                    |                                   |                                   |                                   |                                 | Υ                     |                |                |                |                |

|                   |                            | 802.1CB                                                 |                |                              |                               |                                  | Y                                | Υ              |                                 |                                    |                                   |                                   |                                   |                                 | Υ                     |                |                |                |                |

|                   |                            | Qci                                                     |                |                              |                               |                                  | Y                                | Υ              |                                 |                                    |                                   |                                   |                                   |                                 | Υ                     |                |                |                |                |

|                   |                            | Qbv                                                     |                |                              |                               |                                  | Y                                | Υ              |                                 |                                    |                                   |                                   |                                   |                                 | Υ                     |                |                |                |                |

|                   | Virtual Switch             | 1                                                       |                |                              |                               |                                  | Y                                | Υ              |                                 |                                    |                                   |                                   |                                   |                                 | Υ                     |                |                |                |                |

|                   |                            | Qbv                                                     |                |                              | Y                             |                                  | Y                                | Υ              | Y                               | Y                                  |                                   |                                   |                                   |                                 |                       | Y              |                |                |                |

|                   |                            | Qbu                                                     |                |                              | Y                             |                                  | Y                                | Υ              | Y                               | Y                                  |                                   |                                   |                                   |                                 |                       | Y              |                |                |                |

|                   |                            | Qci                                                     |                |                              |                               |                                  |                                  |                |                                 |                                    |                                   |                                   |                                   |                                 |                       | Y              |                |                |                |

|                   | TSN                        | Qav                                                     |                |                              | Y                             | Υ                                | Y                                | Υ              | Y                               | Υ                                  |                                   |                                   |                                   |                                 |                       | Υ              |                |                |                |

|                   | Standards                  | 802.1AS                                                 |                |                              | Y                             | Υ                                | Y                                | Υ              | Y                               | Y                                  |                                   |                                   |                                   |                                 |                       | Y              | Y              | Y              | Y              |

|                   |                            | 802.1CB                                                 |                |                              |                               |                                  |                                  |                |                                 |                                    |                                   |                                   |                                   |                                 |                       | Y              |                |                |                |

|                   |                            | VCAP chain mo                                           | ode            |                              |                               |                                  |                                  |                |                                 |                                    |                                   |                                   |                                   |                                 |                       | Y              |                |                |                |

| Real-time         |                            | 802.1 Q-in-Q                                            |                |                              |                               |                                  |                                  |                |                                 |                                    |                                   |                                   |                                   |                                 |                       | Y              |                |                |                |

| Networking        |                            | Linux tc comma                                          | and            |                              | Y                             |                                  | Y                                | Y              | Y                               | Y                                  |                                   |                                   |                                   |                                 |                       | Y              |                |                |                |

|                   |                            | TSN tool                                                |                |                              |                               |                                  |                                  |                |                                 |                                    |                                   |                                   |                                   |                                 |                       | Y              |                |                |                |

|                   | TSN                        |                                                         | Qbv            |                              | Y                             |                                  | Y                                | Y              | Y                               | Y                                  |                                   |                                   |                                   |                                 |                       | Y              |                |                |                |

|                   |                            |                                                         | Qbu            |                              | Y                             |                                  | Y                                | Y              | Y                               | Y                                  |                                   |                                   |                                   |                                 |                       | Y              |                |                |                |

|                   | Configurati<br>ons         | NETCONF/                                                | Qci            |                              |                               |                                  |                                  |                |                                 |                                    |                                   |                                   |                                   |                                 |                       | Y              |                |                |                |

|                   |                            | YANG                                                    | IP             |                              | Y                             |                                  | Y                                | Y              | Y                               | Y                                  |                                   |                                   |                                   |                                 |                       | Y              |                |                |                |

|                   |                            |                                                         | MAC            |                              | Y                             |                                  | Y                                | Y              | Y                               | Y                                  |                                   |                                   |                                   |                                 |                       | Y              |                |                |                |

|                   |                            |                                                         | VLAN<br>config |                              | Y                             |                                  | Y                                | Y              | Y                               | Y                                  |                                   |                                   |                                   |                                 |                       | Y              |                |                |                |

NXP Semiconductors

REALTIMEEDGEUG

# Real-time Edge Software User Guide

Table 1. Key features...continued

| Feature            |                  |                                  |         | i.MX<br>6ULL<br>14x14<br>EVK | i.MX<br>8DXL<br>LPDDR4<br>EVK | i.MX 8M<br>Mini<br>LPDDR4<br>EVK | i.MX 8M<br>Plus<br>LPDDR4<br>EVK | i.MX 93<br>EVK   | i.MX<br>93 9x9<br>LPDDR4<br>QSB | i.MX 93<br>14x14<br>LPDDR4x<br>EVK | i.MX 95<br>19x19<br>LPDDR5<br>EVK | i.MX 95<br>15x15<br>LPDDR4<br>EVK | 11x11 | i.MX<br>91 9x9<br>LPDDR4<br>QSB | i.MX<br>RT1180<br>EVK | LS1028<br>ARDB | LS1043<br>ARDB | LS1046<br>ARDB | LX2160<br>ARDB |

|--------------------|------------------|----------------------------------|---------|------------------------------|-------------------------------|----------------------------------|----------------------------------|------------------|---------------------------------|------------------------------------|-----------------------------------|-----------------------------------|-------|---------------------------------|-----------------------|----------------|----------------|----------------|----------------|

|                    |                  |                                  | Qbv     |                              | Y                             |                                  | Y                                | Υ                | Y                               |                                    |                                   |                                   |       |                                 |                       | Y              |                |                |                |

|                    |                  | Web-based configuration          | Qbu     |                              | Y                             |                                  | Y                                | Υ                | Y                               |                                    |                                   |                                   |       |                                 |                       | Y              |                |                |                |

|                    |                  | Comigaration                     | Qci     |                              |                               |                                  |                                  |                  |                                 |                                    |                                   |                                   |       |                                 |                       | Y              |                |                |                |

|                    |                  | Dynamic topolo discovery         | gy      |                              | Y                             |                                  | Y                                | Υ                | Y                               |                                    |                                   |                                   |       |                                 |                       | Y              |                |                |                |

|                    |                  |                                  | Qci     |                              |                               |                                  |                                  |                  |                                 |                                    |                                   |                                   |       |                                 |                       | Υ              |                |                |                |

|                    |                  | Dynamic TSN configuration        | CQF     |                              |                               |                                  |                                  |                  |                                 |                                    |                                   |                                   |       |                                 |                       | Y              |                |                |                |

|                    |                  | J                                | Qbv     |                              | Y                             |                                  | Y                                | Υ                | Y                               |                                    |                                   |                                   |       |                                 |                       | Y              |                |                |                |

|                    |                  | AVTP Talker/Lis                  | stener  | Y                            | Y                             | Υ                                | Y                                | Υ                |                                 | Y                                  |                                   |                                   |       |                                 |                       |                |                |                |                |

|                    |                  | AVDECC                           |         | Y                            | Y                             | Υ                                | Y                                | Υ                |                                 | Y                                  |                                   |                                   |       |                                 |                       |                |                |                |                |

|                    | AVB<br>standards | MAAP                             |         | Y                            | Y                             | Υ                                | Y                                | Υ                |                                 | Y                                  |                                   |                                   |       |                                 |                       |                |                |                |                |

|                    | Starradi do      | Milan                            |         | Y                            | Y                             | Υ                                | Y                                | Υ                |                                 | Y                                  |                                   |                                   |       |                                 |                       |                |                |                |                |

|                    |                  | Media clock red                  | covery  | Y                            | Y                             | Y <sup>[1]</sup>                 | Y                                | Y <sup>[1]</sup> |                                 | Y <sup>[1]</sup>                   |                                   |                                   |       |                                 |                       |                |                |                |                |

|                    | AVB Bridge o     | on SJA1105Q-EVI                  | 3       |                              | Y                             |                                  |                                  |                  |                                 | Y                                  |                                   |                                   |       |                                 |                       |                |                |                |                |

|                    | AVB Hybrid o     | on SJA1105Q-EVI                  | 3       |                              |                               |                                  |                                  |                  |                                 | Y                                  |                                   |                                   |       |                                 |                       |                |                |                |                |

|                    | IEEE 1588/8      | 02.1AS                           |         |                              | Y                             | Υ                                | Y                                | Υ                | Y                               | Y                                  |                                   |                                   |       |                                 |                       | Y              | Υ              | Y              | Y              |

| dustrial<br>otocol |                  | IGH EtherCAT stack               | master  | Y                            | Y                             | Υ                                | Y                                | Υ                |                                 |                                    |                                   |                                   |       |                                 |                       | Y              | Y              | Y              | Y              |

|                    | EtherCAT         | IGH native Ethe<br>device driver | ernet   |                              | Y                             | Υ                                | Y                                | Υ                |                                 |                                    |                                   |                                   |       |                                 |                       | Y              | Y              | Y              |                |

|                    | master           | SOEM                             |         |                              |                               | Y                                | Y                                | Υ                |                                 |                                    |                                   |                                   |       |                                 |                       |                |                |                |                |

|                    |                  | CodeSYS Ethe master stack        | rCAT    | Y                            |                               | Y                                | Y                                | Υ                |                                 |                                    |                                   |                                   |       |                                 |                       |                |                |                |                |

|                    | FlexCAN          |                                  |         |                              |                               |                                  |                                  |                  |                                 |                                    |                                   |                                   |       |                                 |                       | Y              |                |                |                |

|                    | CANopen          |                                  |         |                              |                               |                                  |                                  |                  |                                 |                                    |                                   |                                   |       |                                 |                       |                |                |                |                |

|                    |                  | open62541                        |         | Y                            | Y                             | Υ                                | Y                                | Υ                | Y                               | Y                                  |                                   |                                   |       |                                 |                       | Y              | Y              | Y              | Y              |

|                    | OPC UA           | OPC UA PubSi<br>TSN              | ub over |                              | Y                             |                                  | Y                                | Υ                | Y                               | Y                                  |                                   |                                   |       |                                 |                       | Y              |                |                |                |

|                    | BEE (Mikroe      | Click board)                     |         |                              |                               |                                  |                                  |                  |                                 |                                    |                                   |                                   |       |                                 |                       | Y              |                |                |                |

|                    | BLE (Mikroe      | Click board)                     |         |                              |                               |                                  |                                  |                  |                                 |                                    |                                   |                                   |       |                                 |                       | Y              |                |                |                |

|                    | NFC (Mikroe      | Click board)                     |         |                              |                               |                                  |                                  |                  |                                 |                                    |                                   |                                   |       |                                 |                       | Y              |                |                |                |

|                    | Mardhana         | Modbus-RTU                       |         | Y                            | Y                             | Υ                                | Y                                | Υ                | Y                               | Y                                  |                                   |                                   |       |                                 |                       |                |                |                |                |

|                    | Modbus           | Modbus-TCP                       |         | Y                            | Υ                             | Υ                                | Υ                                | Υ                | Y                               | Y                                  |                                   |                                   |       |                                 |                       | Y              | Υ              | Υ              | Y              |

<sup>[1]</sup> Media clock recovery is implemented through a software-based sampling

# 1.3 Supported NXP platforms

The Table 2 lists the NXP hardware SoCs and boards that support the Real-time Edge software.

Table 2. Supported NXP platforms

| Platform                  | Architecture | Boot     |

|---------------------------|--------------|----------|

| i.MX 6ULL EVK             | Arm v7       | SD       |

| i.MX 8DXL LPDDR4 EVK      | Arm v8       | SD, eMMC |

| i.MX 8M Mini LPDDR4 EVK   | Arm v8       | SD, eMMC |

| i.MX 8M Plus LPDDR4 EVK   | Arm v8       | SD, eMMC |

| i.MX 93 EVK               | Arm v8       | SD, eMMC |

| i.MX 93 9x9 QSB           | Arm v8       | SD, eMMC |

| i.MX 93 14x14 EVK         | Arm v8       | SD, eMMC |

| i.MX 95 19x19 LPDDR5 EVK  | Arm v8       | SD, eMMC |

| i.MX 95 15x15 LPDDR4X EVK | Arm v8       | SD, eMMC |

| i.MX 91 11x11 LPDDR4X EVK | Arm v8       | SD, eMMC |

| i.MX 91 9x9 LPDDR4 QSB    | Arm v8       | SD, eMMC |

| LS1028ARDB                | Arm v8       | SD, eMMC |

| LS1043ARDB                | Arm v8       | SD       |

| LS1046ARDB                | Arm v8       | SD, eMMC |

| LX2160ARDB Rev 2          | Arm v8       | SD       |

# 1.3.1 Switch settings

The <u>Table 3</u> lists and describes the switch configuration for the platforms supported by Real-time Edge software.

Table 3. Switch setting for various NXP platforms

| Platform                  | Boot source             | Switch setting                                                                                               |

|---------------------------|-------------------------|--------------------------------------------------------------------------------------------------------------|

| i.MX 6ULL EVK             | Internal Boot / MicroSD | SW602 = 0b'10 (internal boot) and SW601[1:4] = 0b'0010 (MicroSD)                                             |

| i.MX 8DXL LPDDR4 EVK      | SD, eMMC                | • SD: SW1[1:4] = 0b'1100<br>• eMMC: SW1[1:4] = 0b'0100                                                       |

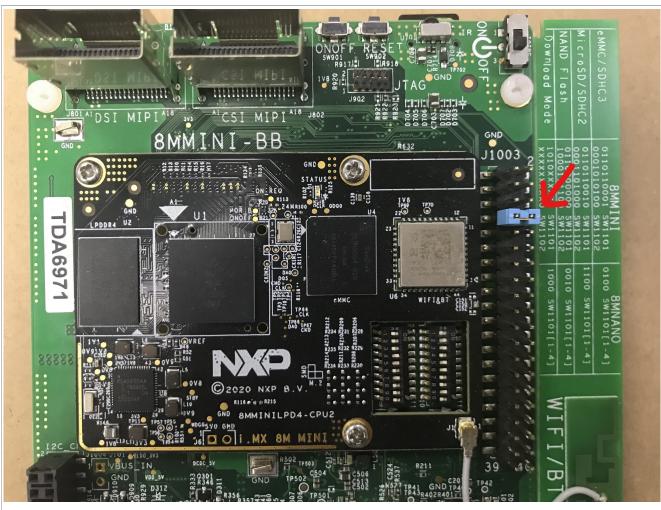

| i.MX 8M Mini LPDDR4 EVK   | MicroSD / uSDHC2        | • SW1101[1:10] = 0b' 0110110010<br>• SW1102[1:10] = 0b' 0001101000                                           |

| i.MX 8M Plus LPDDR4 EVK   | MicroSD / SDHC2         | SW4[1:4] = 0b'0011                                                                                           |

| i.MX 93 EVK               | MicroSD / uSDHC2        | SW1301[1:4] = 0b'0100                                                                                        |

| i.MX 93 9x9 QSB           | MicroSD / uSDHC2        | SW601[1:4] = 0b'0011                                                                                         |

| i.MX 93 14x14 EVK         | SD, eMMC                | • SD: SW5[1:4] = 0b'0100<br>• eMMC: SW5[1:4] = 0b'0000                                                       |

| i.MX 95 19x19 LPDDR5 EVK  | SD, eMMC                | • SD: SW7[1:4] = 0b'1011<br>• eMMC: SW7[1:4] = 0b'1010                                                       |

| i.MX 95 15x15 LPDDR4X EVK | SD, eMMC                | • SD: SW7[1:4] = 0b1011<br>• eMMC: SW7[1:4] = 0b1010                                                         |

| i.MX 91 11x11 LPDDR4X EVK | SD, eMMC                | • SD: SW1301[1:4] = 0b0100<br>• eMMC: SW1301[1:4] = 0b0000                                                   |

| i.MX 91 9x9 LPDDR4 QSB    | SD, eMMC                | • SD: SW3[1:4] = 0b0011<br>• eMMC: SW3[1:4] = 0b0010                                                         |

| LS1028ARDB                | SD, eMMC                | • SD: SW2[1:8] = 0b'10001000<br>• eMMC: SW2[1:8] = 0b'10011000                                               |

| LS1043ARDB                | SD                      | SW4[1:8] + SW5[1] = 0b'00100000_0                                                                            |

|                           |                         | <ul><li>UART1 output select</li><li>SW3[3] = 0b'0: RJ45</li><li>SW3[3] = 0b'1: CMSIS-DAP (MiniUSB)</li></ul> |

| LS1046ARDB                | SD, eMMC                | SW5[1:8] + SW4[1] = 0b'00100000_0                                                                            |

|                           |                         | UART1 output select  • SW4[4] = 0b'0: RJ45  • SW4[4] = 0b'1: CMSIS-DAP (MicroUSB)                            |

| LX2160ARDB Rev2           | SD                      | SW1[1:8] = 0b'10001000                                                                                       |

|                           | 1                       |                                                                                                              |

# 1.3.2 Flashing pre-built images

Pre-built images for platforms supported by Real-time Edge software can be downloaded from NXP website from the below URL:

https://www.nxp.com/design/software/development-software/real-time-edge-software:REALTIME-EDGE-SOFTWARE.

Download the image required and extract it by using the commands below: (The code below shows the commands used for LS1028ARDB-PA as an example)

```

$ unzip Real-time Edge v3.0 LS1028ARDB.zip

$ cd Real-time_Edge v3.0 LS1028ARDB/real-time-edge

$ 1s

atf

fsl-ls1028a-rdb-jailhouse-without-enetc.dtb

Image-1s1028ardb.bin

dр

fsl-ls1028a-rdb-dpdk.dtb

nxp-image-real-time-edge-ls1028ardb.manifest

fsl-ls1028a-rdb-dsa-swp5-eno3.dtb nxp-image-real-time-edge-

ls1028ardb.rootfs.tar.bz2

fsl-ls1028a-rdb.dtb

nxp-image-real-time-edge-ls1028ardb.wic.zst

fsl-ls1028a-rdb-jailhouse.dtb

rcw

$ zstd -d nxp-image-real-time-edge-ls1028ardb.wic.zst

```

Insert SD card, device node "sdx" (for example: sdc) is created in directory "/dev/" with USB reader, flash file "nxp-image-real-time-edge-ls1028ardb.wic" to SD card:

```

$ sudo dd if=./nxp-image-real-time-edge-ls1028ardb.wic of=/dev/sdc bs=1M

conv=fsync

```

After flashing this image to SD card, insert this SD card into LS1028ARDB board, connect UART1 port and open it. Then, powering on the LS1028ARDB board displays the message as shown in Figure 1.

```

NOTICE: Fixed DDR on board

4 GB DDR4, 32-bit, CL=11, ECC on BL2: v2.4(release):lf-5.15.5-1.0.0-0-g05f788b9b-dirty

NOTICE:

NOTICE:

NOTICE: BL2: Built : 05:49:10, Mar 2 2022

BL2: Booting BL31

NOTICE:

BL31: v2.4(release):lf-5.15.5-1.0.0-0-g05f788b9b-dirty

NOTICE:

NOTICE: BL31: Built : 05:49:10, Mar 2 2022

NOTICE: Welcome to ls1028ardb BL31 Phase

U-Boot 2021.04+fsl+g5e08bb0ff9 (Apr 21 2022 - 09:19:32 +0000)

SoC: LS1028AE Rev1.0 (0x870b0010)

Clock Configuration:

CPU0(A72):1500 MHz CPU1(A72):1500 MHz

400 MHz DDR:

1600 MT/s

Bus:

Reset Configuration Word (RCW):

00000000: 3c004010 00000030 00000000 00000000

00000010: 00000000 018f0000 0030c000 00000000

00000020: 020031a0 00002580 00000000 00003296

00000030: 00000000 00000008 00000000 00000000

00000060: 00000000 00000000 200e705a 00000000

00000070: bb580000 00000000

Model: NXP Layerscape 1028a RDB Board

Board: LS1028AE Rev1.0-RDB, Version: A, boot from SD

Figure 1. LS1028ARDB boot log

```

# 1.4 Real-time Edge Software Yocto Project

For using Yocto build environment, refer to the *Real-time Edge Yocto Project User Guide*. This document describes the steps to build Real-time Edge images using a Yocto Project build environment for both i.MX and QorlQ (Layerscape) boards.

### 1.5 Related documentation

All documentation related to Real Time Edge software is available on the link: <u>REALTIME EDGE Documentation</u>. The following documents are available:

- Real-time Edge Release Notes (RN00161) (provides release information)

- Real-time Edge User Guide (REALTIMEEDGEUG) (provides detailed user guide)

- Real-time Edge Yocto Project User Guide (RTEDGEYOCTOUG)(provides information for using Yocto build environment)

- GenAVB/TSN Stack Evaluation User Guide ( GENAVBTSNUG)(provides information on how to set up Audio Video Bridging evaluation experiments of the GenAVB/TSN Stack on NXP platforms)

- Harpoon User's Guide (HRPNUG) (provides information to build Harpoon Yocto images)

- i.MX6ULL EVK GenAVB/TSN Rework Application Note (AN13678)

- For details about the graphics feature available in i.MX 8M Plus and i.MX 8M Mini boards, refer to the <u>i.MX</u>

Graphics User's Guide.

To boot up and set up the boards mentioned in this document, refer to the instructions available in the following user guides:

- i.MX 6ULL EVK Quick Start Guide

- i.MX 8M Mini LPDDR4 EVK Quick Start Guide

- i.MX 8M Plus LPDDR4 EVK Quick Start Guide

- i.MX 8XLite EVK Quick Start Guide

- LS1028ARDB Quick Start Guide

- LS1043ARDB Getting Started Guide

- LS1046ARDB Getting Started Guide

- LX2160A/LX2160A-Rev2 RDB Quick Start Guide

- i.MX 93 EVK Quick Start Guide

- i.MX 91 EVK Quick Start Guide

- i.MX RT1180 Getting Started Guide

**Note:** In case of any access issue related to these documents, contact your local NXP Field Application Engineer (FAE) or support executive.

# 2 Real-time system

#### 2.1 Overview

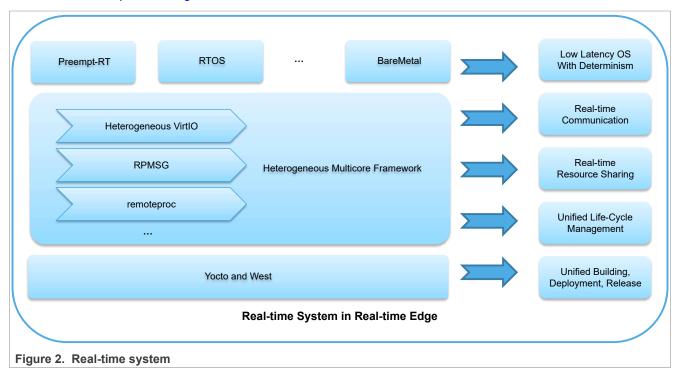

Real-time System addresses several real-time requirements on multicore platforms. These include aspects such as schedule latency, inter-core communication, hardware resource sharing, unified life-cycle management, and unified building and deployment mechanism.

To support different schedule latency requirements, Real-time System provides:

- Preempt-RT Linux

- · native RTOS on Cortex-A core and Cortex-M core

- · RTOS on Cortex-A core with Jailhouse and

- · BareMetal framework.

It also provides a flexible combination of different cores running Preempt-RT Linux and RTOS/BareMetal to meet different real-time requirements for different use cases.

The heterogeneous multicore framework feature of Real-Rime Edge software provides different intercore communication mechanisms and hardware-resource sharing mechanisms between different CPU cores and different OSes to cover high-performance communication and real-time requirements. Unified CPU Core life cycle management provides a unified mechanism to bootstrap the Cortex-A core and Cortex-M core on the heterogeneous MPU system. Refer to chapter <a href="Section 3" "Heterogeneous Multicore Framework" for details.">Section 3 "Heterogeneous Multicore Framework"</a> for details.

The unified software building and deploying mechanism provides easy building and deployment for the software components running on the Cortex-A core and Cortex-M core. These components and features of this mechanism are depicted in <a href="Figure 2">Figure 2</a>.

Real-time Edge software provides a general software architecture to run Real-time Systems on MPU platforms with the following features:

· Different frameworks and flexible combinations for different schedule latency requirements

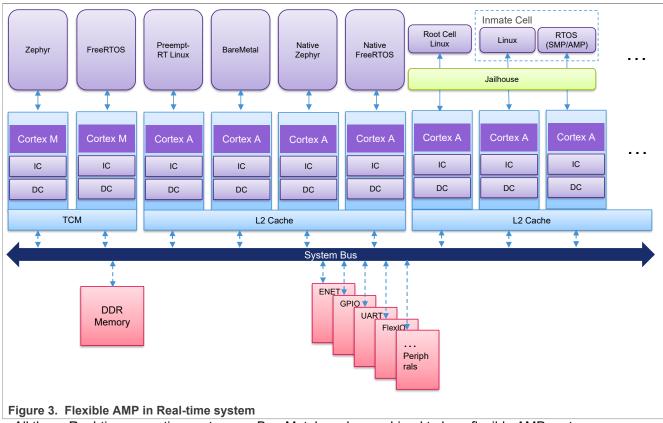

The <u>Figure 3</u> shows all the OS/Baremetal supported in Real-time Edge on MPU platforms with different-scale schedule latency:

# - Preempt-RT Linux on Cortex-A Core

Real-time Linux kernel provides deterministic low latency compared to Linux.

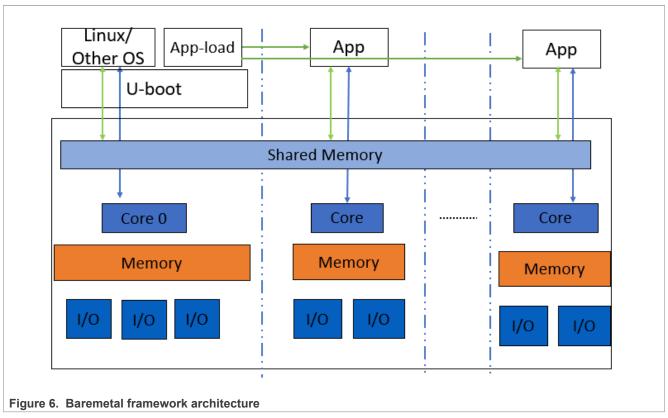

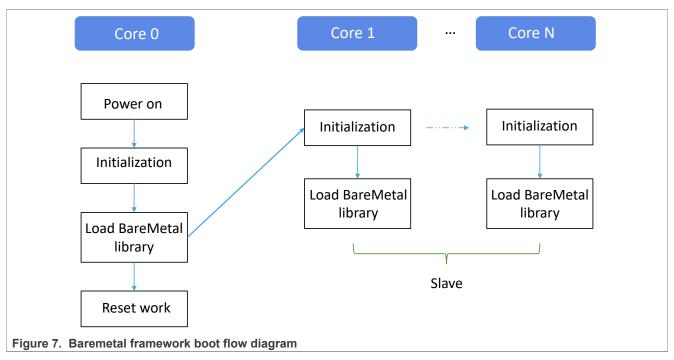

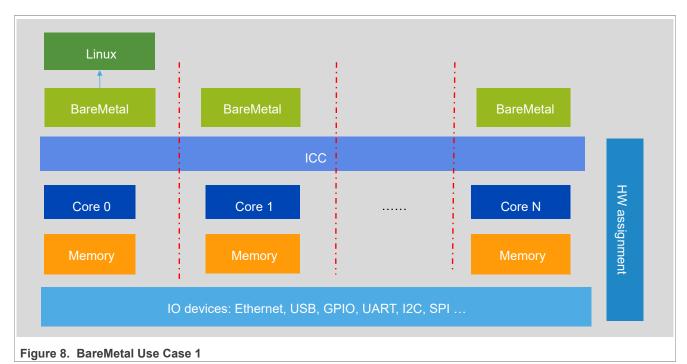

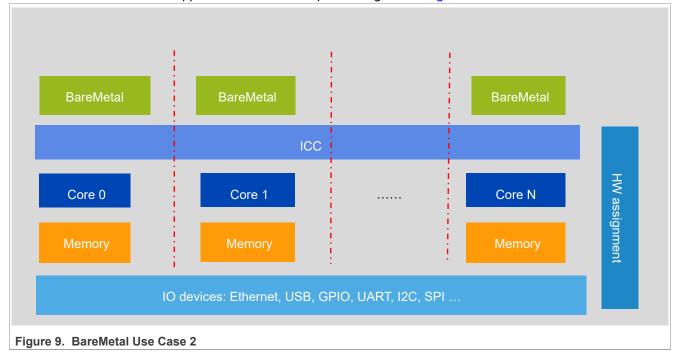

#### - Baremetal on Cortex-A Core

Single or multiple BareMetal instance run Cortex-A Core(s) with zero schedule latency.

### - Native RTOS SMP/AMP on Cortex-A Core

Native RTOS (FreeRTOS or Zephyr) is kicked to one or more Cortex-A Core from U-Boot, no Jailhouse is used and targets lower latency and higher performance as compared to RTOS with Jailhouse.

#### - RTOS SMP/AMP on Corex-A Core with Jailhouse

RTOS (FreeRTOS or Zephyr) runs in Jailhouse inmate with hardware resource isolations on Cortex-A Core.

### - RTOS and Baremetal on Cortex-M Core

This is generally used for Real-time Control systems, but has less CPU computing ability than Cortex-A Core.

All these Real-time operating systems or BareMetal can be combined to be a flexible AMP system on multicore system. For example, i.MX 8M Plus platform has four Cortex-A53 cores and one Cortex-M7 core. The Real-time Edge software supports the flexible AMP system to run these OS/BareMetal combinations:

- Four Cortex-A53 cores run SMP Preempt-RT Linux, Cortex-M7 core run RTOS.

- Four Cortex-A53 cores run four Baremetal/RTOS instances. Cortex-M7 core run RTOS.

- One or more Cortex-A53 cores run Preempt-RT Linux, the other Cortex-A53 cores run one or more.

Baremetal/RTOS instances, Cortex-M7 core run RTOS.

- One or more Cortex-A53 cores run Preempt-RT Linux as Jailhouse Root Cell, the other Cortex-A53 cores run as one or more inmate cell(s) with RTOS.

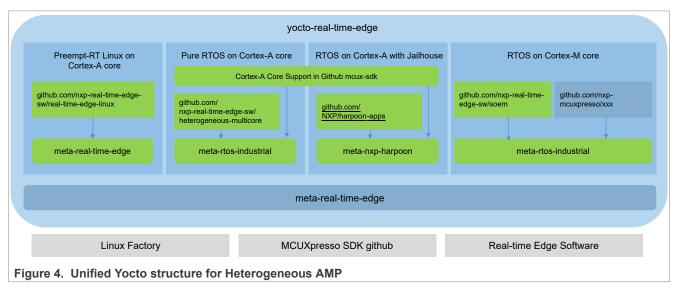

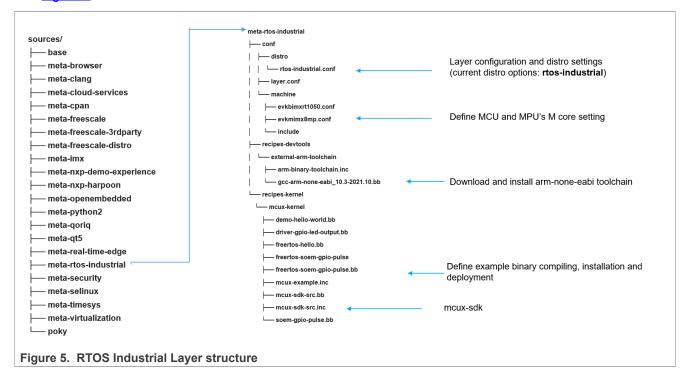

#### Unified Software Building, Deploy, and Release

- All different OS/application running on different cores are built via Yocto.

- A bitbake command is used to create all images on different cores.

- Single Flash Image includes all OS/applications running on all CPU cores.

# Heterogeneous Multicore Framework

A common framework with the following key features and functions:

Inter-Core Data Communication and Resource Sharing

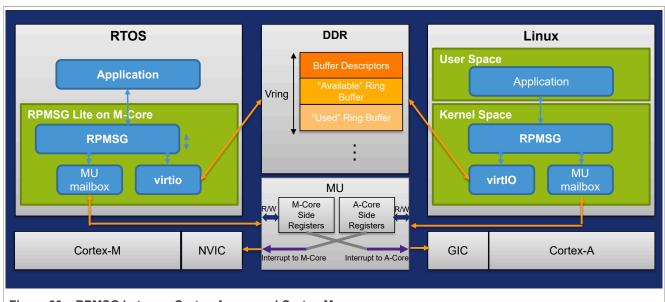

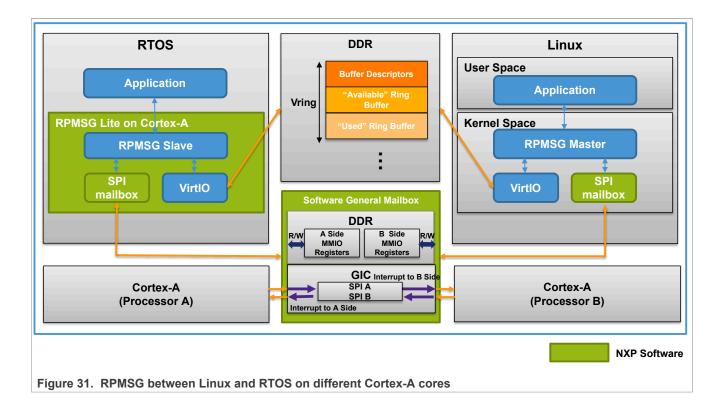

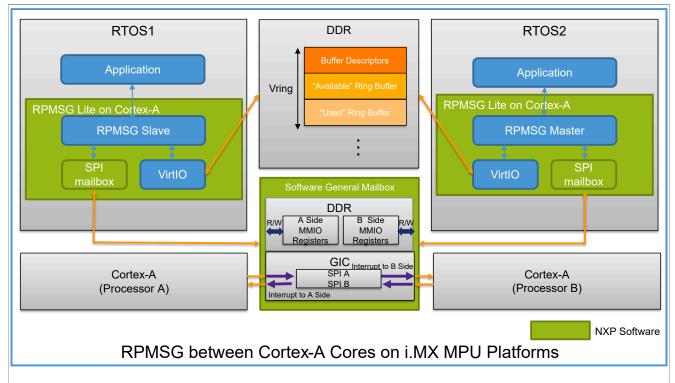

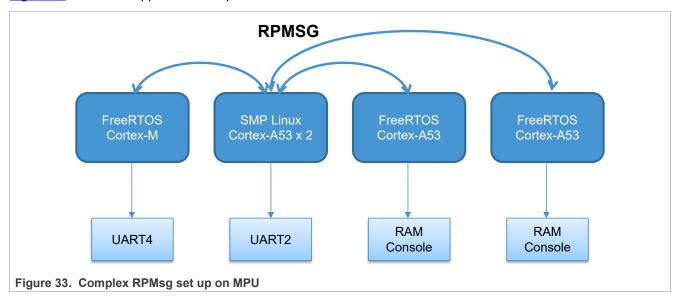

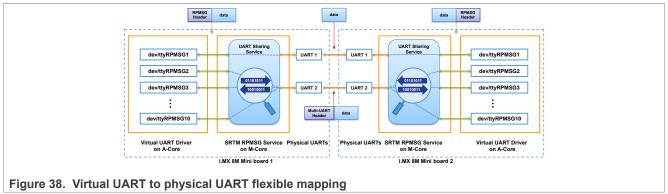

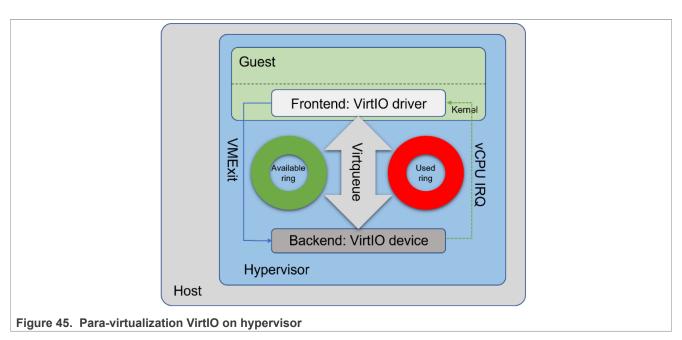

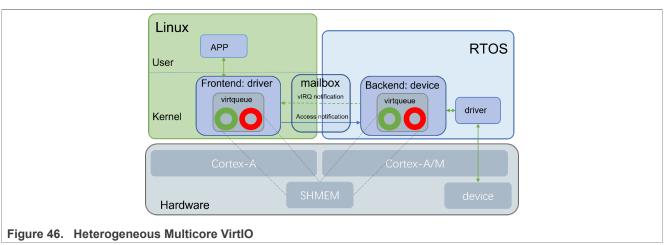

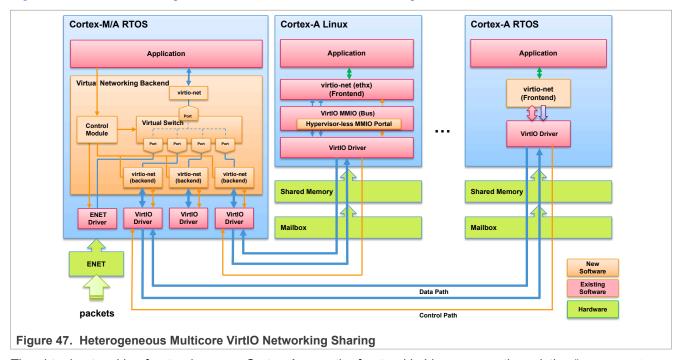

Common Heterogeneous Multicore Framework provides data communication and resource sharing between M-Core and A-Core(s) or between different A-Cores simultaneously: RPMSG provides standard message communication for low bandwidth use cases, and Heterogeneous Multicore Virtio provides high performance data path and resource sharing to meet high bandwidth requirement.

- Unified Life-Cycle management for flexible AMP

Real-time Edge software supports Preempt-RT Linux, FreeRTOS, Zephyr, and BareMetal running on different processors with Heterogeneous Multicore Framework.

# 2.1.1 Real-time-system support matrix

The Table 4 shows the support matrix on NXP platforms:

Table 4. Real-time-system support matrix

|        | eal-time<br>System | i.MX 8M<br>LPDDR4 |           | i.MX 8M<br>LPDD<br>EVI | R4        | i.MX 8     | DXL       | i.MX 93    | EVK        | i.MX<br>EVK<br>x 1 | (14        | i.MX<br>RT1180<br>EVK |            | i.MX<br>91<br>11x11<br>EVK | i.M)<br>15)<br>E\ | (15       | 192        | ( 95<br>(19<br>/K | LS1028<br>ARDB | LS1043<br>ARDB | LS1046<br>ARDB | LX2160<br>ARDB |

|--------|--------------------|-------------------|-----------|------------------------|-----------|------------|-----------|------------|------------|--------------------|------------|-----------------------|------------|----------------------------|-------------------|-----------|------------|-------------------|----------------|----------------|----------------|----------------|

|        | Cores              | 4 xA53            | 1 x<br>M4 | 4 x<br>A53             | 1 x<br>M7 | 2 x<br>A35 | 1 x<br>M4 | 2 x<br>A55 | 1 x<br>M33 | 2 x<br>A55         | 1 x<br>M33 |                       | 1 x<br>A55 | 1 x<br>A55                 |                   | 1 x<br>M7 | 6 x<br>A55 | 1 x<br>M7         | 2 x A72        | 4 x<br>A53     | 4 x<br>A72     | 16 x<br>A72    |

| Preem  | npt-RT Linux       | Y                 |           | Y                      |           | Y          |           | Y          |            | Y                  |            |                       | Υ          | Υ                          | Y                 |           | Υ          |                   | Y              | Y              | Y              | Y              |

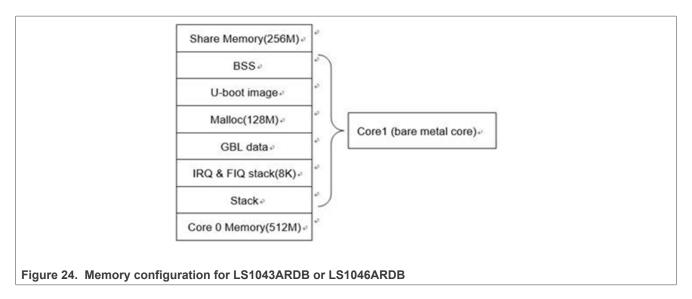

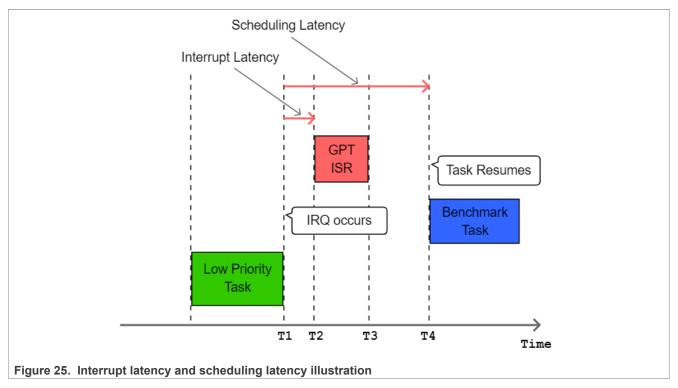

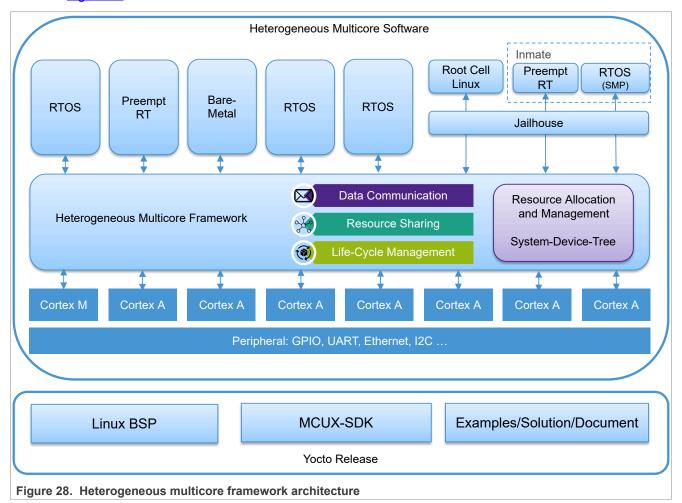

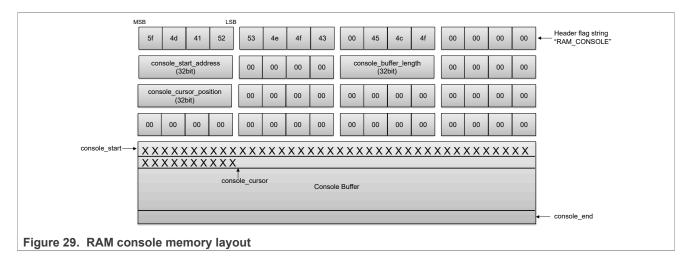

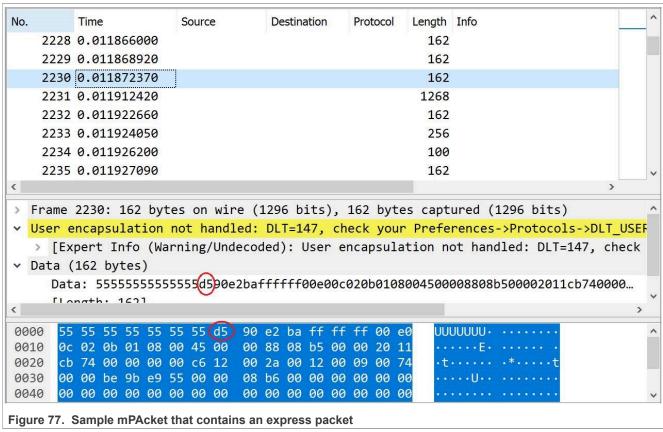

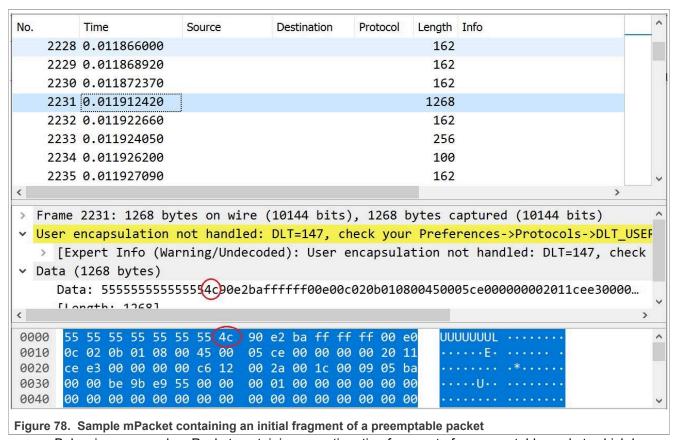

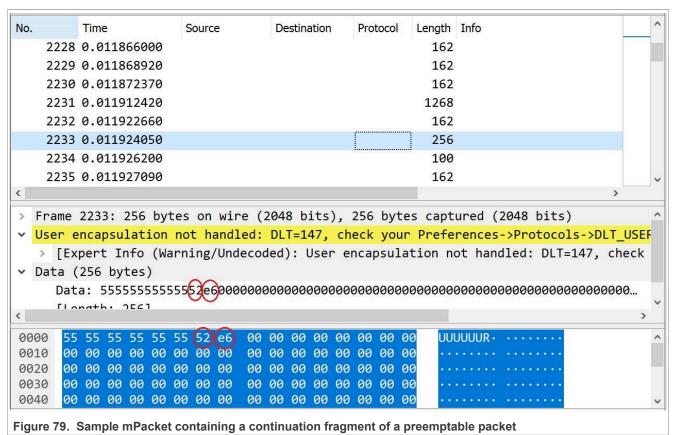

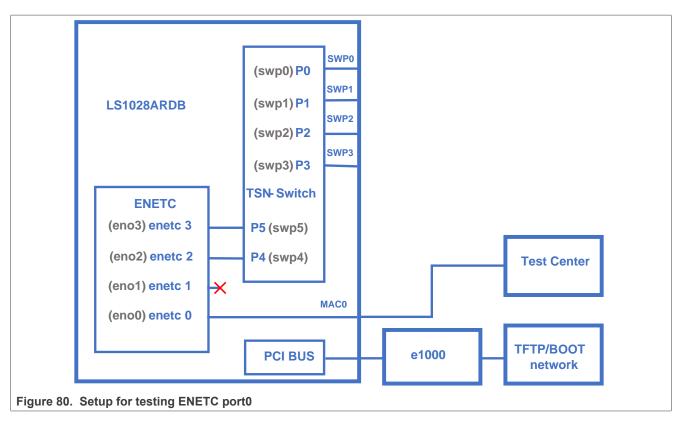

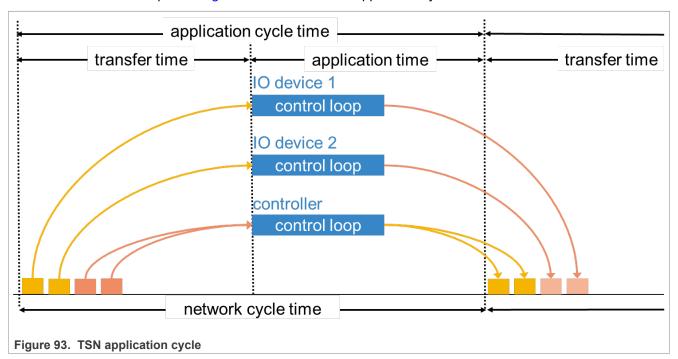

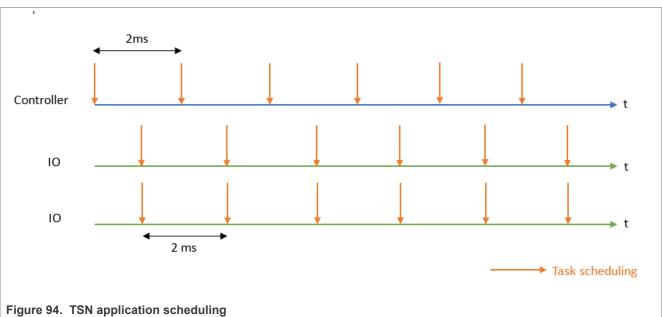

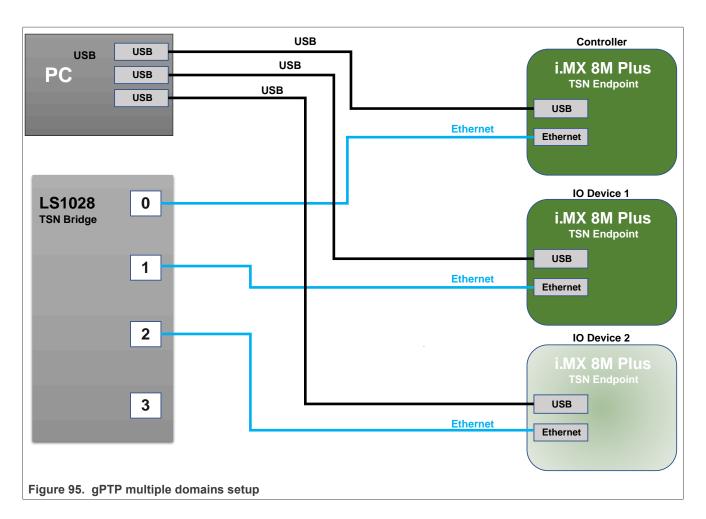

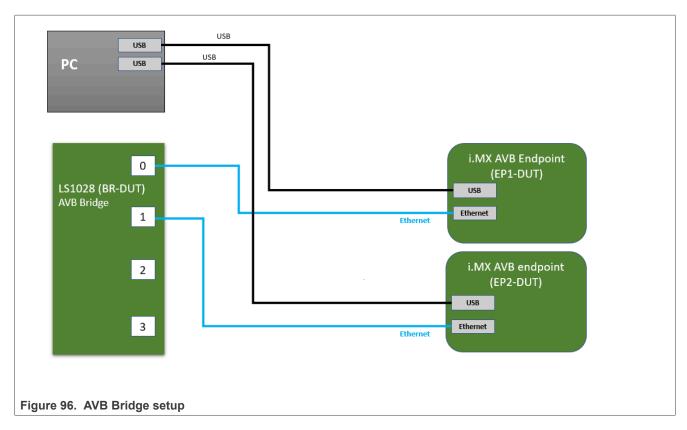

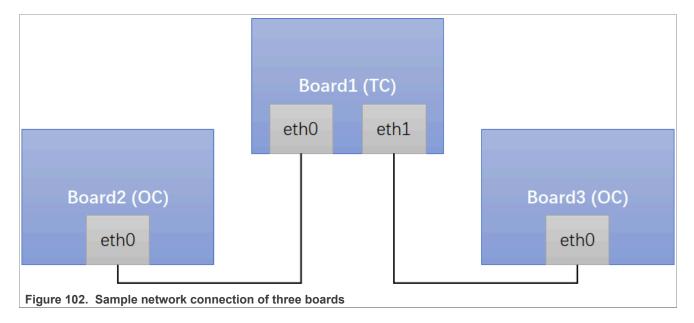

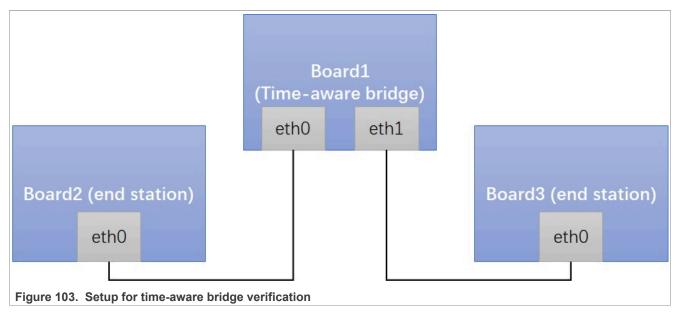

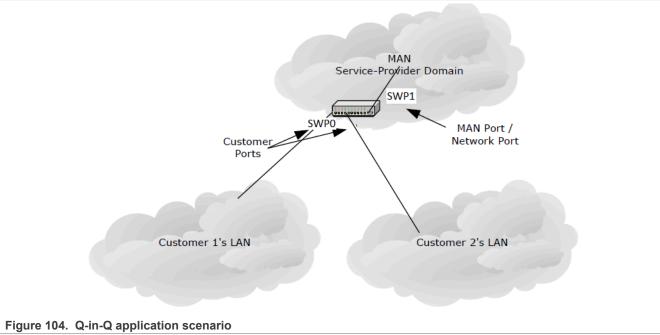

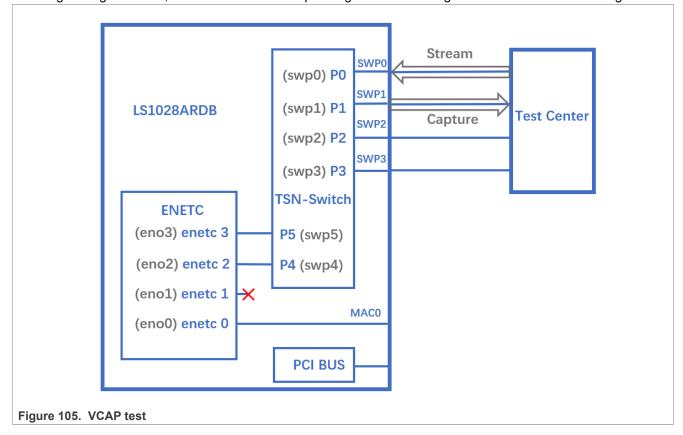

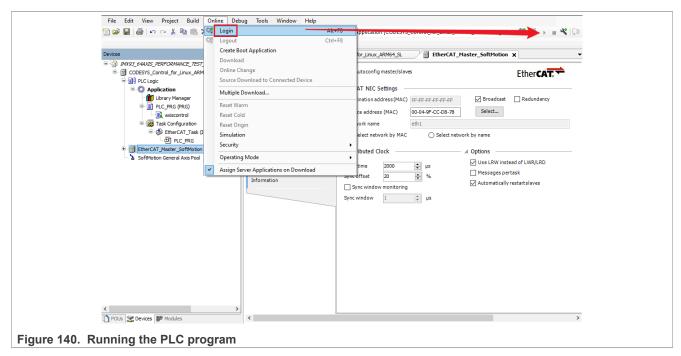

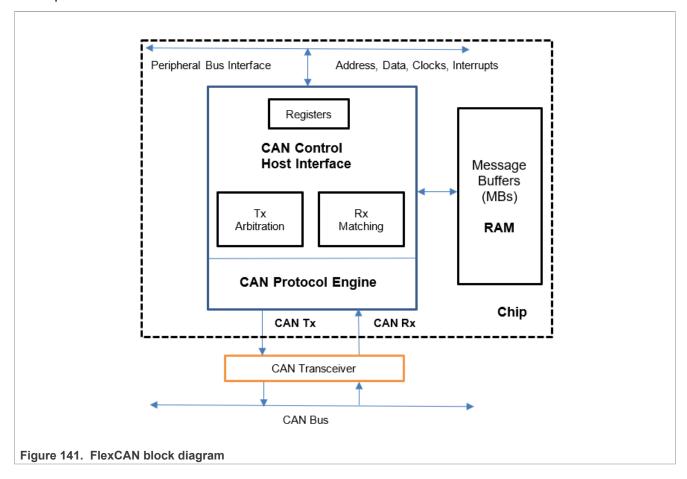

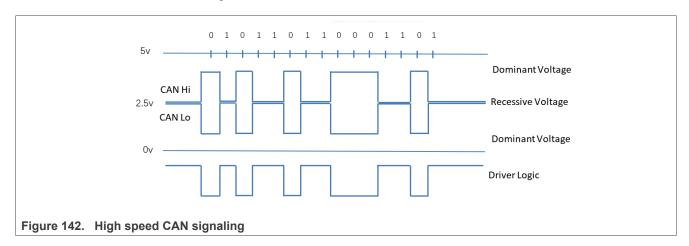

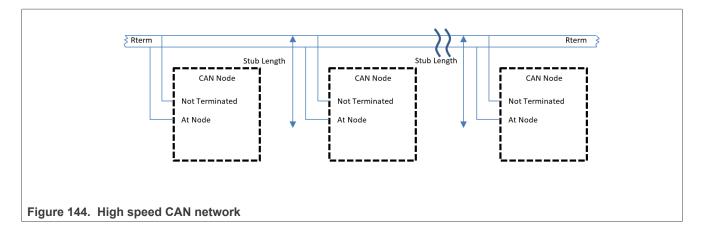

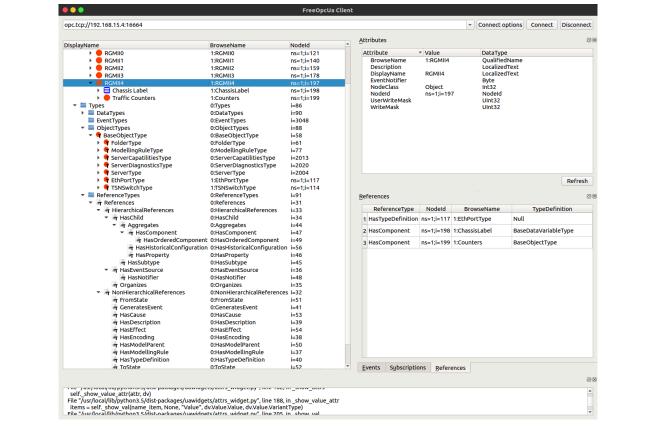

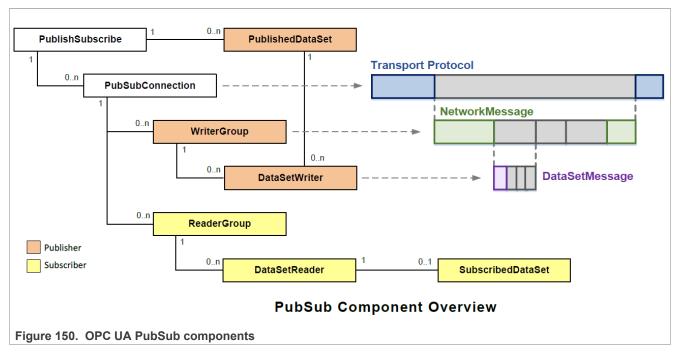

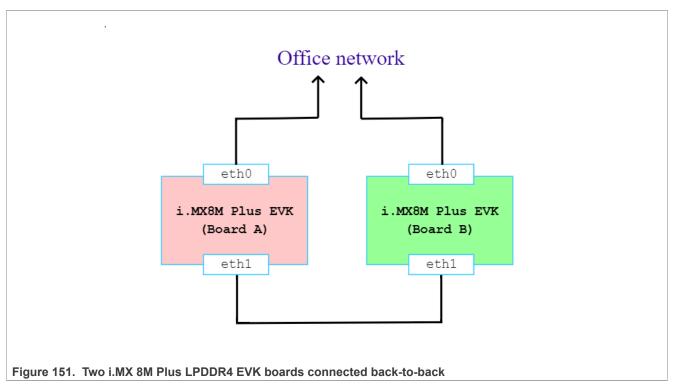

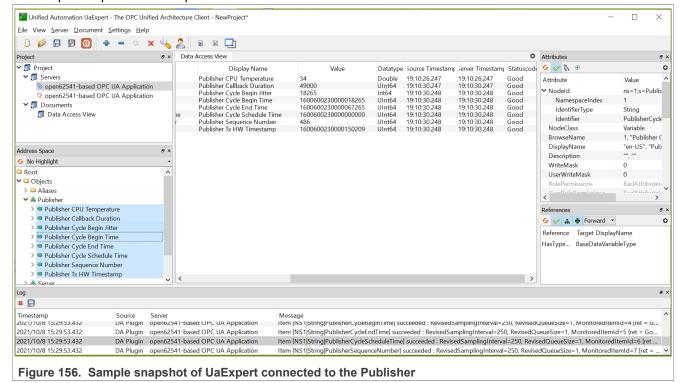

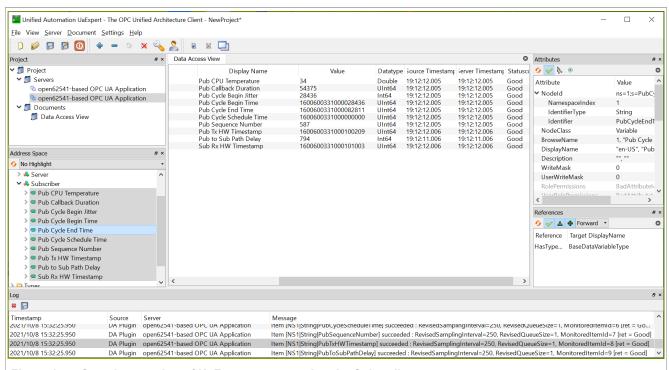

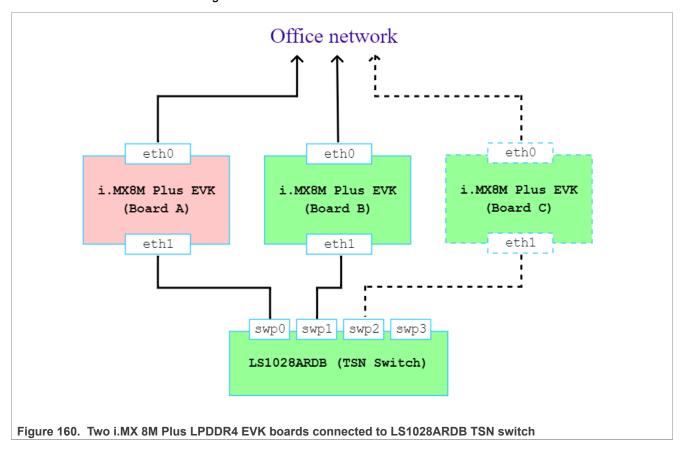

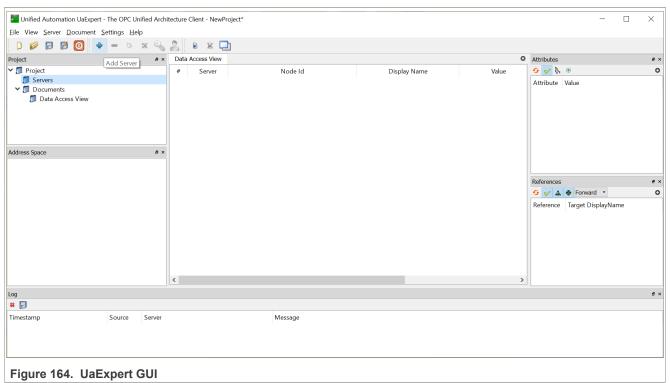

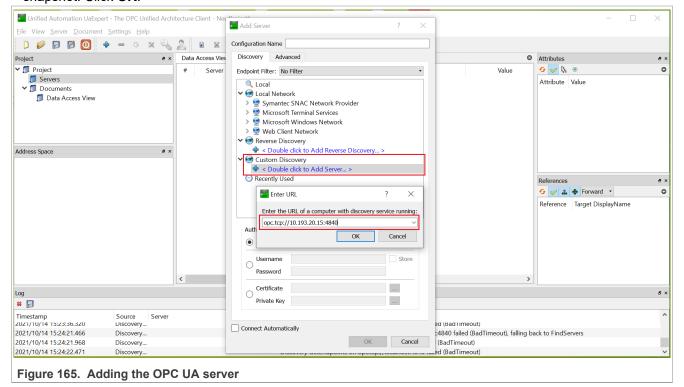

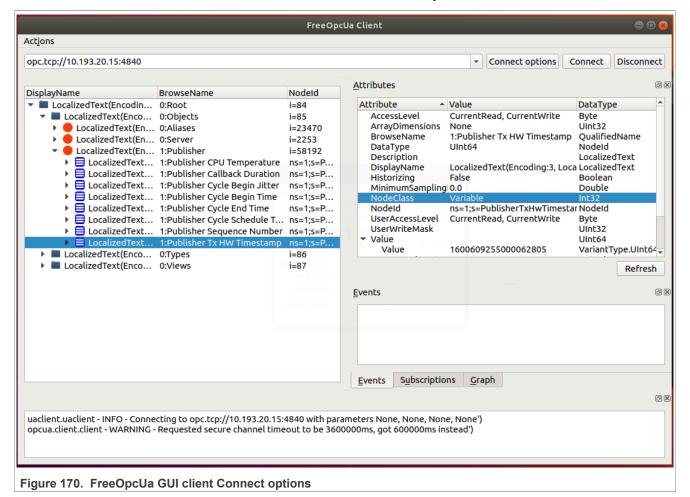

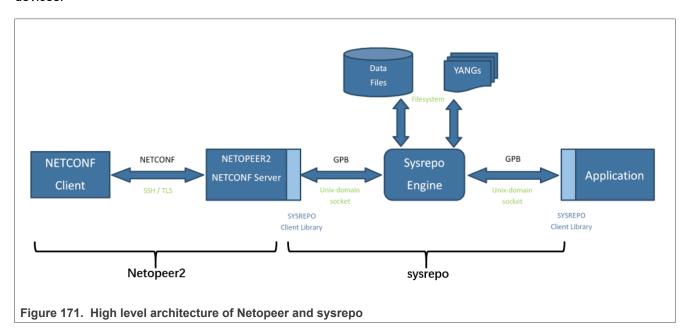

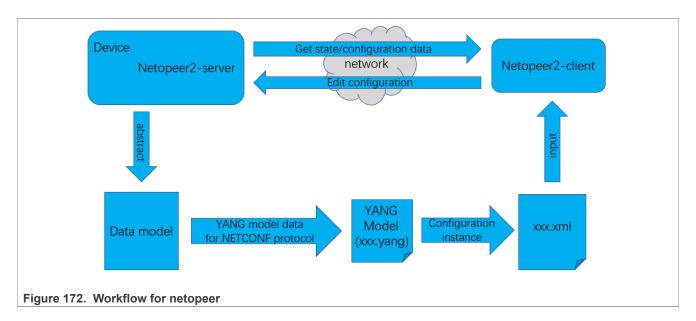

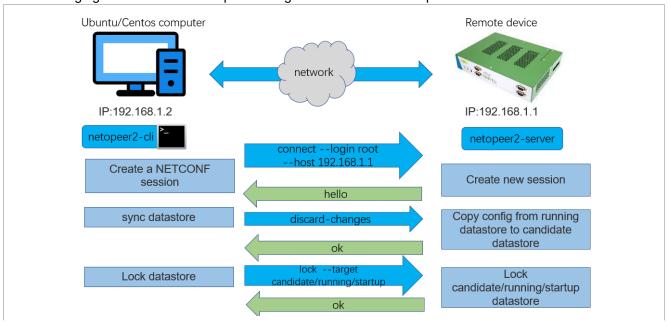

| BareN  |                    | Y                 | Υ         | Υ                      | Y         |            |           | Y          | Y          |                    |            |                       |            |                            |                   |           |            |                   | Y              | Y              | Y              | Y              |