## MPC8xx ATM Supplement to the MPC860/MPC850 PowerQUICC™ User's Manual

© Motorola Inc. 1998. All rights reserved.

Portions hereof © International Business Machines Corp. 1991–1998. All rights reserved.

This document contains information on a new product under development. Motorola reserves the right to change or discontinue this product without notice. Information in this document is provided solely to enable system and software implementers to use PowerPC microprocessors. There are no express or implied copyright licenses granted hereunder to design or fabricate PowerPC integrated circuits or integrated circuits based on the information in this literature. When the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters can and do vary in different applications. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part.

Motorola and (Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

The PowerPC name is a registered trademark and the PowerPC logotype is a trademark of International Business Machines Corporation used by Motorola under license from International Business Machines Corporation. SDLC is a trademark of International Business Machines Corporation.

AppleTalk is a registered trademark of Apple Computer, Inc. Centronics is a trademark of Centronics, Inc.

| Paragraph<br>Number | Title                                                        | Page<br>Number |

|---------------------|--------------------------------------------------------------|----------------|

|                     | Chapter 1                                                    |                |

|                     | Overview                                                     |                |

| 1.1                 | MPC860SAR Capabilities                                       | 1-1            |

| 1.2                 | Comparison with the MPC860                                   |                |

| 1.2.1               | Microcode Changes                                            |                |

| 1.2.2               | Functionality Limitations Due to Internal Resources          |                |

| 1.2.2.1             | General Issues                                               |                |

| 1.2.2.2             | Issues Concerning the UTOPIA Interface                       |                |

| 1.2.2.3             | Issues Concerning the ATM Pace Controller (APC)              |                |

| 1.2.3               | Functionality Limitations Due to Pin Multiplexing            |                |

| 1.3                 | Features                                                     |                |

| 1.4                 | MPC860SAR and MPC850SAR Comparison                           | 1-5            |

| 1.5                 | General Description                                          |                |

| 1.5.1               | ATM Controller UTOPIA Mode                                   |                |

| 1.5.1.1             | Transmitter Overview                                         | 1-6            |

| 1.5.1.2             | Receiver Overview                                            |                |

| 1.5.2               | ATM Controller Serial Mode                                   | 1-8            |

| 1.5.2.1             | Transmitter Overview                                         | 1-8            |

| 1.5.2.2             | Receiver Overview                                            | 1-9            |

| 1.5.2.3             | Cell Delineation                                             | 1-10           |

| 1.5.2.4             | Cell Payload Scrambling                                      | 1-10           |

| 1.5.3               | Extended Channel Mode                                        |                |

| 1.5.4               | ATM Pace Control (APC)                                       | 1-11           |

| 1.5.5               | Expanded Cells                                               | 1-11           |

|                     | Chapter 2 Buffer Descriptor Structures and Connection Tables | e              |

|                     | ·                                                            |                |

| 2.1                 | Buffer Descriptors (BD)                                      |                |

| 2.1.1               | AAL5 Buffers                                                 |                |

| 2.1.2               | AAL0 Buffers                                                 |                |

| 2.1.3               | Receive Buffer Descriptor                                    |                |

| 2.1.4               | Transmit Buffer Descriptor                                   |                |

| 2.2                 | Receive and Transmit Connection Tables                       |                |

| 2.2.1               | Receive Connection Table (RCT)                               |                |

| 2.2.2               | Transmit Connection Table (TCT)                              | 2-12           |

|                     | Chapter 3 Parameter RAM Configuration                        |                |

| 2.1                 | Parameter RAM Map                                            | 2 1            |

| 3.1                 | rarameter KAWI Wap                                           | 3-1            |

| Paragraph<br>Number | Title                                                 | Page<br>Number |

|---------------------|-------------------------------------------------------|----------------|

| 3.1.1               | Receive Function Code and Status Register             | 3-6            |

| 3.1.2               | Transmit Function Code and Status Register            | 3-8            |

| 3.1.3               | Address Match Parameters (AM1–AM5)                    |                |

| 3.1.4               | APC Status Register (APCST)                           |                |

| 3.1.5               | Serial Cell Synchronization Status Register (ASTATUS) | 3-13           |

|                     | Chapter 4                                             |                |

|                     | ATM Controller                                        |                |

| 4.1                 | Address Mapping                                       | 4-1            |

| 4.1.1               | VCI/VPI Look-up Table                                 | 4-1            |

| 4.1.1.1             | Adding a New Channel Entry                            |                |

| 4.1.1.2             | Removing a Channel Entry                              |                |

| 4.1.2               | Address Compression                                   |                |

| 4.1.2.1             | First-Level Addressing Table                          |                |

| 4.1.2.2             | Second-Level Addressing Tables                        |                |

| 4.1.2.3             | Dual-Level Address Compression Example                |                |

| 4.1.2.4             | Anti-Channel Aliasing Function                        |                |

| 4.1.2.5             | OAM Screening Function                                |                |

| 4.1.2.6             | Location of Connection Tables                         |                |

| 4.1.3               | CAM Address Mapping                                   | 4-5            |

| 4.2                 | Multi-PHY Configuration (MPHY)                        |                |

| 4.2.1               | Setting Multi-PHY mode                                |                |

| 4.2.2               | Receive Multi-PHY Operation                           |                |

| 4.2.2.1             | Look-up Table MPHY Support                            |                |

| 4.2.2.2             | Address Compression Multi-PHY Support                 |                |

| 4.2.2.3             | CAM Multi-PHY Support                                 |                |

| 4.2.3               | Transmit Multi-PHY Operation                          |                |

| 4.2.4               | APC Multi-PHY Parameters                              |                |

| 4.3                 | MPC860SAR Commands                                    |                |

|                     | Chapter 5                                             |                |

|                     | ATM Pace Control                                      |                |

| 5.1                 | APC Algorithm                                         | 5-1            |

| 5.1.1               | APC Implementation Details                            |                |

| 5.1.2               | APC Parameters                                        |                |

| 5.1.3               | Programming APC Table Size and NCITS                  |                |

| 5.1.4               | Defining APC Slot Time                                |                |

| 5.1.5               | Programming Rates for Channels                        |                |

| 5.1.6               | APC Initialization and Operating Considerations       |                |

| 5.1.7               | Modifying Channel Transmit Pace                       |                |

|                     | , ,                                                   |                |

| Paragraph<br>Number | Title                                       | Page<br>Number |

|---------------------|---------------------------------------------|----------------|

| 5.1.8               | Minimizing Cell Delay Variation             | 5-6            |

| 5.2                 | Direct Scheduling of Cells                  | 5-6            |

| 5.3                 | Using the APC with Multiple ATM Ports       | 5-6            |

| 5.4                 | Using the APC Without Using SCC4 or UTOPIA  | 5-8            |

| 5.5                 | APC Table                                   | 5-9            |

| 5.6                 | Transmit Queue                              | 5-9            |

| 5.7                 | APC Parameters                              | 5-10           |

|                     | Chapter 6                                   |                |

|                     | Exceptions                                  |                |

| 6.1                 | Event Register                              | 6-2            |

| 6.1.1               | UTOPIA Mode Event Register (IDSR1)          | 6-2            |

| 6.1.2               | Serial Mode Event Register (SCCE)           | 6-3            |

| 6.2                 | Exception Queue Entry                       |                |

| 6.3                 | Interrupt Table Mask (IMASK)                | 6-6            |

|                     | Chapter 7                                   |                |

|                     | Interface Configuration                     |                |

| 7.1                 | General Registers                           | 7-1            |

| 7.1.1               | Port D Pin Assignment Register (PDPAR)      | 7-1            |

| 7.1.2               | Timer 4                                     | 7-2            |

| 7.1.3               | CP Timer                                    | 7-2            |

| 7.2                 | UTOPIA Mode Registers                       |                |

| 7.2.1               | System Clock Control Register (SCCR)        |                |

| 7.2.2               | Port B—TxCAV Signal                         |                |

| 7.2.3               | Port C—RxCav Signal                         |                |

| 7.2.4               | Port D—UTOPIA Data and Control Signals      |                |

| 7.2.5               | CP Controller Configuration Register (RCCR) | 7-5            |

| 7.2.6               | UTOPIA Mode Initialization Process          |                |

| 7.3                 | Serial Mode Configuration                   | 7-6            |

| 7.3.1               | CP Controller Configuration Register (RCCR) |                |

| 7.3.2               | SCC Configuration                           | 7-6            |

| 7.3.2.1             | General SCC Mode Register (GSMR)            | 7-6            |

| 7.3.2.2             | Protocol-Specific Mode Register (PSMR)      | 7-7            |

| 7.3.2.3             | SCC Event Register (SCCE)                   | 7-7            |

| 7.3.2.4             | SCC Mask Register (SCCM)                    | 7-7            |

| 7.3.3               | Serial Interface Configuration              | 7-7            |

| 7.3.3.1             | Serial Interface Registers                  | 7-8            |

|                     | Chapter 8                                   |                |

| Paragraph<br>Number | Title                               | Page<br>Number |

|---------------------|-------------------------------------|----------------|

|                     | UTOPIA Interface                    |                |

| 8.1                 | MPC860SAR UTOPIA Interface Signals  | 8-1            |

| 8.2                 | UTOPIA Single-PHY                   | 8-6            |

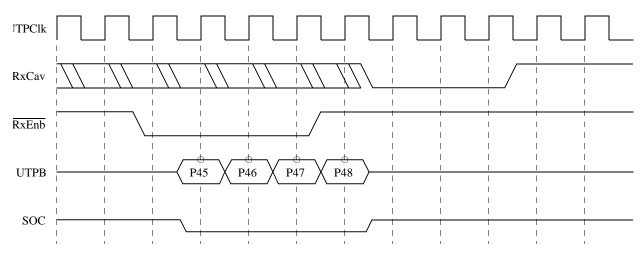

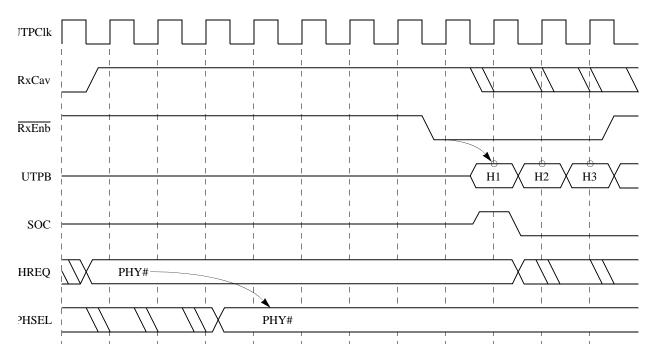

| 8.2.1               | Receive Cell Transfer Operation     | 8-6            |

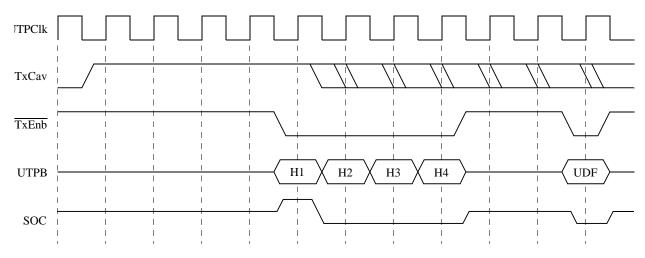

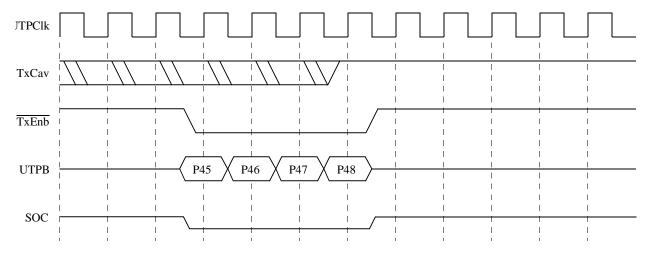

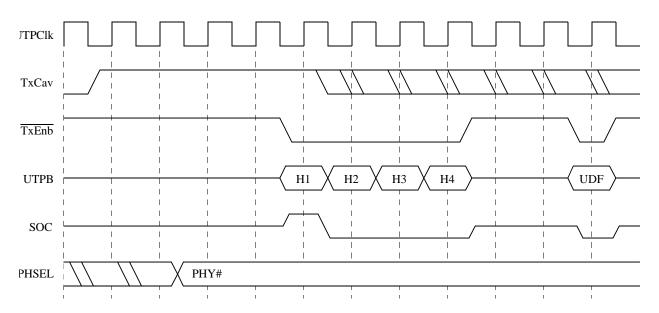

| 8.2.2               | Transmit Cell Transfer Operation    | 8-8            |

| 8.2.2.1             | UTOPIA Bus and SOC Drive            | 8-8            |

| 8.3                 | UTOPIA Multi-PHY Operations         | 8-9            |

| 8.3.1               | Setting up PHSEL and PHREQ Pins     |                |

| 8.3.2               | Receive Cell Transfer Operation     | 8-10           |

| 8.3.3               | Transmit Cell Transfer Operation    | 8-11           |

| 8.3.4               | Example MPHY Implementation         | 8-11           |

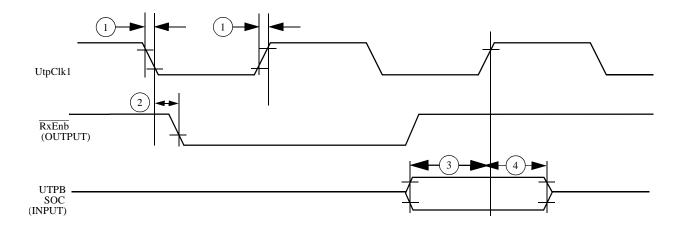

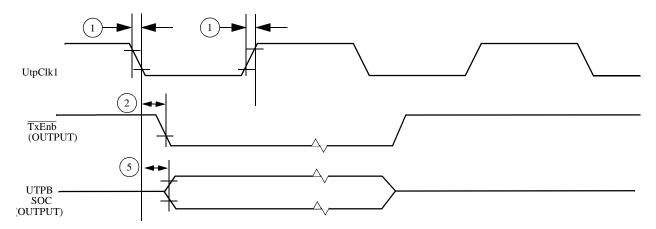

| 8.4                 | UTOPIA Interface Transfer Timing    | 8-13           |

| 8.5                 | UTOPIA AC Electrical Specifications | 8-15           |

|                     | Appendix A                          |                |

|                     | Performance                         |                |

| A.1                 | Receiver                            | A-1            |

| A.2                 | Transmitter                         | A-2            |

## **ILLUSTRATIONS**

| Figure<br>Number | Title                                                           | Page<br>Number |

|------------------|-----------------------------------------------------------------|----------------|

| Figure 1-1       | . MPC860SAR Application Example                                 | 1-5            |

| Figure 1-2       | . Expanded Cell Structure                                       | 1-12           |

| Figure 2-1       | . Transmit Buffer and BD List Example                           | 2-2            |

| Figure 2-2       | . AAL0 Buffer Structure                                         | 2-3            |

| Figure 2-3       | . Receive Buffer Descriptor                                     | 2-3            |

| Figure 2-4       | . Transmit Buffer Descriptor                                    | 2-6            |

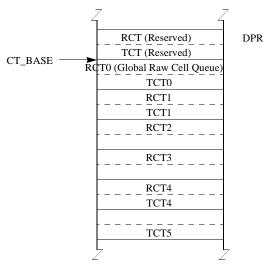

| Figure 2-5       | . Example of a Six-Entry Connection Table in Dual-port RAM      | 2-8            |

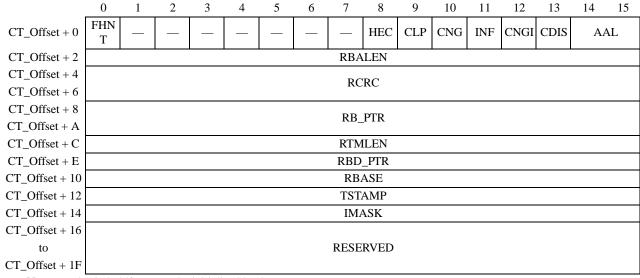

| Figure 2-6       | . Receive Connection Table (RCT)                                | 2-9            |

| Figure 2-7       | . Transmit Connection Table (TCT)                               | 2-12           |

| Figure 3-1       | . Receive Function Code and Status Register                     | 3-6            |

| Figure 3-2       | . Transmit Function Code and Status Register                    | 3-8            |

| Figure 3-3       | . HMASK                                                         | 3-10           |

| Figure 3-4       | . FLMASK                                                        | 3-11           |

| Figure 3-5       | . APC Status Register (APCST)                                   |                |

| Figure 3-6       | . Serial Cell Synchronization Status Register (ASTATUS)         | 3-13           |

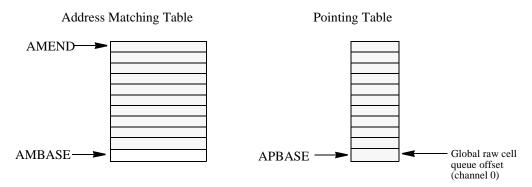

| Figure 4-1       | . Address Mapping Tables                                        | 4-2            |

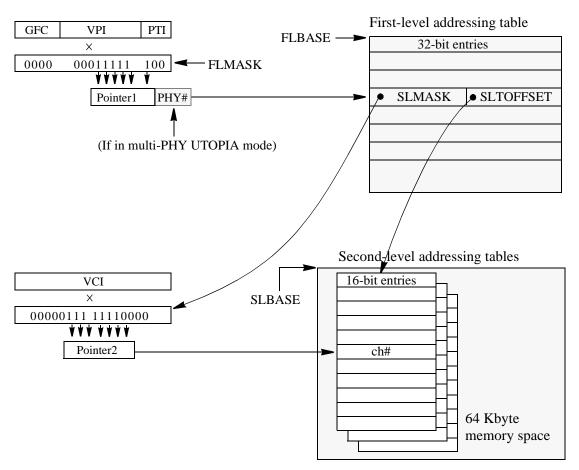

| Figure 4-2       | . Address Compression                                           | 4-4            |

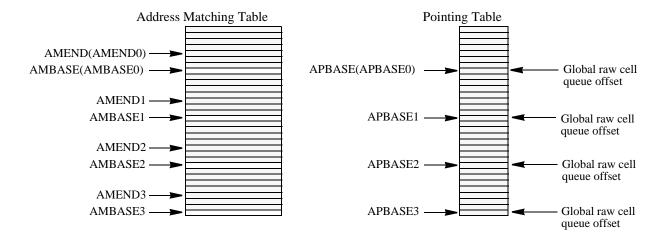

| Figure 4-4       | . Address Mapping Tables for Multi-PHY Operations               |                |

| Figure 4-3       | . Multi-PHY Pointing Table Entry                                | 4-6            |

| Figure 4-5       | . CPM Command Register (CPCR)                                   |                |

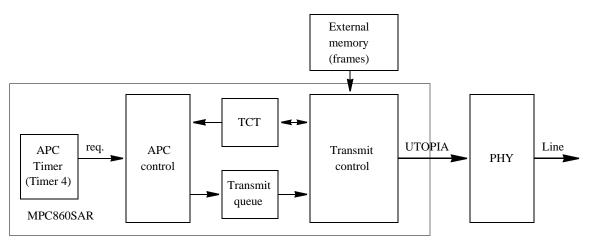

| Figure 5-1       | . APC in the MPC860SAR UTOPIA Mode—Transmit Flow                | 5-2            |

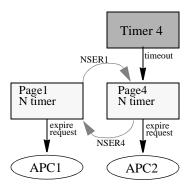

| Figure 5-2       | . Example of Single PHY and Single Serial APC Configuration     | 5-7            |

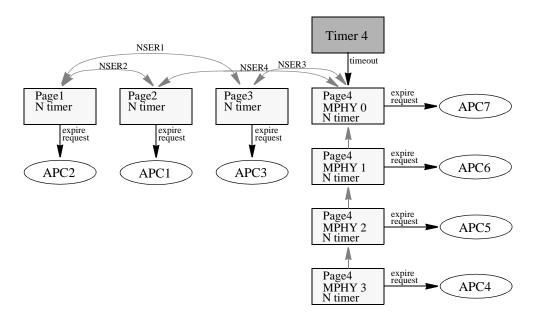

| Figure 5-3       | . Example of Maximum Multi-PHY and Multi-Serial APC Configurate |                |

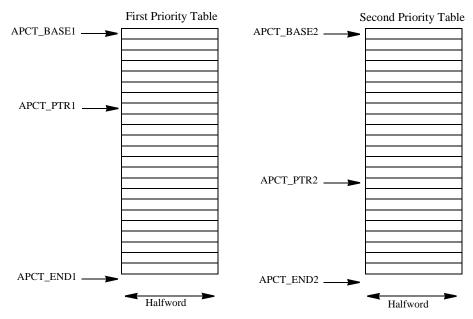

| Figure 5-4       | . APC Table                                                     | 5-9            |

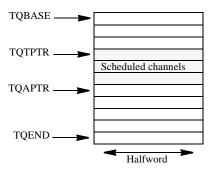

| Figure 5-5       | . Transmit Queue                                                | 5-10           |

| Figure 6-1       | . Circular Exception Queue                                      |                |

| Figure 6-2       | . UTOPIA Mode Event Register (IDSR1)                            | 6-2            |

| Figure 6-3       | . Serial Mode Event Register (SCCE)                             | 6-3            |

| Figure 6-4       | . Exception Queue Entry                                         |                |

| Figure 7-1       | . Port D Pin Assignment Register (PDPAR)                        | 7-1            |

| Figure 7-2       | . System Clock Control Register (SCCR)                          | 7-4            |

| Figure 7-3       | . Protocol-Specific Mode Register (PSMR)                        |                |

| Figure 8-1       | . MPC860SAR UTOPIA Interface                                    |                |

| Figure 8-2       | . UTOPIA Receiver Start of Cell                                 | 8-7            |

| Figure 8-3       | . UTOPIA Receiver End of Cell                                   |                |

| Figure 8-4       | . UTOPIA Transmitter Start of Cell                              |                |

| Figure 8-5       | . UTOPIA Transmitter End of Cell                                | 8-9            |

| Figure 8-6       | . Multi-PHY Implementation Example                              |                |

| Figure 8-7       | . UTOPIA Receiver Multi-PHY Example                             |                |

| Figure 8-8       | . UTOPIA Transmitter Multi-PHY Example                          |                |

| Figure 8-9       | . UTOPIA Receive Timing                                         |                |

| Figure 8-10      | . UTOPIA Transmit Timing                                        | 8-16           |

## **ILLUSTRATIONS**

Figure Page Number Title Page

## **TABLES**

| Table<br>Number | Title                                                                | Page<br>Number |

|-----------------|----------------------------------------------------------------------|----------------|

| Table 2-1       | . Receive Buffer Descriptor Field Descriptions                       | 2-4            |

| Table 2-2       | . Transmit Buffer Descriptor Field Descriptions                      | 2-7            |

| Table 2-3       | . RCT Field Descriptions                                             | 2-10           |

| Table 2-4       | .TCT Field Descriptions                                              |                |

| Table 3-1       | . Serial and UTOPIA Interface Parameter RAM Configuration            | 3-1            |

| Table 3-2       | . Serial Interface Parameter RAM Configuration                       | 3-6            |

| Table 3-3       | . Receive Function Code and Status Register Field Descriptions       | 3-7            |

| Table 3-4       | . Transmit Function Code and Status Register Field Descriptions      | 3-9            |

| Table 3-5       | . AM1-AM5 Parameter Configuration with Look-up Table                 | 3-10           |

| Table 3-6       | . HMASK Field Descriptions                                           | 3-11           |

| Table 3-7       | . AM1-AM5 Parameter Configuration in Extended Channel Mode           | 3-11           |

| Table 3-8       | . FLMASK Field Descriptions                                          |                |

| Table 3-9       | . AM1-AM5 Parameter Usage—Extended Channel Mode                      | 3-12           |

| Table 3-10      | . APC Status Register Field Descriptions                             | 3-13           |

| Table 3-11      | . ASTATUS Register Field Descriptions                                | 3-14           |

| Table 4-1       | . CPCR Field Descriptions                                            |                |

| Table 4-2       | . MPC860SAR Commands                                                 | 4-9            |

| Table 5-1       | . APC Parameters                                                     | 5-10           |

| Table 5-2       | . APC Parameter Descriptions                                         | 5-11           |

| Table 6-1       | . IDSR1 Field Descriptions                                           | 6-2            |

| Table 6-2       | . SCCE Field Descriptions                                            | 6-3            |

| Table 6-3       | . Exception Queue Entry Field Descriptions                           |                |

| Table 7-1       | . PDPAR Field Descriptions                                           |                |

| Table 7-2       | . SCCR Field Descriptions                                            |                |

| Table 7-3       | . Port D Pin Assignment                                              |                |

| Table 7-4       | . PSMR Field Descriptions                                            |                |

| Table 8-1       | . MPC860SAR Signal Functions                                         |                |

| Table 8-2       | . MPC850SAR Signal Functions                                         |                |

| Table 8-3       | . UTOPIA Interface Transfer Timing                                   |                |

| Table 8-4       | . UTOPIA AC Electrical Specifications                                |                |

| Table A-1       | . Receiver Performance (with 50MHz System Clock)                     |                |

| Table A-2       | . Transmitter (Including 1 Priority APC) Performance (with 50MHz Sys | stem Clock)    |

|                 | Λ 2                                                                  |                |

MOTOROLA Tables ix

## **TABLES**

Table Page Number Title Page

## Chapter 1 Overview

This chapter provides an overview of the features of the MPC860SAR and the differences between the 860SAR and the MPC860. This document also serves as the programming/design model for use with the MPC850SAR. Differences between the MPC850SAR and the MPC860SAR are detailed later in this chapter.

## 1.1 MPC860SAR Capabilities

The MPC860SAR is a member of the MPC860 PowerQUICC<sup>TM</sup> family. In addition to the standard MPC860MH capabilities, the 860SAR includes the universal test & operations PHY interface for ATM (UTOPIA), AAL5 and AAL0 segmentation and reassembly (SAR) functionality, an ATM pace controller (APC) and transmission convergence (TC) sublayer for E1/DS1 and xDSL implemented by the serial channels.

These features make the 860SAR a very adaptable ATM SAR controller that can be used for a variety of ATM applications. Several examples follow:

- ATM line card controllers

- ATM to WAN interworking (frame relay, T1/E1 circuit emulation, ADSL applications)

- Residential broadband network interface units (ATM-to-Ethernet)

- High performance set-top controller

- ATM25 SAR

Since the 860SAR implements a superset of the ATOM1 microcode, the 860SAR supports ATOM1 features in addition to providing SAR functionality.

## 1.2 Comparison with the MPC860

The 860SAR is pin compatible with the MPC860 and both controllers can be used in identical applications with some small but significant programming changes made to accommodate the controllers' differences. The MPC860 and MPC860SAR have identical electrical and mechanical specifications.

#### 1.2.1 Microcode Changes

A significant part of the 860SAR ATM functionality is implemented by the communications processor (CP) module using certain internal ROM space. In order to make that space available, the DSP library routines (for example, FIR, IIR) have been removed, and therefore the DSP functionality described in the User's Manual for the standard MPC860 is not available in the 860SAR.

#### 1.2.2 Functionality Limitations Due to Internal Resources

#### 1.2.2.1 General Issues

Timer 4 is used by the ATM Pace Controller to periodically activate the APC pace algorithm. Therefore, if ATM is enabled (i.e. PDPAR[ATM]=1), then timer 4 cannot be used for its normal function, but must instead be used as the APC timer.

Also, because of a required setting of the RCCR, IDMA2 can only be used in level-sensitive mode if ATM is enabled.

#### 1.2.2.2 Issues Concerning the UTOPIA Interface

The UTOPIA interface of the MPC860SAR is implemented using the hardware of IDMA1 and the parameter RAM page of SCC4. Therefore, if the UTOPIA port of the 860SAR is used:

- SCC4 is unavailable (due to the loss of parameter RAM page 4)

- IDMA1 is unavailable (due to the loss of handshake signals and event registers)

#### 1.2.2.3 Issues Concerning the ATM Pace Controller (APC)

The MPC860SAR contains an ATM Pace Controller (APC) which is used to automatically multiplex and schedule ATM cells for transmission. Most applications will use the APC, so these limitations will apply to most designs. The APC can be disabled simply by disabling Timer 4. However, if the APC is used, then only the following options are available:

- the UTOPIA port can be used (and SCC4 will be unavailable)

- SCC4 can be used in ATM mode

- SCC4 can be used in transparent mode

- SCC4 can be disabled

SCC1, SCC2, and SCC3 can be used in any mode desired, including ATM.

A detailed explanation of the technical reasons for this is provided in Section 5.4, "Using the APC Without Using SCC4 or UTOPIA".

#### 1.2.3 Functionality Limitations Due to Pin Multiplexing

If the MPC860SAR's UTOPIA interface is used, then several existing pins are used as UTOPIA data and control signals, and therefore some of those pins' alternate functions

become unavailable. Most of the UTOPIA signals are multiplexed with the port D signals.

If the UTOPIA port is used, then:

- IDMA1 is unavailable (due to the loss of the DREQ0 signal).

- Ethernet CAM support for SCC2, SCC3, and SCC4 is unavailable (due to the loss of the REJECT2, REJECT3, and REJECT4 signals)

- Parallel Interface Port (PIP) is unavailable (due to the loss of the PIP handshake signals)

The SCC3 and SCC4 signals on port D are also optionally available on ports A, B, and C. Therefore, SCC3 will be available even if the UTOPIA port is used. SCC4 will still not be available when the UTOPIA port is used, because of the resource conflicts explained above.

#### 1.3 Features

The 860SAR supports the following features:

- Serial ATM capability available on any SCC

- Optional UTOPIA port available (replaces SCC4 if used)

- Cell processing up to 60 Mbps aggregate receive and transmit via UTOPIA interface (with 50 MHz system clock).

- Cell processing up to 20 Mbps aggregate receive and transmit via serial interface (with 50 MHz system clock)

- Memory-to-memory cell processing (via serial interface in loopback)

- Performs transmission convergence (TC) to E1/T1/ADSL serial lines.

- Support of AAL0 and AAL5 protocols on a per virtual circuit (VC) basis.

- AAL0 support allows other AAL types to be handled by software.

- Support for 32 active VCs internally, and up to 64K using external memory.

- Cell multiplexing and demultiplexing.

- Flexible and efficient cell rate pacing; supports CBR and UBR, with easy hook-up to ABR.

- Supports UTOPIA and serial (E1/T1/ADSL) interfaces.

- Compliant with ATMF UNI 4.0 specification.

- CLP and congestion indication marking.

- Separate transmit and receive buffer descriptor (BD) rings for each channel.

- Interrupt report per channel using exception queue.

- Supports 53 byte to 64 byte (expanded) ATM cell size.

- Glueless serial interface to Motorola CopperGold ADSL interface device.

- Supports AAL5 connections:

- Reassembly:

- Reassembles CPCS\_PDU directly to host memory

- CRC32 check

- CPCS\_PDU padding removal

- CS\_UU, CPI, and LENGTH reporting

- CLP and congestion reporting

- Interrupt per buffer or per message

- Report on errors (CRC, length mismatch, message abort)

- Real-time time stamp capability supports connection timeout

#### — Segmentation:

- Segments CPCS\_PDU directly from host memory

- Performs CPCS\_PDU padding.

- CRC32 generation

- Automatic last cell marking (in the PTI field of the cell header)

- Automatic CS\_UU, CPI, and LENGTH insertion (in the last cell)

- Supports AAL0 connections:

- Receive:

- Whole cell is stored in memory (with exception of the HEC).

- CRC10 pass/fail indication

- Interrupt per buffer (cell)

- Transmit:

- Reads a whole cell (with exception of the HEC) from the buffer.

- Optional CRC10 insertion

- PHY:

- UTOPIA provides glueless interface to PHY

- UTOPIA level 1 master (ATM side) with cell-level handshake

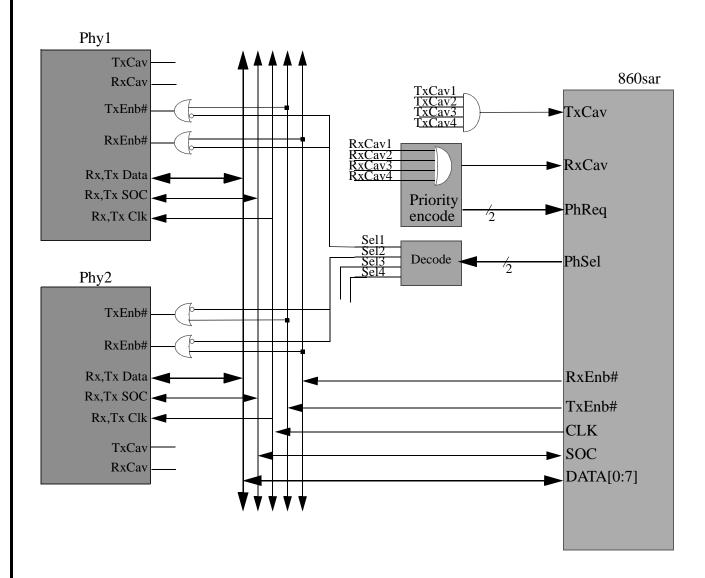

- Supports use of external logic to implement UTOPIA level 2 multi-PHY interface (for up to 4 PHY)

- T1/E1/ADSL serial line

- HEC generation/checking

- Cell delineation

- Cell payload scrambling/de-scrambling option (X<sup>43</sup>+1 polynomial)

- Automatic idle/un-assigned cell insertion/stripping

- Cells with incorrect HEC are marked and counted.

- ATM pace control (APC) unit:

- 2 priority levels

- Constant bit rate (CBR) pacing on a per VC basis

- Unspecified bit rate (UBR) pacing

- Available bit rate (ABR) pacing (pace is managed by the host)

- Receive address look-up supported by three modes of operation:

- Sequential look-up table (for up to 32 channels in internal mode)

- Flexible, user-defined address compression mechanism.

- Content-addressable memory (CAM).

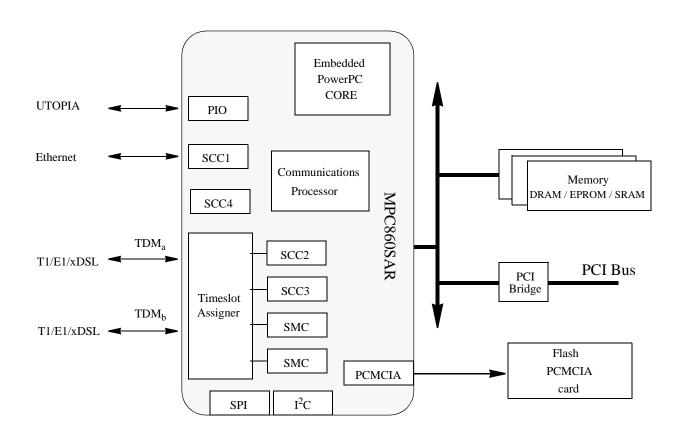

Figure 1-1 shows a typical 860SAR configuration for support of serial and UTOPIA mode ATM transmissions. A description of the 860SAR's serial and UTOPIA mode transmit, receive, and transmission scheduling capabilities for AAL0 and AAL5 cell types is provided in subsequent sections.

Figure 1-1. MPC860SAR Application Example

## 1.4 MPC860SAR and MPC850SAR Comparison

The MPC850SAR is a cost reduced version of the MPC860SAR. There are less SCCs available on the MPC850SAR. The programming model for the MPC850SAR is for the most part identical to the MPC860SAR and therefore most everything in this supplement applies to the MPC850SAR, except:

- SCC4 is not available. However, the parameter RAM page associated with SCC4 is still available in DPR. This parameter RAM page is used by the UTOPIA port.

- The pinout is different. Signal functionality is the same for both parts, but pin multiplexing is different.

The "UTOPIA Interface" chapter of this document contains a table with MPC850SAR pin assignment/definitions. For a complete description of the MPC850 refer to the MPC850 User's Manual.

## 1.5 General Description

The 860SAR's ATM controller supports several ATM sublayers and two interface modes of operation. The interface modes provide a UTOPIA interface and a serial interface. In both modes the ATM controller performs ATM adaptation layer (AAL5 and AAL0), segmentation and reassembly (SAR), and the ATM layer protocol function. In the UTOPIA mode, the ATM layer interfaces the PHY directly through the UTOPIA interface. In serial mode, the ATM controller also implements the transmission convergence (TC) sublayer and interfaces the PHY through its SCCs.

As mentioned above, the PHY interface to the ATM controller is through UTOPIA or a bit stream from the TC layer. The ATM controller also performs the AAL SAR on the user data as it is transmitted and received. The transmitted and received data resides in system memory in single or multiple data buffers.

The following sections describe the transmit and receive mechanisms for the two modes and the functionality of the ATM pace controller (APC), which is common to the two modes. Detailed information for the two modes of operation can be found in Chapter 7, "Interface Configuration." Detailed information about the APC can be found in Chapter 5, "ATM Pace Control." For proper operation of the 860SAR, SCC4 must be included as a channel used for either serial or UTOPIA mode ATM transactions; if only one channel is selected for ATM operations, SCC4 must be the channel configured for use.

#### 1.5.1 ATM Controller UTOPIA Mode

In the UTOPIA mode, the 860SAR handles receive and transmit operations on a cell-by-cell basis. The UTOPIA interface implements cell-level handshake and therefore the supported bit rate is higher than the bit rate accomplished in the serial mode.

#### 1.5.1.1 Transmitter Overview

The transmit process begins with the APC. The APC controls the ATM traffic of the transmitter through a user-configured timer that defines the maximum outgoing bit rate. The APC holds the traffic parameters of each channel and divides the total bit rate amongst the requesting channels. It can provide CBR and UBR traffic services. ABR can also be supported through software manipulation of APC parameters. The task of the APC is to define the next channel (or channels) to be transmitted. Refer to Chapter 5, "ATM Pace Control," for additional information about the operation and programming of the APC.

The APC schedules channels for transmission by inserting the channel number in the transmit queue. If a channel is in the transmit queue and the PHY asserts the transmit cell available (TxCav) signal, the transmitter starts the transmit process. At first, the transmitter takes the first channel number from the transmit queue. The channel number determines

which channel entry is read in the transmit connection table (TCT). The transmitter then checks the status of the specific connection. If there is no open data buffer, it opens a new transmit buffer using the channel's buffer descriptor (BD) list. The APC then copies 48 octets from the external buffer, performs CRC32 for AAL5, copies the cell header from the cell header entry of the TCT, and transmits the whole cell through the UTOPIA interface.

At the last cell of an AAL5 frame, the transmitter appends to the user frame the trailer of the common part conversion sublayer-protocol data unit (CPCS-PDU). It adds pads as required, appends the length (calculated during the frame transmit), and copies the CPCS-UU and CPI from the BD. The transmitter also sets the PTI[1] bit at the header of the last cell of the message. An interrupt is optionally generated to declare the end of transmit frame.

During AAL0 transmissions the ATM controller simply copies the whole cell (except the HEC) prepared by the user from the channel's buffer and transmit it through the UTOPIA interface. Note that the HEC is not generated by the 860SAR in UTOPIA mode. The transmit HEC transferred to the UTOPIA interface is a dummy byte value (set to 0x00), and the PHY is responsible for the calculation of the HEC. The ATM controller can optionally generate CRC10 on the cell payload and place the result at the end of the payload (CRC10 field). This feature is used to support OAM CRC10; refer to ITU specification I.610 for additional details.

If no additional valid buffers are available for the requesting channel in the BD list, the transmit process ends and no cell is transmitted by the 860SAR. It is the responsibility of the PHY to generate an idle cell in an empty cell slot. An empty cell slot is generated every time this channel is scheduled by the APC until a new valid buffer is ready, or a deactivate channel command is issued. See Section 4.3, "MPC860SAR Commands," for additional information about ATM controller commands and syntax.

#### 1.5.1.2 Receiver Overview

The receive process begins when the PHY asserts the receive cell available signal (RxCav), indicating that the PHY has a complete cell in its receive FIFO buffer.

The 860SAR begins processing the cell by receiving the cell header through the UTOPIA interface. The receiver translates the header address (VCI/VPI/PTI) to a channel number through either a look-up table in dual-port RAM, address compression tables in external RAM, or an external content-addressable memory (CAM). A cell header that has no match is treated as an AAL0 cell and is passed to the global raw cell queue (channel 0). If the cell is matched to a channel, the channel status is read from the receive connection table (RCT), and if no open buffer is available a new buffer is opened. The payload (48 octets) is copied to the buffer, the CRC is calculated, and the RCT parameters are updated. If no empty buffers are available for the received channel in the BD list an interrupt is generated and the cell is discarded.

On receipt of an AAL5 end-of-frame marker (indicated by the PTI[1] bit) the receiver separates the trailer of the CPCS-PDU from the user data. The pads are removed as

required, the length field is checked against the length which was calculated during the frame receive, the CPCS-UU and CPI are copied to the BD, and the buffer is closed. An interrupt is optionally generated to declare the end of received frame. If a CRC or length error occurs, it is marked in the BD and an interrupt is generated. AAL5 frames longer than 65535 octets will result in a CRC error and the contents of the "Data Length" field of the BD will contain (length of frame)MODULO(0xffff).

On receipt of an AAL0 cell the ATM controller simply copies the whole cell (with the exception of the HEC) from the UTOPIA interface to the channel's current buffer, and calculates and checks CRC10 on the cell payload. This option is used to support OAM cell check per ITU specification I.610. Note that the received HEC is not checked by the 860SAR in UTOPIA mode. It is the responsibility of the PHY to check the HEC and discard cells with an incorrect HEC.

#### 1.5.2 ATM Controller Serial Mode

The 860SAR's serial controllers operate independently of the physical interface standard used. The physical interface must provide a synchronization signal to define the byte boundary of the receive and transmit data streams to the 860SAR, so that it can deliver and accept byte-aligned data to or from the 860SAR serial interface. This byte synchronization signal is particularly important to the serial receiver, which cannot achieve cell synchronization without it. Generally, one of the 860SAR TDM ports is used in the serial mode to allow easy connection to an E1 or T1 line interface device. However, the use of the other serial interfaces, using either the TDM ports or the NMSI mode of the SCC, is also possible. The operation of the TDM interface using the time slot assigner (TSA) is described in subsequent sections.

While operating in serial mode, the transmit and receive flows are similar to those when operating in UTOPIA mode. In addition to the functionality of the UTOPIA mode, the serial mode provides the transmission convergence (TC) layer which adds cell delineation, scrambling, idle cell generation or screening, and defines the interface characteristics for support of E1/T1 or ADSL line interface devices.

#### 1.5.2.1 Transmitter Overview

The serial transmitting process begins with the APC. The APC controls the ATM traffic of the transmitter through a user-configured timer that defines the maximum outgoing bit rate. The APC holds the traffic parameters of each channel and divides the total bit rate amongst the requesting channels. It can provide CBR and UBR traffic services. ABR can also be supported through software manipulation of APC parameters. The task of the APC is to define the next channel (or channels) to be transmitted. Refer to Chapter 5, "ATM Pace Control," for additional information about the operation and programming of the APC.

When operating in serial mode, transmit requests are generated by an SCC. The transmitter determines the next channel from the transmit queue for the current SCC, reads the channel data from the transmit connection table (TCT), and updates the TCT. The cell is copied to an internal buffer where the CRC32 and HEC are calculated, the cell header is appended,

and scrambling is optionally performed. After the cell assembly process, the cell is moved into the SCC's transmit FIFO for transmission.

The transmitter appends the trailer of the CPCS-PDU in the last cell of an AAL5 user frame. The CPCS-PDU consists of the frame length (which was calculated during the frame transmit), the CPCS-UU and CPI fields from the BD, and cell padding as required. The transmitter also sets the PTI[1] bit in the header of the last cell of the frame. An interrupt can be optionally generated to declare the end of a transmit frame.

When transmitting AAL0 cells the ATM controller simply copies the whole cell (except the HEC) from the channel's cell transmit buffer. The ATM controller optionally generates CRC10 for the cell payload and places the result at the end of the payload. This feature is used to support OAM CRC10 per ITU specification I.610.

In the event of an empty transmit queue or no valid BDs for the requesting channel in the BD list, the transmitter generates an idle or unassigned cell (with the cell contents defined by the user). The transmitter sends idle cells if there are no channel numbers in the transmit queue or if the current channel in the transmit queue has no valid buffers. Channels can be removed from the transmit queue with the deactivate channel command. For additional information about ATM controller commands, refer to Section 4.3, "MPC860SAR Commands."

#### 1.5.2.2 Receiver Overview

The receive process starts after the receiver becomes synchronized with the incoming cells and can perform cell delineation. A receive request is then generated by an SCC. The receiver copies the first word from the serial controller to the dual-port RAM (DPR). The receiver translates the header address (VCI/VPI/PTI) to a channel number through either a look-up table in dual-port RAM, address compression tables in external RAM, or an external content-addressable memory (CAM). If the header has no match the incoming cell is treated as an AAL0 cell, and is passed to the global raw cell queue (channel 0). If the cell is matched to a channel the channel status is read from the receive connection table (RCT). As the FIFO of the serial controller fills, the received cell is read from the FIFO of the serial controller, the HEC is checked, and cell descrambling is optionally performed. Cells with HEC errors are passed to the global raw cell queue, and the HEC error is recorded in the BD. The receiver will screen out either idle cells or unassigned cells, as programmed.

Throughout the cell assembly process, either the entire cell (for AAL0 connections) or the cell payload (for AAL5 connections) is copied to external memory through DMA bursts and the RCT is updated. If there are no empty buffers for the received channel in the BD list, an interrupt is generated and the cell is discarded.

CRC32 is checked on the cell payload for AAL5 connections, with pass/fail indication provided in the last BD of the received CPCS\_PDU. The end of an AAL5 frame is indicated by the PTI[1] bit in the received cell header. When an end-of-frame indication occurs the receiver separates the trailer of the CPCS-PDU from the user data. The length field is compared against the length calculated during the frame receive operation, the pads are

removed as required, the CPCS-UU and CPI are copied to the BD, and the receive buffer is closed. An interrupt can be optionally generated to declare the end of a receive frame. Detected CRC or length errors are marked in the BD and an interrupt is generated. AAL5 frames longer than 65535 octets will result in a CRC error and the contents of the "Data Length" field of the BD will contain (length of frame)MODULO(0xffff).

When AAL0 cells are received the ATM controller simply copies the whole cell from the serial controller without the HEC to the next receive buffer in the channel's BD list. The ATM controller calculates and checks CRC10 on the cell payload. This option supports the OAM cell check per ITU specification I.610.

#### 1.5.2.3 Cell Delineation

In serial mode cell delineation is part of the receiver flow control. The user must provide synchronization signals to the 860SAR and octet-align incoming cells to the synchronization signals. The ATM controller provides SDH/PDH oriented cell delineation on an octet basis using the HEC mechanism defined in ITU specification I.432. Note that when using E1 and T1 ATM links, the cells are always octet-aligned (refer to ITU specification G.804) and synchronization signals are provided by the E1 and T1 interface devices.

When cell reception commences, the ATM controller takes a short while to acquire correct cell delineation. Once the ATM controller has locked to the incoming cell stream, it remains locked unless there are excessive errors. A status bit indicates the current delineation status, and an interrupt is generated whenever the cell lock status changes. Cells received before the cell delineation process has completed will be stored in the global raw cell queue.

#### 1.5.2.4 Cell Payload Scrambling

Cell payload scrambling is optionally performed in both transmit flow (scrambling) and receive flow (descrambling) using the  $X^{43}+1$  scrambling algorithm. The first cell transmitted following initialization is not correctly scrambled because there is no valid data in the 43-bit delay line. The ATM controller always transmits an empty cell first thereby avoiding data corruption. On cell reception, the descrambling algorithm self-synchronizes before the HEC delineation process is complete and cell reception begins.

#### 1.5.3 Extended Channel Mode

In extended mode the number of connections supported by the ATM controller is increased from 32 transmit and receive channels up to 65,535 transmit and receive channels. When extended mode is invoked the TCT and RCT structures greater than 31 are placed in the external memory and a CAM or address compression method is used for VCI/VPI/PTI mapping instead of an internal look-up table. In this case parameters for "internal" channels (channels with an internal TCT and RCT; channels 0 through 31) are directly accessed in the dual-port RAM, and "external" channels (channels with TCTs and RCTs located in external memory) require DMA accesses to read and update the external TCT and RCT.

The bit rate supported by the extended mode is reduced and throughput depends on the number of external channels and the bit rate ratio between external and internal channels.

#### 1.5.4 ATM Pace Control (APC)

The ATM pace controller determines the next channel (or *n* channels) to be transmitted and writes the channel number of these channels in the transmit queue every APC slot time. The transmitter transmits one cell for each channel entry in the transmit queue. The APC is controlled by the communications processor (CP) through a cyclic table (APC table) in the dual-port RAM that is used to schedule transmission of all the active channels.

The operation of the APC is controlled by several input parameters programmed by the user. Scheduling of traffic is controlled through the APC table length, the number of cells to be selected in an APC slot time, and the APC request timer. The period of the APC request timer determines the length of an APC slot time. The APC uses the APC\_period parameter in the TCT to schedule the channel in the APC table.

The APC may optionally handle two APC tables. The first table is serviced with high priority and the second is serviced with a lower priority; thus, channels from the second table are scheduled on a bit rate availability basis. This capability is used for channels with higher cell delay variation (CDV) tolerance and for UBR traffic.

The APC\_period for CBR traffic is set by the user prior to the activation command, and CBR transmissions are scheduled through the high-priority table. The APC\_period for UBR transmissions is also constant, and is scheduled in the low-priority table. The APC\_period of ABR transmissions is adjusted by the host in response to RM cell reception and defines the ABR available cell rate (ACR). The APC period can be changed on-the-fly, thereby allowing the bit rate for a channel to be changed dynamically, as is necessary to control transmission of traffic types such as ABR. For ABR, it is the user's responsibility to evaluate resource management (RM) cells and update the APC\_period entry in the TCT.

The APC input parameters are described in Chapter 5, "ATM Pace Control." These parameters define the minimum and maximum cell rate and cell delay variation.

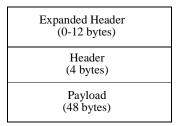

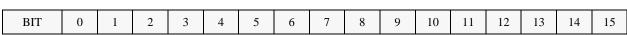

#### 1.5.5 Expanded Cells

Typical ATM cells are 53 bytes long, consisting of a header (4 bytes), HEC (1 byte) and payload (48 bytes). The 860SAR also supports cells up to 64 bytes in length (referred to as expanded cells) that use extra header fields for internal information in switch applications. Expanded cells consist of an expanded header of 0 to 3 words (0, 4, 8, or 12 bytes), a cell header (4 bytes), and a payload (48 bytes); the HEC is not included as error checking is not required within a switch. Expanded cells are available only when operating in UTOPIA mode. Figure 1-2 shows the structure of an expanded cell.

Figure 1-2. Expanded Cell Structure

During transmit operations, the expanded header of each cell is taken from the expanded field in the BD and transmitted ahead of the cell header and payload. During receive operations the expanded header of the last cell of the current connection is copied to the expanded field in the receiver's BD.

# Chapter 2 Buffer Descriptor Structures and Connection Tables

The 860SAR's communication processor module (CPM) manages ATM traffic through the UTOPIA and serial interfaces by means of transmit and receive buffer descriptor (BD) structures and transmit and receive connection tables (referred to as TCTs and RCTs, respectively). Buffer descriptors are circular lists of pointers into transmit and receive buffer space in external memory. The following sections describe the organization and configuration of the buffer descriptors, TCTs, and RCTs.

## 2.1 Buffer Descriptors (BD)

ATM SAR operates as a multi-channel protocol, segmenting and reassembling each channel's transmit and receive data to and from different sets of memory buffers simultaneously. This behavior makes it necessary to have a separate list of BDs for each channel. The method implemented by the 860SAR ATM controller is based on the traditional 860 buffering methodology, with the difference that there are multiple BD lists which are located in the external memory. Each channel is configured with two BD lists for transmit and receive operations. The number of BDs according to channel and the size of the buffers is defined by the user. This method allows the 860SAR to perform segmentation and reassembly directly to the user memory and to better use available memory space. The 860SAR accesses BDs in list order. The BD list is a cyclic list; when the 860SAR reaches the last BD it returns to the head of the list.

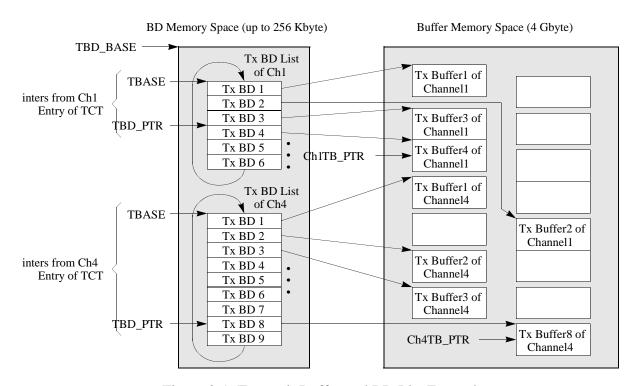

Figure 2-1 shows an example of the transmitter BD lists and buffers and the pointers associated with them. In this example there are two transmit channels; channel 1 and channel 4. Each transmitting channel has a transmit BD list and an entry in the TCT where the BD pointers are placed (TBASE, TBD\_PTR, and TB\_PTR). TBDBASE and RBDBASE are the base addresses of the BD external memory spaces and are placed in the parameter RAM to identify separate blocks of memory for the receive and transmit BDs. TBASE holds the address offset from TBDBASE of the starting BD of a given channel. In this example, the first transmit BD of channel 1 is located at the address specified by TBD\_BASE plus the offset specified by channel 1's TBASE. The TBD\_PTR is an offset pointer inside a BD list specifying the current active BD.

In the example shown in Figure 2-1, when channel 1 receives a transmit request then a cell is transmitted from buffer 4 in its transmit BD list using TB\_PTR of channel 1 as a pointer to the cell data. The transmitter advances the TB\_PTR to point to the next cell data every time it transmits a cell for channel 1. When the end of a transmit buffer is reached, the transmitter advances the TBD\_PTR to the next BD in the list and continues to transmit if the BD is valid. If the end of the BD list is reached, the transmitter returns to the head of the list by setting TBD\_PTR to the TBASE address of the channel.

Figure 2-1. Transmit Buffer and BD List Example

#### 2.1.1 AAL5 Buffers

The buffers used by the 860SAR may reside in either internal or external memory. Each buffer can hold a whole CPCS-PDU message or part of it. The buffers used by the 860SAR transmitter are accessed in BD list order; if more than one buffer for a message is used, all the BDs for the buffers should be in consecutive order in the BD list. The last buffer of a message is padded automatically by the 860SAR transmitter to fit an AAL5 cell payload according to ITU specification I.363. The transmit buffer data length for AAL5 transmit buffers must be greater than or equal to 48 bytes for all buffers except the first and last buffer of a CPCS-PDU; the first and last buffers of a CPCS-PDU must have a data length greater than zero. Note that AAL5 transmit buffers have no alignment restrictions.

Receive buffers can also hold either a whole CPCS-PDU message or part of it. Receive buffers must start on a burst-aligned address (divisible by 16) and their lengths can be any multiple of 48 bytes (that is, the value of SMRBLR in parameter RAM must equal N x 48, where N is an integer.) The receive BDs are used in order and in multiples of 48 bytes, except for the last buffer in a message from which the AAL5 pads are removed.

During transmit or receive operations, interrupts are optionally generated at the end of each BD or the end of an AAL5 CPCS-PDU.

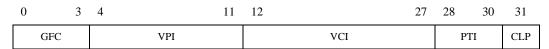

#### 2.1.2 AAL0 Buffers

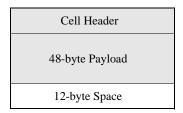

During AAL0 operations each buffer contains one raw cell. When the receiver or transmitter completes writing or reading the buffer, it moves to the next buffer in the list and optionally issues an interrupt. The placement of an AAL0 cell in a buffer is shown in Figure 2-2.

Figure 2-2. AAL0 Buffer Structure

An AAL0 buffer size is 64 bytes. 52 bytes of this buffer are used to hold cell header and payload; the HEC is not included in the receive or transmit buffers. The remaining 12 bytes of the buffer are not used by the 860SAR and are available to the user. Unlike other protocols, both the AAL0 transmit and receive buffers must start on a burst-aligned address (divisible by 16).

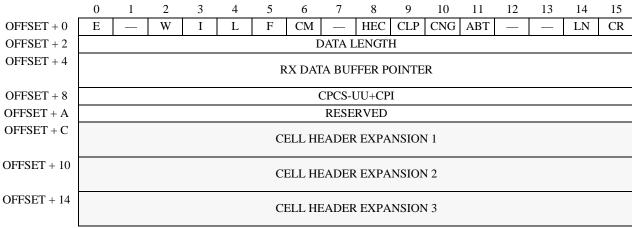

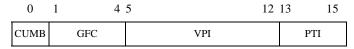

#### 2.1.3 Receive Buffer Descriptor

The format of the receive buffer descriptor is applicable to both SAR UTOPIA and serial modes. The buffer descriptors are 12 bytes long in standard (53-byte) cell mode and 24 bytes long in expanded cell mode. In standard cell mode, the cell header expansion fields do not exist, and the buffer descriptor occupies a 12-byte region of memory, with the next buffer descriptor following immediately after it. Figure 2-3 describes the contents and memory locations of a receive buffer descriptor in expanded cell mode.

Note: Entries in boldface must be initialized by the user.

Figure 2-3. Receive Buffer Descriptor

I

Table 2-1 describes the control and status bits in a receive buffer descriptor.

#### Table 2-1. Receive Buffer Descriptor Field Descriptions

| Offset from RBD_PTR | Bits | Name | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|---------------------|------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x00                | 0    | Е    | Empty. Determines whether a buffer is accessible by the CPU core or the CP.  O The data buffer associated with this receive BD has been filled with the received data, or data reception has been aborted due to an error condition. The CPU core is free to examine or write to any fields of this receive BD. The CP will not access a BD while the E-bit is cleared to zero.  The data buffer associated with this RxBD is empty, or reception is currently in progress. This receive BD and its associated receive buffer are in use by the CP. Once the E bit is set, the CPU core should not write any fields of this receive BD. |

|                     | 1    | _    | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                     | 2    | W    | Wrap. Determines that this is the final BD in table.  O This is not the last BD in the receive BD list of the current channel.  This is the last BD in the receive BD list of this current channel. After this buffer has been used, the CP will receive incoming data for this channel into the first BD in the list (the BD pointed to by the channels's RCT[RBASE] address). The number of receive BDs in this table is programmable and is determined only by the W bit and the overall space constraints of 256K memory space for all the receive channels.                                                                        |

|                     | 3    | I    | Interrupt. Enables RXB interrupts when a receive buffer is closed during receipt of an AAL5 frame or an AAL0 buffer. Note that RXF interrupts are not effected by this bit.  O No interrupt is generated after this buffer has been used.  Interrupt occurs after this buffer has been closed by the ATM controller while processing an AAL5 frame. This class of interrupt is indicated through the setting of the RXB bit in an entry in the exception queue. The GINT bit in the ISDR or SCCE is set according to the INT_CNT counter value set in the parameter RAM.                                                                |

|                     | 4    | L    | Last in frame. Set by the ATM controller when this buffer is the last in a frame. This implies the end of the CPCS-PDU by channels that implement AAL5, or reception of an error, in which case one or more error bits are set. The ATM controller writes the number of frame octets to the data length field.  0 The buffer is not the last in a frame.  1 The buffer is the last in a frame.                                                                                                                                                                                                                                          |

|                     | 5    | F    | First in frame. Set by the ATM controller when this buffer is the first in a frame. This bit is reserved in AAL0 BDs.  O The buffer is not the first in a frame.  1 The buffer is the first in a frame.                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                     | 6    | СМ   | Continuous mode. Determines whether the buffer associated with this BD is continuously marked as empty.  O Normal operation  The E bit is not cleared by the CP after this BD is closed, allowing the associated data buffer to be automatically overwritten the next time the CP accesses this BD.                                                                                                                                                                                                                                                                                                                                     |

|                     | 7    |      | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

Table 2-1. Receive Buffer Descriptor Field Descriptions (Continued)

| Offset from RBD_PTR | Bits  | Name                           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------------------|-------|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x00                | 8     | HEC                            | HEC error. A receiver HEC error occurred on at least one cell of the frame. Cells with HEC errors are passed to the global raw cell queue with this bit set.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                     | 9     | CLP                            | Cell loss priority. Indicates that at least one cell was received with CLP bit set. This bit is set in the last BD in the frame by the 860SAR for channels that implement AAL5. For channels that implement AAL0, this bit is not valid. The CLP bit can be found in the cell header (first word) of the AAL0 received data buffer.                                                                                                                                                                                                                                                                                                                                                                                               |

|                     | 10    | CNG                            | Congestion indication. Indicates that the last cell in the frame was received with PTI congestion bit set. This bit is set in the last BD of the frame by the 860SAR for channels that implement AAL5. For channels that implement AAL0, this bit is copied from the PTI bit in the header of the received cell.                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                     | 11    | ABT                            | Abort. Indicates that a frame abort was detected (last cell in frame indicated zero frame length.) This error bit is set in the last BD of the aborted frame by the 860SAR for channels that implement AAL5.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                     | 12–13 | _                              | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                     | 14    | LN                             | Receive length error. The number of octets received in the frame does not match the length specified in the length field of the AAL5 CPCS-PDU. This bit is set in the last BD of the frame by the 860SAR for channels that implement AAL5. Note that the whole received PDU is written to the data buffer even if a receive length error is detected.                                                                                                                                                                                                                                                                                                                                                                             |

|                     | 15    | CR                             | Receive CRC error. This bit indicates a CRC32 error for AAL5 channels or a CRC10 error for AAL0 channels. The receiver performs CRC32 checking on the CPCS-PDU for AAL5 channels and sets the CR bit in the last BD when a CRC error is detected. On AAL0 channels, the receiver performs CRC10 checking on the cell payload. It will set the CR bit if a CRC error is detected.  O No error  Indicates CRC32 error for AAL5 channel and CRC10 failure for AAL0 channel. Note: CRC10 checking is performed for all AAL0 channels. The CR bit is set when the received cell includes a CRC10 field in the cell payload and an error is detected. This check is provided to support OAM CRC10 according to ITU specification I.610. |

| 0x02                | _     | Data length                    | Data length. For AAL5 BDs, the data length is the number of octets written by the CP into the BD's data buffer. When the BD is the last BD in the frame (indicated by the BD[L] bit set to 1), the data length contains the total number of frame octets. This field is written by the CP as the buffer is closed. For AAL0 BDs the data length field is reserved.  Note: The amount of memory allocated for all the receive buffers should be greater than or equal to the memory size specified in the SMRBLR field in parameter RAM.                                                                                                                                                                                           |

| 0x04                | _     | Receive data<br>buffer pointer | Receive data buffer pointer. The receive buffer pointer always points to the first location of the data buffer, which may reside in either internal or external memory. This pointer is specified by the host process, and must be burst aligned (divisible by 16).                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 0x08                | _     | CPCS-UU<br>and CPI             | CPCS-UU and CPI. This field contains the CPCS-UU and CPI fields received from the SAR. This field is transferred from the CPCS-PDU trailer, and contains user-to-user (UU) information and common part indications (CPI). This field is written by the 860SAR and is valid only when the BD is the last BD in the frame, and is applicable only to AAL5 channels.                                                                                                                                                                                                                                                                                                                                                                 |

I

I

Table 2-1. Receive Buffer Descriptor Field Descriptions (Continued)

| Offset from RBD_PTR | Bits | Name                                    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------------------|------|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x0C                |      | Cell header<br>expansion 1,<br>2, and 3 | Cell header expansion 1, 2, and 3. These fields are added to the BD when expanded cells are enabled by the user (SRSTATE[EC] bit is set in parameter RAM). When expanded cell headers are enabled and the last BD of an AAL5 frame is closed, the 860SAR copies the expanded cell header into this field; cell header expansion 1 is the first word to be received, cell header expansion 3 is the last word to be received. When expanded cell headers are enabled for AAL0 channels, the expanded cell headers will be copied into these fields for every receive BD. The bytes are ordered according to the DMA byte ordering (programmed through the SRFCR field in the parameter RAM). If the ECSIZE field in the parameter RAM is set to a value less than 3, the cell header expansion fields are populated with the number of words specified in ECSIZE. |

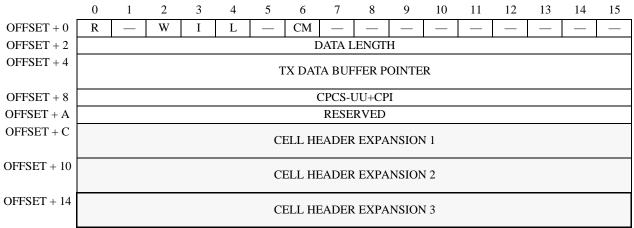

#### 2.1.4 Transmit Buffer Descriptor

Data is prepared for transmission by the ATM controller by arranging it in buffers referenced by the channel's transmit BD list. The ATM controller confirms transmission or indicates error conditions using the BDs to inform the host that the buffers have been serviced. The format of the transmit buffer descriptor is applicable for both SAR UTOPIA and serial modes. The buffer descriptors are 12 bytes long in standard (53-byte) cell mode and 24 bytes long in expanded cell mode. In standard cell mode, the cell header expansion fields do not exist, and the buffer descriptor occupies a 12-byte region of memory, with the next buffer descriptor following immediately after it. Figure 2-4 describes the contents and memory locations of a transmit buffer descriptor.

Note: Entries in boldface must be initialized by the user.

Figure 2-4. Transmit Buffer Descriptor

I

Table 2-2 provides a description of the control and status bits in a transmit buffer descriptor.

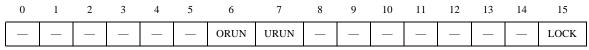

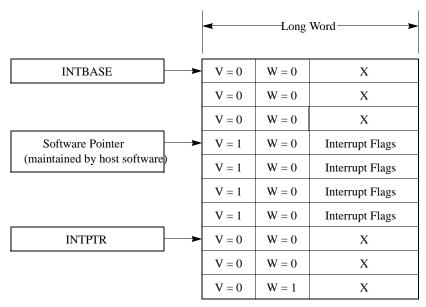

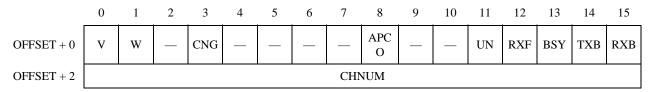

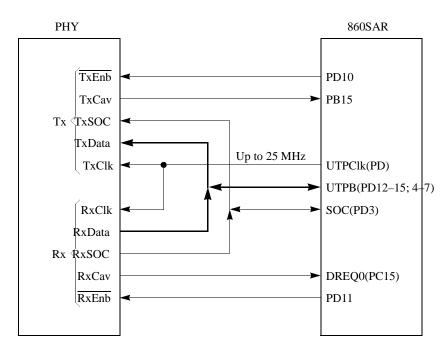

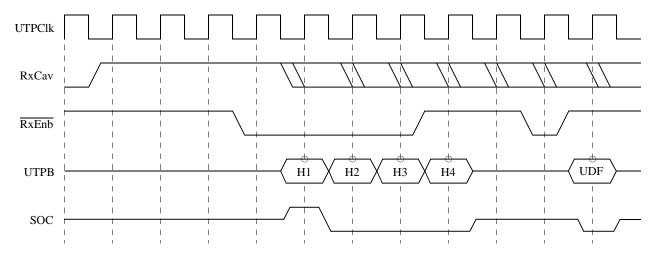

#### Table 2-2. Transmit Buffer Descriptor Field Descriptions