## ATOM1 :

## MC68360 ATM Microcode

## **User's Manual**

#### **Document Reference:**

| Version | Comments                                 | Release date      |

|---------|------------------------------------------|-------------------|

| 0.1     | First Release                            | 18th Aug., 1994   |

| 0.2     | Updated User's Manual                    | 1st Nov., 1994    |

| 1.0     | Updated for CRC-32 and buffer scattering | 21st. March, 1996 |

|         |                                          |                   |

|         |                                          |                   |

Motorola reserves the right to make changes without further notice to any product herein to improve reliability, function, or design. Motorola does not assume any liability arising out of the application or use of any product, circuit, or software described herein; neither does it convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support life, or for any other application in which the failure of the Motorola products for any such intended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and the Motorola logo\* are registered trademarks of Motorola.

-----

ATOM1 User's Manual 1.0

-1-

. ....

. . .

. . .

# **TABLE OF CONTENTS**

| 1.             | INTRODUCTION                                                          | . 5 |

|----------------|-----------------------------------------------------------------------|-----|

| 1.1.           | Key Features of ATOM1                                                 | . 5 |

| 1.2.           | MC68360 SCCs                                                          |     |

| 1.3.           | Conventions                                                           |     |

|                |                                                                       |     |

| 2.             | ATOM1 OPERATION                                                       | . 7 |

| 2.1.           | Number of Connections                                                 |     |

| 2.2.           | Cell Delineation                                                      |     |

| 2.3.           | AAL Frame Check Sequences                                             |     |

| 2.4.           | PDH & SDH Physical Layer Signalling & OAM Functions                   |     |

| 2.5.           | Traffic Control                                                       |     |

| 2.6.           | Physical Interface                                                    |     |

| 2.7.           | Buffer Descriptor and Buffer Structures                               |     |

| 2.1.           | Durier Descriptor and Durier Structures                               | . 0 |

| 3.             | REGISTERS                                                             | 9   |

| 3.1.           | General Registers                                                     |     |

| 3.1.1.         | RISC Controller Configuration Register (RCCR)                         |     |

| 3.1.2.         | CP Control Registers                                                  |     |

| 3.1.2.         | SCC Registers                                                         |     |

| 3.2.<br>3.2.1. | General SCC Mode Register (GSMR)                                      |     |

|                | $\mathbf{c}$                                                          |     |

| 3.2.2.         | Protocol Specific Mode Register (PSMR)                                |     |

| 3.2.3.         | SCC Event Register (SCCE)                                             |     |

| 3.2.4.         | SCC Mask Register (SCCM)                                              | 11  |

| 3.2.5.         | SCC Status Register (SCCS)                                            |     |

| 3.3.           | Serial Interface                                                      |     |

| 3.3.1.         | Serial Interface Registers                                            |     |

| 3.3.2.         | Serial Interface RAM                                                  |     |

| 3.4.           | Parallel Port Registers                                               | 13  |

|                |                                                                       |     |

| 4.             | ATOM1 SCC PARAMETER RAM                                               |     |

| 4.0.1.         | BD Queue Pointers (RBASE and TBASE)                                   |     |

| 4.0.2.         | SCC Function Code Registers (RFCR and TFCR)                           |     |

| 4.0.3.         | Transparent Mode Receive Maximum Buffer Length (MRBLR)                |     |

| 4.0.4.         | SCC Internal State Parameters (RSTATE and TSTATE)                     | 15  |

| 4.0.5.         | BD and Buffer Pointers (R_PTR, RBD_PTR, T_PTR and TBD_PTR)            |     |

| 4.0.6.         | Transmit and Receive Buffer Queue Start Pointers (TX_BUFF1, RX_BUFF1) |     |

| 4.0.7.         | Buffer Counters (R_CNT and T_CNT)                                     |     |

| 4.0.8.         | Receiver Delineation Counters (ALPHA and DELTA)                       |     |

| 4.0.9.         | Version Number (AVERSION)                                             |     |

| 4.0.10         |                                                                       |     |

| 4.0.11         | . Empty Cell Data (EHEAD and EPAYLOAD)                                | 16  |

| 4.0.12         | . Status Information (ASTATUS)                                        | 17  |

| 4.0.13         |                                                                       | 17  |

| 4.0.14         |                                                                       |     |

| 4.0.15         |                                                                       |     |

| 4.0.16         |                                                                       |     |

| . 18         |

|--------------|

| . 19         |

| . 19         |

|              |

| . 21         |

| . 21<br>. 22 |

| . 22         |

| . 24         |

|              |

| . 25         |

| 27           |

| . 27         |

| . 27         |

| . 29         |

| . 29         |

| 20           |

| . 30         |

| . 30         |

|              |

| . 31         |

| . 31         |

| . 51         |

|              |

| . 32         |

| . 32         |

| . 33         |

| . 33         |

|              |

| . 36         |

|              |

# LIST OF TABLES

| Table 1.  | CP Control Registers                             |    |

|-----------|--------------------------------------------------|----|

| Table 2.  | MC68360 Serial Interface Programming Example     |    |

| Table 3.  | Serial Interface RAM Programming Example         |    |

| Table 4.  | ATOM1 TDM A Port Pin Requirements                |    |

| Table 5.  | MC68360 Port Register Programming                |    |

| Table 6.  | ATOM1 SCC Parameter RAM Memory Map               |    |

| Table 7.  | ATOM1 CRC-32 Calculator Parameter RAM Memory Map |    |

| Table 8.  | ATOM1 Performance                                |    |

| Table 9.  | ATOM1 and other Protocol Performance             | 28 |

| Table 10. | CRC-32 Calculator Performance                    | 29 |

|           |                                                  |    |

# **LIST OF FIGURES**

| Figure 1.  | Typical ATOM1 Application System           | . 6 |

|------------|--------------------------------------------|-----|

| Figure 2.  | ATOM1 RCCR                                 |     |

| Figure 3.  | ATOM1 PSMR                                 | 10  |

| Figure 4.  | ATOM1 SCCE                                 | 11  |

| Figure 5.  | ASTATUS                                    | 17  |

| Figure 6.  | HEADMASK                                   | 18  |

| Figure 7.  | HEADn                                      | 18  |

| Figure 8.  | ATOM1 Transmit Buffer and BD Queue Example | 21  |

| Figure 9.  | ATOM1 Receive Buffer Descriptor            | 22  |

| Figure 10. | ATOM1 Transmit Buffer Descriptor           | 23  |

| Figure 11. | Transmit Buffer                            | 24  |

| Figure 12. | Mixed Voice and Data Transmission Example  | 25  |

| Figure 13. | ATOM1 CAM Interface                        | 26  |

| Figure 14. | ATOM1 Disk Structure                       | 30  |

| Figure 15. | ATOM1 Transmitter Procedure                | 32  |

| Figure 16. | ATM Cell Payload Scrambling Mechanism      | 33  |

| Figure 17. | ATOM1 Receiver Procedure                   | 34  |

| Figure 18. | Cell Delineation State Diagram             | 35  |

## ATOM1

# **Asynchronous Transfer Mode Microcode for the QUICC**

# 1. INTRODUCTION

ATOM1 is an MC68360 RAM-based microcode that provides physical layer ATM functions by converting one or more of the QUICC's serial communication controllers (SCCs) into an ATM cell transmitter and receiver. ATOM1 provides the user with cell streaming facilities (cell reception and transmission) and event indications. The user can add AAL functions to ATOM1 using software.

The primary application of ATOM1 is intended to be G.804 plesiochronous digital hierarchy (PDH) and synchronous digital hierarchy (SDH) E1 and DS1 ATM equipment. Such equipment is used for signalling and low rate data transfer and may be part of the telecommunications infrastructure or terminal equipment.

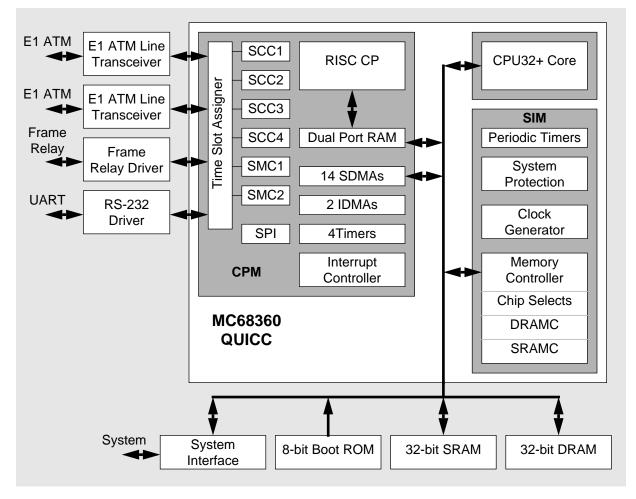

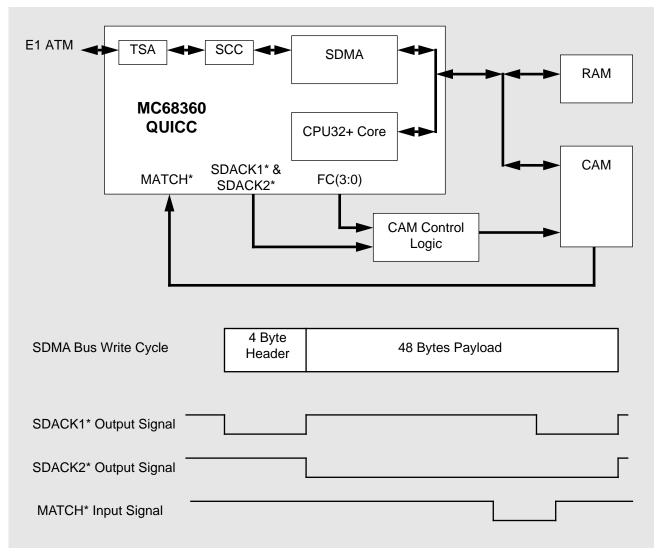

Figure 1 shows an ATM communications module built around the QUICC running an ATOM1 microcode. This module could be a board within a larger system or part of a larger ATM board. The ATOM1 microcode runs on the QUICC's RISC communications processor (CP) and is stored in the dual port RAM. The user interface to ATOM1 is through buffer descriptors located in the QUICC's dual port RAM and data buffers located in external memory. The QUICC's CPU32+ controls the module and memory using the on-chip memory controller and other integration features.

## **1.1. Key Features of ATOM1**

The key features of ATOM1 are:

- Cell transmission and reception for all AAL protocols.

- Handles serial data rates up to 8 Mbps with a 25 MHz QUICC and up to 11 Mbps with a 33 MHz QUICC.

- Any or all of the QUICC's SCCs can simultaneously handle ATM cells.

- Transmit and receive data buffers located in main memory.

- On transmission, ATOM1 constructs the cell header and appends the user defined payload.

- Bandwidth reservation option in the transmit queue to allow mixing of data and isochronous services.

- On reception, ATOM1 verifies incoming cell headers and strips the HEC before passing the cell to the user.

- Automatic empty cell transmission when there are no pending data transfers.

- Receiver filters and discards empty cells and those with non-matching addresses.

- CAM support on reception for handling many connections.

- User controlled cell scrambling option.

- Incoming cells with incorrect HECs are received and marked as such.

- A CRC-32 calculator is available to reduce processor performance requirements when

handling AAL5 cells.

Standard QUICC features are available when ATOM1 is running.

Figure 1. Typical ATOM1 Application System

### 1.2. MC68360 SCCs

ATOM1 can operate on any MC68360 SCC and can simultaneously operate on any two, three or all four SCCs. To maintain the performance of ATOM1, it is recommended that the highest speed connection operates on SCC1 and the lowest speed connection on SCC4.

ATOM1 uses the SCC in transparent mode with microcode performing ATM cell functions. When ATOM1 is loaded and RAM microcode is enabled, transparent mode operation is available on any SCC other than ones running ATOM1.

#### **1.3.** Conventions

The reader is assumed to be familiar with the QUICC and ATM. For further information about the QUICC, please refer to the MC68360 User's Manual. Full details of the ATM protocols can be found in the relevant ITU-T recommendations and the ATM Forum UNI document listed at the end of this manual.

In this manual, the term "user" is used to describe the CPU software that drives ATOM1. In the MC68360 this may be the CPU32+ or an external CPU.

# 2. ATOM1 OPERATION

ATOM1 transmits and receives 53-byte ATM cells as defined in the ATM Forum UNI specification (ATOM1 also handles NNI cells). Cells are transmitted from a single queue and the user has full control over each cell's GFC, VPI, VCI, PT, CLP and payload fields. ATOM1 generates and inserts the cell HEC field on transmission and checks and strips it on reception. An option is included to apply the HEC coset pattern (binary 01010101) to transmitted and received cells.

ATOM1 performs cell rate adaptation to the capacity of the transmission link by the inserting empty cells when no cells are queued by the user. On reception, ATOM1 ignores empty cells. The user can define the empty cell to be either an unassigned or idle cell.

Received cells with HEC errors are received and marked as such. The HEC is passed to the user to allow user software to implement HEC correction algorithms as required. ATOM1 does not attempt to correct any HEC errors.

ATOM1 provides an option to scramble data on transmission and receive scrambled data using the  $X^{43}$ +1 scrambling algorithm. The first cell to be transmitted by ATOM1 after initialisation will not be correctly scrambled because there is no valid data in the 43-bit delay line. ATOM1 always transmits an empty cell first therefore avoiding data corruption. On reception, the descrambling algorithm self-synchronises before the HEC delineation process is complete and cell reception begins.

## 2.1. Number of Connections

ATOM1 transmits one cell at a time on the virtual connection specified for that cell. The user can transmit ATM cells with the whole range of the cell's address field (VCI and VPI combined).

ATOM1 receives cells after matching the cell header with a header look-up table or an external CAM. The internal look-up table has up to 16 entries and cell headers can have bits masked before the comparison.

The user must maintain enough open channels to receive OAM and signalling cells. User software must handle OAM and signalling cells.

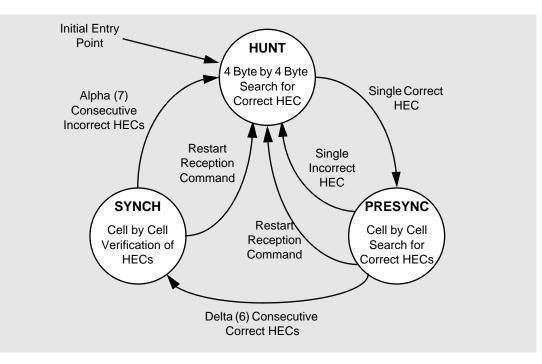

## 2.2. Cell Delineation

The user must provide synchronisation signals to the QUICC and octet-align incoming cells to the synchronisation signals. ATOM1 provide SDH/PDH oriented cell delineation using the HEC mechanism defined in I.432 on an octet basis. The synchronisation signals need not delimit the start of cell but must be octet aligned with incoming cells. When using E1 and T1 ATM links, the cells are always octet aligned (see ITU G.804) and synchronisation signals are provided by the E1 and T1 interface devices.

ATOM1 User's Manual 1.0

When reception commences, ATOM1 takes a short while to acquire correct cell delineation. Once ATOM1 has locked to the incoming cell stream, it remains locked unless there are excessive errors. An interrupt is generated whenever the cell lock status changes and a status bit will indicate the current delineation status.

Further details of the cell delineation mechanism are given in Appendix A.

## 2.3. AAL Frame Check Sequences

To increase software throughput of AAL5 frames, a CRC-32 calculator is included. This is not an integral part of the cell transmission and reception process in order that CRC-32 sequences may be calculated across long AAL5 frames made up of interleaved ATM cells. The CRC-32 calculator is a command which ATOM1 interprets by working through a data buffer generating the required CRC-32 sequence.

## 2.4. PDH & SDH Physical Layer Signalling & OAM Functions

PDH and SDH framing physical layer signalling and OAM functions are not provided by ATOM1 but the user can handle these by routing the PDH/SDH OAM, signalling and overhead timeslots to one of the QUICC's SMCs or another SCC.

## 2.5. Traffic Control

ATOM1 transmits cells from it's single transmission queue in the order that they are presented. It is the user's responsibility to apply traffic management techniques to avoid congestion and breaking the UPC rules if the connection data rate is less than the transmit bit rate. Failure to apply these techniques may result in bursty traffic on open connections.

When ATOM1's transmit queue is empty, ATOM1 will automatically transmit empty cells.

## 2.6. Physical Interface

The ATOM1 microcode is independent of the physical interface standard used. Generally, one of the QUICC's TDM ports will be used with ATOM1 to allow easy connection to an E1 or T1 line interface device. Other serial interfaces are not precluded and may be selected when programming the MC68360 serial interface. This User's Manual describes the TDM interface using the Time Slot Assigner (TSA).

## 2.7. Buffer Descriptor and Buffer Structures

ATOM1 uses an optimized version of the standard MC68360 data buffer and buffer descriptor (BD) structures. The ATOM1 structures are better suited to handling numerous small data buffers as is required in ATM. The BDs are just two bytes long instead of the normal eight byte BDs and buffers are fixed length. Data buffers are scattered in receive and transmit buffer memory areas, each 16K bytes, located anywhere in the processor's memory map.

## 3. **REGISTERS**

ATOM1 requires several general MC68360 and SCC registers to be configured for operation and reports status in SCC registers.

## **3.1.** General Registers

All the MC68360 general registers (SIM, memory controller, chip select, SDMA, etc.) must be configured as described in the MC68360 User's Manual with the exception of the CP Control Registers and RISC Controller Configuration Register. Interrupts are generated by ATOM1 and the MC68360 interrupt controller must be configured by the user (see the MC68360 User's Manual, section 7.15 for details).

#### **3.1.1. RISC** Controller Configuration Register (RCCR)

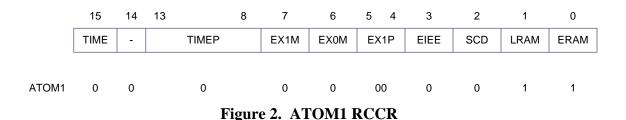

The MC68360's RCCR controls microcode operation. To run ATOM1, the RCCR should be set as shown in Figure 2. Further details are given in the MC68360 User's Manual, section 7.1.1.

Setting RCCR bit 0 enables RAM microcode operation and this should not be done until ATOM1 and the MC68360 are initialized.

Note: the RISC timers are unavailable when ATOM1 is running and the TIME and TIMEP bits must be cleared in the RCCR.

#### **3.1.2.** CP Control Registers

The user must configure CP Control registers as shown in Table 1. Note, the value programmed into CPCR4 depends on the QUICC device version used.

| Address    | Name  | Description           | User Writes (hex)                                                    |

|------------|-------|-----------------------|----------------------------------------------------------------------|

| REGB+\$5CC | CPCR1 | CP Control Register 1 | 8056                                                                 |

| REGB+\$5CE | CPCR2 | CP Control Register 2 | 8076                                                                 |

| REGB+\$5D0 | CPCR3 | CP Control Register 3 | 8036                                                                 |

| REGB+\$5D2 | CPCR4 | CP Control Register 4 | 8E18 rev B1 MC68360<br>8818 rev B2, B3, B4, C0,<br>C1 and E MC68360s |

| Fable 1: | CP | Control | Registers |

|----------|----|---------|-----------|

|----------|----|---------|-----------|

#### **3.2.** SCC Registers

ATOM1 operates using an SCC and is enabled in the SCC's General SCC Mode Register (GSMR). The clock source is configured in the serial interface registers (see section 3.3.1).

#### 3.2.1. General SCC Mode Register (GSMR)

ATOM1 requires the following bits to be set in the GSMR: TRX, TTX, CDP, CTSP, CDS and CTSS. To enable ATOM1's transmit and receive functions, the ENT and ENR bits must be set when the initialisation sequence has been completed. Full GSMR details are given in the MC68360 User's Manual, section 7.10.2.

Additionally, the REVD bit in the GSMR (bit 45) changes function to become the CAM control bit when ATOM1 is running:

- CAM 0 Use the internal address table for address matching.

- 1 Use the external CAM for address matching.

To enable an SCC to run ATOM1, the SCC must be in transparent mode and have MRBLR = 0. When MRBLR is programmed with a non-zero value, the SCC operates in transparent mode. Mixed mode operation of an SCC (where the transmitter runs ATOM1 and the receiver is in transparent mode or vice versa) running ATOM1 is not allowed.

When ATOM1 is loaded and running, the maximum serial performance of an SCC in transparent mode is reduced very slightly.

#### **3.2.2.** Protocol Specific Mode Register (PSMR)

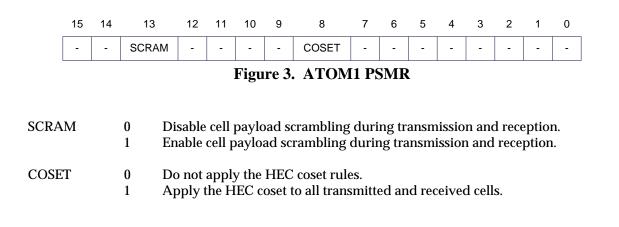

The SCC Protocol Specific Mode Register (PSMR) controls various SCC functions that are protocol specific. Before enabling ATOM1, the user should initialize the PSMR. The PSMR should only be written when the transmitter and receiver are disabled, otherwise erratic behaviour could result.

For ATOM1, the PSMR is used to control the scrambling and HEC coset functions of both the transmitter and receiver (see Figure 3).

ATOM1 User's Manual 1.0

-10-

#### **3.2.3.** SCC Event Register (SCCE)

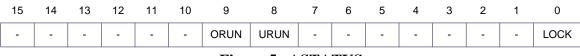

The SCC event register (SCCE) contains status bits for events recognized by ATOM1 and the SCC circuitry. Whenever a bit is set in the SCCE, an interrupt to the user is generated unless the corresponding bit in the SCC Mask register (SCCM) is set. All bits in the SCCE are sticky bits: they are set by the SCC hardware or ATOM1 and must be reset by the user writing a one.

Bits 15-8 are set by the SCC hardware and some unused bits may be set. The user should mask interrupts from all unused bits in the SCCM. Bits 7-0 are set by ATOM1 to indicate events that it has detected (see Figure 4).

| 15 | 14 | 13 | 12  | 11  | 10  | 9 | 8 | 7   | 6    | 5    | 4   | 3   | 2   | 1  | 0  |

|----|----|----|-----|-----|-----|---|---|-----|------|------|-----|-----|-----|----|----|

| -  | -  | -  | GLR | GLT | DCC | - | - | NMA | SYNC | FIFO | HEC | OAM | BSY | ТΧ | RX |

Figure 4. ATOM1 SCCE

- RX A cell has been received and a receive buffer used. This bit is set on completion of reception.

- TX A cell has been transmitted and a transmit buffer used.

- BSY A cell was received and discarded due to lack of receive buffers.

- OAM A control cell (OAM or reserved for future use as indicated by the PT field) been received and a receive buffer used. This bit is set on completion of reception. When this bit is set, the RX bit is also set but about 10 system clocks later.

- HEC A cell has been received with a HEC error. This bit is also set when the SYNC bit is set. The HEC bit is set as soon as a HEC error is detected it does not wait until the complete cell is received.

- FIFO A transmit FIFO underrun or receive FIFO overrun error has occurred. See ASTATUS for the exact status.

- SYNC ATOM1 has lost or gained cell delineation.

- NMA ATOM1 received a cell with a non-matching address.

- DCC The carrier sense status as generated by the DPLL has changed. See description of the Transparent Mode SCCE in the MC68360 User's Manual, section 7.10.21.11.

- GLT A clock glitch was detected by the SCC on the transmit clock. See description of the Transparent Mode SCCE in the MC68360 User's Manual, section 7.10.21.11.

- GLR A clock glitch was detected by the SCC on the receive clock. See description of the Transparent Mode SCCE in the MC68360 User's Manual, section 7.10.21.11.

#### 3.2.4. SCC Mask Register (SCCM)

The SCCM has the same bit definitions as the SCCE and allows the user to mask interrupts. Further details are given in the MC68360 User's Manual, section 7.10.8.2.

#### 3.2.5. SCC Status Register (SCCS)

The function of the SCCS register is unchanged when ATOM1 uses an SCC.

## **3.3.** Serial Interface

ATOM1 may use the MC68360's serial interface (SI) in any mode although the time division multiplex mode to allows easy connection to E1 and T1 line interface devices. This section of the User's Manual concentrates on the TDM interface although use of other serial interfaces is not precluded.

It is the user's responsibility to ensure that incoming cells are octet aligned with the SI handshake or synchronisation pulses. ATOM1 will then apply the cell HEC delineation mechanism correctly and synchronise with the incoming cell stream.

ATOM1 can use either of the MC68360 TDM ports. Programming information is given here for use of TDM A and can easily be converted for TDM B. Further information about the SI is given in the MC68360 User's Manual, section 7.8.

#### **3.3.1.** Serial Interface Registers

The SI registers SIMODE, SIGMR and SICR should be programmed for the required interface standard and the user must configure the SI RAM pointer (SIRP) as required in the system. An example of programming the SI registers for connection to a line interface device with common transmit and receive clocks is shown in Table 2. In this example, ATOM1 is running on SCC1.

Note: the timeslot assigner TSA must not be enabled in SIGMR until the SI RAM and other registers have been configured.

|        | Register                              | User Writes (hex) |

|--------|---------------------------------------|-------------------|

| SIMODE | Serial Interface Mode Register        | 0000 0058         |

| SIGMR  | Serial Interface Global Mode Register | 04                |

| SICR   | Serial Interface Clock Route Register | 0000 0040         |

#### Table 2: MC68360 Serial Interface Programming Example

#### **3.3.2.** Serial Interface RAM

ATOM1 can use the MC68360 TSA with independent receiver and transmitter routing RAM tables. An example of programming these two tables for back-to-back ATM cell transmission and reception is given in Table 3. TDM A is used and data is routed to SCC1. Other SCCs and TDM B may be used. For debug purposes, all four SI strobes are asserted during various timeslots: L1ST1 during cell header transmission, L1ST2 on HEC transmission, L1ST3 during cell header reception and L1ST4 on HEC reception.

| SI RAM Entry | User Writes (hex) | Strobe Asserted | Remarks                                     |

|--------------|-------------------|-----------------|---------------------------------------------|

| Rx A 0       | 104E              | L1ST3           | Receive four bytes of cell header           |

| Rx A 1       | 2042              | L1ST4           | Receive one byte HEC field                  |

| Rx A 2       | 007E              | -               | Receive first sixteen bytes of cell payload |

Table 3: Serial Interface RAM Programming Example

ATOM1 User's Manual 1.0

| SI RAM Entry | User Writes (hex) | Strobe Asserted | Remarks                                       |

|--------------|-------------------|-----------------|-----------------------------------------------|

| Rx A 3       | 007E              | -               | Receive second sixteen bytes of cell payload  |

| Rx A 4       | 007F              | -               | Receive final sixteen bytes of cell payload   |

| Tx A 0       | 044E              | L1ST1           | Transmit four bytes of cell header            |

| Tx A 1       | 0842              | L1ST2           | Transmit one byte HEC field                   |

| Tx A 2       | 007E              | -               | Transmit first sixteen bytes of cell payload  |

| Tx A 3       | 007E              | -               | Transmit second sixteen bytes of cell payload |

| Tx A 4       | 007F              | -               | Transmit final sixteen bytes of cell payload  |

Table 3: Serial Interface RAM Programming Example

### **3.4.** Parallel Port Registers

For ATOM1 operation over TDM A, the MC68360 parallel port pins should be set up to interface to external signals as shown in Table 4. The TSA strobes and SDMA Acknowledge pins are shown and common receive and transmit clocks are used.

| Signal   | Pin  | Direction |

|----------|------|-----------|

| L1TXDA   | PA6  | Output    |

| L1RXDA   | PA7  | Input     |

| L1RSYNCA | PC11 | Input     |

| L1RCLKA  | PA8  | Input     |

| L1ST1    | PB12 | Output    |

| L1ST2    | PB13 | Output    |

| L1ST3    | PB14 | Output    |

| L1ST4    | PB15 | Output    |

| SDACK1*  | PC10 | Output    |

| SDACK2*  | PC8  | Output    |

Table 4: ATOM1 TDM A Port Pin Requirements

To achieve this, Table 5 shows an example of how the port registers may be programmed.

|       | Register                          | User Writes (hex) |

|-------|-----------------------------------|-------------------|

| PIPC  | PIP Configuration Register        | 0000              |

| PADIR | Port A Data Direction Register    | 00C0              |

| PAPAR | Port A Pin Assignment Register    | 01C0              |

| PAODR | Port A Open Drain Register        | 0000              |

| PBDIR | Port B Data Direction Register    | 0000 0000         |

| PBPAR | Port B Pin Assignment Register    | 0000 F000         |

| PBODR | Port B Open Drain Register        | 0000              |

| PCDIR | Port C Data Direction Register    | 0500              |

| PCPAR | Port C Pin Assignment Register    | 0D00              |

| PCSO  | Port C Special Option Register    | 0000              |

| PCINT | Port C Interrupt Control Register | 0000              |

Table 5: MC68360 Port Register Programming

ATOM1 User's Manual 1.0

# 4. ATOM1 SCC PARAMETER RAM

When ATOM1 operates on a particular SCC, the SCC parameter RAM memory map is that shown in Table 6. The user must initialize the parameter RAM with the values given after reset or when re-initializing ATOM1.

| Address Name  |              | Width | Description                                               | User Writes (hex)         |  |  |

|---------------|--------------|-------|-----------------------------------------------------------|---------------------------|--|--|

| SCC Base + 00 | RBASE        | Word  | Receive BD Base Address                                   | UD                        |  |  |

| SCC Base + 02 | TBASE        | Word  | Transmit BD Base Address                                  | UD                        |  |  |

| SCC Base + 04 | RFCR         | Byte  | Receive Function Code                                     | UD                        |  |  |

| SCC Base + 05 | TFCR         | Byte  | Transmit Function Code                                    | UD                        |  |  |

| SCC Base + 06 | MRBLR        | Word  | Transparent Rx Max Buffer Length                          | 0000                      |  |  |

| SCC Base + 08 | RSTATE       | Long  | Receiver Internal State                                   | use init rx/tx<br>command |  |  |

| SCC Base + 0C | R_PTR        | Long  | Receiver Internal Data Pointer                            | -                         |  |  |

| SCC Base + 10 | RBD_PTR      | Word  | Receive BD Pointer                                        | use init rx/tx<br>command |  |  |

| SCC Base + 12 | R_CNT        | Word  | Receive Internal Byte Counter                             | -                         |  |  |

| SCC Base + 14 | RTEMP        | Long  | Receiver Temporary Data Storage                           | -                         |  |  |

| SCC Base + 18 | TSTATE       | Long  | Transmitter Internal State                                | use init rx/tx<br>command |  |  |

| SCC Base + 1C | T_PTR        | Long  | Transmit Internal Data Pointer                            | -                         |  |  |

| SCC Base + 20 | TBD_PTR      | Word  | Transmit BD Pointer                                       | use init rx/tx<br>command |  |  |

| SCC Base + 22 | T_CNT        | Word  | Transmit Internal Byte Counter                            | -                         |  |  |

| SCC Base + 24 | TTEMP        | Long  | Transmitter Temporary Data Storage                        | -                         |  |  |

| SCC Base + 28 | ALPHA        | Word  | Receiver Delineation Alpha Counter                        | -                         |  |  |

| SCC Base + 2A | DELTA        | Word  | Receiver Delineation Delta Counter                        | -                         |  |  |

| SCC Base + 2C | AVERSION     | Word  | ATOM1 Version Number                                      | -                         |  |  |

| SCC Base + 2E | CAM_PORT     | Word  | CAM Port B Mask                                           | -                         |  |  |

| SCC Base + 30 | RX_BUFF1     | Long  | Receive Buffer Area Start Address                         | UD                        |  |  |

| SCC Base + 34 | TX_BUFF1     | Long  | Transmit Buffer Area Start Address                        | UD                        |  |  |

| SCC Base + 38 | EHEAD        | Long  | Empty Cell Header<br>(little endian byte format)          | 0000 0000<br>or 0100 0000 |  |  |

| SCC Base + 3C | EPAYLOAD     | Long  | Empty Cell Payload<br>(little endian byte format)         | 6A6A 6A6A                 |  |  |

| SCC Base + 40 | RSTUFF       | Long  | Receive Data Stuffing Location (53 to 52 byte conversion) | -                         |  |  |

| SCC Base + 44 | SHUFFLESTATE | Word  | Receiver Data Shuffling State                             | 0000                      |  |  |

| SCC Base + 46 | RHECTEMP     | Word  | Temporary HEC Storage                                     | -                         |  |  |

| SCC Base + 48 | THECTEMP     | Word  | Temporary HEC storage area                                | -                         |  |  |

| SCC Base + 4A | ASTATUS      | Word  | ATOM1 status word                                         | 0000                      |  |  |

| SCC Base + 4C | NMA_HEAD     | Long  | Non-Matching Address Cell Header                          | -                         |  |  |

| SCC Base + 50 | NMA_CNT      | Word  | Non-Matching Address Cell Counter                         | 0000                      |  |  |

| SCC Base + 52 | HEC_ERR      | Word  | HEC Error Counter                                         | 0000                      |  |  |

Table 6: ATOM1 SCC Parameter RAM Memory Map

ATOM1 User's Manual 1.0

| _ | _ |              | _ |   |

|---|---|--------------|---|---|

|   |   | $\mathbf{V}$ |   |   |

|   |   |              |   |   |

|   |   |              |   | _ |

|   |   |              |   |   |

| Address       | Name     | Width | Description                        | User Writes (hex) |

|---------------|----------|-------|------------------------------------|-------------------|

| SCC Base + 54 | RSCRAM   | Long  | Receiver Scrambling Storage        | -                 |

| SCC Base + 58 | RSCRAM1  | Long  | Receiver Scrambling Storage        | -                 |

| SCC Base + 5C | TSCRAM   | Long  | Transmitter Scrambling Storage     | -                 |

| SCC Base + 60 | TSCRAM1  | Long  |                                    | -                 |

| SCC Base + 64 | HEADMASK | Long  | Cell Header Comparison Mask        | UD                |

| SCC Base + 68 | HEAD1    | Long  | Cell Header Look-Up Table Entry 1  | UD                |

| SCC Base + 6C | HEAD2    | Long  | Cell Header Look-Up Table Entry 2  | UD                |

| SCC Base + 70 | HEAD3    | Long  | Cell Header Look-Up Table Entry 3  | UD                |

| SCC Base + 74 | HEAD4    | Long  | Cell Header Look-Up Table Entry 4  | UD                |

| SCC Base + 78 | HEAD5    | Long  | Cell Header Look-Up Table Entry 5  | UD                |

| SCC Base + 7C | HEAD6    | Long  | Cell Header Look-Up Table Entry 6  | UD                |

| SCC Base + 80 | HEAD7    | Long  | Cell Header Look-Up Table Entry 7  | UD                |

| SCC Base + 84 | HEAD8    | Long  | Cell Header Look-Up Table Entry 8  | UD                |

| SCC Base + 88 | HEAD9    | Long  | Cell Header Look-Up Table Entry 9  | UD                |

| SCC Base + 8C | HEAD10   | Long  | Cell Header Look-Up Table Entry 10 | UD                |

| SCC Base + 90 | HEAD11   | Long  | Cell Header Look-Up Table Entry 11 | UD                |

| SCC Base + 94 | HEAD12   | Long  | Cell Header Look-Up Table Entry 12 | UD                |

| SCC Base + 98 | HEAD13   | Long  | Cell Header Look-Up Table Entry 13 | UD                |

| SCC Base + 9C | HEAD14   | Long  | Cell Header Look-Up Table Entry 14 | UD                |

| SCC Base + A0 | HEAD15   | Long  | Cell Header Look-Up Table Entry 15 | UD                |

| SCC Base + A4 | HEAD16   | Long  | Cell Header Look-Up Table Entry 16 | UD                |

UD = User Defined

#### Table 6: ATOM1 SCC Parameter RAM Memory Map

#### 4.0.1. BD Queue Pointers (RBASE and TBASE)

The user configures RBASE and TBASE to define the starting location of the receive and transmit BD queues in the dual-port RAM. Further information is given in the MC68360 User's Manual, section 7.10.7.1.

#### 4.0.2. SCC Function Code Registers (RFCR and TFCR)

The user configures RFCR and TFCR to define the SDMA function code pin settings during SDMA transfers. Further information is given in the MC68360 User's Manual, section 7.10.7.2.

#### 4.0.3. Transparent Mode Receive Maximum Buffer Length (MRBLR)

To run ATOM1 on an SCC, the user must program that SCC's MRBLR to zero. When MRBLR is programmed with a non-zero value, the SCC operates in transparent mode as described in the MC68360 User's Manual, section 7.10.21.

#### 4.0.4. SCC Internal State Parameters (RSTATE and TSTATE)

ATOM1 uses RSTATE and TSTATE to store internal state variables and flags during operation. The user must not write to these locations.

#### 4.0.5. BD and Buffer Pointers (R\_PTR, RBD\_PTR, T\_PTR and TBD\_PTR)

During cell transmission and reception, ATOM1 uses R\_PTR, RBD\_PTR, T\_PTR and TBD\_PTR as pointers to the current BD and data locations. RBD\_PTR and TBD\_PTR point to the current or next BD to use and need to be initialized with the Init Rx/Tx command to point to the locations given in RBASE and TBASE. R\_PTR, and T\_PTR point to the next data location in memory. When ATOM1 is operating, these locations should not be written by the user. Further information is given in the MC68360 User's Manual, sections 7.10.7.4 and 7.10.7.5.

#### 4.0.6. Transmit and Receive Buffer Queue Start Pointers (TX\_BUFF1, RX\_BUFF1)

The user configures TX\_BUFF1 and RX\_BUFF1 to define the starting location of the transmit and receive buffer areas in main memory. This is the starting address of the 16K byte areas where transmit and receive buffers reside. TX\_BUFF1 and RX\_BUFF1 must be long-word aligned addresses (bits 0 and 1 must be zero).

TX\_BUFF1 and RX\_BUFF1 can be dynamically changed provided that care is taken to synchronise the buffer queues held in user software and the queues that the QUICC's CP sees. The CPM reads TX\_BUFF1 and RX\_BUFF1 every time that it opens a data buffer so it is advised that the transmit and receive queues are allowed to empty before TX\_BUFF1 and RX\_BUFF1 are changed.

#### 4.0.7. Buffer Counters (R\_CNT and T\_CNT)

During ATM cell transmission and reception, ATOM1 uses R\_CNT and T\_CNT to count the number of bytes transmitter or received. The user must not write to these locations.

#### 4.0.8. Receiver Delineation Counters (ALPHA and DELTA)

ATOM1 applies the HEC delineation mechanism described in I.432 with Alpha=7 and Delta=6 to locate and maintain cell synchronisation. During reception, ATOM1 updates the ALPHA and DELTA parameter locations and the user must not write to these locations. There is no need to initialise these locations.

#### 4.0.9. Version Number (AVERSION)

During operation, ATOM1 writes a version number to AVERSION. The current version number stored in AVERSION is \$0001.

#### 4.0.10. CAM Port Selection (CAM\_PORT)

When the CAM interface is enabled, the user should set one or more bits in CAM\_PORT to select which of the QUICC's Port B pins is the match input or inputs for this SCC. Bit 0 of CAM\_PORT corresponds to PB0, bit 1 to PB1, etc.

#### 4.0.11. Empty Cell Data (EHEAD and EPAYLOAD)

ATOM1 transmits and receives empty cells using EHEAD and EPAYLOAD. On transmission, an empty cell is made up by transmitting EHEAD once, calculating and transmitting a HEC and transmitting EPAYLOAD twelve times. On reception, the incoming header is compared with EHEAD to check for empty cells and EPAYLOAD is not used.

The user is free to select whatever empty cell header and payload values are required: the ATM Forum UNI Specification states that unassigned cells should be transmitted while the ITU mandates use of idle cells.

#### 4.0.12. Status Information (ASTATUS)

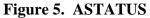

The ATOM1 Status parameter provides the user with additional status information concerning FIFO errors and receiver synchronisation status. ASTATUS is shown in Figure 5.

Bits in the upper byte is set by ATOM1 and cleared by the user. Bits in the lower byte are set and cleared by ATOM1. During initialisation, the user must clear all bits in ASTATUS. During operation, the user can read and clear (write zero) to the upper byte but must only read the lower byte.

FIFO overruns and underruns are reported in the SCCE FIFO bit and further information is given in the ORUN and URUN bits:

| ORUN | 0<br>1 | No Receiver FIFO Overrun.<br>Receiver FIFO Overrun.         |

|------|--------|-------------------------------------------------------------|

| URUN | 0<br>1 | No transmitter FIFO underrun.<br>Transmitter FIFO underrun. |

Each change in state of the receiver cell delineation is reported in the SCCE SYNC bit. The LOCK bit shows the current delineation status:

| LOCK | 0 | The ATOM1 receiver is out of synchronisation and is not receiving cells. |

|------|---|--------------------------------------------------------------------------|

|      | 1 | The ATOM1 receiver has gained cell delineation and is receiving cells.   |

#### 4.0.13. Non-Matching Header Storage and Counter (NMA\_HEAD and NMA\_CNT)

When a cell is received with a non-matching header, the header (minus the HEC) is written to NMA\_HEAD, NMA\_CNT is incremented and the NMA bit set in the SCCE. NMA\_HEAD is a location where headers from non-matching cells are logged and NMA\_CNT is a counter of non-matching cells. The user is free to read and clear NMA\_CNT at any time.

#### 4.0.14. HEC Error Counter (HEC\_ERR)

HEC\_ERR is a 16-bit counter of incoming cells with HEC errors. The user is free to read and clear HEC\_ERR at any time.

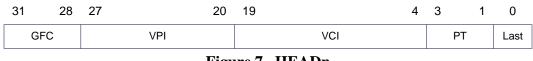

#### 4.0.15. Incoming Header Mask and Look-up Table (HEADMASK and HEADn)

When the CAM option is disabled, ATOM1 masks the header of each incoming cell with HEADMASK and then searches for the result in the HEADn table. When a match is found, the cell is received otherwise the cell header is logged in NMA\_HEAD and the remainder of the cell is discarded.

The HEADMASK masking process uses a bitwise AND function so bits can be masked out by clearing the relevant bit in HEADMASK. The bit locations for HEADMASK are shown in Figure 6. Bit 0 must always be written with zero.

| 31 28 | 27 20 | 19 4 | 3  | 1 0 |

|-------|-------|------|----|-----|

| GFC   | VPI   | VCI  | PT | 0   |

Figure 6. HEADMASK

The result of the masking is then compared with each of the HEADn values, starting with HEAD1. Although sixteen locations are shown in the HEADn table, the user may define fewer. The final location in the table is denoted with the Last bit being set. When multiple HEADn locations are being used, the user should take care because the look-up table can overlap other peripheral areas in memory (see the MC68360 User's Manual section 3.2 for further details). If the look-up table is extended to overlap other peripheral's parameter RAM areas, the other peripherals cannot be used.

The bit locations for the HEADn locations are shown in Figure 7. Bit 0 should be written with zero except for the last entry in the table.

Figure 7. HEADn

ATOM1 searches the HEADn table sequentially so the headers for the most frequently connections should be at the beginning of the table.

#### 4.0.16. Temporary Data Storage

During ATM cell transmission and reception, ATOM1 uses RTEMP, TTEMP, RSTUFF, RHECTEMP, THECTEMP, RSCRAM, RSCRAM1, TSCRAM and TSCRAM1 to store temporary data. This data is for internal use and the user must not write to these locations.

# 5. ATOM1 COMMANDS

The following commands are understood by ATOM1:

- Initialise Receiver and Transmitter Parameters

- Initialise Receiver Parameters

**Initialise Transmitter Parameters**

- Stop Transmit

- Restart Transmit

- Restart Reception

- CRC-32 Calculator

Execution of other SCC commands may cause errant behaviour. All commands are given through the Command Register and operate as with other protocols except Restart Reception.

The ATOM1 commands to initialise the receiver and transmitter parameters operate the same as for other SCC protocols. If the initialisation commands are given during cell transmission and reception, cell synchronisation will be lost.

The Stop Transmit Command stops cell transmission immediately and the transmit line goes high. To stop transmission of data cells but continue with empty cells, the user must wait for the transmit BD queue to empty.

The commands are run by writing the command and channel number to the QUICC's Command Register (CR). The op-codes for the initialisation, Stop Transmit and Restart Transmit command are the same as for the QUICC's other protocols. The op-code for the Restart Reception command is and the CRC-32 calculator 1111. All other bits in the CR remain unchanged.

Command execution latency for the initialisation, Stop Transmit and Restart Transmit command are the same as for the QUICC's other protocols. The Restart Reception command is executed when the current cell being received is complete and execution time therefore depends on the data rate and when the command is given. For all commands, ATOM1 clears the FLG bit in the CR to indicate completion of the command.

### 5.1. Restart Reception Command

The Restart Reception Command is similar to Enter Hunt Mode. If ATOM1 is currently receiving an empty cell, cell delineation is immediately lost and the resynchronisation process begins. If the current cell being received is a data or control cell (being received or discarded by ATOM1), the current buffer is closed and cell delineation is lost at the end of the cell. The Enter Hunt Mode command should not be used with ATOM1.

To restart the receiver immediately regardless of the current state, the Init Rx Parameter command can be used.

The Restart Reception Command and the CRC-32 Calculator share the same op-code in the command register. To issue a Restart Reception Command, the user must ensure that the current CRC-32 calculation is complete and the CRC\_CNT parameter is zero.

## 5.2. CRC-32 Calculator

The CRC-32 Calculator command calculates the 32-bit CRC sequence used in AAL5 frames on a data buffer defined by a pointer and length. Multiple buffers may be strung together by the

ATOM1 User's Manual 1.0 -19- No Re

user to calculate the CRC-32 value over a large AAL5 frame made up of multiple CRC-32 buffers. ITU I.363 gives more details and examples of AAL5 CRC calculations.

Note: The QUICC's CP runs the ATOM1 CRC-32 calculator as its lowest priority task. High traffic throughput on the SCCs and other CP activity will adversely affect the CRC-32 calculator's performance.

The ATOM1 CRC-32 calculator replaces four parameters in QUICC's RISC Timer Parameter RAM area (starting at DPRBASE + \$DB0) as shown in Table 7. The user must initialize the CRC-32 parameter RAM with the values given after reset or when re-initializing ATOM1.

| Address         | Name       | Width | Description                             | User Writes (hex) |

|-----------------|------------|-------|-----------------------------------------|-------------------|

| DPRBASE + \$DB0 | CRC_PTR    | Long  | CRC-32 Calculator Pointer               | UD                |

| DPRBASE + \$DB4 | CRC_CNT    | Word  | CRC-32 Calculator Counter               | UD                |

| DPRBASE + \$DB6 | CRC_FC     | Byte  | CRC-32 Calculator Function Code         | UD                |

| DPRBASE + \$DB8 | CRC_RESULT | Long  | CRC-32 Calculator Seed Value and Result | 0000 0000 or UD   |

UD = User Defined

#### Table 7: ATOM1 CRC-32 Calculator Parameter RAM Memory Map

To start a CRC-32 calculation, the CRC\_PTR, CRC\_CNT, CRC\_RESULT and CRC\_FC parameters must be initialised to give the start address of the data block for the calculation, block length, starting CRC-32 seed and function code. ATOM1 reads and writes these four parameters during a CRC-32 calculation so they must not be altered by the user while the calculation is in progress.

The CRC\_PTR may be programmed with any address that corresponds to the start of the CRC-32 buffer in memory. The length of the buffer must be programmed into the CRC\_CNT parameter. If CRC\_CNT is zero at the start of the command, ATOM1 will run a Restart Reception command rather than the CRC-32 calculator.

The CRC\_RESULT parameter must be preset to zero at the start of a new CRC-32 calculation. On completion of the calculation, CRC\_RESULT holds the resulting 32-bit CRC value. At the beginning of a CRC-32 calculation, CRC\_RESULT may be programmed with the result of a previous CRC-32 calculation if buffers are being strung together.

The user configures CRC\_FC to define the SDMA function code pin settings when the SDMA reads the CRC-32 buffer. Further information is given in the MC68360 User's Manual, section 7.10.7.2.

A CRC-32 calculation is started by writing \$0F01 to the command register. When the command has been accepted and CRC-32 processing begins, ATOM1 clears the FLG bit in the command register. Processing continues through the whole CRC-32 buffer and when the calculation is complete, ATOM1 sets bit 15 in the RISC Timer Even Register (RTER). This can be used to generate a processor interrupt by programming the QUICC's interrupt controller. Bit 15 of the RTER should be cleared before a CRC-32 calculation is started.

# 6. **BUFFER DESCRIPTORS & BUFFERS**

ATOM1 uses a modified version of the standard MC68360 BD and buffer data structure better suited to the high number of and small size of ATM cells. There is a single transmit BD queue and a single receive queue. Associated with each BD queue is a buffer queue. All ATOM1 BDs are two bytes long and buffers are all 52 bytes long. These BD and buffer sizes maximise the number of BDs that can be located in the QUICC's dual port RAM when the ATOM1 microcode is also present and running.

The BDs are a subset of the standard QUICC BDs containing only a 16-bit status and control word. Buffer length and pointer fields are not implemented as for other QUICC serial protocols. BDs are located in the QUICC's dual port RAM.

All data buffers have a fixed length of 52 bytes and are located within 16K byte buffer areas in memory. Receive BD1 is associated with buffer 1, receive BD2 with buffer 2, etc. Transmit and receive buffers are scattered within a 16K byte memory area and use an eleven bit pointer within the transmit BD to locate the buffer exactly. The transmitter and receiver each use different 16K byte buffer areas which may be located anywhere in memory.

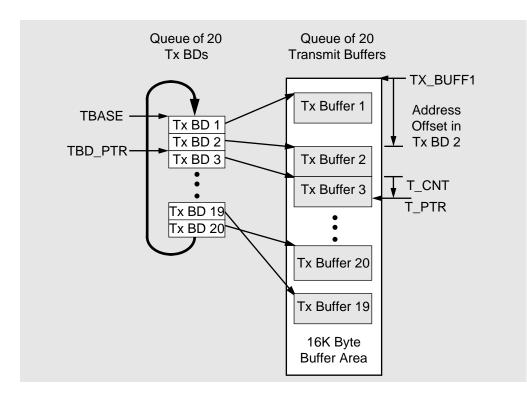

## 6.1. ATOM1 Buffer Descriptor and Buffer Queues

Figure 8 shows an example of the transmitter BD and data buffer queues and the pointers associated with them. In this example, there are 20 BDs, each linked to a buffer. TBASE points to the start of the BD queue and TX\_BUFF1 points to the start of the buffer area. ATOM1 calculates the exact start address of a transmit buffer by adding TX\_BUFF1 to the address field in the transmit BD. Buffers may thus be scattered randomly throughout the 16K byte area.

Figure 8. ATOM1 Transmit Buffer and BD Queue Example

ATOM1 User's Manual 1.0

In this example, the first two buffers have been transmitted and ATOM1 has advanced the TBD\_PTR pointer to point at the current BD. Similarly, the T\_PTR pointer has been advanced to point to the current data being transmitted by ATOM1. T\_CNT is the offset of T\_PTR from the start of the data buffer. When the end of the BD queue is reached, TBD\_PTR is wrapped back by loading it from TBASE. Receive BD and buffer queues follow the same structure as shown here for transmission.

## 6.2. Receive Buffer Descriptor and Data Buffer

Receive BDs are two bytes long as shown in Figure 9. Each BD is linked to one buffer that can hold a received ATM cell. Receive buffers may be scattered around a 16K byte area of memory but each buffer must start on a long word aligned address. If the start address of a buffer is at the very end of the 16K byte area (for example, the BD is programmed with \$8FFF) then the end of the received cell will be 48 bytes outside of the 16K byte area.

When the user prepares an empty receive BD, the address pointer to the start of the data buffer must be written into the BD. When the Empty bit is set, ownership if the BD is handed over from the user to the QUICC's CP and the user must not modify any part of the BD. Once a cell is received and ATOM1 returns the BD and buffer to the user, the address pointer field is replaced with OAM and error status flags and the HEC of the incoming cell. User software must maintain a copy of the address pointer for each receive BD in the receive queue.

| 15 | 14 | 13 | 12 | 11  | 10  | 9   | 8   | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|----|----|----|----|-----|-----|-----|-----|----|----|----|----|----|----|----|----|

| E  | -  | w  | I  | A13 | A12 | A11 | A10 | A9 | A8 | A7 | A6 | A5 | A4 | A3 | A2 |

|    |    |    |    |     |     |     |     |    |    |    |    |    |    |    |    |

Empty Receive BD as Written by User

| E | - | W | I | - | - | OAM | ERR | HEC |

|---|---|---|---|---|---|-----|-----|-----|

|   |   |   |   |   |   |     |     |     |

Used Receive BD after reception of a Cell

Figure 9. ATOM1 Receive Buffer Descriptor

| Ε      | Empty     | Control bit set by the user to indicate that the associated buffer is empty and ATOM1 can receive a cell into it.               |

|--------|-----------|---------------------------------------------------------------------------------------------------------------------------------|

| W      | Wrap      | Control bit set by the user to wrap the receive BD queue after this BD.                                                         |

| Ι      | Interrupt | Control bit set by the user. When a cell is received into the buffer associated with this BD, a receive interrupt is generated. |

| A2-A13 | Address   | Address offset to the start of the data buffer from the start of the 16K byte receive data area.                                |

| OAM    | OAM Cell  | Status bit set by ATOM1. The associated cell is an OAM or reserved cell (cell PT field = $1xx$ ).                               |

| ERR    | HEC Error | Status bit set by ATOM1. The associated cell was received with an error in the header as detected by the HEC check.             |

| ATOMIT USEL S Manual 1.0 | ATOM1 | <b>User's Manual</b> | 1.0 |

|--------------------------|-------|----------------------|-----|

|--------------------------|-------|----------------------|-----|

-22-

HEC HEC Byte Byte containing the received cell's HEC field.

ATOM1 stores received ATM cells in receive buffers after removing the HEC. Receive data buffers have the same structure as transmit buffers. The first byte of the buffer is the first byte received (the GFC field and part of the VPI). The HEC field is removed and stored in the receive BD.

#### 6.3. Transmit Buffer Descriptor and Data Buffer

Transmit BDs are two bytes long as shown in Figure 10. Each BD is linked to one buffer that must hold the complete ATM cell to be transmitted. Transmit buffers may be scattered around a 16K byte area of memory but must start on a long word aligned address. If the start address of a buffer is at the very end of the 16K byte area (for example, the transmit BD is programmed with \$8FFF) then the end of the transmit cell will be 48 bytes outside of the 16K byte area.

| 15 | 14   | 13 | 12 | 11  | 10  | 9   | 8   | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|----|------|----|----|-----|-----|-----|-----|----|----|----|----|----|----|----|----|

| R  | SKIP | W  | I  | A13 | A12 | A11 | A10 | A9 | A8 | A7 | A6 | A5 | A4 | A3 | A2 |

Figure 10. ATOM1 Transmit Buffer Descriptor

| R      | Ready     | Control bit set by the user to initiate transmission of the associated cell. ATOM1 clears the Ready bit when the associated buffer has been transmitted.                                                    |

|--------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SKIP   | Skip BD   | Control bit set by the user. When ATOM1 encounters a transmit BD with the Skip bit set, an empty cell is transmitted and control passes to the next BD. When the Skip bit is set, the Ready bit is ignored. |

| W      | Wrap      | Control bit set by the user to wrap the transmit BD queue after this BD.                                                                                                                                    |

| Ι      | Interrupt | Control bit set by the user. When the cell associated with this BD is transmitted, a transmit interrupt is generated. This bit is ignored when the Skip bit is also set.                                    |

| A2-A13 | Address   | Address offset to the start of the data buffer from the start of the 16K byte transmit data area.                                                                                                           |

ATOM1 transmits the ATM cell stored in the transmit buffer and automatically inserts the HEC. Data buffers are all 52 bytes long with the first four bytes being the cell header as shown in Figure 11. The first byte of the buffer is the first byte to be transmitted.

| GFC         | VPI     | PT | CLP |  |  |  |  |  |

|-------------|---------|----|-----|--|--|--|--|--|

| Payload     |         |    |     |  |  |  |  |  |

|             | Payload |    |     |  |  |  |  |  |

| •<br>•<br>• |         |    |     |  |  |  |  |  |

| Payload     |         |    |     |  |  |  |  |  |

Figure 11. Transmit Buffer

#### 6.3.1. Transmit Bandwidth Reservation

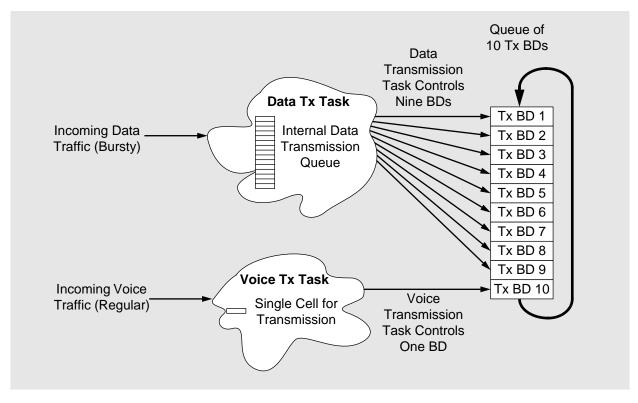

ATOM1 includes a mechanism to reserve transmit bandwidth to aid tasks that require low latency transmission. An example of such a system might be one that simultaneously handles voice and data transmissions: the data transmission task can queue a large number of ATM cells that are not delay sensitive while the voice transmission circuit has less traffic but must be serviced at regular intervals.

The mixed voice and data example is used here to illustrate the bandwidth reservation system.

In most systems, the number of transmit and receive buffer descriptors and buffers per SCC is fixed when the system software is designed. For example, the ATOM1 transmit queue may be fixed at ten buffers. The data transmission software can maintain its own software queue that may hold several hundred cells. The voice task must transmit each cell as soon as it is generated and not store them in a queue. If the voice cells were to be placed at the end of the software data transmission queue, the latency would be too high.

The transmit bandwidth reservation system avoids this problem by allowing selected BDs to be reserved for the voice transmission. When ten BDs are allocated to the data and voice transmission software tasks, nine can be assigned for data and one for voice. This reserves 10% of the transmission bandwidth for voice channels.

The reservation mechanism uses the Skip bit in the transmit BD. As ATOM1 processes the transmit BD queue, it transmits cells where the Skip bit is zero. When a BD with the Skip is encountered, it is skipped and an empty cell is transmitted in its place.

In the mixed data and voice example, the data transmission software can control nine of the ten BDs and set their Ready bits to initiate transmission. The voice transmission software reserves one BD by setting its Skip bit. When a voice cell is ready for transmission, the voice transmission software inserts the header and payload in the relevant transmit data buffer, clears the Skip bit and sets the Ready bit. Next time that ATOM1 checks this BD, it will see only the Ready bit set and therefore transmit the voice cell.

Figure 12 illustrates this example. The tenth transmit BD is reserved for voice traffic. While the voice transmission task is constructing an ATM cell and has nothing in the transmit BD queue,

ATOM1 User's Manual 1.0

-24-

it reserves bandwidth by setting the Skip bit. When the voice cell has been constructed and loaded into the tenth transmit buffer, the Skip bit is cleared and the Ready bit set. The voice cell is then transmitted with a maximum delay of nine cells.

Figure 12. Mixed Voice and Data Transmission Example

# 7. ATOM1 CAM INTERFACE

Figure 13 shows the ATOM1 CAM interface and a timing diagram illustrating operation. Operation is similar to the Ethernet CAM interface (see the MC68360 User's Manual section 7.10.23.7 for further details). The SDACK1\* signal delimits a header write cycle on the data bus and SDACK2\* delimits payload write cycles. Both SDACK1\* and SDACK2\* are asserted during the final payload write cycle. ATOM1 samples the MATCH\* signal during the last data transfer of the cell.

#### Figure 13. ATOM1 CAM Interface

The user selects the pin to be used as the MATCH\* input from the port B PB0-PB15 pins using the CAM\_PORT parameter. Multiple CAMs can be connected to a single SCC running ATOM1 by using multiple MATCH\* inputs. ATOM1 looks for one or more of the MATCH\* inputs to be active. The port B pins being used as the MATCH\* input must be configured as input ports using the port B configuration registers PBPAR and PBDIR.

When ATOM1 is operating on several SCCs concurrently, each may be connected to a CAM. To distinguish between the SDMA cycles for each SCC, each receiver function codes should be programmed to a different value.

When the CAM interface is operating with ATOM1, the Ethernet CAM interface can still be used. The CAM control logic will need to check the function codes and SDACK signals to determine which SCC has initiated a particular bus cycle and enable the appropriate CAM chip.

# 8. LOADING & CONFIGURING ATOM1

Before operation, the ATOM1 microcode must be loaded into the MC68360's internal RAM. The microcode is delivered in a file of S-records ready to download to a Motorola QUADS board and a general M68000 assembly code file. Further details of QUADS download procedures are given in the QUADS User's Manual.

The microcode occupies the internal RAM blocks DPRBASE+0 to DPRBASE+3FF and DPRBASE+600 to DPRBASE+6FF. These areas are unavailable for use by the user.

Once the ATOM1 microcode is loaded into the MC68360's internal RAM, it is initialized as follows:

- 1. Configure SDMA.

- 2. Configure parallel ports.

- 3. Configure serial interface.

- 4. Enable TSA.

- 5. Configure CP registers.

- 6. Enable RAM microcode.

- 7. Configure SCC registers. Configure GSMR, PSMR, SCCE and SCCM to select required operation.

- 8. Configure ATOM1 parameter RAM.

- 9. Initialize queue of empty receive BDs and buffers.

- 10. Clear transmit BDs.

- 11. Enable SCC by setting ENT and ENR bits in the GSMR lower long word.

Once initialisation is complete, ATOM1 can be controlled through the transmit and receive BD queues and commands.

Example source code for initialisation and operation of ATOM1 is given in Appendix B.

# 9. **PERFORMANCE**

Tables 8 and 9 show the results of some performance characterisation experiments where ATOM1 is run concurrently with other SCCs. All results are for zero wait state access to memory. In the experiments, all SCCs were continually transmitting and receiving data cells (no commands or CRC-32 calculations) and frames of the following size:

| HDLC frames     | 24 bytes data + 2 bytes CRC      |

|-----------------|----------------------------------|

| Ethernet frames | 64 bytes data + 4 bytes CRC      |

| ATM cells       | 5 byte header + 48 bytes payload |

| Configuration | ATOM1 SCCs    | Mode                  | Frequency Ratio | System<br>Frequency |

|---------------|---------------|-----------------------|-----------------|---------------------|

| 1 ATM         | SCC1          | ATOM1 - No Scrambling | 1:3             |                     |

| 1 ATM         | SCC1          | ATOM1 - Scrambling    | 1:4.5           | _                   |

| 2 ATM         | SCC1, 2       | ATOM1 - No Scrambling | 1:8             |                     |

| 2 ATM         | SCC1, 2       | ATOM1 - Scrambling    | 1:10            | 25 MHz /<br>33 MHz  |

| 3 ATM         | SCC1, 2, 3    | ATOM1 - No Scrambling | 1:10            |                     |

| 3 ATM         | SCC1, 2, 3    | ATOM1 - Scrambling    | 1:14            |                     |

| 4 ATM         | SCC1, 2, 3, 4 | ATOM1 - No Scrambling | 1:13            |                     |

| 4 ATM         | SCC1, 2, 3, 4 | ATOM1 - Scrambling    | 1:19            |                     |

#### Table 8: ATOM1 Performance

|                                             |      | ATOM1 SCC              |                    |          |          |                    |                     |          |      |      |     |

|---------------------------------------------|------|------------------------|--------------------|----------|----------|--------------------|---------------------|----------|------|------|-----|

| Configuration                               | SCC  | Mode                   | Frequency<br>Ratio | SCC      | Mode     | Frequency<br>Ratio | System<br>Frequency |          |      |      |     |

| 1 ATM<br>channel<br>+<br>3 HDLC<br>channels | SCC1 | ATOM1<br>No Scrambling | 1:12<br>(note 1)   | SCC2/3/4 | HDLC     | 1:8                |                     |          |      |      |     |

|                                             | SCC1 | ATOM1<br>Scrambling    | 1:12<br>(note 1)   | SCC2/3/4 | HDLC     | 1:9                | 25 MHz /            |          |      |      |     |

|                                             | SCC1 | ATOM1<br>No Scrambling | 1:3.5              | SCC2/3/4 | HDLC     | 1:390<br>(note 2)  | 33 MHz              |          |      |      |     |

|                                             | SCC1 | ATOM1<br>Scrambling    | 1:5                | SCC2/3/4 | HDLC     | 1:390<br>(note 2)  |                     |          |      |      |     |

| 1 ATM +<br>1 Ethernet<br>channel            | SCC1 | ATOM1<br>No Scrambling | 1:6                | SCC2     | Ethernet | 1:2.5              | 25 MHz              |          |      |      |     |

|                                             | SCC1 | ATOM1<br>Scrambling    | 1:7                | SCC2     | Ethernet | 1:2.5              | 23 1011 12          |          |      |      |     |

| 1 ATM,                                      | SCC1 | M SCC1                 | ATOM1              | 1:12     | SCC2     | Ethernet           | 1:2.5               |          |      |      |     |

| 1 Ethernet +                                |      | No Scrambling          | (note 1)           | SCC3     | HDLC     | 1:4                | 25 MHz              |          |      |      |     |

| 1 HDLC                                      | SCC1 | ATOM1                  | 1:12               | SCC2     | Ethernet | 1:2.5              | 25 1011 12          |          |      |      |     |

| channel                                     |      | 3001                   | 3001               | 3001     |          | nannei SCCT        | Scen Scrambling     | (note 1) | SCC3 | HDLC | 1:5 |

| 1 ATM +<br>1 Ethernet                       | SCC1 | ATOM1<br>No Scrambling | 1:3.5              | SCC2     | Ethernet | 1:3.3              | 33 MHz              |          |      |      |     |

| channel                                     | SCC1 | ATOM1<br>Scrambling    | 1:4                | SCC2     | Ethernet | 1:3.3              |                     |          |      |      |     |

| 1 ATM.                                      | SCC1 | ATOM1                  | 1:16               | SCC2     | Ethernet | 1:3.3              |                     |          |      |      |     |

| 1 Ethernet +                                | 3001 | No Scrambling          | (note 3)           | SCC3     | HDLC     | 1:4                | 22 M⊔-              |          |      |      |     |

| 1 HDLC                                      | SCC1 | ATOM1                  | 1:16               | SCC2     | Ethernet | 1:3.3              | 33 MHz              |          |      |      |     |

| channel                                     | 3001 | Scrambling             | (note 3)           | SCC3     | HDLC     | 1:5                |                     |          |      |      |     |

Notes:

1. A frequency ratio of 1:12 equates to 2.048 MHz at 25 MHz.

2. A frequency ratio of 1:390 equates to 64 KHz at 25 MHz.

3. A frequency ratio of 1:16 equates to 2.048 MHz at 33 MHz.

#### **Table 9: ATOM1 and other Protocol Performance**

This data traffic in the experiments represents typical worst case scenarios for real life applications where QUICC data structures were organised to maximise performance. All frames were restricted to single buffers that were aligned to long-word addresses and receive frame address comparisons were disabled. The Ethernet figures quoted in Table 8 are for half duplex operation<sup>1</sup>.

The frequency ratios quoted are between the main QUICC clock and SCC bit clock.

## 9.1. Command Execution Latency

When ATOM1 is operating, typical and worst-case command execution latencies are slightly longer than when only the standard ROM microcodes are running.

Note: The ATOM1 Restart Reception command is not executed until ATOM1 processes the end of the current cell being received. Therefore command latency for the Restart Reception command depends on when the command is given and data rate.

## 9.2. CRC-32 Calculation Execution

Table 10 shows the results of some performance characterisation experiments where ATOM1 is running on one or more SCCs while CRC-32 calculations are also running. The QUICC's CP runs the CRC-32 calculator as its lowest priority task so the duration of a calculation varies depending on the exact loading and state of the CP. The CRC-32 calculations were run over a buffer of 44 bytes representing the AAL5 payload of a single cell AAL5 frame with start of the data buffer aligned to a longword address. All results shown in Table 10 are for system operation at 25MHz and can be scaled for operation at other frequencies.

| Configuration | ATOM1 SCCs    | Mode                  | Frequency Ratio | CRC-32<br>Calculation<br>Duration |

|---------------|---------------|-----------------------|-----------------|-----------------------------------|

| 1 ATM         | SCC1          | ATOM1 - No Scrambling | 1:12 (note 1)   | 20 - 24 μs                        |

| 1 ATM         | SCC1          | ATOM1 - Scrambling    | 1:12 (note 1)   | 20 - 28 μs                        |

| 2 ATM         | SCC1, 2       | ATOM1 - No Scrambling | 1:12 (note 1)   | 28 - 37 μs                        |

| 2 ATM         | SCC1, 2       | ATOM1 - Scrambling    | 1:12 (note 1)   | 52 - 72 μs                        |

| 3 ATM         | SCC1, 2, 3    | ATOM1 - No Scrambling | 1:12 (note 1)   | 52 - 76 μs                        |

| 3 ATM         | SCC1, 2, 3    | ATOM1 - No Scrambling | 1:25 (note 2)   | 23 - 30 μs                        |

| 3 ATM         | SCC1, 2, 3    | ATOM1 - Scrambling    | 1:25 (note 2)   | 27 - 52 μs                        |

| 4 ATM         | SCC1, 2, 3, 4 | ATOM1 - No Scrambling | 1:25 (note 2)   | 26 - 34 μs                        |

| 4 ATM         | SCC1, 2, 3, 4 | ATOM1 - Scrambling    | 1:25 (note 2)   | 40 - 65 μs                        |

Notes:

1. A frequency ratio of 1:12 equates to 2.083 MHz at 25 MHz.

2. A frequency ratio of 1:25 equates to 1 MHz at 25 MHz.

#### Table 10: CRC-32 Calculator Performance

<sup>1.</sup> The experimental Ethernet data rate was 5 Mbps full duplex which equates to 10 Mbps on a conventional half duplex Ethernet system.

# **10. ATOM1 DISK STRUCTURE**

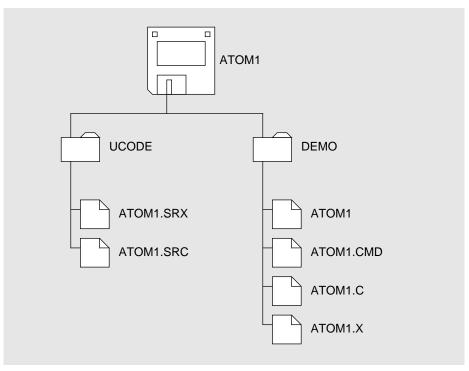

ATOM1 is shipped on a PC format disk. Figure 14 shows the disk structure. The microcode is held in the UCODE directory and demonstration software is stored in the DEMO directory. ATOM1.SRX is the S-record microcode file for the QUADS board memory map. ATOM1.SRC is an M68000 assembly code file for the ATOM1 microcode that can be assembled and linked to any system memory map.

The file ATOM1.C contains the C source code for the initialisation and ping-pong demonstration software given in Appendix B. ATOM1 and ATOM1.CMD are the makefiles for the C demonstration software and ATOM1.X is the S-record file of the demonstration software, ready to download to a QUADS board.

Figure 14. ATOM1 Disk Structure

# 11. MC68360 MASK SET APPLICABILITY

ATOM1 microcode operates on revision B or later MC68360s and MC68EN360s. Note: there are slight differences to the initialisation software for revision B1 and later devices (see section 3.1.2). The ATOM1 microcode cannot be used in conjunction with the QMC protocol for multichannel operation on an MC68MH360 due to on-chip RAM space constraints.

# **12. ORDERING INFORMATION**

The ATOM1 package contains relocatable ATOM1 object code, object code for the QUADS board, a User's Manual and demonstration software for the QUADS board. ATOM1 is available on DOS media by using the following part number:

M68360SWATM1-DOS PC disk.

# **13. REFERENCES**

- 1. MC68360 User's Manual, MC68360UM/AD Rev 1, Motorola, 1995.

- 2. ITU I.432, B-ISDN User Network Interface Physical Layer Specification, 1991.

- 3. ATM Forum User Network Interface Specification, version 3.0, 1993.

- 4. Draft Recommendation ITU G.804, ATM Cell Mapping into Plesiochronous Digital Hierarchy (PDH), 1993.

- 5. ITU I.363, B-ISDN ATM Adaptation Layer Specification.

# **Appendix 1. STATE MACHINE DETAILS**

## A1.1 ATOM1 Transmitter

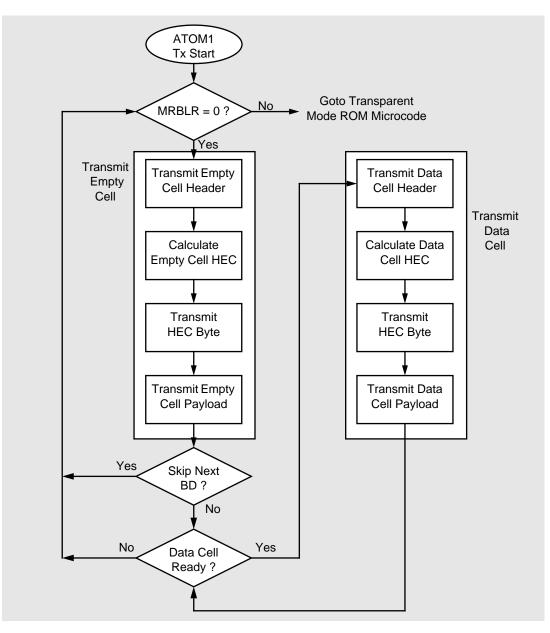

Figure 15 shows the ATOM1 transmitter procedure. After start-up when MRBLR is zero, an empty cell is transmitted before the first transmit BD is polled. If the BD has the Skip bit set, an empty cell is transmitted and the transmitter moves to the next BD. If the BD is ready, a user defined ATM cell is transmitted, otherwise another empty cell is transmitted. Operation continues in this manner until the Stop Transmit command or a FIFO underrun error occurs of the user disables the SCC transmitter. The transmitted cells may have their payloads scrambled as described below.

Figure 15. ATOM1 Transmitter Procedure

ATOM1 User's Manual 1.0

## A1.2 ATM Cell Payload Scrambling

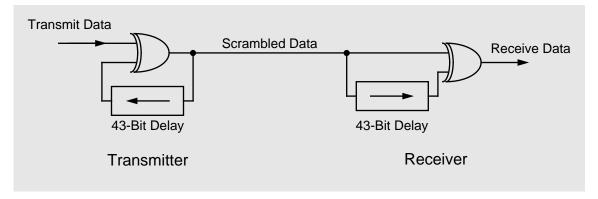

ATOM1 provides a scrambling option on a per line basis for cell payload bytes using the polynomial  $X^{43}$ +1. Figure 16 illustrates the payload transmitter and receiver scrambling mechanism used by ATOM1.

Figure 16. ATM Cell Payload Scrambling Mechanism

The context of the transmit and receive scrambling mechanism is independent of the cell's virtual connection. The seed value for the scrambling algorithm for a particular cell is obtained from the 43 cell payload bits transmitted or received immediately prior to the current cell. Two consecutive cells may be from different connections and scrambling mechanism ignores this.

## A1.3 ATOM1 Receiver

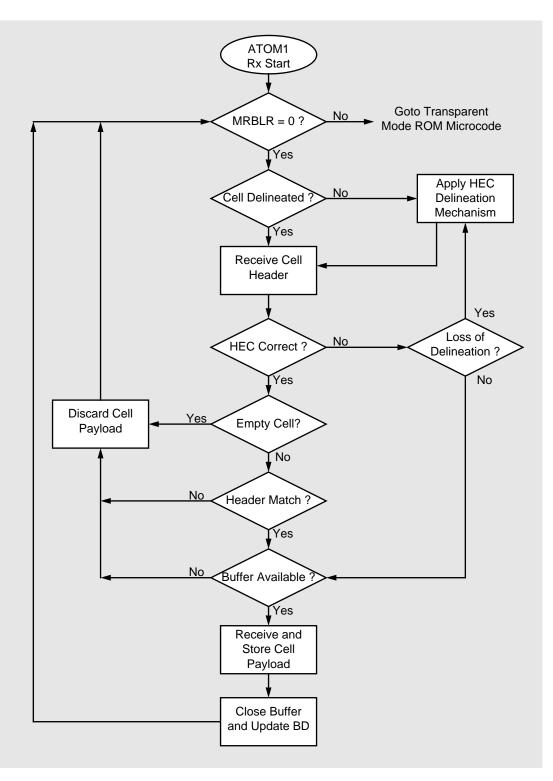

Figure 17 shows the ATOM1 receiver procedure. After start-up when MRBLR is zero, the HEC delineation procedure begins (see below). Once complete, cell reception commences.