# MC9S08MP16 Controller Daughter Board for BLDC/PMSM Motor Control Drive

**Users Manual**

Rev. 0 06/2009

freescale.com

#### **Table of Contents**

### Chapter 1 Board Overview

| 1.1   | MC9S08MP16 Controller Daughter Board for BLDC/PMSM Motor Control Drive Outline 7 |

|-------|----------------------------------------------------------------------------------|

| 1.2   | About this Manual                                                                |

| 1.3   | Setup Guide                                                                      |

| 1.4   | Board Description                                                                |

|       | Chapter 2 Pin Description                                                        |

| 2.1   | Introduction                                                                     |

| 2.2   | Signal Descriptions                                                              |

| 2.2.1 | Daughter Board Connectors J1 and J2                                              |

| 2.2.2 | BDM Header J3                                                                    |

| 2.2.3 | Configuration Header J4                                                          |

| 2.2.4 | ADC Configuration Header JP1                                                     |

#### Appendix A.

MC9S08MP16 Controller Daughter Board for BLDC/PMSM Motor Control Drive Schematics

Appendix B. Bill of Materials

Appendix C.

MC9S08MP16 Controller Daughter Board for BLDC/PMSM Motor Control Drive Layouts

## MC9S08MP16 Controller Daughter Board for BLDC/PMSM Motor Control Drive

**Users Manual**

by:Petr Frgal Freescale Semiconductor Czech System Center

To provide the most up-to-date information, the revision of our documents on the World Wide Web will be the most current. Your printed copy may be an earlier revision. To verify that you have the latest information available, refer to <a href="http://www.freescale.com">http://www.freescale.com</a>

The following revision history table summarizes changes contained in this document. For your convenience, the page number designators have been linked to the appropriate location.

#### **Revision History**

| Date    | Revision<br>Level | Description     | Page<br>Number(s) |

|---------|-------------------|-----------------|-------------------|

| 06/2009 | 0                 | Initial release | N/A               |

## Chapter 1 Board Overview

### 1.1 MC9S08MP16 Controller Daughter Board for BLDC/PMSM Motor Control Drive Outline

Freescale's MC9S08MP16 Controller Daughter Board for BLDC/PMSM Motor Control Drive together with a 3-Phase BLDC/PMSM Motor Control Drive board create a single unit for developing BLDC/PMSM motor-control applications.

The daughter board is connected via two connectors to the 3-Phase BLDC/PMSM Motor Control Drive board. All necessary signals are available to allow a variety of algorithms to control the 3-Phase PMSM and BLDC motors.

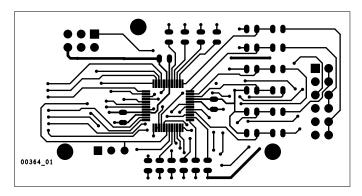

Figure 1-1 is an illustration of the controller daughter board.

#### 1.2 About this Manual

Key items are in the following locations in this manual:

- Setup instructions 1.3 Setup Guide

- Schematics Appendix A. MC9S08MP16 Controller Daughter Board for BLDC/PMSM Motor Control Drive Schematics

- Pin assignments Chapter 2 Pin Description

- Pin-by-pin description 2.2 Signal Descriptions

Figure 1-1 MC9S08MP16 Controller Daughter Board

MC9S08MP16 Controller Daughter Board for BLDC/PMSM Motor Control Drive, Rev. 0

#### 1.3 Setup Guide

Setup and connections for the MC9S08MP16 Controller Daughter Board for BLDC/PMSM Motor Control Drive are straightforward. The controller daughter board plugs into the main board via two 20-pin daughter board connectors. The system can be powered by a 12 to 24 V DC power supply. For safety reasons, and ease of making measurements, use a regulated DC supply. Limit power supply to under five amps.

Place jumpers to route the required signals to the controller. For jumper settings, visit chapter 2.2.4 ADC Configuration Header JP1.

A step-by-step setup procedure for the main board is available in the *3-Phase BLDC/PMSM Motor Control Drive Users Manual* LVMCDBLDCPMSMUG.

#### WARNING

Check the power supply voltage before plugging in the Controller Daughter Board. If an input voltage higher than 24 V is applied, the controller daughter board can be damaged.

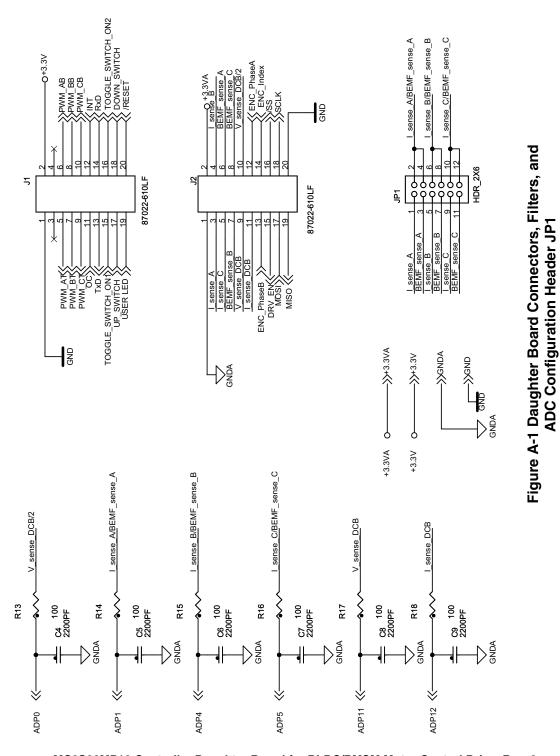

#### 1.4 Board Description

The Controller Daughter Board is populated with an MC9S08MP16 8-bit HCS08 controller. All the necessary signals are available on two 20-pin Rib-cage connectors, J1 and J2. BDM header J3 is used for program upload onto the controller. Headers J4 and JP1 are configuration headers and are used for board configuration. For more details, look into 2.2.3 Configuration Header J4 and 2.2.4 ADC Configuration Header JP1.

Board schematic is available in Appendix A. MC9S08MP16 Controller Daughter Board for BLDC/PMSM Motor Control Drive Schematics.

## Chapter 2 Pin Description

#### 2.1 Introduction

Inputs and outputs are located on seven connectors and headers available on the board:

- Two 20-pin daughter board connectors J1, J2

- BDM header J3

- Configuration header J4

- ADC configuration header JP1

Pin descriptions for each connector and header are identified in the following information.

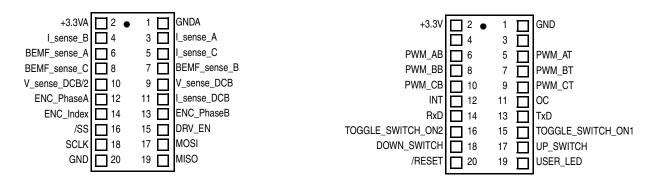

Figure 2-1 shows the pin assignments for the daughter board connectors J1 and J2.

Table 2-1 and Table 2-2 show the signal descriptions. JP1 configuration header is used to share AD converter inputs for BEMF voltages and phase currents.

#### 2.2 Signal Descriptions

Pin descriptions are identified in this subsection.

#### 2.2.1 Daughter Board Connectors J1 and J2

Signal inputs and outputs for interconnection with the 3-Phase BLDC/PMSM LV Motor Control Drive are situated on two 20-pin connectors, located on the board's bottom-side. Figure 2-1 shows the pin assignments. This figure shows the physical layout of the connectors, assuming that the board is oriented upside down (bottom is up). Table 2-1 and Table 2-2 contain the lists of signal descriptions for connectors J1 and J2.

Table 2-1 Daughter Board Connector J1 — Signal Descriptions

| Pin # | Signal Name | Description                                                                                      |  |

|-------|-------------|--------------------------------------------------------------------------------------------------|--|

| 1     | GND         | Digital and power ground                                                                         |  |

| 2     | +3.3V       | Digital +3.3 V power supply                                                                      |  |

| 3     | No Connect  |                                                                                                  |  |

| 4     | No Connect  |                                                                                                  |  |

| 5     | PWM_AT      | Gate-drive signal for the top half-bridge of phase A. A logic low turns on phase A's top switch. |  |

MC9S08MP16 Controller Daughter Board for BLDC/PMSM Motor Control Drive, Rev. 0

#### Table 2-1 Daughter Board Connector J1 — Signal Descriptions (Continued)

| Pin # | Signal Name           | Description                                                                                             |  |  |

|-------|-----------------------|---------------------------------------------------------------------------------------------------------|--|--|

| 6     | PWM_AB                | Gate-drive signal for the bottom half-bridge of phase A. A logic high turns phase A's bottom switch on. |  |  |

| 7     | PWM_BT                | Gate-drive signal for the top half-bridge of phase B. A logic low turns on phase B's top switch.        |  |  |

| 8     | PWM_BB                | Gate-drive signal for the bottom half-bridge of phase B. A logic high turns phase B's bottom switch on. |  |  |

| 9     | PWM_CT                | Gate-drive signal for the top half-bridge of phase C. A logic low turns on phase C's top switch.        |  |  |

| 10    | PWM_CB                | Gate-drive signal for the bottom half-bridge of phase C. A logic high turns phase C's bottom switch on. |  |  |

| 11    | ОС                    | Overcurrent signal from the 3-phase bridge driver.                                                      |  |  |

| 12    | INT                   | Interrupt signal from the 3-phase bridge driver.                                                        |  |  |

| 13    | TxD                   | TxD signal between JM60 and the Controller Daughter Board.                                              |  |  |

| 14    | RxD                   | RxD signal between JM60 and the Controller Daughter Board.                                              |  |  |

| 15    | TOGGLE_<br>SWITCH_ON1 | Toggle-switch input (switch in position ON1) on the BLDC drive.                                         |  |  |

| 16    | TOGGLE_<br>SWITCH_ON2 | Toggle-switch input (switch in position ON2) on the BLDC drive.                                         |  |  |

| 17    | UP_SWITCH             | UP switch input.                                                                                        |  |  |

| 18    | DOWN_SWITCH           | DOWN switch input.                                                                                      |  |  |

| 19    | USER_LED              | USER LED signal.                                                                                        |  |  |

| 20    | /RESET                | RESET signal.                                                                                           |  |  |

#### Table 2-2 Daughter Board Connector J2 — Signal Descriptions

| Pin #                                                                                                         | Signal Name                                                                                                    | Description                                                                                              |  |

|---------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|--|

| 1                                                                                                             | GNDA                                                                                                           | Analog-power supply ground.                                                                              |  |

| 2                                                                                                             | +3.3VA                                                                                                         | Analog +3.3 V power supply.                                                                              |  |

| 3                                                                                                             | I_sense_A  Analog-sense signal that measures current in phase A. It is scaled at 50 V per a of DC-bus current. |                                                                                                          |  |

| 4                                                                                                             | I_sense_B                                                                                                      | Analog-sense that measures current in phase B. It is scaled at 0.563 V per amp of DC-bus current.        |  |

| 5 I_sense_C Analog-sense signal that measures current in phase C. It is scaled at 0.56 amp of DC-bus current. |                                                                                                                | Analog-sense signal that measures current in phase C. It is scaled at 0.563 V per amp of DC-bus current. |  |

| I h I BEWE SENSE A I                                                                                          |                                                                                                                | Analog-sense signal that measures phase A back-EMF. It is scaled at 8.09 mV per volt of DC-bus voltage.  |  |

#### MC9S08MP16 Controller Daughter Board for BLDC/PMSM Motor Control Drive, Rev. 0

#### Table 2-2 Daughter Board Connector J2 — Signal Descriptions (Continued)

| Pin # | Signal Name   | Description                                                                                               |  |

|-------|---------------|-----------------------------------------------------------------------------------------------------------|--|

| 7     | BEMF_sense_B  | Analog-sense signal that measures phase B back-EMF. It is scaled at 8.09 mV per volt of DC-bus voltage.   |  |

| 8     | BEMF_sense_C  | Analog-sense signal that measures phase C back-EMF. It is scaled at 8.09 mV per volt of DC-bus voltage.   |  |

| 9     | V_sense_DCB   | Analog-sense signal that measures bus voltage. It is scaled at 8.09 V per volt of DC-bus voltage.         |  |

| 10    | V_sense_DCB/2 | Analog-sense signal that measures half of bus voltage. It is scaled at 4.05 V per volt of DC-bus voltage. |  |

| 11    | I_sense_DCB   | Analog-sense signal that measures bus current. It is scaled at 0.563 V per amp of DC-bus current.         |  |

| 12    | ENC_PhaseA    | Encoder or Hall sensor Phase A input pin logic.                                                           |  |

| 13    | ENC_PhaseB    | Encoder or Hall sensor Phase B input pin logic.                                                           |  |

| 14    | ENC_Index     | Encoder Index or Hall sensor Phase C input pin logic.                                                     |  |

| 15    | DRV_EN        | 3-phase bridge gate driver enable signal.                                                                 |  |

| 16    | /SS           | SPI pin chip select pin for the 3-phase bridge driver.                                                    |  |

| 17    | MOSI          | SPI pin Master Out Slave In pin for the 3-phase bridge driver.                                            |  |

| 18    | SCLK          | SPI pin Clock Source pin Input for the 3-phase bridge driver.                                             |  |

| 19    | MISO          | SPI pin Master In Slave Out pin for the 3-phase bridge driver.                                            |  |

| 20    | GND           | D Digital and power ground.                                                                               |  |

Figure 2-1 J2 and J1 Connector Physical View

MC9S08MP16 Controller Daughter Board for BLDC/PMSM Motor Control Drive, Rev. 0

#### 2.2.2 BDM Header J3

This serves for updating the software for the MC9S08MP16 controller. Signals are described in Table 2-3.

Table 2-3 BDM Header J3 — Signal Descriptions

| Pin # Signal Name |         | Description                 |

|-------------------|---------|-----------------------------|

| 1                 | BKGD/MS | Background debug pin        |

| 2 GND             |         | Digital ground              |

| 3 No Connect      |         |                             |

| 4 /RESET          |         | RESET signal                |

| 5 No Connect      |         |                             |

| 6 +3.3V           |         | Digital +3.3 V power supply |

#### 2.2.3 Configuration Header J4

Configuration header J4 serves for connecting OC signal or INT signal to the controller FTM2FAULT pin. Table 2-4 shows the jumper setting for selected function.

Table 2-4 Configuration Header J4 — Signal Descriptions

|                            |     | <u> </u>                                      |

|----------------------------|-----|-----------------------------------------------|

| Pin<br>shorted Signal Name |     | Description                                   |

| 1–2 OC                     |     | Overcurrent signal connected to the FTM2FAULT |

| 2–3                        | INT | Interrupt signal connected to the FTM2FAULT   |

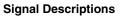

#### 2.2.4 ADC Configuration Header JP1

Table 2-5 shows the ADC Configuration Headers pin description. Headers select if the BEMF voltages or phase currents are routed to the controller ADC inputs ADP1, ADP4, and ADP5.

Table 2-5 ADC Configuration Header JP1 — Signal Descriptions

| ADC input  | Pins shorted | Signal Name                                           | Description                                         |

|------------|--------------|-------------------------------------------------------|-----------------------------------------------------|

| 1–2 l_sens | I_sense_A    | Analog-sense signal that measures current in phase A. |                                                     |

| 7511       | 3–4          | BEMF_sense_A                                          | Analog-sense signal that measures phase A back-EMF. |

| ADC input | ADC input Pins shorted Signal Name |              | Description                                           |  |

|-----------|------------------------------------|--------------|-------------------------------------------------------|--|

| ADP4      | 5–6                                | I_sense_B    | Analog-sense signal that measures current in phase B. |  |

| ADF4      | 7–8                                | BEMF_sense_B | Analog-sense signal that measures phase B back-EMF.   |  |

| ADDE      | 9–10                               | I_sense_C    | Analog-sense signal that measures current in phase C. |  |

| ADP5      | 11–12                              | BEMF_sense_C | Analog-sense signal that measures phase C back-EMF.   |  |

## Appendix A. MC9S08MP16 Controller Daughter Board for BLDC/PMSM Motor Control Drive Schematics

MC9S08MP16 Controller Daughter Board for BLDC/PMSM Motor Control Drive, Rev. 0

**Figure A-2 Controller and Headers**

## Appendix B. Bill of Materials

**Table B-1 Parts List**

| DESIGNATORS   | QUANTITY | DESCRIPTION                        | MANUFACTURER               | PART NUMBER   |

|---------------|----------|------------------------------------|----------------------------|---------------|

| C1-C3         | 2        | 100 nF/6.3 V size 0805             | ANY ACCEPTABLE             | _             |

| C4-C9         | 5        | 100 pF/6.3 V size 0805             | ANY ACCEPTABLE             | _             |

| J1, J2        | 2        | 87022-610                          | FCI                        | 87022-610LF   |

| J3            | 1        | HDR 2x3                            | TYCO<br>ELECTRONICS        | 1-87215-2     |

| J4            | 3        | HDR 1x3                            | TYCO<br>ELECTRONICS        | 87220-3       |

| JP1           | 1        | HDR 2x6                            | TYCO<br>ELECTRONICS        | 87215-3       |

| R1-R7, R9-R11 | 10       | 10 kΩ Resistor 1/8 W size 0805     | ANY ACCEPTABLE             | _             |

| R13-R18       | 6        | 100 Ω Resistor 1/8 W 1 % size 0805 | ANY ACCEPTABLE             | _             |

| U1            | 1        | 8-bit HCS08 controller/LQFP-48     | FREESCALE<br>SEMICONDUCTOR | MC9S08MP16CLF |

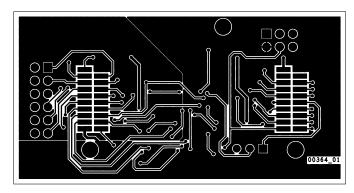

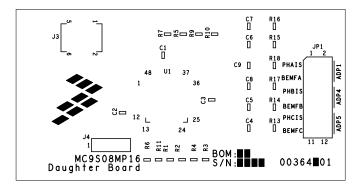

## Appendix C. MC9S08MP16 Controller Daughter Board for BLDC/PMSM Motor Control Drive Layouts

Figure C-1 Board Top Layer

Figure C-2 Board Bottom Layer

Figure C-3 Board Silkscreen Top Layer

MC9S08MP16 Controller Daughter Board for BLDC/PMSM Motor Control Drive, Rev. 0

#### How to Reach Us:

#### Home Page:

www.freescale.com

#### F-mail·

support@freescale.com

#### **USA/Europe or Locations Not Listed:**

Freescale Semiconductor Technical Information Center, CH370 1300 N. Alma School Road Chandler, Arizona 85224 +1-800-521-6274 or +1-480-768-2130 support@freescale.com

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) support@freescale.com

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064, Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor China Ltd.

Exchange Building 23F

No. 118 Jianguo Road

Chaoyang District

Beijing 100022

China

+86 10 5879 8000

support.asia@freescale.com

#### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center 1-800-441-2447 or 303-675-2140 Fax: 303-675-2150 LDCForFreescaleSemiconductor@hibbertgroup.com

Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. The ARM POWERED logo is a registered trademark of ARM Limited. ARM7TDMI-S is a trademark of ARM Limited. Java and all other Java-based marks are trademarks or registered trademarks of Sun Microsystems, Inc. in the U.S. and other countries. The Bluetooth trademarks are owned by their proprietor and used by Freescale Semiconductor, Inc. under license.

© Freescale Semiconductor, Inc. 2009. All rights reserved.

LVBLDCMP16DBUM Rev. 0 06/2009