## **KE17ZDTSIUG**

# $\frac{\text{KE17Z Dual Touch Sensing Interface (TSI) User Guide}}{\text{Rev. 2} - 7 \text{ May 2024}}$

User guide

#### **Document information**

| I | Information | Content                                                                                     |

|---|-------------|---------------------------------------------------------------------------------------------|

| I | Keywords    | KE17ZDTSIUG, KE17Z, KE1xZ, TSI, touch, touch sensing, touch electrode, touchpad             |

| , | Abstract    | Touch Sensing Interface (TSI) provides touch sensing detection on capacitive touch sensors. |

#### 1 Introduction

Touch Sensing Interface (TSI) provides touch sensing detection on capacitive touch sensors. The external capacitive touch sensor is typically formed on a PCB. The sensor electrodes are connected to TSI input channels through the I/O pins in the device.

#### 1.1 TSI model support of KE1xZ family

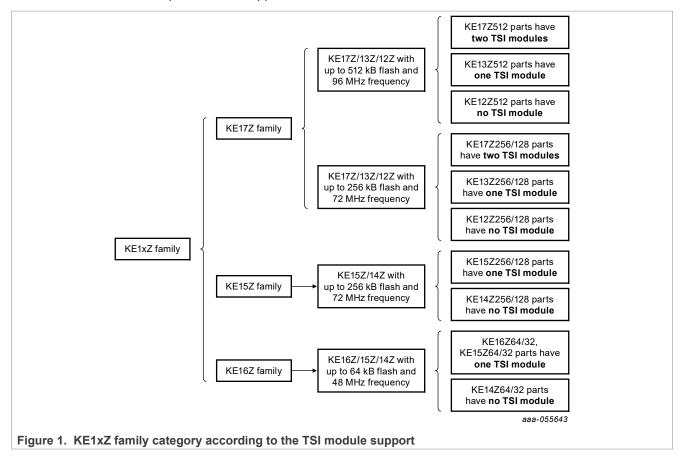

Figure 1 shows the KE1xZ family category according to TSI module support.

- KE17Z family includes the KE17Z512 series with up to 96 MHz frequency, and the KE17Z256 series with up to 72 MHz frequency. For the KE17Z family, KE17Z parts support two TSI modules, KE13Z parts support one TSI module, and KE12Z parts do not support TSI.

- For KE15Z family and KE16Z family, the KE15Z256/128 parts, KE16Z64/32 parts, KE15Z64/32 parts support one TSI module, KE14Z parts do not support TSI.

#### 1.2 KE17Z dual TSI

#### 1.2.1 KE17Z dual TSI features

KE17Z MCU has two TSI modules. It supports two kinds of touch sensing methods: self-capacitance (also called self-cap) mode and mutual-capacitance (also called mutual-cap) mode.

KE17ZDTSIUG

All information provided in this document is subject to legal disclaimers.

The dual-TSI technology of the KE17Z MCU supports up to 50 touch channels. The two TSI modules not only increase the number of touch electrodes, but also work in parallel to increase the scanning efficiency of touch electrodes and save the scanning time.

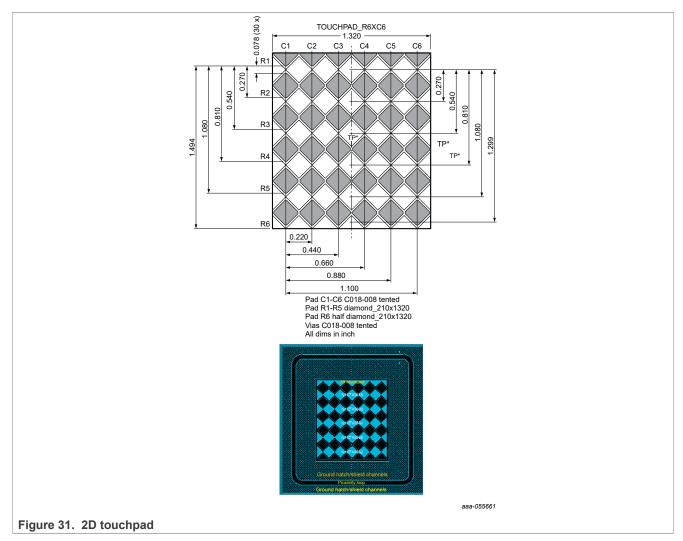

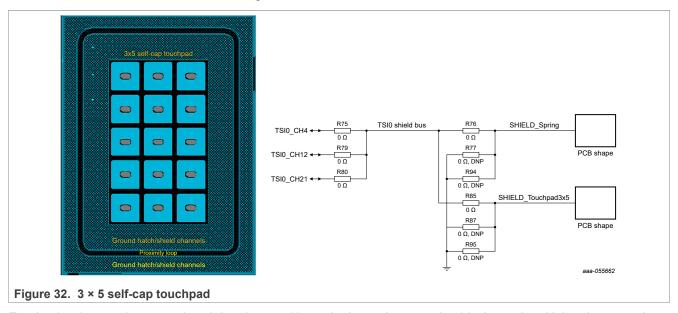

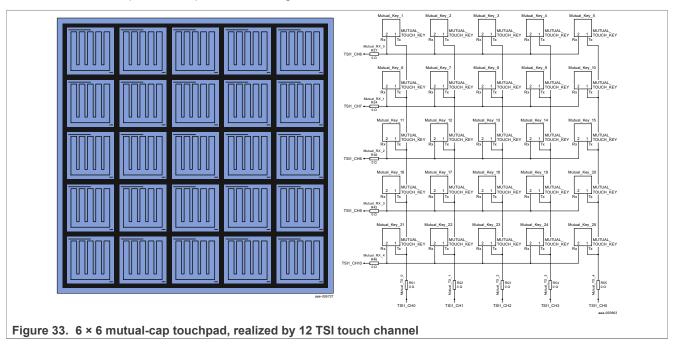

To enhance the liquid tolerance and improve the driving ability, each TSI module has three shield channels, up to 25 touch channels for self-cap mode, and up to  $6 \times 6$  touch channels for mutual-cap mode. Both mentioned methods can be combined on one single PCB, while only the lower 12 TSI channels TSI[0:11] can be used for mutual mode.

Note: TSI[0:5] are TSI TX pins and TSI[6:11] are TSI RX pins in mutual mode.

- In the self-capacitive mode, developers can use these 50 channels to design 50 (25 × 2) touch electrodes.

- In the mutual-capacitive mode, design options expand to up to 72 (6 × 6 × 2) touch electrodes.

In some use cases, such as a multi-burner induction cooker with touch controls or touch keyboards, the MCUs can support touchscreen designs scaling up to 98 touch electrodes (26 electrodes using self-capacitance + 72 electrodes using mutual channels).

#### 1.2.2 TSI model difference of KE17Z512 and KE17Z256/128

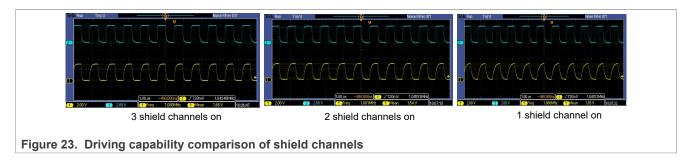

KE17Z512 and KE17Z256/128 are all support the dual TSI modules. To improve shield drive strength, the TSI IP in KE17Z512 series has done upgrade to enhance the shield channel drive strength and increase the number of shield channels by the using a shield multiplexing feature.

<u>Table 1</u> describes the shield feature comparison between KE17Z512 series and KE17Z256 series.

Table 1. Shield feature comparison between KE17Z512 series and KE17Z256/128 series

| Shield channel features          | KE17Z512                                                                                                         | KE17Z256/128                                                                           |

|----------------------------------|------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| Flexible shield channel          | Each TSI channel can be configured as a shield channel.                                                          |                                                                                        |

| Support more TSI shield channels | Each TSI can support up to 25 shield channels.                                                                   | Each TSI module has up to three normal drive shield channels. These three channels are |

| Enhanced TSI shield channel      | The shield drive strength of four TSI shield channels are enhanced four times compared to other shield channels. | flexible and configurable.                                                             |

#### 1.2.3 Features of KE17Z dual TSI models

Table 2. Features of KE17Z dual TSI models

| Features                 | KE17Z series TSI                                                                                                                                   |

|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| Operating voltage        | 2.7 V – 5.5 V                                                                                                                                      |

| Function clock source    | TSI internal generated                                                                                                                             |

| Function clock range     | 37 KHz-10 MHz                                                                                                                                      |

| Sensing mode             | Self-cap mode: Basic self-cap mode Sensitivity boost mode Noise cancellation mode  Mutual-cap mode: Basic mutual-cap mode Sensitivity boost enable |

| TSI channels             | Up to 50 channels (TSI0, TSI1)                                                                                                                     |

| Touch channel assignment | Self-cap mode: TSI[0:24]                                                                                                                           |

KE17ZDTSIUG All information provided in this document is subject to legal disclaimers. © 2024 NXP B.V. All rights reserved

Table 2. Features of KE17Z dual TSI models...continued

| Features                 | KE17Z series TSI                                                                                                                                                                                                                                                                                                                        |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                          | Mutual-cap mode: Tx[0:5], Rx[6:12]                                                                                                                                                                                                                                                                                                      |

| Touch Electrodes support | <ul> <li>Self-cap electrodes: up to 50 (25+25)</li> <li>Mutual-cap electrodes: up to 72 (6 × 6 + 6 × 6)</li> <li>Total up to: 98</li> </ul>                                                                                                                                                                                             |

| Shield channels          | <ul> <li>KE17Z512: <ul> <li>Each touch channel can be configured as the shield channel, up to 25 shield channels for each TSI module.</li> <li>Four enhanced shield channels for each TSI: CH4, CH12, CH21, CH24</li> </ul> </li> <li>KE17Z256/128: <ul> <li>Three shield channels for each TSI: CH4, CH12, CH21</li> </ul> </li> </ul> |

| Trigger source support   | <ul><li>Software trigger by writing GENCS[SWTS] bit.</li><li>Hardware trigger through INPUTMUX</li></ul>                                                                                                                                                                                                                                |

| Interrupt support        | End of scan interrupt, Out of range interrupt                                                                                                                                                                                                                                                                                           |

| Low power support        | STOP mode, VLPS mode: fully function when setting GENCS [STPE] to 1                                                                                                                                                                                                                                                                     |

| Low power wakeup         | Each TSI channel can wake up MCU from low power mode                                                                                                                                                                                                                                                                                    |

| DMA support              | The out-of-range event or end-of-scan event can trigger the DMA transfer                                                                                                                                                                                                                                                                |

| Hardware noise filter    | SSC reduces the frequency noise and promotes the signal-to-noise ratio. (PRBS mode, up-down counter mode)                                                                                                                                                                                                                               |

| IEC 61000 -4-6           | Passed 3 V/10 V level                                                                                                                                                                                                                                                                                                                   |

## 1.3 KE1xZ part numbers supporting TSI model

This chapter lists all the KE1xZ ordering parts with TSI supported, which is for users to check.

#### 1.3.1 KE17Z parts supporting dual TSI modules

<u>Table 3</u> lists the number of TSI channels corresponding to different parts of KE17Z. These parts all support dual TSI modules.

Table 3. KE17Z parts supporting dual TSI modules

| Product           | Frequency | Memory     |              | Package   |         | IO and ADO | channel           |              | НМІ                          |

|-------------------|-----------|------------|--------------|-----------|---------|------------|-------------------|--------------|------------------------------|

| Part<br>number    | MHz       | Flash (kB) | SRAM<br>(kB) | Pin count | Package | GPIOs      | GPIOs<br>(INT/HD) | ADC channels | TSI<br>[Number,<br>channels] |

| MKE17<br>Z512VLL9 | 96        | 512        | 96           | 100       | LQFP    | 89         | 89/8              | 24           | 2, 50 ch                     |

| MKE17<br>Z512VLH9 | 96        | 512        | 96           | 64        | LQFP    | 58         | 58/8              | 24           | 2, 50 ch                     |

| MKE17<br>Z256VLL7 | 72        | 256        | 48           | 100       | LQFP    | 89         | 89/8              | 16           | 2, 50 ch                     |

| MKE17<br>Z256VLH7 | 72        | 256        | 48           | 64        | LQFP    | 58         | 58/8              | 16           | 2, 47 ch                     |

| MKE17<br>Z256VLF7 | 72        | 256        | 48           | 48        | LQFP    | 42         | 42/6              | 11           | 2, 31 ch                     |

Table 3. KE17Z parts supporting dual TSI modules...continued

| Product           | Frequency | Memory     |              | Package   |         | IO and ADO | нмі               |              |                              |

|-------------------|-----------|------------|--------------|-----------|---------|------------|-------------------|--------------|------------------------------|

| MKE17<br>Z128VLL7 | MHz       | Flash (kB) | SRAM<br>(kB) | Pin count | Package | GPIOs      | GPIOs<br>(INT/HD) | ADC channels | TSI<br>[Number,<br>channels] |

| MKE17<br>Z128VLL7 | 72        | 128        | 32           | 100       | LQFP    | 89         | 89/8              | 16           | 2, 50 ch                     |

| MKE17<br>Z128VLH7 | 72        | 128        | 32           | 64        | LQFP    | 58         | 58/8              | 16           | 2, 47 ch                     |

| MKE17<br>Z128VLF7 | 72        | 128        | 32           | 48        | LQFP    | 42         | 42/6              | 11           | 2, 31 ch                     |

#### 1.3.2 KE1xZ parts supporting one TSI module

<u>Table 4</u> to <u>Table 6</u> list the number of TSI channels corresponding to different parts of KE13Z, KE15Z256/128, KE16Z64/32, and KE15Z64/32. These parts all support one TSI modules.

Table 4. KE13Z parts supporting one TSI module

| Product           | Frequency | Memory     |              | Package   |         | IO and ADO | Cchannel          |              | НМІ                          |

|-------------------|-----------|------------|--------------|-----------|---------|------------|-------------------|--------------|------------------------------|

| Part<br>number    | MHz       | Flash (kB) | SRAM<br>(kB) | Pin count | Package | GPIOs      | GPIOs<br>(INT/HD) | ADC channels | TSI<br>[Number,<br>channels] |

| MKE13<br>Z512VLL9 | 96        | 512        | 96           | 100       | LQFP    | 89         | 89/8              | 24           | 1, 25 ch                     |

| MKE13<br>Z512VLH9 | 96        | 512        | 96           | 64        | LQFP    | 58         | 58/8              | 24           | 1, 22 ch                     |

| MKE13<br>Z256VLL7 | 72        | 256        | 48           | 100       | LQFP    | 89         | 89/8              | 16           | 1, 25 ch                     |

| MKE13<br>Z256VLH7 | 72        | 256        | 48           | 64        | LQFP    | 58         | 58/8              | 16           | 1, 22 ch                     |

| MKE13<br>Z256VLF7 | 72        | 256        | 48           | 48        | LQFP    | 42         | 42/6              | 11           | 1, 15 ch                     |

| MKE13<br>Z128VLL7 | 72        | 128        | 32           | 100       | LQFP    | 89         | 89/8              | 16           | 1, 25 ch                     |

| MKE13<br>Z128VLH7 | 72        | 128        | 32           | 64        | LQFP    | 58         | 58/8              | 16           | 1, 22 ch                     |

| MKE13<br>Z128VLF7 | 72        | 128        | 32           | 48        | LQFP    | 42         | 42/6              | 11           | 1, 15 ch                     |

Table 5. KE15Z256/128 parts supporting one TSI module

| Product               | Frequency | Memory        |              |                                 | Package      |         | IO and AD | C channel         |              | НМІ                          |

|-----------------------|-----------|---------------|--------------|---------------------------------|--------------|---------|-----------|-------------------|--------------|------------------------------|

| Part<br>number        | MHz       | Flash<br>(kB) | SRAM<br>(kB) | Flex<br>NVM/<br>FlexRAM<br>(KB) | Pin<br>count | Package | GPIOs     | GPIOs<br>(INT/HD) | ADC channels | TSI<br>[Number,<br>channels] |

| MKE15<br>Z256<br>VLL7 | 72        | 256           | 32           | 32/2                            | 100          | LQFP    | 89        | 89/8              | 16+12        | 1, 25 ch                     |

| MKE15<br>Z256<br>VLH7 | 72        | 256           | 32           | 32/2                            | 64           | LQFP    | 58        | 58/8              | 16+11        | 1, 22 ch                     |

| MKE15<br>Z128<br>VLL7 | 72        | 128           | 16           | 32/2                            | 100          | LQFP    | 89        | 89/8              | 16+12        | 1, 25 ch                     |

| MKE15<br>Z128<br>VLH7 | 72        | 128           | 16           | 32/2                            | 64           | LQFP    | 58        | 58/8              | 16+11        | 1, 22 ch                     |

Table 6. KE16Z64/32, KE15Z64/32 parts supporting one TSI module

| Product          | Frequency | Memory     |              | Package   |         | IO and ADO | Cchannel          |              | НМІ                          |

|------------------|-----------|------------|--------------|-----------|---------|------------|-------------------|--------------|------------------------------|

| Part<br>number   | MHz       | Flash (kB) | SRAM<br>(kB) | Pin count | Package | GPIOs      | GPIOs<br>(INT/HD) | ADC channels | TSI<br>[Number,<br>channels] |

| MKE16<br>Z64VLF4 | 48        | 64         | 8            | 48        | LQFP    | 42         | 42/6              | 12           | 1, 25 ch                     |

| MKE16<br>Z64VLD4 | 48        | 64         | 8            | 44        | LQFP    | 38         | 38/6              | 12           | 1, 22 ch                     |

| MKE15<br>Z64VLF4 | 48        | 64         | 8            | 48        | LQFP    | 42         | 42/6              | 12           | 1, 25 ch                     |

| MKE15<br>Z64VLD4 | 48        | 64         | 8            | 44        | LQFP    | 38         | 38/6              | 12           | 1, 22 ch                     |

| MKE16<br>Z32VLF4 | 48        | 32         | 4            | 48        | LQFP    | 42         | 42/6              | 12           | 1, 25 ch                     |

| MKE16<br>Z32VLD4 | 48        | 32         | 4            | 44        | LQFP    | 38         | 38/6              | 12           | 1, 22 ch                     |

| MKE15<br>Z32VLF4 | 48        | 32         | 4            | 48        | LQFP    | 42         | 42/6              | 12           | 1, 25 ch                     |

| MKE15<br>Z32VLD4 | 48        | 32         | 4            | 44        | LQFP    | 38         | 38/6              | 12           | 1, 22 ch                     |

| MKE15<br>Z64VFP4 | 48        | 64         | 8            | 40        | QFN     | 36         | 36/4              | 11           | 1, 23 ch                     |

| MKE15<br>Z32VFP4 | 48        | 32         | 4            | 40        | QFN     | 36         | 36/4              | 11           | 1, 23 ch                     |

KE17Z Dual Touch Sensing Interface (TSI) User Guide

## 1.4 TSI model comparison of KE1xZ family

<u>Table 7</u> shows the detailed TSI channel configuration for each KE1xZ part. It helps users to select the proper part number for touch application design.

Table 7. KE1xZ TSI channels for different package

|              |                          | KE17Z far                                    | nily with up                                                              | to 512 kB                               | Flash                                   | KE17Z fan                                                                 | nily with up                                                              | o to 256 kB                                                               | Flash                                          |                                                |                                                | KE15Z with<br>up to 256 kB<br>Flash                                        | KE16Z far<br>Flash                                                           | mily with uլ                                                                 | o to 64 kB                              |

|--------------|--------------------------|----------------------------------------------|---------------------------------------------------------------------------|-----------------------------------------|-----------------------------------------|---------------------------------------------------------------------------|---------------------------------------------------------------------------|---------------------------------------------------------------------------|------------------------------------------------|------------------------------------------------|------------------------------------------------|----------------------------------------------------------------------------|------------------------------------------------------------------------------|------------------------------------------------------------------------------|-----------------------------------------|

| TSI n        | nodule                   | 2                                            |                                                                           | 1                                       |                                         | 2                                                                         |                                                                           |                                                                           | 1                                              |                                                |                                                | 1                                                                          | 1                                                                            |                                                                              |                                         |

| Pack         | age                      | KE17<br>Z512<br>100LQFP                      | KE17<br>Z512<br>64LQFP                                                    | KE13<br>Z512<br>100LQFP                 | KE13<br>Z512<br>64LQFP                  | KE17Z<br>100LQFP                                                          | KE17Z<br>64LQFP                                                           | KE17Z<br>48LQFP                                                           | KE13Z<br>100LQFP                               | KE13Z<br>64LQFP                                | KE13Z<br>48LQFP                                | KE15Z 100/64<br>LQFP                                                       | KE16Z/<br>KE15Z<br>48LQFP                                                    | KE16Z/<br>KE15Z<br>44LQFP                                                    | KE15Z<br>40QFN                          |

| Part ı       | number                   | MKE17<br>Z512<br>VLL9                        | MKE17<br>Z512<br>VLH9                                                     | MKE13<br>Z512<br>VLL9                   | MKE13<br>Z512<br>VLH9                   | MKE17<br>Z256<br>VLL7<br>MKE17<br>Z128<br>VLL7                            | MKE17<br>Z256<br>VLH7<br>MKE17<br>Z128<br>VLH7                            | MKE17<br>Z256<br>VLF7<br>MKE17<br>Z128<br>VLF7                            | MKE13<br>Z256<br>VLL7<br>MKE13<br>Z128<br>VLL7 | MKE13<br>Z256<br>VLH7<br>MKE13<br>Z128<br>VLH7 | MKE13<br>Z256<br>VLF7<br>MKE13<br>Z128<br>VLF7 | MKE15Z256<br>VLL7 MKE15<br>Z128VLL7<br>MKE15Z256<br>VLH7 MKE15<br>Z128VLH7 | MKE16<br>Z64VLF4<br>MKE15<br>Z64VLF4<br>MKE16<br>Z32VLF4<br>MKE15<br>Z32VLF4 | MKE16<br>Z64VLD4<br>MKE15<br>Z64VLD4<br>MKE16<br>Z32VLD4<br>MKE15<br>Z32VLD4 | MKE15<br>Z64VFP4<br>MKE15<br>Z32VFP4    |

| Frequ        | uency                    | 96 MHz                                       | 96 MHz                                                                    | 96 MHz                                  | 96 MHz                                  | 72 MHz                                                                    | 72 MHz                                                                    | 72 MHz                                                                    | 72 MHz                                         | 72 MHz                                         | 72 MHz                                         | 72 MHz                                                                     | 48 MHz                                                                       | 48 MHz                                                                       | 48 MHz                                  |

| Flash        | 1                        | 512 kB                                       | 512 kB                                                                    | 512 kB                                  | 512 kB                                  | 256<br>KB/128<br>KB                                                       | 256<br>KB/128<br>KB                                                       | 256<br>KB/128<br>KB                                                       | 256<br>KB/128<br>KB                            | 256<br>KB/128<br>KB                            | 256<br>KB/128<br>KB                            | 256 KB/128 KB                                                              | 64 KB/32<br>KB                                                               | 64 KB/32<br>KB                                                               | 64 KB/32<br>KB                          |

| Max.<br>supp | keys<br>ort              | 98                                           | 95                                                                        | 49                                      | 46                                      | 98                                                                        | 95                                                                        | 39                                                                        | 49                                             | 46                                             | 19                                             | 49                                                                         | 49                                                                           | 33                                                                           | 47                                      |

|              | Self-cap<br>mode<br>nels | 50-ch<br>(TSI0:25-<br>ch,<br>TSI1:25-<br>ch) | 47-ch<br>(TSI0:22-<br>ch,<br>TSI1:25-<br>ch)                              | 25-ch<br>(TSI0:25-<br>ch)               | 22-ch<br>(TSI0:22-<br>ch)               | 50-ch<br>(TSI0:25-<br>ch,<br>TSI1:25-<br>ch)                              | 47-ch<br>(TSI0:22-<br>ch,<br>TSI1:25-<br>ch)                              | 31-ch<br>(TSI0:15-<br>ch,<br>TSI1:16-<br>ch)                              | 25-ch<br>(TSI0:25-<br>ch)                      | 22-ch<br>(TSI0:22-<br>ch)                      | 15-ch<br>(TSI0:15-<br>ch)                      | 25-ch<br>(TSI0:25-ch)                                                      | 25-ch<br>(TSI0:25-<br>ch)                                                    | 22-ch<br>(TSI0:22-<br>ch)                                                    | 23-ch<br>(TSI0:23-<br>ch)               |

|              | Mutual-<br>cap mode      | TX/6-ch,<br>RX/6-ch;                         | 24-ch<br>(TSI0:<br>TX/6-ch,<br>RX/6-ch;<br>TSI1:TX/6-<br>ch, RX/6-<br>ch) | 12-ch<br>(TSI0:<br>TX/6-ch,<br>RX/6-ch) | 12-ch<br>(TSI0:<br>TX/6-ch,<br>RX/6-ch) | 24-ch<br>(TSI0:<br>TX/6-ch,<br>RX/6-ch;<br>TSI1:TX/6-<br>ch, RX/6-<br>ch) | 24-ch<br>(TSI0:<br>TX/6-ch,<br>RX/6-ch;<br>TSI1:TX/6-<br>ch, RX/6-<br>ch) | 16-ch<br>(TSI0:<br>TX/2-ch,<br>RX/6-ch;<br>TSI1:TX/6-<br>ch, RX/2-<br>ch) | 12-ch<br>(TSI0:<br>TX/6-ch,<br>RX/6-ch)        | 12-ch<br>(TSI0:<br>TX/6-ch,<br>RX/6-ch)        | 8-ch<br>(TSI0:<br>TX/2-ch,<br>RX/6-ch)         | 12-ch (TSI0:<br>TX/6-ch, RX/6-<br>ch)                                      | 12-ch<br>(TSI0:<br>TX/6-ch,<br>RX/6-ch)                                      | 9-ch<br>(TSI0:<br>TX/4-ch,<br>RX/5-ch)                                       | 12-ch<br>(TSI0:<br>TX/6-ch,<br>RX/6-ch) |

KE17ZDTSIUG

All information provided in this document is subject to legal disclaimers.

KE17Z Dual Touch Sensing Interface (TSI) User Guide

Table 7. KE1xZ TSI channels for different package...continued

|      |                           | KE17Z far                                                                                                               | nily with u                    | p to 512 kB                                                                            | S Flash                                                                                                                 | KE17Z far                                             | nily with u                                           | o to 256 kB                                                                          | 3 Flash                                               |                                                       |                                                                                      | KE15Z with<br>up to 256 kB<br>Flash | KE16Z far<br>Flash                | nily with u                           | p to 64 kB                        |

|------|---------------------------|-------------------------------------------------------------------------------------------------------------------------|--------------------------------|----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|--------------------------------------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|--------------------------------------------------------------------------------------|-------------------------------------|-----------------------------------|---------------------------------------|-----------------------------------|

| TSI0 | Self-cap<br>channel       | 25-ch<br>TSI0[0:24]                                                                                                     | 22-ch<br>TSI0[0:12]<br>[16:24] | 25-ch<br>,TSI0[0:24]                                                                   | 22-ch<br>TSI0[0:12]<br>[16:24]                                                                                          | 25-ch<br>TSI0[0:24]                                   | 22-ch<br>TSI0[0:12]<br>[16:24]                        | 15-ch<br>TSI0[0-<br>1,6-<br>12,16-<br>18,22-24]                                      | 25-ch<br>TSI0[0:24]                                   | 22-ch<br>TSI0[0:12]<br>[16:24]                        | 15-ch<br>TSI0[0-<br>1,6-<br>12,16-<br>18,22-24]                                      | 25-ch<br>TSI0[0:24]                 | 25-ch<br>TSI0[0:24]               | 22-ch<br>TSI0[0:1,<br>4:10,<br>12:24] | 23-ch<br>TSI0[0:18,<br>20:23]     |

|      | Mutual-<br>cap<br>channel | TX[0:5],<br>RX[6:11]                                                                                                    | TX[0:5],<br>RX[6:11]           | TX[0:5],<br>RX[6:11]                                                                   | TX[0:5],<br>RX[6:11]                                                                                                    | TX[0:5],<br>RX[6:11]                                  | TX[0:5],<br>RX[6:11]                                  | TX[0:1],<br>RX[6:11]                                                                 | TX[0:5],<br>RX[6:11]                                  | TX[0:5],<br>RX[6:11]                                  | TX[0:1],<br>RX[6:11]                                                                 | TX[0:5],<br>RX[6:11]                | TX[0:5],<br>RX[6:11]              | TX[0:1,<br>4:5],<br>RX[6:10]          | TX[0:5],<br>RX[6:11]              |

|      | Shield<br>channel         | Up to 25<br>shield<br>channels:<br>CH4,<br>CH12,<br>CH21,<br>CH24 are<br>enhanced<br>TSI<br>channels<br>than<br>others. |                                | Up to 25 shield channels: CH4, CH12, CH21, CH24 are enhanced TSI channels than others. | Up to 22<br>shield<br>channels:<br>CH4,<br>CH12,<br>CH21,<br>CH24 are<br>enhanced<br>TSI<br>channels<br>than<br>others. | Three<br>shield<br>channels:<br>CH4,<br>CH12,<br>CH21 | Three<br>shield<br>channels:<br>CH4,<br>CH12,<br>CH21 | One<br>shield<br>channel:<br>CH12                                                    | Three<br>shield<br>channels:<br>CH4,<br>CH12,<br>CH21 | Three<br>shield<br>channels:<br>CH4,<br>CH12,<br>CH21 | One<br>shield<br>channel:<br>CH12                                                    | One shield<br>channel: CH12         | One<br>shield<br>channel:<br>CH12 | One<br>shield<br>channel:<br>CH12     | One<br>shield<br>channel:<br>CH12 |

|      | Comment                   |                                                                                                                         | No CH13,<br>CH14,<br>CH15      |                                                                                        | No CH13,<br>CH14,<br>CH15                                                                                               |                                                       | No CH13,<br>CH14,<br>CH15                             | No CH2,<br>CH3,<br>CH4,<br>CH5,<br>CH13,<br>CH14,<br>CH15,<br>CH19,<br>CH20,<br>CH21 |                                                       | No CH13,<br>CH14,<br>CH15                             | No CH2,<br>CH3,<br>CH4,<br>CH5,<br>CH13,<br>CH14,<br>CH15,<br>CH19,<br>CH20,<br>CH21 |                                     |                                   | No CH2,<br>CH3,<br>CH11               | No CH19,<br>CH24                  |

| TSI1 | Self-cap<br>channel       | 25-ch<br>TSI0[0:<br>24]                                                                                                 | 25-ch<br>TSI1[0:<br>24]        | NA                                                                                     | NA                                                                                                                      | 25-ch<br>TSI1[0:<br>24]                               | 25-ch<br>TSI1[0:<br>24]                               | 16-ch<br>TSI1[0-<br>7,11-<br>12,15-<br>18,23-24]                                     |                                                       |                                                       |                                                                                      | NA                                  | NA                                | NA                                    | NA                                |

KE17Z Dual Touch Sensing Interface (TSI) User Guide

Table 7. KE1xZ TSI channels for different package...continued

|                           | KE17Z far            | nily with up to 5                                                                                                       | 12 kB Flash | KE17Z fai                                             | mily with u                                           | p to 256 kB                                                                   | Flash |   |   | KE15Z with<br>up to 256 kB<br>Flash | KE16Z fan<br>Flash | nily with up | to 64 kB |

|---------------------------|----------------------|-------------------------------------------------------------------------------------------------------------------------|-------------|-------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------------------------------|-------|---|---|-------------------------------------|--------------------|--------------|----------|

| Mutual-<br>cap<br>channel | TX[0:5],<br>RX[6:11] | TX[0:5],<br>RX[6:11]                                                                                                    |             | TX[0:5],<br>RX[6:11]                                  | TX[0:5],<br>RX[6:11]                                  | TX[0:5],<br>RX[7,11]                                                          |       |   |   |                                     |                    |              |          |

| Shield<br>channel         |                      | Up to 25<br>shield<br>channels:<br>CH4,<br>CH12,<br>CH21,<br>CH24 are<br>enhanced<br>TSI<br>channels<br>than<br>others. |             | Three<br>shield<br>channels:<br>CH4,<br>CH12,<br>CH21 | Three<br>shield<br>channels:<br>CH4,<br>CH12,<br>CH21 | Two<br>shield<br>channels:<br>CH4,<br>CH12                                    |       |   |   |                                     |                    |              |          |

| Comment                   |                      |                                                                                                                         |             |                                                       |                                                       | No CH8,<br>CH9,<br>CH10,<br>CH13,<br>CH14,<br>CH19,<br>CH20,<br>CH21,<br>CH22 |       |   |   |                                     |                    |              |          |

| tasheet                   | KE1xZP10             | 00M96SF0                                                                                                                | ı           | KE1xZP10                                              | 00M72SF1                                              | 1                                                                             |       | ı | ı | KE1xZP100<br>M72SF0                 | KE1xZP48           | M48SF0       |          |

Figure 2 shows the assignment of dual TSI channels on the three packages of KE17Z. Compared with the KE17Z 100LQFP, the TSI channels marked in yellow are not supported in the KE17Z 64 LQFP. The ones marked in yellow and red are TSI channels not supported in K17Z 48 LQFP.

#### KE17Z Dual Touch Sensing Interface (TSI) User Guide

KE17ZDTSIUG

KE17Z Dual Touch Sensing Interface (TSI) User Guide

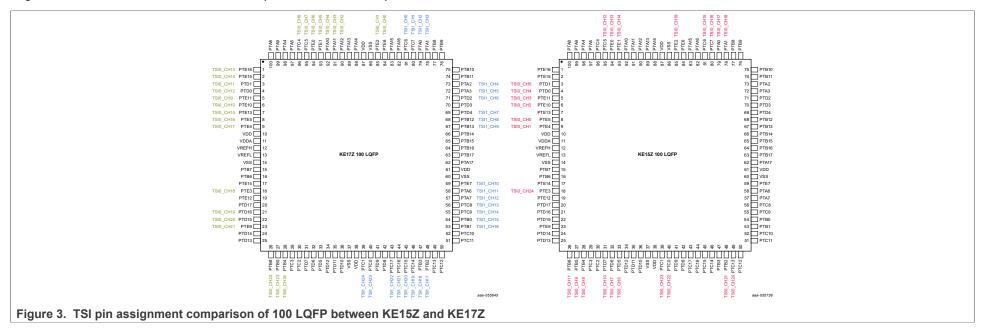

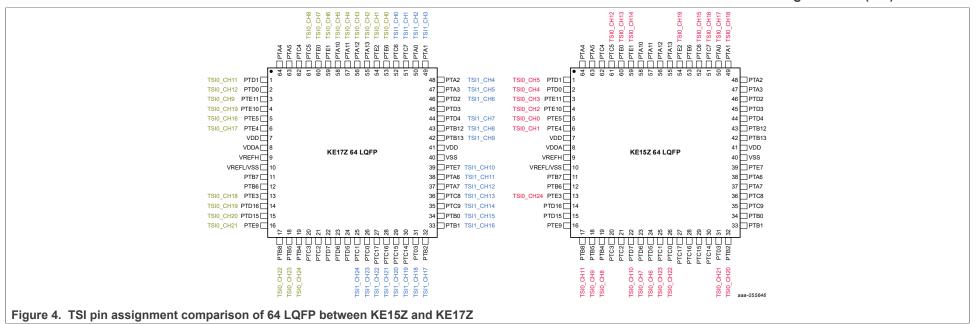

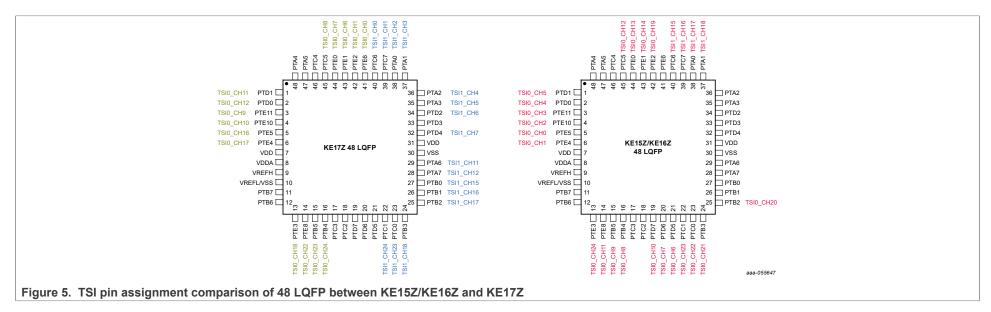

For the KE17Z in 100LQFP, 64LQFP, and 48LQFP packages, its pin assignment is compatible with the KE15Z. That is, the number and position of GPIO pins are the same. But the TSI channel assignment of KE17Z is different from KE15Z. To migrate the touch code from KE15Z to KE17Z, see <u>Figure 3</u>, <u>Figure 4</u>, and <u>Figure 5</u> for the TSI channel assignment. For more migration details, see the *Migration Guide from KE15Z256 to KE17Z256* (document <u>AN13429</u>) and the *Migration Guide from MT256P to MT512X* (document <u>AN14202</u>)

#### KE17Z Dual Touch Sensing Interface (TSI) User Guide

KE17Z Dual Touch Sensing Interface (TSI) User Guide

## 1.5 KE17Z dual TSI evaluation board

X-KE17Z-TSI-EVB is a touch sensing reference design including multiple touch patterns based on the 5 V Robust KE17Z MCU of NXP. It has dual-TSI modules and supports up to 50 touch channels, all demonstrated on the board.

Figure 6. X-KE17Z-TSI-EVB, KE17Z dual TSI evaluation board

## 2 TSI self-cap mode introduction

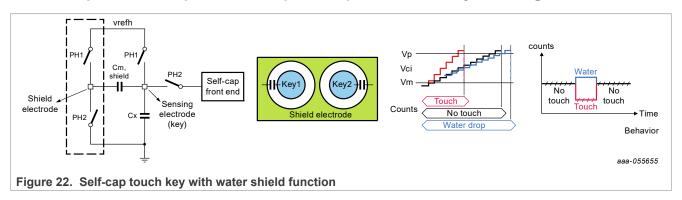

The sensor structure and electric field distribution between self-cap sensor and mutual-cap sensor are different.

## 2.1 Self-cap touch sensor

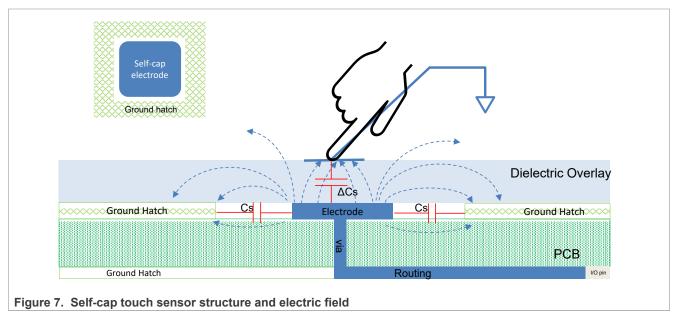

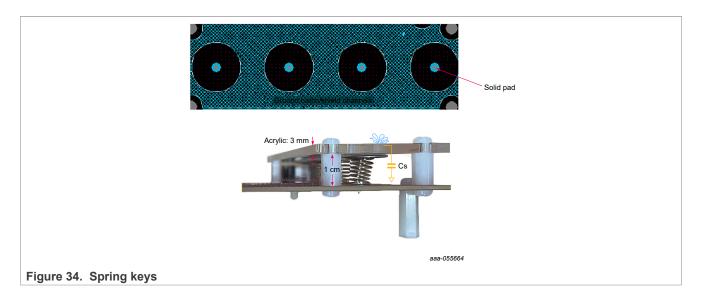

In self-cap mode, TSI requires only one pin for each touch sensor. As shown in <u>Figure 7</u>, capacitance exists between electrode to system ground. Touch changes the field through the human body and creates extra capacitance.

Self-cap touch sensor structure:

- Cs: Intrinsic self-capacitance. 10 50 pF as usual.

- ΔCs: Touch generated self-capacitance. 0.3 2 pF as usual.

- Sensitivity of sensor: ΔCs/Cs. 1 10 % as usual.

#### 2.2 Self-cap sensing mode

There are three modes of self-cap mode:

- · Basic self-cap mode

- · Noise cancellation mode

- · Sensitivity boost mode

The noise cancellation mode and sensitivity boost mode cannot be enabled at same time. The following describes the three modes.

#### 2.2.1 Basic self-cap sensing mode

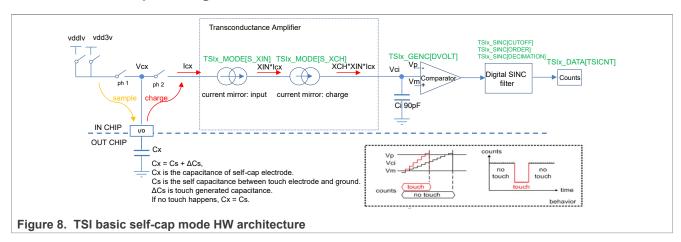

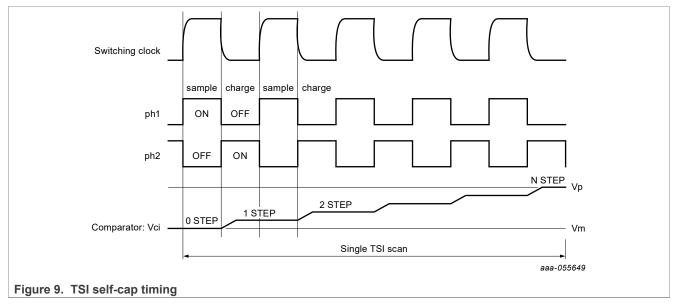

Inside the TSI IP module, the TSI scan is operated by non-overlapping clock ph1/ph2 and trans-conductance amplifier.

There are two phases controlled by the ph1 and ph2 respectively for the TSI scan module:

- Sample phase: The switch ph1 controls the sample phase. When ph1 turns on, the external touch electrode

C<sub>x</sub> is charged by vdd3v.

- Charge phase: The switch ph2 controls the charge phase. When ph1 turns off and then ph2 turns on, the

charge on the capacitor C<sub>x</sub> flows to the internal integrated capacitor Ci, which generates the average current

I<sub>cx</sub>.

Via the trans-conductance amplifier, the  $I_{cx}$  are amplified to charge Ci and the voltage  $V_{ci}$  ramps on Ci.  $V_{ci}$  is detected by the comparator, when the  $V_{ci}$  becomes larger than the pre-setting  $V_p$ ,  $C_i$  is discharged to negative reference  $V_m$ . Then the next scanning cycle continues.

The digital SINC filter controls the scan cycle. The digital SINC filter is a digital decimation filter for filtering out the low frequency noise from EMC. The digital SINC detects and accumulates the filter number of  $V_{ci}$  ramp up steps in per cycle. The digital SINC filter outputs the total counter, which can be read from TSIX DATA[TSICNT]. The software uses the counts to detect touch.

KE17ZDTSIUG

All information provided in this document is subject to legal disclaimers

When touch happens, input capacitance  $C_x$  increases. The charging current of  $C_i$  becomes larger and then the number of  $V_{ci}$  ramp up steps is reduced. The output count of the digital SINC filter is reduced, so the value of TSIX DATA[TSICNT] is decreased.

#### 2.2.2 Noise cancellation mode of self-cap

If the touch sensor encounters strong low frequency noise, noise cancellation can be activated by setting TSIX MODE[S NOISE].

In the noise cancellation mode, vdd3v, and vddlv (1.2 V) are dual sample voltages. Two phases exist in noise cancellation architecture:

- Charging phase of Ci when vdd3v is on and vddlv is off

- Discharging phase of C<sub>i</sub> when vdd3v is off and vddlv is on

Two switching clock cycles cost to samples twice, which includes charging phase (sampling vdd3v) and discharging phase (sampling vddIv). The input current of C<sub>i</sub> equals to the charging phase current abstract discharging phase current. At the end of each second phase, low frequency noise is subtracted. In a long integration period, the noise induced error can be canceled.

#### 2.2.3 Sensitivity boost mode of self-cap

The larger parasitic capacitance causes the low sensitivity. The low sensitivity results in the difficulty to recognize the touch event. For example, when the touch overlay is thick, it becomes hard to detect a touch event correctly.

To increase the sensitivity, enable a sensitivity-boost feature by removing part parasitic capacitance virtually. So, the touch works well under the thicker overlay with sensitivity boost enabled.

**Note:** The capacitance to be removed cannot be configured more than the intrinsic capacitance of the touch key. Otherwise, it causes the sensitivity invalid.

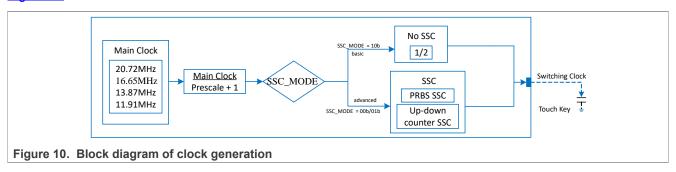

#### 2.3 Clock generation

The clock generation determines the TSI scan speed. The maximum frequency of TSI is about 10 MHz.

The TSI module is only clocked by the main clock, which is generated by the TSI module itself without any other external clock source. The main clock has four ranges of frequency. It can be divided into the switching clock, which is used to control the ph1/ph2 switching speed and finally determines the whole scan time, as shown in Figure 10.

- When SSC\_MODE = 10b, the switching clock is divided from the main clock directly, as the basic clock generation.

- When SSC\_MODE = 00b/01b, the switching clock is generated from the SSC module, as the advanced clock generation.

KE17ZDTSIUG

All information provided in this document is subject to legal disclaimers.

#### 2.3.1 Basic clock generation

Equation 1 is the basic clock generation, when TSIx\_SSC0[SSC\_MODE] = 10b.

Switching Clock =

$$\frac{Main\ Clock}{SSC\ PRESCALE\ NUM\ +\ 1}$$

$\times$   $\frac{1}{2}$  (1)

Table 8. Main clock setting

| Register         | Value | Main clock (MHz) |

|------------------|-------|------------------|

|                  | 00    | 20.72            |

| TSI_MODE[SETCLK] | 01    | 16.65            |

|                  | 10    | 13.87            |

|                  | 11    | 11.91            |

Table 9. Divider setting

| Register | Value    | SSC_PRESCALE_NUM + 1 |

|----------|----------|----------------------|

|          | 00000000 | divide 1             |

|          | 00000001 | divide 2             |

|          |          |                      |

|          | 11111111 | divide 256           |

There is an example of the basic clock generation, the main clock as 16.65 MHz, the divider as 16, and the result of switching clock is 1.04 MHz.

To use no SSC switching clock with a frequency of 1 MHz,

- Set SETCLK < 1:0 > to **01b** to get the main clock = 16.65 MHz.

- Set SSC\_MODE < 1:0 > to **10b** to disable the SSC function.

- Set SSC\_PRESCALE\_NUM < 7:0 > to **00000111b** to get division 8. When SSC mode is disabled, the frequency is *main clock/[(SSC\_PRESCALE\_NUM+1) × 2]*.

- Keep other registers in TSIx SSC0, TSIx SSC1, and TSIx SSC2 as the default value.

Switching Clock =

$$\frac{Main\ Clock}{Divider}$$

×  $\frac{1}{2}$  =  $\frac{16.65\ MHz}{8}$  ×  $\frac{1}{2}$  = 1.04 MHz

#### 2.3.2 Advanced clock generation, spread spectrum clocking

The Spread Spectrum Clocking (SSC) increases the noise immunity to RF interference and spreads the emissions.

With the SSC enabled (TSIx\_SSC0[SSC\_MODE] = 00/01b), the switching clock is generated by the SSC module, other than the direct divided main clock.

In the Self-cap mode, changing the SSC charge time does not affect the final scan result. It changes the total scan time as it changes the switching clock frequency.

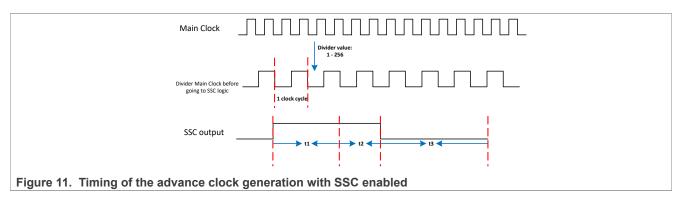

If SSC mode is enabled, the timing of the switching clock generation is as shown in Figure 11.

KE17ZDTSIUG

All information provided in this document is subject to legal disclaimers.

As shown in <u>Figure 11</u>, t1 and t2 determine the SSC output 1's period and t3 determines the SSC output 0's period.

Equation 3 shows the advanced clock generation, with SSC enabled when TSIx SSC0[SSC MODE] = 00/01b.

Switching Clock =

$$\frac{Main\ Clock}{\left(SSC\_PRESCALE\_NUM + 1\right) \times [t1+t2+t3]}$$

(3)

- When TSIx SSC0[SSC MODE] = 00b, t2 can be random (PRBS).

- When TSIx\_SSC0[SSC\_MODE] = 01b, t2 can be the range of TSIx\_SSC2[MOVE\_NOCHARGE\_MIN] to TSIx\_SSC2[MOVE\_NOCHARGE\_MAX].

The generation of the switching clock includes:

• The switching clock can be generated as a pseudo random clock using the Pseudo-Random Binary Sequence (PRBS) method by setting TSI SSC0[SSC MODE] = 00. t2 is configured as the random width.

Table 10. TSI SSC0[SSC MODE] = 00, PRBS mode

| Variable | Register                     | Clock cycle | Description        |

|----------|------------------------------|-------------|--------------------|

| t1       | TSIx_SSC0[BASE_NOCHARGE_NUM] | 1 - 16      | SSCHighWidth       |

| t2       | TSIx_SSC0[PRBS_OUTSEL]       | 2 - 15      | SSCHighRandomWidth |

| t3       | TSIx_SSC0[CHARGE_NUM]        | 1 - 16      | SSCLowWidth        |

Switching Clock can be generated in a configurable up-down counter method by setting

TSI\_SSC0[SSC\_MODE] = 01. The range of t2 is limited by TSI\_SSC2 [MOVE\_NOCHARGE\_MIN] and

TSI\_SSC2 [MOVE\_NOCHARGE\_MAX].

Table 11. TSI\_SSC0[SSC\_MODE] = 01, up-down counter mode

| Variable | Register                                                    | Clock cycle | Description         |

|----------|-------------------------------------------------------------|-------------|---------------------|

| t1       | TSI_SSC0[BASE_NOCHARGE_NUM]                                 | 1 - 16      | SSCHighWidth        |

| t2       | TSI_SSC2[MOVE_NOCHARGE_MIN] TSI_<br>SSC2[MOVE_NOCHARGE_MAX] | MAX-MIN     | SSCHighCounterWidth |

| t3       | TSI_SSC0[CHARGE_NUM]                                        | 1 ~ 16      | SSCLowWidth         |

There is an example of the advance clock generation attached below.

To use PRBS mode SSC switching clock with a central frequency of 1 MHz.

- Set SETCLK<1:0> to 01b to get the main clock = 16.65 MHz.

- Set SSC PRESCALE NUM<7:0> to 0b to get division 1. The divided main clock is 16.65 MHz.

- Set  $SSC_MODE<1:0>$  to 00b to enable PRBS SSC mode. SSC t2 is random.

- Set BASE\_NOCHARGE\_NUM<3:0> to 0100b to set t1 = 5. The basic length of SSC output bit 1's period is five clock cycle of the divided main clock.

KE17ZDTSIUG

All information provided in this document is subject to legal disclaimers.

- Set PRBS\_OUTSEL<3:0> to **0110b** to set the t2 range from 1 to 6. The average of t2 is 3.5. t2 is the random length of SSC output bit 1's period. It is a 3.5 clock cycle of the divided main clock.

- Set CHARGE\_NUM<3:0> to **0110b** to set t3 = 7. The basic length of SSC output bit 1's period is seven clock cycle of the divided main clock.

- Keep other registers in TSIX SSC0, TSIX SSC1, and TSIX SSC2 as default value.

- Then, the switching clock = 16.65 MHz/[(5+3.5+7) \* (0 + 1)] = 1.074 MHz. The switching clock is spectrum spread pulse.

$$Switching\ Clock\ =\ \frac{Main\ Clock}{\left(SSC\_PRESCALE\_NUM\ +\ 1\right) \left(SSCHighWidth(t1)+SSCHighRandomWidth(t2)+SSCLowWidth(t3)\right)} = \frac{16.65MHz}{(0+1) \left((5+3.5+7)\right)}\ =\ 1.074MHz \tag{4}$$

#### 2.4 TSI scan time and scan result accumulation

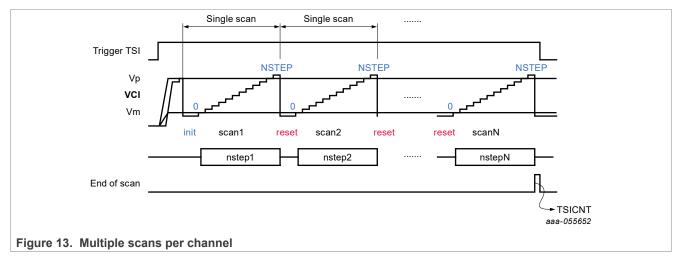

TSI supports multiple scans per channel. That is, to get better Signal-to-Noise Ratio (SNR) and resolution, TSI performs multiple scans. The final scan result is accumulated in TSI\_DATA[TSICNT] counter as the NSTEP multiplied by the number of scans, and the scan time is multiple of single TSI scan time.

#### Note:

With higher **Decimation**, the number of scans is increased. The result is the physically longer TSI counter accumulation and increased resolution.

If the **Order** is higher than 1, then the scan number physically executed by TSI is smaller than the scan number calculated by HW. It is beneficial to get the higher resolution.

#### 2.4.1 TSI single scan process

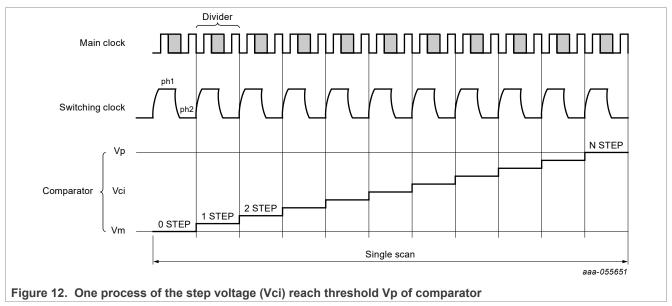

<u>Figure 12</u> shows one process that the step voltage  $(V_{ci})$  reaches threshold  $V_p$  of comparator from  $V_m$ . If  $V_{ci}$  reaches the threshold  $V_p$ , the voltage VCI is discharged to  $V_m$  for next scanning. The step voltage  $(V_{ci})$  depends on touch sensor and IP configuration.

Calculate NSTEP in basic self-cap mode.

Equation 5 is the basic equation of the self-cap mode. NSTEP is the V<sub>ci</sub> steps of TSI single scan in self-cap mode.

$$NSTEP = \frac{Ci \times (Vp - Vm)}{vdd3v \times Cs \times S \_XIN \times S \_XCH}$$

(5)

KE17ZDTSIUG

All information provided in this document is subject to legal disclaimers.

Equation 6 is the basic equation of the scan time.  $T_{nstep}$  is the time cost of TSI single scan in **self-cap** mode.

$$Tnstep = NSTEP \times \frac{1}{F_{SW}} \tag{6}$$

- C<sub>i</sub>: Typical 90 pF. The integrated capacitance inside the TSI module.

- Vdd3v: Typical 3.3 V. PMC internal voltage regulator generates the analog power supply voltage.

- V<sub>p</sub>, V<sub>m</sub>: Configurable, dual reference voltage, which can be configured by TSIx\_GENCS[DVOLT].

- S\_XIN, S\_XCH: Configurable, the parameters of analog front end, configured TSIx\_MODE[S\_XIN], TSIx\_MODE[S\_XCH].

- F<sub>sw</sub>: Configurable, the switching clock frequency.

- Cs: The self-capacitance of touch sensor.

- 2. Equation 7 is a new equation to calculate NSTEP when noise cancellation mode is enabled.

$$NSTEP = \frac{2 \times Ci \times (Vp - Vm)}{(vdd3v - vddlv) \times Cs \times S_X IN \times S_X CH}$$

$$(7)$$

Vddlv: The internal power supply voltage. Typical 1.2 V.

3. Calculate NSTEP in basic self-cap mode.

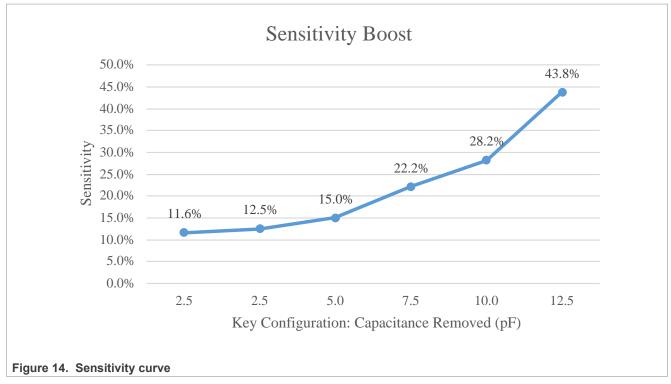

The TSI self-cap mode implements the sensitivity boost by canceling the external intrinsic capacitance. The value of the capacitance to be canceled ranges from 2.5 pF to 20 pF, which is configurable in register TSI\_MODE[S\_CTRIM].

For example, given the intrinsic capacitance of the touch electrode is 20 pF (it can be calculated by NSTEP equation), setting the S\_CTRIM value as 5.0 pF can make the effective intrinsic capacitance become 15 pF. As the intrinsic sensitivity of the touch key is given by  $\Delta$ Cs/Cs, the less intrinsic capacitance would result in more sensitive touch response. With this sensitivity boost enabled, sensitivity can be improved to  $\Delta$ Cs/ (Cs-S\_CTRIM\*(S\_XDN/S\_XCH)).

The sensitivity boost feature in self-cap mode can be activated by setting  $\mathtt{TSI\_MODE[S\_SEN]}$ . Equation 8 is a new equation to calculate NSTEP when sensitivity boost function is enabled.

$$NESTP = \frac{Ci \cdot \langle Vp-Vm \rangle}{vdd3v \cdot \langle Cs-S\_CTRIM \cdot \langle S\_XDN/S\_XCH \rangle) \cdot s\_XIN \cdot s\_XCH}$$

(8)

- S\_CTRIM: Configurable, the capacitance to be removed.

- S XDN/S XCH: Configurable, the capacitance multiplier.

- The actual capacitance to be removed is S\_CTRIM × (S\_XDN/S\_XCH).

#### 2.4.2 TSI scan multiple rounds in self-cap mode

To minimize the noise deviation on the single scan, TSI supports multiple scans per channel. That is, TSI performs a single scan operation for many times from getting the trigger to the end of the scan.

KE17ZDTSIUG

All information provided in this document is subject to legal disclaimers.

Each time the TSI is triggered, multiple scans can be performed inside the TSI. The scan round is set by the registers ( $TSI\_SINC[DECIMATION]$ , [ORDER], and [CUTOFF]), ranged from 1 to  $32^2$ . When the  $TSI\_SINC[DECIMATION]$  is set to 0 (only once), the single scan is engaged.

The 16-bit counter accumulates all scan results until the scan number reaches a predefined number. To get the final scan result, read TSI DATA[TSICNT].

There are two kinds of scan number:

- For digital calculation to accumulate the final TSI scan result, as shown in Equation 7.

- For TSI IP to execute the scan action practically, as shown in Equation 8.

Scan Result:

$$TSICNT = NSTEP \times \frac{Decimation^{Order}}{Cutof f}$$

(9)

Scan Time:

$$Time = Tnstep \times Decimation \times Order$$

(10)

According to Equation 5, Equation 6, Equation 9, and Equation 10, the parameters of Decimation, Order and Cutoff, S XIN, S XCH, and (Vp -Vm) affect the final accumulated scan result and the total scan time.

Users must adjust the touch electrode according to different applications. The parameters of TSI can be adjusted comprehensively to achieve the best performance of TSI.

For example,

- Increase the voltage of (Vp-Vm) can reduce the effect of low frequency noise, but the scan time of TSI increases. The increase of <code>S\_XCH</code> and <code>S\_XIN</code> can increase the charging current of C<sub>i</sub> and shorten the scan time of TSI, but the noise increases. Therefore, when (Vp-Vm) increases, <code>S\_XCH</code> and <code>S\_XIN</code> can be reduced, which cannot only reduce the scanning time but also reduce the noise and enhance the sensitivity.

- Decimation, Order, and Cutoff increase the number of scans for the touch electrodes and enhance the antiinterference of the electrodes. At the same time, the scan time of the touch electrodes is also longer. Setting the Order as 2 is recommended as it can save scan time to achieve the same digital scan result.

#### 2.5 Scan time and sensitivity boost tests in self-cap mode

#### 2.5.1 Scan time test in self-cap mode

This chapter shows the one self-cap touch electrode scan time test results on X-KE17Z-TSI-EVB.

As shown in <u>Table 12</u>, given the NSTEP is 110 and Tnstep is 239 us by the measurement result of a single scan, shown as <u>Example 1</u>. The theoretical value can be calculated by <u>Equation 9</u> and <u>Equation 10</u>.

Table 12. Scan time test by changing the configuration of Decimation, Order, Cutoff

|   |                          |       |                | Configurations |       |        | Result            |                                    |                       |                                     |

|---|--------------------------|-------|----------------|----------------|-------|--------|-------------------|------------------------------------|-----------------------|-------------------------------------|

|   | Switching<br>Clock (MHz) | NSTEP | Tnstep<br>(µs) | Decimation     | Order | Cutoff | NSTEP<br>Multiple | Counter<br>(TSICNT) <sup>[1]</sup> | Real<br>Scan<br>Round | Scan<br>Time <sup>[2]</sup><br>(µs) |

| 1 | 0.52                     |       |                | 1              | 1     | 1      | 1                 | 110                                | 1                     | 239                                 |

| 2 | 0.52                     | 110   | 239            | 2              | 1     | 1      | 2                 | 220                                | 2                     | 448                                 |

| 3 | 0.52                     | 110   | 239            | 4              | 1     | 1      | 4                 | 440                                | 4                     | 869                                 |

| 4 | 0.52                     | 110   | 239            | 8              | 1     | 1      | 8                 | 880                                | 8                     | 1709                                |

| 5 | 0.52                     | 110   | 239            | 16             | 1     | 1      | 16                | 1760                               | 16                    | 3390                                |

| 6 | 0.52                     | 110   | 239            | 32             | 1     | 1      | 32                | 3520                               | 32                    | 6750                                |

| 7 | 0.52                     | 110   | 239            | 1              | 2     | 1      | 1                 | 110                                | 2                     | 449                                 |

KE17ZDTSIUG

All information provided in this document is subject to legal disclaimers.

Table 12. Scan time test by changing the configuration of Decimation, Order, Cutoff...continued

|    |                          |       |                | Configurations |       |        | Result            |                                    |                       |                                     |

|----|--------------------------|-------|----------------|----------------|-------|--------|-------------------|------------------------------------|-----------------------|-------------------------------------|

|    | Switching<br>Clock (MHz) | NSTEP | Tnstep<br>(µs) | Decimation     | Order | Cutoff | NSTEP<br>Multiple | Counter<br>(TSICNT) <sup>[1]</sup> | Real<br>Scan<br>Round | Scan<br>Time <sup>[2]</sup><br>(µs) |

| 8  | 0.52                     | 110   | 239            | 2              | 2     | 1      | 4                 | 440                                | 4                     | 869                                 |

| 9  | 0.52                     | 110   | 239            | 4              | 2     | 1      | 16                | 1760                               | 8                     | 1709                                |

| 10 | 0.52                     | 110   | 239            | 8              | 2     | 1      | 64                | 7040                               | 16                    | 3390                                |

| 11 | 0.52                     | 110   | 239            | 8              | 2     | 2      | 32                | 3520                               | 16                    | 3390                                |

<sup>[1]</sup> The Counter (TSICNT) is read from the register when debugging the code.

- Other conditions: Ci, 90 pF; vdd3v, 3.3 V; S XIN, 1/4; S XCH, 1/2.

- Example 1: Configure the Decimation, Order, and Cutoff as 1, and the final scan result is 110. TSI performs a scan operation for one time, and the scan time is 239 µs.

- Example 2: Change the Decimation to 2, and the final scan result becomes 220. TSI performs the scan twice, and the scan time is 448, about twice of the previous 239 µs.

- Example 10: Change the order to 2, and the final scan result becomes 110 \* 64 = 7040. TSI only performs a scan for 8 \* 2 = 16 times, and the scan time is 3390 μs, saving time by setting order = 2.

By comparing the test results when setting order to 1 and order to 2, the conclusion is:

Increasing TSI conversion result (TSICNT) means to cost longer scan time. When TSI performs multiple scans, it is recommended to set order to 2 to reduce interference and save touch electrode scan time. Then change the Decimation and Cutoff to adjust the TSI conversion result. Increasing TSI conversion result means longer scan time.

The scan time in this table is measured by the LPTMR module. That is, start LPTMR on the TSI scan start, stop LPTMR on the TSI scan end, and then read the LPTMR counter to estimate the time cost. There are some inevitable small errors and differences between LPTMR measurement and real TSI scan time.

#### 2.5.2 Sensitivity test result when sensitivity boost feature is enable

When the sensitivity boost function is enabled, NSTEP is calculated by <u>Equation 8</u>, and the calculation of TSICNT and scan time still uses <u>Equation 9</u> and <u>Equation 10</u>.

The sensitivity boost configurations include: S\_SEN Enable, S\_CTRIM, and Multiplier (S\_XDN/S\_XCH).

Table 13. Sensitivity boost configurations registers

| Variable           | Register          | Descriptions                                                      |

|--------------------|-------------------|-------------------------------------------------------------------|

| S_SEN Enable       | TSI_MODE[S_SEN]   | Enable a sensitivity boost by setting S_SEN to 1.                 |

| S_CTRIM            | TSI_MODE[S_CTRIM] | Remove the parasitic capacitance virtually, from 2.5 pF to 20 pF. |

| Multiplier: S_XDN/ | TSI_MODE[S_XDN]   | Multiplier factor when sensitivity boost is enabled.              |

| S_XCH              | TSI_MODE[S_XCH]   | Charge/discharge multiple                                         |

The removed capacitance is:

$$Cremoved = S_{CTRIM} \times \frac{S_{XDN}}{S_{XCH}}$$

(11)

KE17ZDTSIUG

All information provided in this document is subject to legal disclaimers.

<sup>[2]</sup> The actual **Scan time** is calculated by LPTMR module.

Table 14. Sensitivity test for sensitivity boost configurations

| Current Amplifier |       |                                 | Sensitivity     | Boost |                 | Intrinsic                 | Sensitivity                  |                   |  |

|-------------------|-------|---------------------------------|-----------------|-------|-----------------|---------------------------|------------------------------|-------------------|--|

| S_XIN             | s_хсн | Current Amplifier (S_XIN*S_XCH) | S_SEN<br>Enable | S_XDN | S_Ctrim<br>(pF) | C <sub>removed</sub> (pF) | capacitance<br>calculated Cx | calculated<br>(%) |  |

| 1/4               | 1/2   | 1/8                             | OFF             | 1/2   | 2.5             | 0.0                       | 16                           | 11.6              |  |

| 1/4               | 1/2   | 1/8                             | ON              | 1/2   | 2.5             | 2.5                       | 16                           | 12.5              |  |

| 1/4               | 1/2   | 1/8                             | ON              | 1/2   | 5.0             | 5.0                       | 16                           | 15.0              |  |

| 1/4               | 1/2   | 1/8                             | ON              | 1/2   | 7.5             | 7.5                       | 16                           | 22.2              |  |

| 1/4               | 1/2   | 1/8                             | ON              | 1/2   | 10.0            | 10.0                      | 16                           | 28.2              |  |

| 1/4               | 1/2   | 1/8                             | ON              | 1/2   | 12.5            | 12.5                      | 15                           | 43.8              |  |

From sensitivity calculate results, we can find out that the  $C_{removed}$  is the key configuration to the sensitivity boost feature. As  $C_{removed}$  increases, the sensitivity becomes better. That is, it is to recognize touch event. Therefore, users can adjust the  $S\_CTRIM$  and  $S\_XDN$  to quickly adjust the sensitivity of touch electrode recognition.

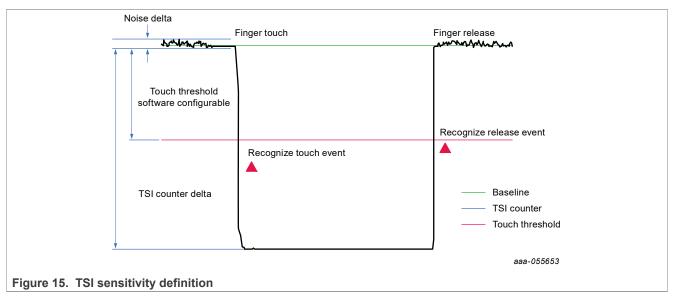

Figure 15 shows the definition of the sensitivity.

$$Sensitivity = \frac{TSI\_Counter\_Delter}{TSI\_Baseline} \times 100\%$$

(12)

The large sensitivity value means the stronger signal caused by finger touch.

Sensitivity around 10 % is recommended in self-cap mode.

## 3 TSI mutual-cap mode

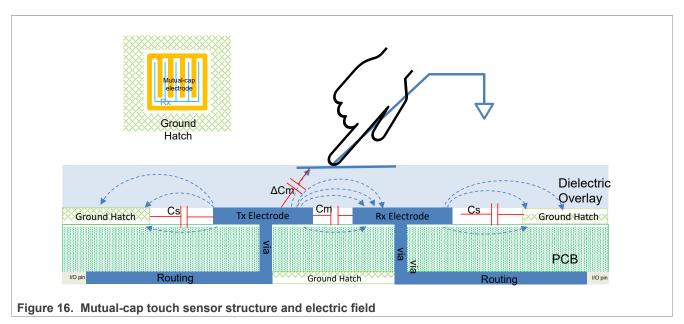

#### 3.1 Mutual-cap sensor

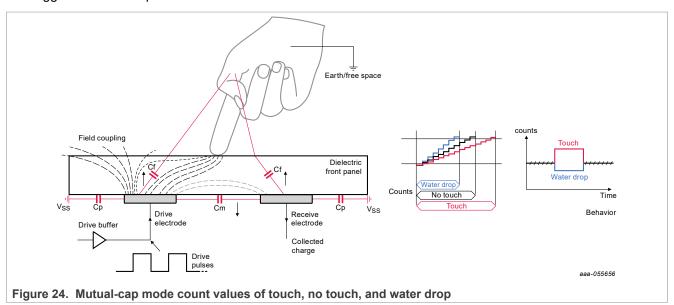

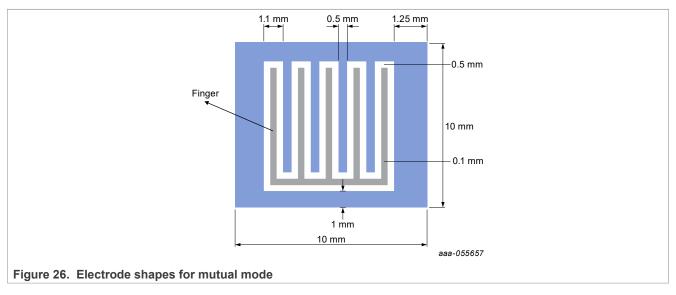

Mutual-cap mode measures the capacitance between two electrodes connected to two TSI channels. One of the TSI channels is used as transmit (TX) channel and the other one is used as receive (RX) channel.

For the two TSI instances of KE17Z, TSIx[5:0] can be used as TX channel by configuring  $TSIx\_MUL0[M\_SEL\_TX]$ . TSIx[11:6] can be used as RX channel by configuring  $TSIx\_MUL0[M\_SEL\_RX]$ . The mutual-cap touch electrode design of TSI0 and TSI1 is independent. Each TSI instance supports the design of 6 × 6 touch electrodes.

Touch changes the field through the human body and reduces the mutual capacitance. TSI IP is to convert the capacitance changing from the sensor to digital code for application.

#### Sensor structure:

- Cm: Intrinsic mutual cap. 2 10 pF as usual.

- ΔCm: Touch reduced mutual cap. 0.3 2 pF as usual.

- Cs: Parasitic self-cap. 10 50 pF as usual.

- Sensitivity of sensor: ΔCm/Cm. 1 20 % as usual.

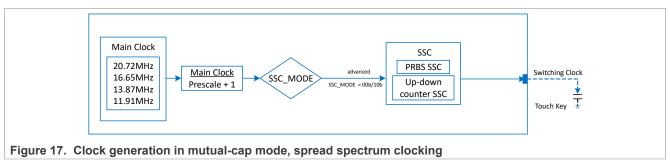

#### 3.2 Clock generation in mutual-cap mode

One difference to the self-mode clock, the **SSC** must be enabled for mutual mode to generate a switching clock, because the TSI RX signal in the mutual mode depends on the <code>TSI\_SSCO[CHARGE\_NUM]</code>. In the mutual mode, changing the SSC charge time changes the RX signal coupled from the TX channel and affects the final scan result.

SSC is enabled, the mutual mode shares the clock generation of the self-cap mode. For detailed configurations, see Section 2.3.2.

Equation 3 is used to calculate the Switching Clock when SSC is enabled.

#### 3.3 Mutual-cap sensing mode

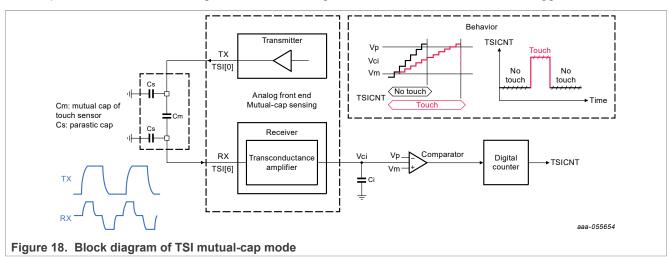

Mutual-cap sensing includes transmitter and receiver. Under clocking, the transmitter outputs pulses, which decouple through a mutual cap then reach the receiver site. The receiver amplifies the signal with a noise cancellation method. The method is similar as a charge transfer circuit in self-cap sensing. That is, convert to averaging charge current on integration cap  $C_i$ , which creates step voltage  $V_{ci}$ .

KE17ZDTSIUG

All information provided in this document is subject to legal disclaimers.

The step number of each scanning is accumulated to give a final count TSICNT for each trigger.

- $V_{pre}$  is selected by  ${\tt TSIx\_MUL1[M\_VPRE\_CHOOSE]}$ .

- ΔV: signal voltage RX received, decided by VDD5V × C<sub>m</sub>/(C<sub>m</sub> + C<sub>s</sub>).

- TX drive mode is controlled by TSIx MUL1[M MOD], -5 +5 V is selected in Figure 19.

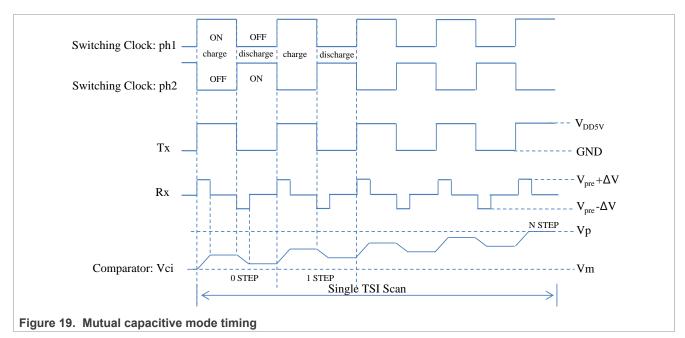

As shown in <u>Figure 18</u> and <u>Figure 19</u>, there are two phases controlled by the switching clock for the TSI mutual capacitive mode:

- Charge phase: The switch ph1 controls the charge phase, when ph1 turns on, the transmit channel outputs

pulses, which are coupled through the mutual capacitance C<sub>m</sub>. Receiver converts the received voltage pulse

(V<sub>pre</sub> + ΔV) to the current I<sub>charge</sub> through the resistor R<sub>s</sub>.

- Discharge phase: The switch ph2 controls the discharge phase, when ph1 turns off then ph2 turns on, the

transmit channel changes the voltage from V<sub>DD5V</sub> to -V<sub>DD5V</sub>, as TX drive mode is selected to output -5 +5 V

by configuring M\_MOD to 1. Receiver converts the received voltage change (Vpre-∆V) to the current I<sub>discharge</sub>

through Rs.

KE17ZDTSIUG

As the integrated  $C_i$  is charged/discharged by the mirrored/amplified current from the receiver, the voltage  $V_{ci}$  ramps on  $C_i$ . When  $V_{ci}$  becomes larger than the pre-setting  $V_p$ , the comparator stops this TSI scan round. TSI can scan multiple rounds by configuring the digital SINC filter (TSIx\_SINC) to filter out the low frequency noise. Accumulated sample results are recorded the as TSIx\_DATA[TSICNT].

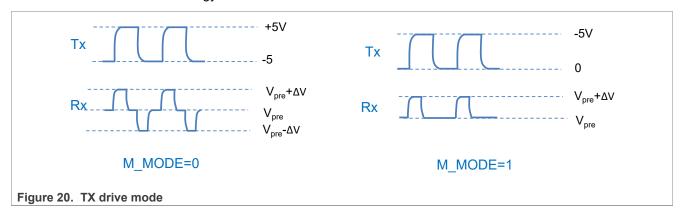

There are two drive modes of Transmitter. <u>Figure 20</u> shows the difference. In one switching clock cycle, when M\_MODE = 1, the voltage change value of RX terminal is  $\Delta V$ . When M\_MODE = 0, the voltage change value of RX terminal is 2 \*  $\Delta V$ , and the charging efficiency of Ci is also twice M\_MODE = 1. Setting M\_MODE to **0** is recommended as it is more energy efficient.

#### 3.3.1 Single scan in mutual-cap mode

The digital process in mutual mode is same as self-cap mode, as shown in <u>Figure 12</u> and <u>Figure 13</u>. C<sub>i</sub> ramp up steps in per cycle is detected and accumulated by digital SINC filter. Digital SINC filter outputs totally counter which can be read from TSIx\_DATA[TSICNT].

NSTEP is the result of TSI single scan in mutual-cap mode, as shown in Equation 13.

$$NSTEP = \frac{Ci \times (Vp-Vm) \times Rs}{\Delta V} \times \frac{M_-PMIRRORL}{M_-PMIRRORR} \times \frac{1}{t3}$$

(13)

- Ci: Fixed 90 pF, the integrated capacitance inside TSI module.

- V<sub>p</sub>, V<sub>m</sub>: Configurable, dual reference voltage which can be configured by DVOLT<1:0>.

- R<sub>s</sub>: Configurable, parameter of analog front end which can be configured by M\_SEN\_RES<3:0>.

- M\_PMIRRORL, M\_PMIRRORR: Configurable, the current multiplier.

- t3: Configurable, SSC output low period.

- $\Delta V$ : Signal voltage RX received, decided by VDD5V ×  $C_m/(C_m + C_s)$   $C_m$  is the mutual capacitance between the TX and RX touch electrode.  $C_s$  is the parasitic capacitance of the touch electrodes. When the mutual-cap electrode is touched,  $C_m$  is decreased,  $C_s$  is increased, and  $\Delta V$  is reduced. The value of NSTEP is increased and the accumulated sample results TSICNT also increase. Equation 14 is the basic equation of the scan time.  $T_{nstep}$  is the time cost of TSI single scan.

$$Tnestp = \frac{Cix(Vp-Vm)\times Rs}{\Delta V} \times \frac{M_{pMIRRORL}}{M_{pMIRRORR}} \times \frac{1}{t3} \times \frac{1}{Fsw}$$

(14)

• F<sub>sw</sub>: Configurable, the switching clock frequency in mutual-cap mode.

#### 3.3.2 TSI scan multiple rounds in mutual-cap mode

Same with the self-cap mode, the scan round in mutual-cap mode is set by the registers (TSI\_SINC[DECIMATION], [ORDER], and [CUTOFF]), ranged from 1 to 32<sup>2</sup>. The scan result and the scan time can be calculated with Equation 9 and Equation 10.

There is an example to calculate the scan result and scan time in mutual-cap mode.

KE17ZDTSIUG

All information provided in this document is subject to legal disclaimers.

#### Test cases:

1.  $\Delta V$  =100 mV, Rs=10k, Vp-Vm=1 V, Ci=90 pF, M\_PMIRRORL = 8, M\_PMIRRORR = M\_NMIRROR= 2, Tsw = 1  $\mu$ s, t3=0.25  $\mu$ s.

Use Equation 13 and Equation 14 to calculate:

NSTEP = 144, TNSTEP = 144 µs.

2. Dec = 8. Order = 2. Cutoff = 1:

Use Equation 9 and Equation 10 to calculate:

TSICNT =  $144 \times 64 = 9216$ , SCANTIME =  $144 \text{ us} \times 8 \times 2 = 2304 \text{ µs}$ .

Note: When using the mutual-cap mode, keep M PMIRRORR and M NMIRROR same.

#### 3.3.3 Scan time test in mutual-cap mode

The scan time determines how long the TSI finishes the scan and get conversion result.

Similar to the Self-cap mode configurations, the mutual mode also supports multiple scan rounds per channel, and the scan number is configured by TSI\_SINC [DECIMATION], [ORDER], and [CUTOFF].

<u>Table 15</u> shows the one mutual-cap touch electrode scan time test results on X-KE17Z-TSI-EVB. The actual **Scan Time** is calculated by LPTMR module. The **Counter (TSICNT)** is read from the register when debugging the code.

In <u>Table 15</u>, give the NSTEP as 388, and Tnstep is 315 µs by the measurement result of single scan, as shown in <u>Example 1</u>. The theoretical value can be calculated by <u>Equation 13</u> and <u>Equation 14</u>.

There are examples for scan time configurations, as shown in <u>Table 15</u>. Give the NSTEP as 388, and Tnstep is  $315 \mu s$  by the measurement of single scan.

By comparing <u>Example 5</u> and <u>Example 9</u>, you can find that when the TSI scan rounds are 16, the scan time of <u>Example 5</u> costs 4473 µs and the scan time of <u>Example 9</u> costs 2256 µs.

Setting order = 2 saves time so that the TSI can scan more touch electrodes in the same amount of time.

Table 15. Scan time test by changing the configuration of Decimation, Order, Cutoff

|    | Switching | ning  |                | Configuration | Configurations |        |                   | Result              |                   |                           |  |

|----|-----------|-------|----------------|---------------|----------------|--------|-------------------|---------------------|-------------------|---------------------------|--|

|    | _         | NSTEP | Tnstep<br>(µs) | Decimation    | Order          | Cutoff | NSTEP<br>multiple | Counter<br>(TSICNT) | Actual scan round | Real<br>LPTMR<br>measured |  |

| 1  | 1.28      | 388   | 315            | 1             | 1              | 1      | 1                 | 388                 | 1                 | 315                       |  |

| 2  | 1.28      | 388   | 315            | 2             | 1              | 1      | 2                 | 780                 | 2                 | 596                       |  |

| 3  | 1.28      | 388   | 315            | 4             | 1              | 1      | 4                 | 1552                | 4                 | 1147                      |  |

| 4  | 1.28      | 388   | 315            | 8             | 1              | 1      | 8                 | 3110                | 8                 | 2257                      |  |

| 5  | 1.28      | 388   | 315            | 16            | 1              | 1      | 16                | 6218                | 16                | 4473                      |  |

| 6  | 1.28      | 388   | 315            | 32            | 1              | 1      | 32                | 12448               | 32                | 8918                      |  |

| 7  | 1.28      | 388   | 239            | 1             | 2              | 1      | 1                 | 387                 | 2                 | 593                       |  |

| 8  | 1.28      | 388   | 239            | 2             | 2              | 1      | 4                 | 1550                | 4                 | 1145                      |  |

| 9  | 1.28      | 388   | 239            | 4             | 2              | 1      | 16                | 6220                | 8                 | 2256                      |  |

| 10 | 1.28      | 388   | 239            | 8             | 2              | 1      | 64                | 24828               | 16                | 4475                      |  |

| 11 | 1.28      | 388   | 239            | 8             | 2              | 2      | 32                | 12414               | 16                | 4463                      |  |

KE17ZDTSIUG

All information provided in this document is subject to legal disclaimers.

## 3.4 Sensitivity boost in mutual-cap mode

#### 3.4.1 Sensitivity boost in mutual-cap mode

Mutual capacitive mode supports sensitivity boost.

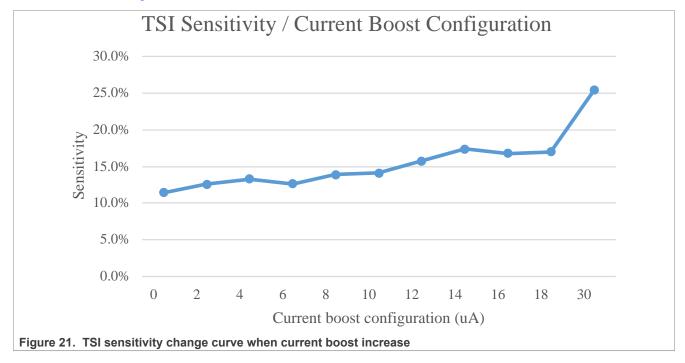

If the mutual touch sensor intrinsic sensitivity is limited due to parasitic, the sensitivity boost feature can be activated by setting  $\texttt{M\_SEN\_BOOST} < 4:0>$ . The basis average charge current is subtracted by boost current which enlarges the signal current.

Different to the self-cap mode, mutual-cap mode implements sensitivity boost by changing the current. It is configurable in register TSI MUL0 [M SEN BOOST]. The current value ranges from 0  $\mu$ A to 62  $\mu$ A.

Table 16. Sensitivity boost enable in mutual-cap mode

| Variable                  | Register               | Value     | Descriptions                                                |

|---------------------------|------------------------|-----------|-------------------------------------------------------------|

| Sensitivity boost current | TSIx_MUL0[M_SEN_BOOST] | 0 - 62 μΑ | Choose the sensitivity boost current to change sensitivity. |