#### Freescale Semiconductor

# MPC850 Family User's Manual

**Integrated Communications Microprocessor**

Supports MPC850

MPC850DE

MPC850SR

MPC850DSL

MPC850UM/D Rev. 1, 1/2001

#### How to Reach Us:

#### Home Page:

www.freescale.com

#### E-mail:

support@freescale.com

#### **USA/Europe or Locations Not Listed:**

Freescale Semiconductor Technical Information Center, CH370 1300 N. Alma School Road Chandler, Arizona 85224 +1-800-521-6274 or +1-480-768-2130 support@freescale.com

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH

Technical Information Center

Schatzbogen 7

81829 Muenchen, Germany

+44 1296 380 456 (English)

+46 8 52200080 (English)

+49 89 92103 559 (German)

+33 1 69 35 48 48 (French)

support@freescale.com

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters

ARCO Tower 15F

1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064

Japan

0120 191014 or +81 3 5437 9125

support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor Hong Kong Ltd.

Technical Information Center

2 Dai King Street

Tai Po Industrial Estate

Tai Po, N.T., Hong Kong

+800 2666 8080

support.asia@freescale.com

Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of. directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

#### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center P.O. Box 5405

Denver, Colorado 80217

1-800-441-2447 or 303-675-2140

Fax: 303-675-2150

LDCForFreescaleSemiconductor@hibbertgroup.com

| D 11 D 1                               |     |

|----------------------------------------|-----|

| Part I—Overview                        |     |

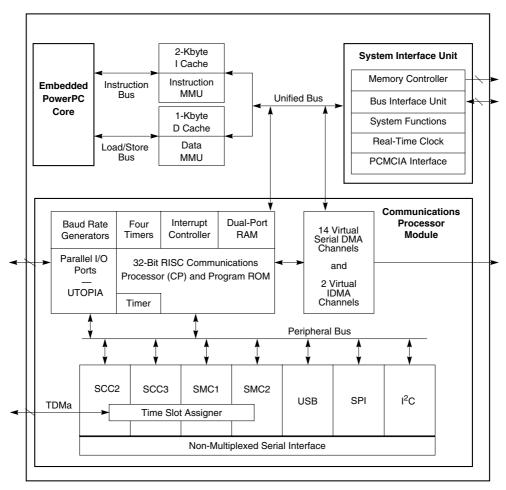

| MPC850 Overview                        | 1   |

| Memory Map                             | 2   |

| Part II—PowerPC Microprocessor Module  | II  |

| PowerPC Core                           | 3   |

| PowerPC Core Register Set              | 4   |

| MPC850 Instruction Set                 | 5   |

| Exceptions                             | 6   |

| Instruction and Data Caches            | 7   |

| Memory Management Unit                 | 8   |

| Instruction Execution Timing           | 9   |

| Part III—PowerPC Microprocessor Module | III |

| System Interface Unit                  | 10  |

| Reset                                  | 11  |

| Part IV—Hardware Interface             | IV  |

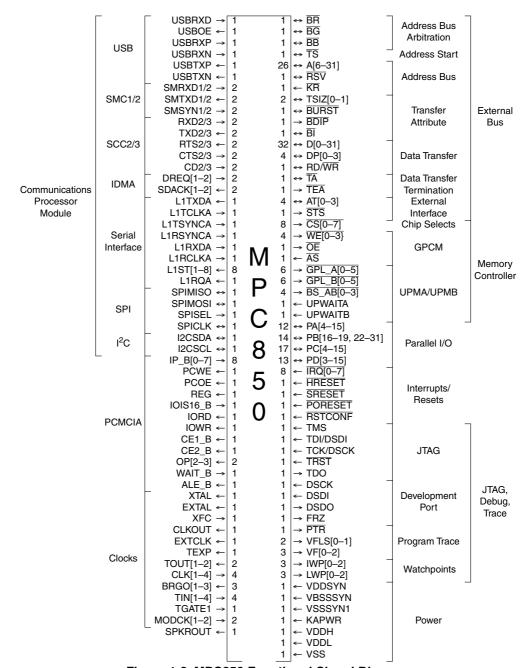

| External Signals                       | 12  |

| External Bus Interface                 | 13  |

| Clocks and Power Control               | 14  |

| Memory Controller                      | 15  |

| PCMCIA Interface                       | 16  |

#### rt I-Overview

| 1   | MPC850 Overview                        |

|-----|----------------------------------------|

| 2   | Memory Map                             |

| II  | Part II—PowerPC Microprocessor Module  |

| 3   | PowerPC Core                           |

| 4   | PowerPC Core Register Set              |

| 5   | MPC850 Instruction Set                 |

| 6   | Exceptions                             |

| 7   | Instruction and Data Caches            |

| 8   | Memory Management Unit                 |

| 9   | Instruction Execution Timing           |

| III | Part III—PowerPC Microprocessor Module |

| 10  | System Interface Unit                  |

| 11  | Reset                                  |

| IV  | Part IV—Hardware Interface             |

| 12  | External Signals                       |

| 13  | External Bus Interface                 |

| 14  | Clocks and Power Control               |

| 15  | Memory Controller                      |

| 16  | PCMCIA Interface                       |

| Part V—Communications Processor Module                        | V        |

|---------------------------------------------------------------|----------|

| Communications Processor Module and Timers                    | 17       |

| Communications Processor                                      | 18       |

| SDMA Channels and IDMA Emulation                              | 19       |

| Serial Interface                                              | 20       |

| SCC Introduction                                              | 21       |

| SCC UART Mode                                                 | 22       |

| SCC HDLC Mode                                                 | 23       |

| SCC AppleTalk Mode                                            | 24       |

| SCC Asynchronous HDLC Mode and IrDA                           | 25       |

| SCC BISYNC Mode                                               | 26       |

| SCC Ethernet Mode                                             | 27       |

| SCC Transparent Mode                                          | 28       |

| IrDA Mode—SCC2 Only                                           | 29       |

| Serial Management Controllers                                 | 30       |

| Serial Peripheral Interface                                   | 31       |

| Universal Serial Bus Controller                               | 32       |

| I <sup>2</sup> C Controller                                   | 33       |

| Parallel I/O Ports                                            | 34       |

| CPM Interrupt Controller Part VI — Asynchronous Transfer Mode | 35       |

| ATM Overview                                                  | VI       |

| Buffer Descriptors and Connection Tables                      | 36       |

| ATM Parameter RAM                                             | 37       |

| ATM Talameter Haw                                             | 38<br>39 |

| ATM Controller ATM Pace Control                               | 40       |

| ATM Face Control ATM Exceptions                               |          |

| Interface Configuration                                       | 41<br>42 |

| UTOPIA Interface                                              | 43       |

| Part VII—System Debugging and Testing Support                 | VII      |

| System Development and Debugging                              | 44       |

| IEEE 1149.1 Test Access Port                                  |          |

| Byte Ordering                                                 | A        |

| Serial Communication Performance                              | В        |

| Register Quick Reference Guide                                | C        |

| Instruction Set Listings                                      |          |

| MPC850                                                        |          |

| MPC850DSL                                                     |          |

|                                                               |          |

| Glossary                                                      | GLO      |

| V<br>17<br>18 | Part V—Communications Processor Module Communications Processor Module and Timers Communications Processor |

|---------------|------------------------------------------------------------------------------------------------------------|

| 19            | SDMA Channels and IDMA Emulation                                                                           |

| 20            | Serial Interface                                                                                           |

| 21            | SCC Introduction                                                                                           |

| 22            | SCC UART Mode                                                                                              |

| 23            | SCC HDLC Mode                                                                                              |

| 24            | SCC AppleTalk Mode                                                                                         |

| 25            | SCC Asynchronous HDLC Mode and IrDA                                                                        |

| 26            | SCC BISYNC Mode                                                                                            |

| 27            | SCC Ethernet Mode                                                                                          |

| 28            | SCC Transparent Mode                                                                                       |

| 29            | IrDA Mode—SCC2 Only                                                                                        |

| 30            | Serial Management Controllers                                                                              |

| 31            | Serial Peripheral Interface                                                                                |

| 32            | Universal Serial Bus Controller                                                                            |

| 33            | I2C Controller                                                                                             |

| 34            | Parallel I/O Ports                                                                                         |

| 35            | CPM Interrupt Controller                                                                                   |

| VI            | Part VI — Asynchronous Transfer Mode                                                                       |

| 36            | ATM Overview                                                                                               |

| 37            | Buffer Descriptors and Connection Tables                                                                   |

| 38            | ATM Parameter RAM                                                                                          |

| 39            | ATM Controller                                                                                             |

| 40            | ATM Pace Controller                                                                                        |

| 41            | ATM Exceptions                                                                                             |

| 42            | Interface Configuration                                                                                    |

| 43            | UTOPIA Interface                                                                                           |

| VII           | Part VII — System Debugging and Testing Support                                                            |

| 44            | System Development and Debugging                                                                           |

| 45            | IEEE 1149.1 Test Access Port                                                                               |

| A             | Byte Ordering                                                                                              |

| В             | Serial Communication Performance                                                                           |

| C             | Register Quick Reference Guide                                                                             |

| <u>D</u>      | Instruction Set Listings                                                                                   |

| F             | MPC850<br>MPC850DSL                                                                                        |

| GLO           | Glossary                                                                                                   |

| IND           | Index                                                                                                      |

| Paragraph<br>Number                                                                                                   | Title                                                                                                                                                                                                                                                                                                  | Page<br>Number                                                     |

|-----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

|                                                                                                                       | Part I<br>Overview                                                                                                                                                                                                                                                                                     |                                                                    |

|                                                                                                                       | Chapter 1<br>Overview                                                                                                                                                                                                                                                                                  |                                                                    |

| 1.1<br>1.2<br>1.2.1<br>1.2.2<br>1.2.2.1<br>1.2.2.2<br>1.2.3<br>1.2.3.1<br>1.2.3.2<br>1.2.3.3<br>1.2.4<br>1.2.5<br>1.3 | Features                                                                                                                                                                                                                                                                                               |                                                                    |

|                                                                                                                       | Part II PowerPC Microprocessor Module                                                                                                                                                                                                                                                                  |                                                                    |

|                                                                                                                       | Chapter 3 The PowerPC Core                                                                                                                                                                                                                                                                             |                                                                    |

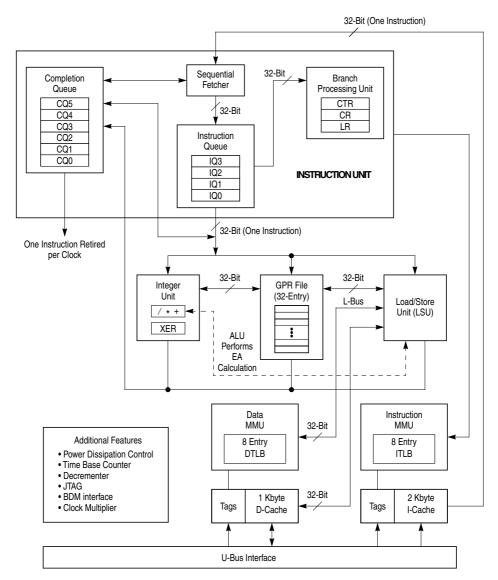

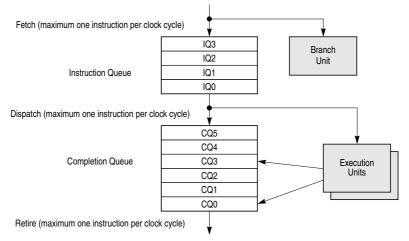

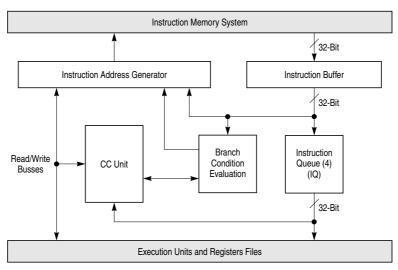

| 3.1<br>3.2<br>3.2.1<br>3.3<br>3.4<br>3.4.1<br>3.4.2<br>3.4.3<br>3.4.3.1<br>3.4.3.2<br>3.5<br>3.6                      | The MPC850 Core as a PowerPC Implementation.  PowerPC Architecture Overview.  Levels of the PowerPC Architecture  Features.  Basic Structure of the Core.  Instruction Flow  Basic Instruction Pipeline  Instruction Unit  Branch Operations  Dispatching Instructions  Register Set  Execution Units. | 3-1<br>3-3<br>3-4<br>3-5<br>3-6<br>3-7<br>3-7<br>3-7<br>3-9<br>3-9 |

**Contents** vii

| Paragraph<br>Number | Title                                             | Page<br>Number |

|---------------------|---------------------------------------------------|----------------|

| 3.6.1               | Branch Processing Unit                            | 3-10           |

| 3.6.2               | Integer Unit                                      |                |

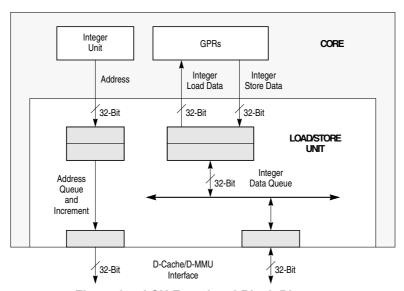

| 3.6.3               | Load/Store Unit                                   | 3-10           |

| 3.6.3.1             | Executing Load/Store Instructions                 | 3-12           |

| 3.6.3.2             | Serializing Load/Store Instructions               |                |

| 3.6.3.3             | Store Accesses                                    |                |

| 3.6.3.4             | Nonspeculative Load Instructions                  | 3-13           |

| 3.6.3.5             | Unaligned Accesses                                |                |

| 3.6.3.6             | Atomic Update Primitives                          |                |

| 3.7                 | The MPC850 and the PowerPC Architecture           | 3-14           |

|                     | Chapter 4                                         |                |

|                     | PowerPC Core Register Set                         |                |

| 4.1                 | MPC850 Register Implementation                    | 4-1            |

| 4.1.1               | PowerPC Registers—User Registers                  |                |

| 4.1.1.1             | PowerPC User-Level Register Bit Assignments       |                |

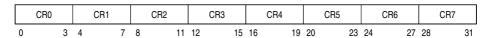

| 4.1.1.1.1           | Condition Register (CR)                           |                |

| 4.1.1.1.2           | Condition Register CR0 Field Definition           |                |

| 4.1.1.1.3           | XER                                               | 4-3            |

| 4.1.1.1.4           | Time Base Registers                               |                |

| 4.1.2               | PowerPC Registers—Supervisor Registers            | 4-4            |

| 4.1.2.1             | DAR, DSISR, and BAR Operation                     | 4-5            |

| 4.1.2.2             | Unsupported Registers                             | 4-6            |

| 4.1.2.3             | PowerPC Supervisor-Level Register Bit Assignments |                |

| 4.1.2.3.1           | Machine State Register (MSR)                      | 4-6            |

| 4.1.2.3.2           | Processor Version Register                        | 4-8            |

| 4.1.3               | MPC850-Specific SPRs                              |                |

| 4.1.3.1             | Accessing SPRs                                    |                |

| 4.2                 | Register Initialization at Reset                  | 4-11           |

|                     | Chapter 5                                         |                |

|                     | MPC850 Instruction Set                            |                |

| 5.1                 | Operand Conventions                               | 5-1            |

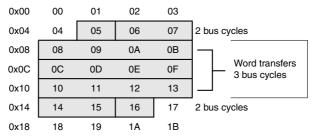

| 5.1.1               | Data Organization in Memory and Data Transfers    |                |

| 5.1.2               | Aligned and Misaligned Accesses                   | 5-1            |

| 5.2                 | Instruction Set Summary                           |                |

| 5.2.1               | Classes of Instructions                           |                |

| 5.2.1.1             | Definition of Boundedly Undefined                 |                |

| 5.2.1.2             | Defined Instruction Class                         |                |

| 5.2.1.3             | Illegal Instruction Class                         | 5-4            |

|                     |                                                   |                |

| Paragraph<br>Number | Title                                                 | Page<br>Number |

|---------------------|-------------------------------------------------------|----------------|

| 5.2.1.4             | Reserved Instruction Class                            | 5-5            |

| 5.2.2               | Addressing Modes                                      | 5-5            |

| 5.2.2.1             | Memory Addressing                                     | 5-5            |

| 5.2.2.2             | Effective Address Calculation                         | 5-6            |

| 5.2.2.3             | Synchronization                                       | 5-6            |

| 5.2.2.3.1           | Context Synchronization                               |                |

| 5.2.2.3.2           | Execution Synchronization                             | 5-7            |

| 5.2.2.3.3           | Instruction-Related Exceptions                        | 5-7            |

| 5.2.3               | Instruction Set Overview                              | 5-7            |

| 5.2.4               | PowerPC UISA Instructions                             | 5-8            |

| 5.2.4.1             | Integer Instructions                                  | 5-8            |

| 5.2.4.1.1           | Integer Arithmetic Instructions                       | 5-8            |

| 5.2.4.1.2           | Integer Compare Instructions                          | 5-9            |

| 5.2.4.1.3           | Integer Logical Instructions                          | 5-10           |

| 5.2.4.1.4           | Integer Rotate and Shift Instructions                 | 5-10           |

| 5.2.4.2             | Load and Store Instructions                           | 5-11           |

| 5.2.4.2.1           | Integer Load and Store Address Generation             |                |

| 5.2.4.2.2           | Register Indirect Integer Load Instructions           | 5-12           |

| 5.2.4.2.3           | Integer Store Instructions                            | 5-12           |

| 5.2.4.2.4           | Integer Load and Store with Byte-Reverse Instructions | 5-13           |

| 5.2.4.2.5           | Integer Load and Store Multiple Instructions          |                |

| 5.2.4.2.6           | Integer Load and Store String Instructions            |                |

| 5.2.4.3             | Branch and Flow Control Instructions                  |                |

| 5.2.4.3.1           | Branch Instruction Address Calculation                |                |

| 5.2.4.3.2           | Branch Instructions                                   |                |

| 5.2.4.3.3           | Condition Register Logical Instructions               |                |

| 5.2.4.4             | Trap Instructions                                     |                |

| 5.2.4.5             | Processor Control Instructions                        |                |

| 5.2.4.5.1           | Move to/from Condition Register Instructions          | 5-17           |

| 5.2.4.6             | Memory Synchronization Instructions—UISA              |                |

| 5.2.5               | PowerPC VEA Instructions                              |                |

| 5.2.5.1             | Processor Control Instructions                        |                |

| 5.2.5.2             | Memory Synchronization Instructions—VEA               |                |

| 5.2.5.2.1           | eieio Behavior                                        |                |

| 5.2.5.2.2           | isync Behavior                                        |                |

| 5.2.5.3             | Memory Control Instructions—VEA                       |                |

| 5.2.6               | PowerPC OEA Instructions                              |                |

| 5.2.6.1             | System Linkage Instructions                           |                |

| 5.2.6.2             | Processor Control Instructions—OEA                    |                |

| 5.2.6.2.1           | Move to/from Machine State Register Instructions      |                |

| 5.2.6.2.2           | Move to/from Special-Purpose Register Instructions    |                |

| 5.2.6.3             | Memory Control Instructions—OEA                       | 5-23           |

Contents ix

| Paragraph<br>Number | Title                                             | Page<br>Number |

|---------------------|---------------------------------------------------|----------------|

|                     | Chapter 6                                         |                |

|                     | Exceptions                                        |                |

| 6.1                 | Exceptions                                        | 6-2            |

| 6.1.1               | Exception Ordering                                |                |

| 6.1.2               | PowerPC-Defined Exceptions                        |                |

| 6.1.2.1             | System Reset Interrupt (0x00100)                  | 6-5            |

| 6.1.2.2             | Machine Check Interrupt (0x00200)                 |                |

| 6.1.2.3             | DSI Exception (0x00300)                           | 6-6            |

| 6.1.2.4             | ISI Exception (0x00400)                           | 6-6            |

| 6.1.2.5             | External Interrupt Exception (0x00500)            | 6-6            |

| 6.1.2.6             | Alignment Exception (0x00600)                     |                |

| 6.1.2.6.1           | Integer Alignment Exceptions                      |                |

| 6.1.2.7             | Program Exception (0x00700)                       |                |

| 6.1.2.8             | Decrementer Exception (0x00900)                   |                |

| 6.1.2.9             | System Call Exception (0x00C00)                   |                |

| 6.1.2.10            | Trace Exception (0x00D00)                         |                |

| 6.1.2.11            | Floating-Point Assist Exception                   |                |

| 6.1.3               | Implementation-Specific Exceptions                |                |

| 6.1.3.1             | Software Emulation Exception (0x01000)            |                |

| 6.1.3.2             | Instruction TLB Miss Exception (0x01100)          |                |

| 6.1.3.3             | Data TLB Miss Exception (0x01200)                 |                |

| 6.1.3.4             | Instruction TLB Error Exception (0x01300)         |                |

| 6.1.3.5             | Data TLB Error Exception (0x014000)               |                |

| 6.1.3.6             | Debug Exceptions (0x01C00–0x01F00)                |                |

| 6.1.4               | Implementing the Precise Exception Model          |                |

| 6.1.5               | Recoverability after an Exception                 |                |

| 6.1.6               | Exception Latency                                 |                |

| 6.1.7               | Partially Completed Instructions                  | 6-20           |

|                     | Chapter 7                                         |                |

|                     | Instruction and Data Caches                       |                |

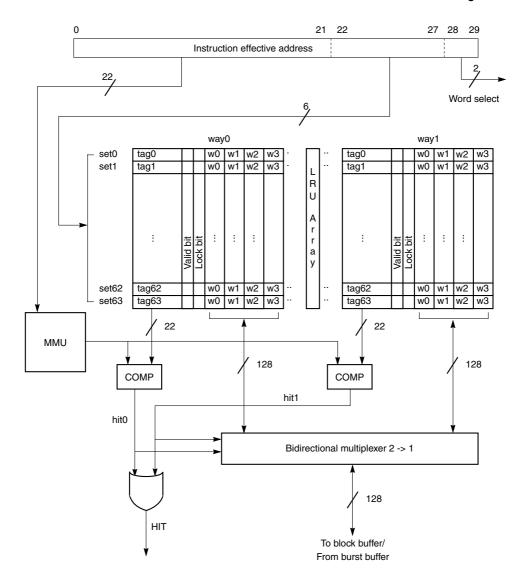

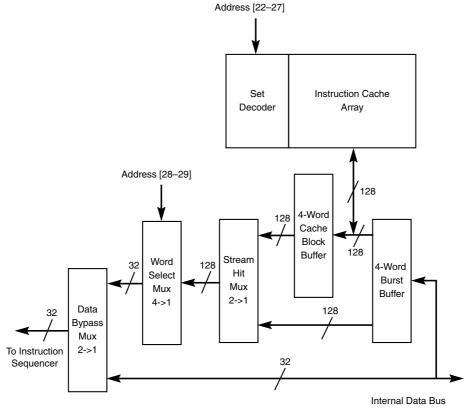

| 7.1                 | Instruction Cache Organization                    | 7–2            |

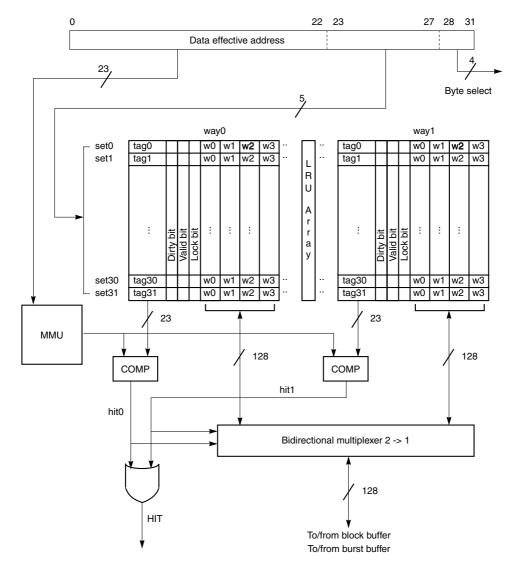

| 7.2                 | Data Cache Organization                           | 7–4            |

| 7.3                 | Cache Control Registers                           | 7–6            |

| 7.3.1               | Instruction Cache Control Registers               | 7–6            |

| 7.3.1.1             | Reading Data and Tags in the Instruction Cache    |                |

| 7.3.1.2             | IC_CST Commands                                   | 7–9            |

| 7.3.1.2.1           | Instruction Cache Enable/Disable Commands         |                |

| 7.3.1.2.2           | Instruction Cache Load & Lock Cache Block Command |                |

| 7.3.1.2.3           | Instruction Cache Unlock Cache Block Command      | 7–10           |

| Paragraph<br>Number |                                                                       | Page<br>mber |

|---------------------|-----------------------------------------------------------------------|--------------|

| 7.3.1.2.4           | Instruction Cache Unlock All Command                                  | . 7–11       |

| 7.3.1.2.5           | Instruction Cache Invalidate All Command                              |              |

| 7.3.2               | Data Cache Control Registers                                          | . 7–11       |

| 7.3.2.1             | Reading Data Cache Tags and Copyback Buffer                           | . 7–14       |

| 7.3.2.2             | DC_CST Commands                                                       |              |

| 7.3.2.2.1           | Data Cache Enable/Disable Commands                                    | . 7–16       |

| 7.3.2.2.2           | Data Cache Load & Lock Cache Block Command                            | . 7–16       |

| 7.3.2.2.3           | Data Cache Unlock Cache Block Command                                 | . 7–17       |

| 7.3.2.2.4           | Data Cache Unlock All Command                                         | . 7–17       |

| 7.3.2.2.5           | Data Cache Invalidate All Command                                     | . 7–17       |

| 7.3.2.2.6           | Data Cache Flush Cache Block Command                                  | . 7–17       |

| 7.4                 | PowerPC Cache Control Instructions                                    | . 7–18       |

| 7.4.1               | Instruction Cache Block Invalidate (icbi)                             | . 7–18       |

| 7.4.2               | Data Cache Block Touch (dcbt) and Data Cache Block                    |              |

|                     | Touch for Store (dcbtst)                                              | 7–18         |

| 7.4.3               | Data Cache Block Zero (dcbz)                                          | . 7–19       |

| 7.4.4               | Data Cache Block Store (dcbst)                                        | . 7–19       |

| 7.4.5               | Data Cache Block Flush (dcbf)                                         | . 7–20       |

| 7.4.6               | Data Cache Block Invalidate (dcbi)                                    | . 7–20       |

| 7.5                 | Instruction Cache Operations                                          | . 7–20       |

| 7.5.1               | Instruction Cache Hit                                                 | . 7–22       |

| 7.5.2               | Instruction Cache Miss                                                | . 7–22       |

| 7.5.3               | Instruction Fetching on a Predicted Path                              | . 7–23       |

| 7.5.4               | Fetching Instructions from Caching-Inhibited Regions                  | . 7–23       |

| 7.5.5               | Updating Code and Memory Region Attributes                            | . 7–24       |

| 7.6                 | Data Cache Operation                                                  | . 7–24       |

| 7.6.1               | Data Cache Load Hit                                                   | . 7–25       |

| 7.6.2               | Data Cache Read Miss                                                  | . 7–25       |

| 7.6.3               | Write-Through Mode                                                    | . 7–26       |

| 7.6.3.1             | Data Cache Store Hit in Write-Through Mode                            | . 7–26       |

| 7.6.3.2             | Data Cache Store Miss in Write-Through Mode                           | . 7–26       |

| 7.6.4               | Write-Back Mode                                                       | . 7–26       |

| 7.6.4.1             | Data Cache Store Hit in Write-Back Mode                               | . 7–26       |

| 7.6.4.2             | Data Cache Store Miss in Write-Back Mode                              | . 7–27       |

| 7.6.5               | Data Accesses to Caching-Inhibited Memory Regions                     | . 7–27       |

| 7.6.6               | Atomic Memory References                                              | . 7–28       |

| 7.7                 | Cache Initialization after Reset                                      | . 7–29       |

| 7.8                 | Debug Support                                                         | . 7–29       |

| 7.8.1               | Instruction and Data Cache Operation in Debug Mode                    | . 7–30       |

| 7.8.2               | Instruction and Data Cache Operation with a Software Monitor Debugger |              |

**Contents** xi

| Paragraph<br>Number | Title                                             | Page<br>Number |

|---------------------|---------------------------------------------------|----------------|

|                     | Chapter 8                                         |                |

|                     | Memory Management Unit                            |                |

| 8.1                 | Features                                          | 8–1            |

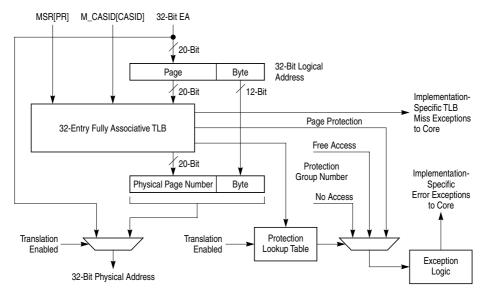

| 8.2                 | PowerPC Architecture Compliance                   |                |

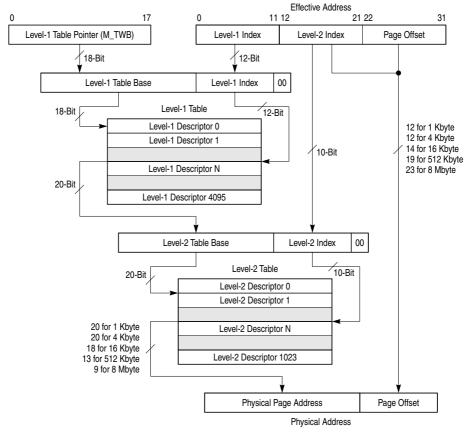

| 8.3                 | Address Translation                               | 8–3            |

| 8.3.1               | Translation Disabled                              | 8–3            |

| 8.3.2               | Translation Enabled                               | 8–3            |

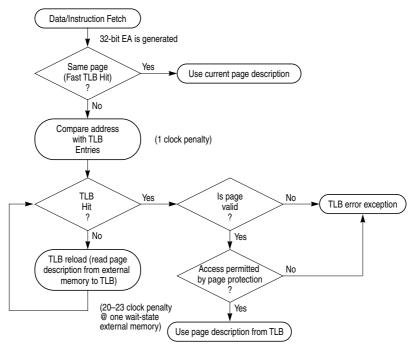

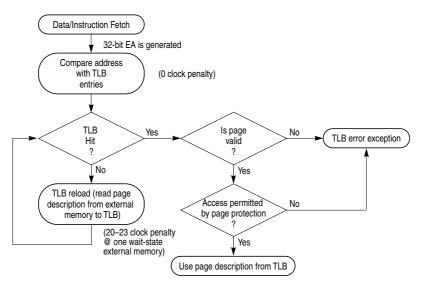

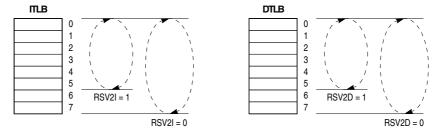

| 8.3.3               | TLB Operation                                     | 8–5            |

| 8.4                 | Using Access Protection Groups                    | 8–6            |

| 8.5                 | Protection Resolution Modes                       | 8–7            |

| 8.6                 | Memory Attributes                                 | 8–8            |

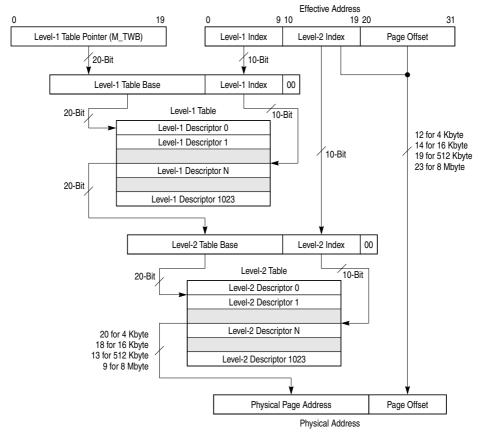

| 8.7                 | Translation Table Structure                       |                |

| 8.7.1               | Level-One Descriptor                              | 8–12           |

| 8.7.2               | Level-Two Descriptor                              |                |

| 8.7.3               | Page Size                                         | 8–14           |

| 8.8                 | Programming Model                                 |                |

| 8.8.1               | IMMU Control Register (MI_CTR)                    |                |

| 8.8.2               | DMMU Control Register (MD_CTR)                    |                |

| 8.8.3               | IMMU/DMMU Effective Page Number Register (Mx_EPN) |                |

| 8.8.4               | IMMU Tablewalk Control Register (MI_TWC)          |                |

| 8.8.5               | DMMU Tablewalk Control Register (MD_TWC)          |                |

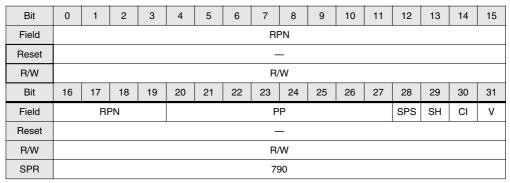

| 8.8.6               | IMMU Real Page Number Register (MI_RPN)           |                |

| 8.8.7               | DMMU Real Page Number Register (MD_RPN)           |                |

| 8.8.8               | MMU Tablewalk Base Register (M_TWB)               |                |

| 8.8.9               | MMU Current Address Space ID Register (M_CASID)   |                |

| 8.8.10              | MMU Access Protection Registers (MI_AP/MD_AP)     |                |

| 8.8.11              | MMU Tablewalk Special Register (M_TW)             |                |

| 8.8.12              | MMU Debug Registers                               |                |

| 8.8.12.1            | IMMU CAM Entry Read Register (MI_CAM)             |                |

| 8.8.12.2            | IMMU RAM Entry Read Register 0 (MI_RAM0)          |                |

| 8.8.12.3            | IMMU RAM Entry Read Register 1 (MI_RAM1)          |                |

| 8.8.12.4            | DMMU CAM Entry Read Register (MD_CAM)             |                |

| 8.8.12.5            | DMMU RAM Entry Read Register 0 (MD_RAM0)          |                |

| 8.8.13              | DMMU RAM Entry Read Register 1 (MD_RAM1)          |                |

| 8.9                 | Memory Management Unit Exceptions                 |                |

| 8.10                | TLB Manipulation                                  |                |

| 8.10.1              | TLB Reload                                        |                |

| 8.10.1.1            | Translation Reload Examples                       |                |

| 8.10.2              | Locking TLB Entries                               |                |

| 8.10.3              | Loading Locked TLB Entries                        |                |

| 8.10.4              | TLB Invalidation                                  | 8–34           |

| Paragraph<br>Number | Title                                      | Page<br>Number |

|---------------------|--------------------------------------------|----------------|

|                     | Chapter 9                                  |                |

|                     | Instruction Execution Timing               |                |

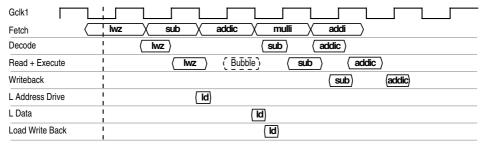

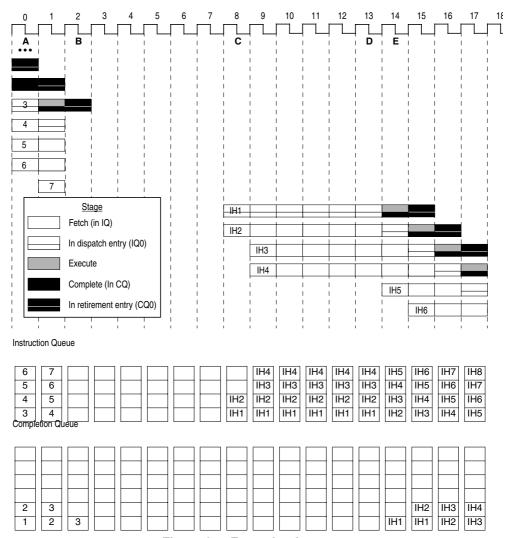

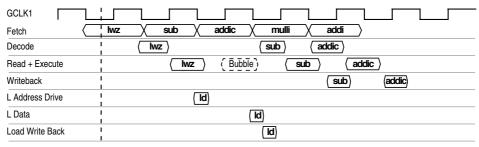

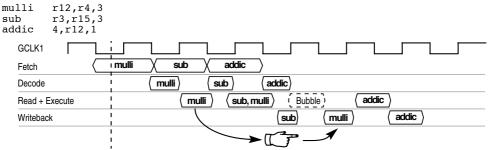

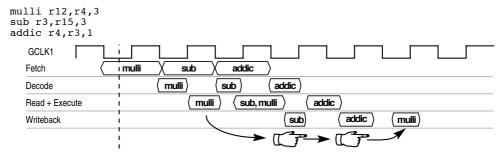

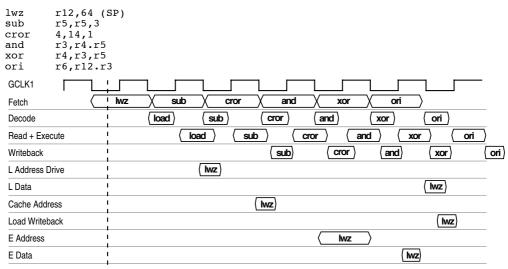

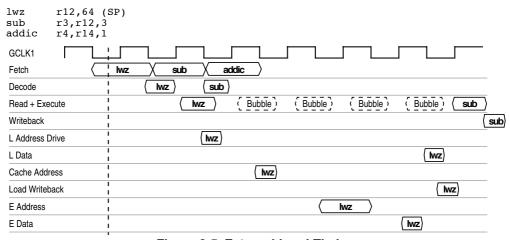

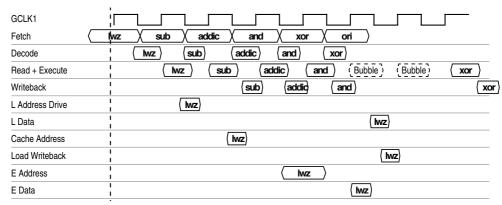

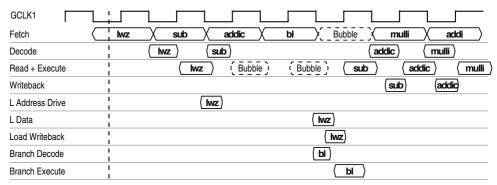

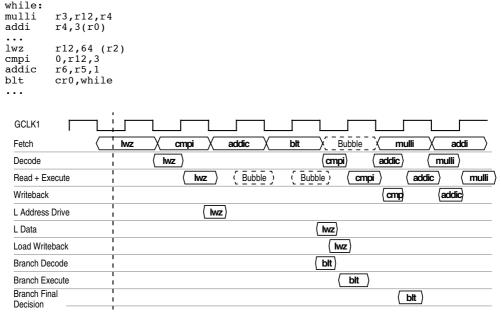

| 9.1                 | Instruction Execution Timing Examples      | 9–1            |

| 9.1.1               | Data Cache Load with a Data Dependency     | 9–1            |

| 9.1.2               | Writeback Arbitration                      |                |

| 9.1.3               | Private Writeback Bus Load                 |                |

| 9.1.4               | Fastest External Load (Data Cache Miss)    |                |

| 9.1.5               | A Full Completion Queue                    |                |

| 9.1.6               | Branch Instruction Handling                |                |

| 9.1.7               | Branch Prediction                          |                |

| 9.2                 | Instruction Timing List                    |                |

| 9.2.1               | Load/Store Instruction Timing              |                |

| 9.2.2               | String Instruction Latency                 |                |

| 9.2.3               | Accessing Off-Core SPRs                    | 9–8            |

|                     |                                            |                |

|                     | Part III                                   |                |

|                     | Configuration and Reset                    |                |

|                     |                                            |                |

|                     | Chapter 10                                 |                |

|                     | System Interface Unit                      |                |

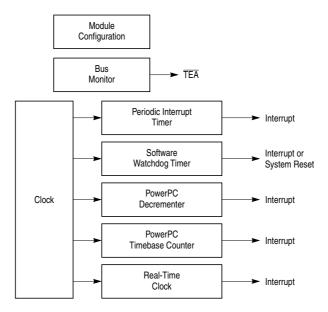

| 10.1                | Features                                   | 10–2           |

| 10.2                | System Configuration and Protection        |                |

| 10.3                | Multiplexing SIU Pins                      |                |

| 10.4                | Programming the SIU                        |                |

| 10.4.1              | Internal Memory Map Register (IMMR)        |                |

| 10.4.2              | SIU Module Configuration Register (SIUMCR) |                |

| 10.4.3              | System Protection Control Register (SYPCR) |                |

| 10.4.4              | Transfer Error Status Register (TESR)      |                |

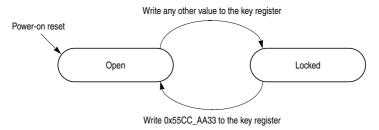

| 10.4.5              | Register Lock Mechanism                    |                |

| 10.5                | System Configuration                       |                |

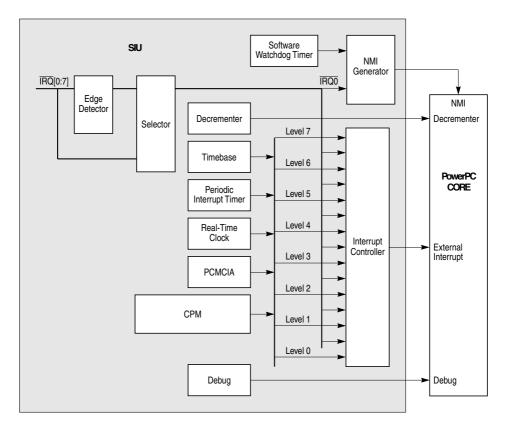

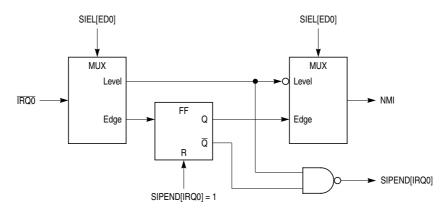

| 10.5.1              | Interrupt Structure                        |                |

| 10.5.2              | Priority of Interrupt Sources              |                |

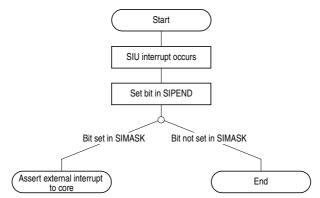

| 10.5.3              | SIU Interrupt Processing                   |                |

| 10.5.3.1            | Nonmaskable Interrupts—IRQ0 and SWT        | 10–14          |

| 10.5.4              | Programming the SIU Interrupt Controller   |                |

| 10.5.4.1            | SIU Interrupt Pending Register (SIPEND)    |                |

| 10.5.4.2            | SIU Interrupt Mask Register (SIMASK)       |                |

| 10.5.4.3            | SIU Interrupt Edge/Level Register (SIEL)   |                |

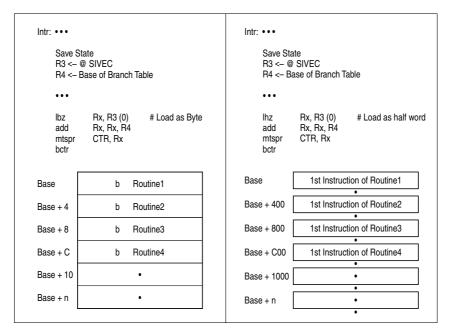

| 10.5.4.4            | SIU Interrupt Vector Register (SIVEC)      |                |

| 10.6                | The Bus Monitor                            |                |

|                     |                                            |                |

Contents xiii

| Paragraph<br>Number | Title                                                  | Page<br>Number |

|---------------------|--------------------------------------------------------|----------------|

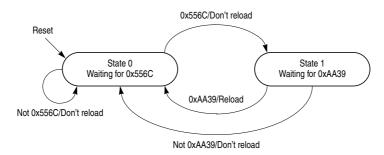

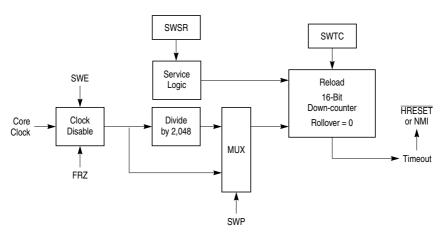

| 10.7                | The Software Watchdog Timer                            |                |

| 10.7.1              | Software Service Register (SWSR)                       | 10–22          |

| 10.8                | The PowerPC Decrementer                                |                |

| 10.8.1              | Decrementer Register (DEC)                             | 10–24          |

| 10.9                | The PowerPC Timebase                                   | 10–24          |

| 10.9.1              | Timebase Register (TBU and TBL)                        |                |

| 10.9.2              | Timebase Reference Registers (TBREFA and TBREFB)       |                |

| 10.9.3              | Timebase Status and Control Register (TBSCR)           | 10–26          |

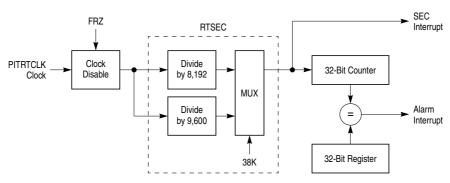

| 10.10               | The Real-Time Clock                                    |                |

| 10.10.1             | Real-Time Clock Status and Control Register (RTCSC)    | 10–28          |

| 10.10.2             | Real-Time Clock Register (RTC)                         |                |

| 10.10.3             | Real-Time Clock Alarm Register (RTCAL)                 |                |

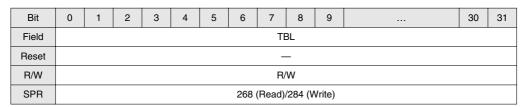

| 10.10.4             | Real-Time Clock Alarm Seconds Register (RTSEC)         | 10–30          |

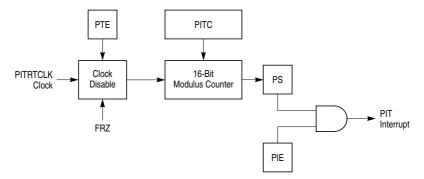

| 10.11               | The Periodic Interrupt Timer (PIT)                     |                |

| 10.11.1             | Periodic Interrupt Status and Control Register (PISCR) | 10–32          |

| 10.11.2             | PIT Count Register (PITC)                              | 10–33          |

| 10.11.3             | PIT Register (PITR)                                    | 10–33          |

| 10.12               | General SIU Timers Operation                           | 10–34          |

| 10.12.1             | Freeze Operation                                       | 10–34          |

| 10.12.2             | Low-Power Stop Operation                               | 10–34          |

|                     | Chapter 11<br>Reset                                    |                |

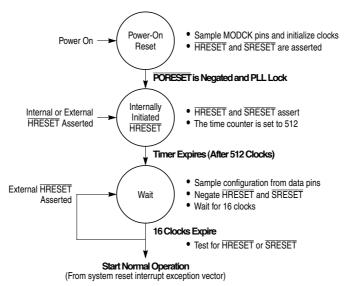

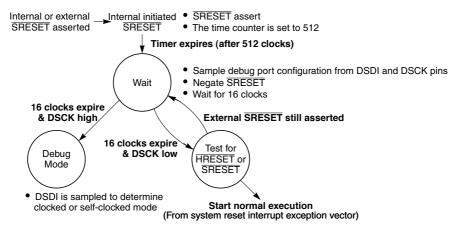

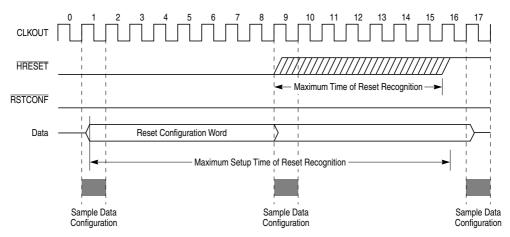

| 11.1                | Types of Reset                                         | 11 1           |

| 11.1.1              | Power-On Reset                                         |                |

| 11.1.1              | External Hard Reset                                    |                |

| 11.1.2              | Internal Hard Reset                                    |                |

| 11.1.3.1            | PLL Loss of Lock                                       |                |

| 11.1.3.1            | Software Watchdog Reset                                |                |

| 11.1.3.2            | Checkstop Reset                                        |                |

| 11.1.3.3            | Debug Port Hard or Soft Reset                          |                |

| 11.1.5              | JTAG Reset                                             |                |

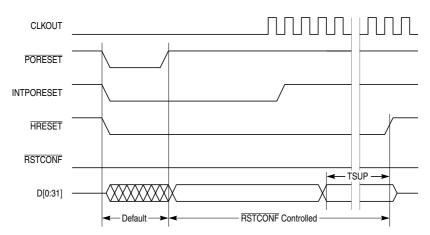

| 11.1.5              | Power-On and Hard Reset Sequence                       |                |

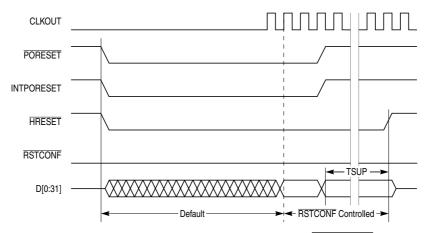

| 11.1.7              | External Soft Reset                                    |                |

| 11.1.7              | Internal Soft Reset                                    |                |

| 11.1.9              | Soft Reset Sequence                                    |                |

| 11.1.9              | Reset Status Register (RSR)                            |                |

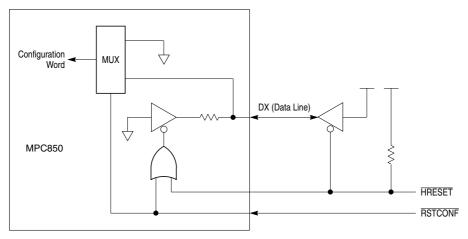

| 11.3                | MPC850 Reset Configuration.                            |                |

| 11.3.1              | Hard Reset                                             |                |

| 11.3.1              | Hard Reset Configuration Word                          |                |

| 11.3.1.1            | Soft Reset                                             |                |

| 11.3.2              | TRST and Power Mode Considerations                     |                |

| 11.7                | TROT and I Owel Mode Considerations                    | 11–11          |

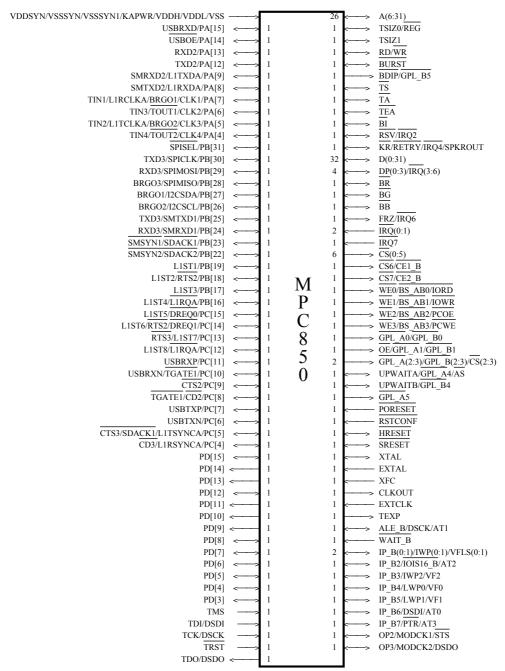

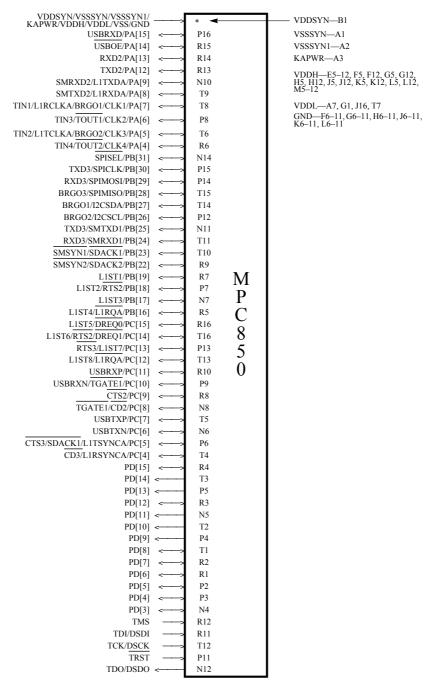

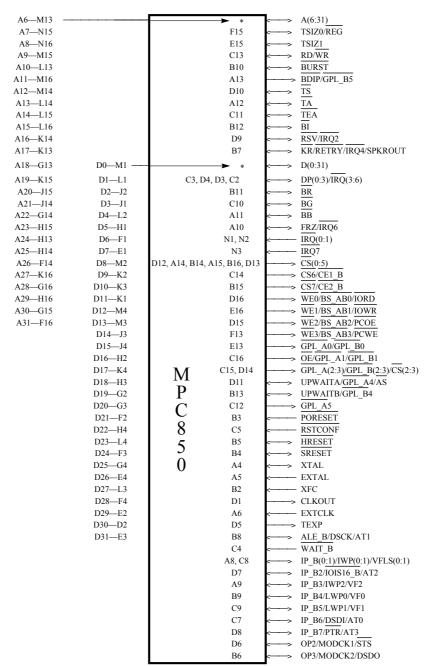

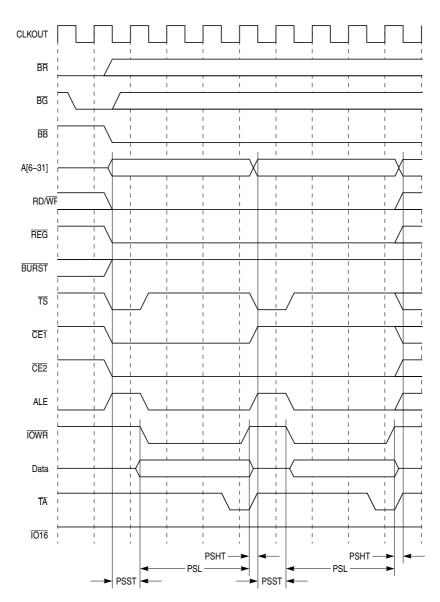

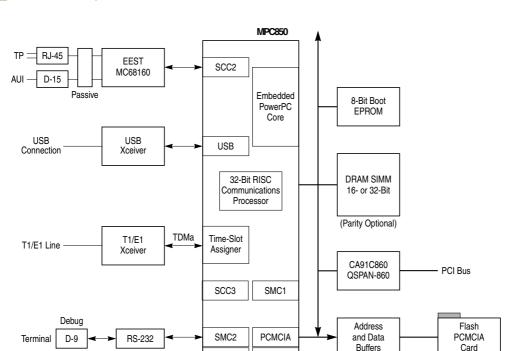

**Paragraph** Page Title Number Number Part IV The Hardware Interface Chapter 12 **External Signals** 12.1 12.2 12.3 12.4 12.4.1 Reset Configuration 12–20 12.4.1.1 12.4.2 12.4.3 Unused Inputs 12–21 12.4.4 12.5 Chapter 13 **External Bus Interface** 13.1 Features 13–1 13.2 13.3 13.4 13.4.1 13.4.2 13.4.2.1 13.4.2.2 13.4.3 13.4.4 13.4.5 13.4.6 13.4.6.1 13.4.6.2 13.4.6.3 13.4.6.4 13.4.7 13.4.7.1 13.4.7.2 13.4.7.3 13.4.7.3.1 13.4.7.3.2

Contents xv

| Paragraph<br>Number | Title                                                            | Page<br>Number |

|---------------------|------------------------------------------------------------------|----------------|

| 13.4.7.3.3          | Transfer Size (TSIZ)                                             | 13–31          |

| 13.4.7.3.4          | Address Types (AT)                                               | 13–31          |

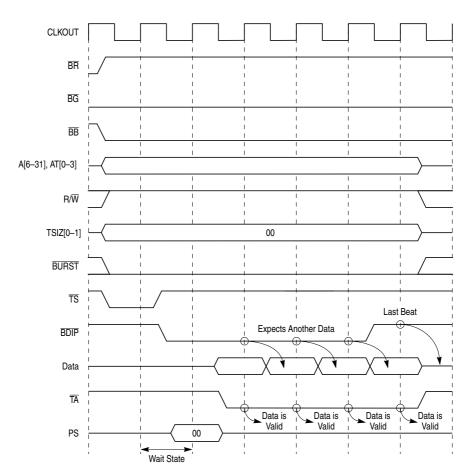

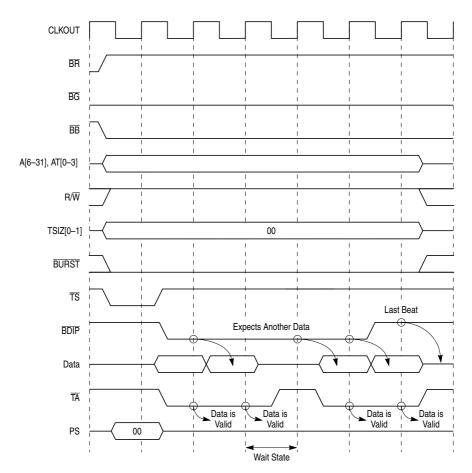

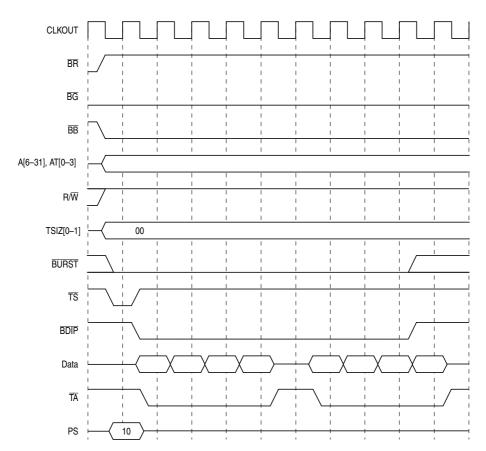

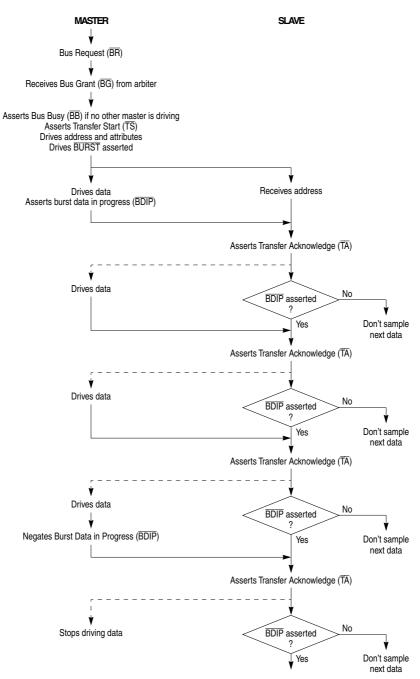

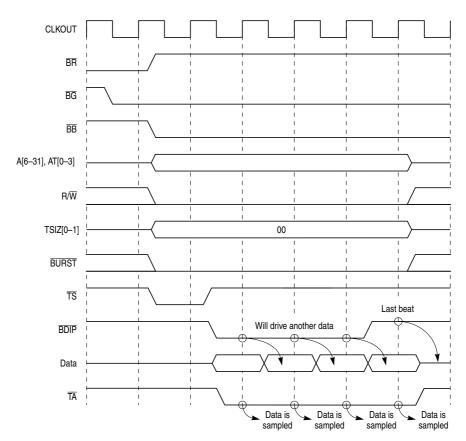

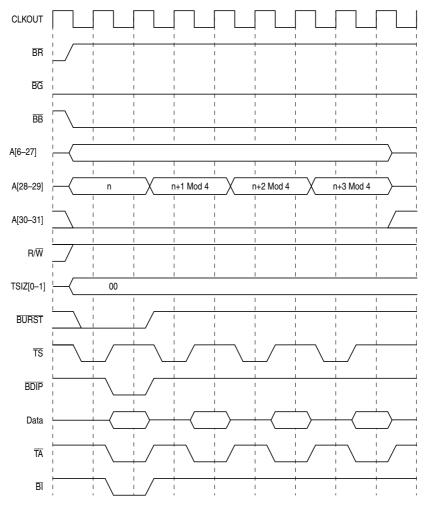

| 13.4.7.3.5          | Burst Data in Progress (BDIP)                                    | 13–34          |

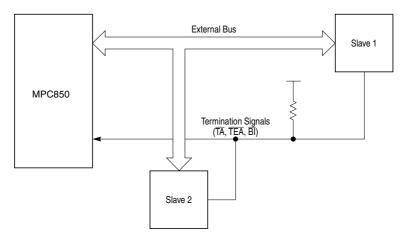

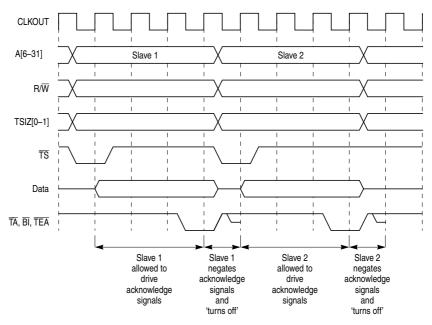

| 13.4.8              | Termination Signals                                              | 13–34          |

| 13.4.8.1            | Transfer Acknowledge (TA)                                        | 13–34          |

| 13.4.8.2            | Burst Inhibit (BI)                                               |                |

| 13.4.8.3            | Transfer Error Acknowledge (TEA)                                 | 13–34          |

| 13.4.8.4            | Termination Signals Protocol                                     | 13–34          |

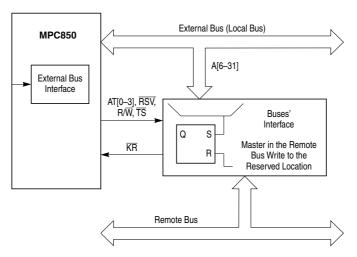

| 13.4.9              | Memory Reservation                                               | 13–35          |

| 13.4.9.1            | Kill Reservation (KR)                                            | 13–36          |

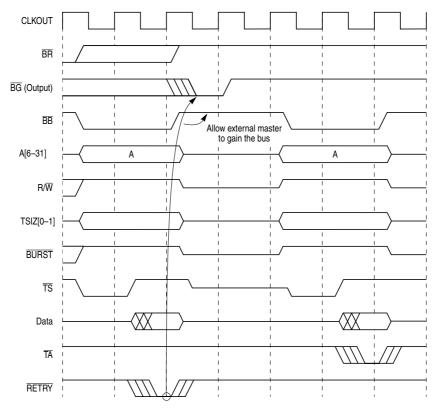

| 13.4.10             | Bus Exception Control Cycles                                     | 13–37          |

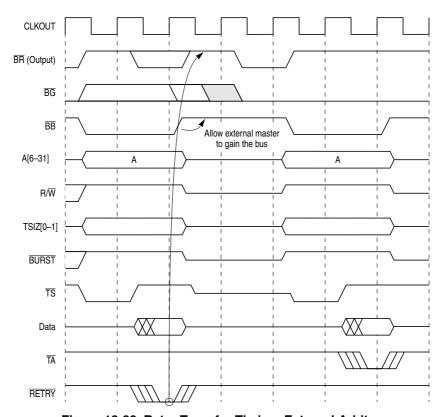

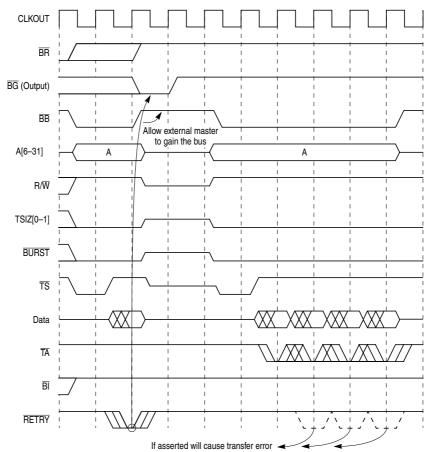

| 13.4.10.1           | RETRY                                                            | 13–38          |

|                     | Chapter 14                                                       |                |

|                     | Clocks and Power Control                                         |                |

| 14.1                | Features                                                         | 14–1           |

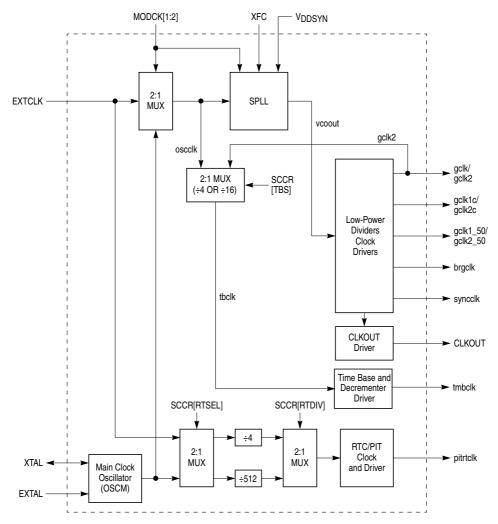

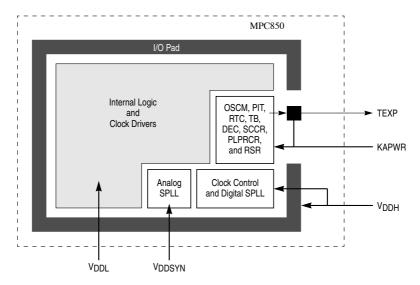

| 14.2                | The Clock Module                                                 | 14–2           |

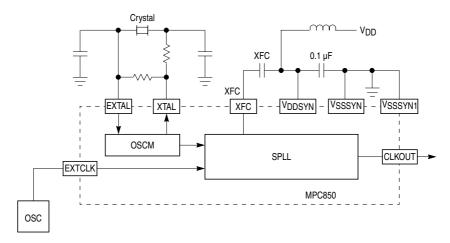

| 14.2.1              | External Reference Clocks                                        | 14–3           |

| 14.2.1.1            | Off-Chip Oscillator Input (EXTCLK)                               | 14–4           |

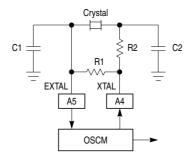

| 14.2.1.2            | Crystal Oscillator Support (EXTAL and XTAL)                      | 14–4           |

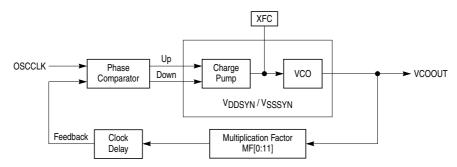

| 14.2.2              | System PLL                                                       | 14–5           |

| 14.2.2.1            | SPLL Reset Configuration                                         | 14–6           |

| 14.2.2.2            | SPLL Output Characteristics and Stability                        | 14–7           |

| 14.2.2.3            | The System Phase-Locked Loop Pins (VDDSYN, VSSSYN, VSSSYN1, XFC) | 14_7           |

| 14.2.2.4            | Disabling the SPLL                                               |                |

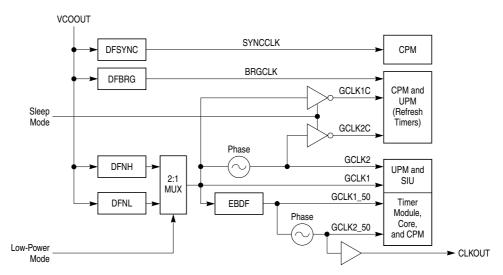

| 14.3                | Clock Signals                                                    |                |

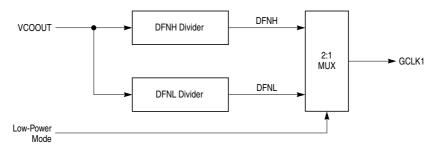

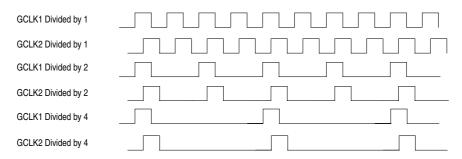

| 14.3.1              | Clocks Derived from the SPLL Output                              |                |

| 14.3.1.1            | The Internal General System Clocks (GCLK1C, GCLK2C,              |                |

| 1.1.0.1.1.1         | GCLK1, GCLK2)                                                    | 14–10          |

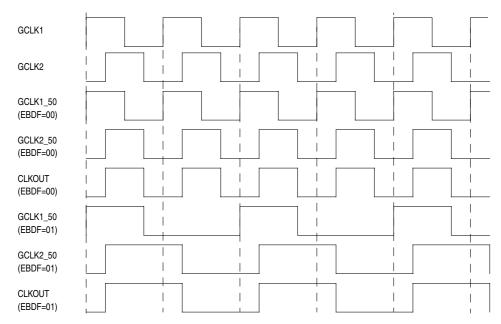

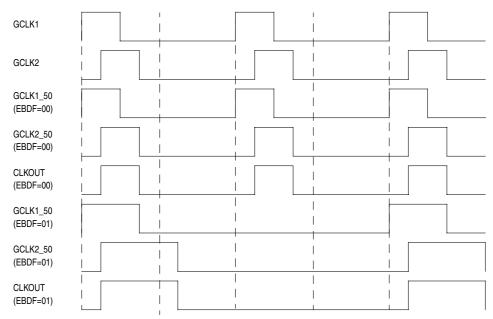

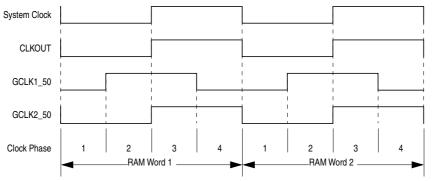

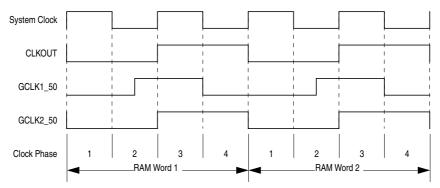

| 14.3.1.2            | Memory Controller and External Bus Clocks (GCLK1_50,             |                |

| 1                   | GCLK2_50, CLKOUT)                                                | 14–11          |

| 14.3.1.3            | CLKOUT Special Considerations: 1:2:1 Mode                        | 14–14          |

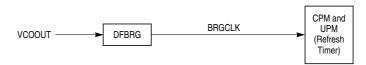

| 14.3.1.4            | The Baud Rate Generator Clock (BRGCLK)                           |                |

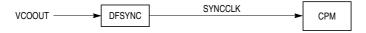

| 14.3.1.5            | The Synchronization Clock (SYNCCLK, SYNCCLKS)                    |                |

| 14.3.2              | The PIT and RTC Clock (PITRTCLK)                                 |                |

| 14.3.3              | The Time Base and Decrementer Clock (TMBCLK)                     | 14–16          |

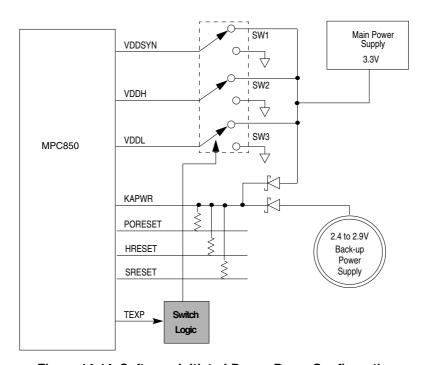

| 14.4                | Power Distribution                                               | 14–16          |

| 14.4.1              | I/O Buffer Power (VDDH)                                          | 14–17          |

| 14.4.2              | Internal Logic Power (VDDL)                                      | 14–18          |

| 14.4.3              | Clock Synthesizer Power (VDDSYN, VSSSYN, VSSYN1)                 |                |

| Paragraph<br>Number | Title                                                      | Page<br>Number |

|---------------------|------------------------------------------------------------|----------------|

| 14.4.4              | Keep-Alive Power (KAPWR)                                   |                |

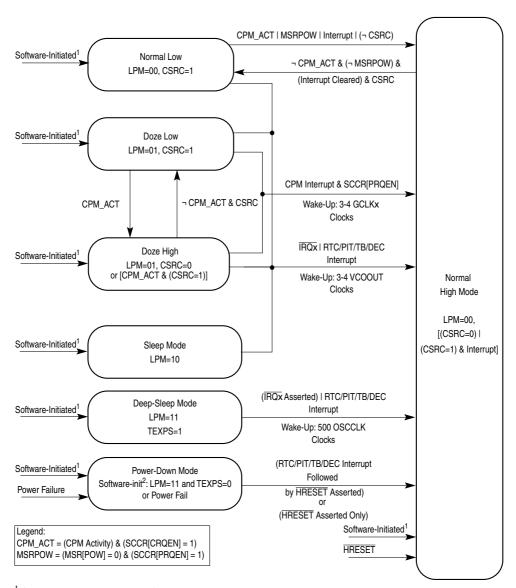

| 14.5                | Power Control (Low-Power Modes)                            |                |

| 14.5.1              | Normal High Mode                                           | 14–21          |

| 14.5.2              | Normal Low Mode                                            |                |

| 14.5.3              | Doze High Mode                                             | 14–21          |

| 14.5.4              | Doze Low Mode                                              | 14–22          |

| 14.5.5              | Sleep Mode                                                 |                |

| 14.5.6              | Deep-Sleep Mode                                            | 14–23          |

| 14.5.7              | Power-Down Mode                                            |                |

| 14.5.7.1            | Software Initiation of Power-Down Mode, with Automatic Wak | te-up 14–24    |

| 14.5.7.2            | Maintaining the Real-Time Clock (RTC) During               |                |

|                     | Shutdown or Power Failure                                  | 14–26          |

| 14.5.7.3            | Register Lock Mechanism: Protecting SIU                    |                |

|                     | Registers in Power-Down Mode                               | 14–26          |

| 14.5.8              | TMIST: Facilitating Nesting of SIU Timer Interrupts        | 14–27          |

| 14.6                | Clock and Power Control Registers                          | 14–27          |

| 14.6.1              | System Clock and Reset Control Register (SCCR)             | 14–27          |

| 14.6.2              | PLL, Low-Power, and Reset Control Register (PLPRCR)        | 14–29          |

|                     | Chapter 15<br>Memory Controller                            |                |

| 15.1                | Features                                                   | 15–1           |

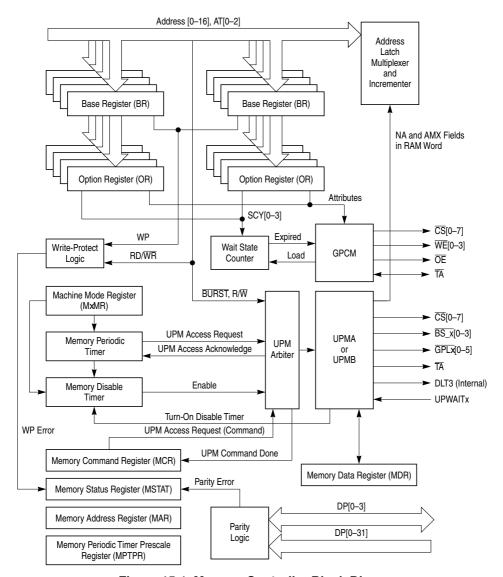

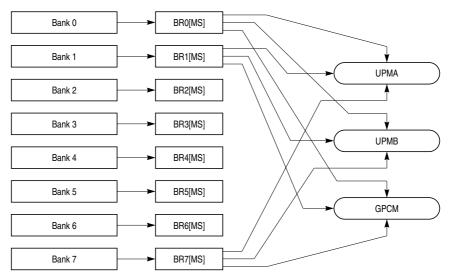

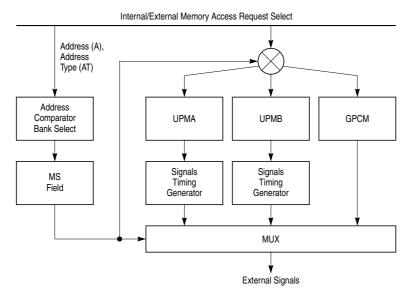

| 15.2                | Basic Architecture                                         | 15–4           |

| 15.3                | Chip-Select Programming Common to the GPCM and UPM         | 15–6           |

| 15.3.1              | Address Space Programming                                  |                |

| 15.3.2              | Register Programming Order                                 |                |

| 15.3.3              | Memory Bank Write Protection                               |                |

| 15.3.4              | Address Type Protection                                    |                |

| 15.3.5              | 8-, 16-, and 32-Bit Port Size Configuration                |                |

| 15.3.6              | Parity Configuration                                       | 15–8           |

| 15.3.7              | Memory Bank Protection Status                              | 15–8           |

| 15.3.8              | UPM-Specific Registers                                     | 15–8           |

| 15.3.9              | GPCM-Specific Registers                                    |                |

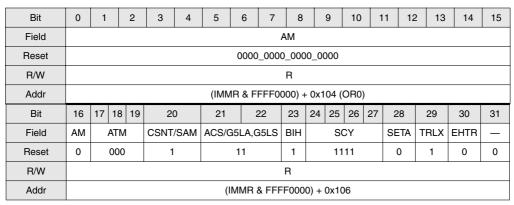

| 15.4                | Register Descriptions                                      | 15–9           |

| 15.4.1              | Base Registers (BRx)                                       |                |

| 15.4.2              | Option Registers (ORx)                                     |                |

| 15.4.3              | Memory Status Register (MSTAT)                             |                |

| 15.4.4              | Machine A Mode Register/Machine B Mode Registers (MxMR)    |                |

| 15.4.5              | Memory Command Register (MCR)                              |                |

| 15.4.6              | Memory Data Register (MDR)                                 |                |

| 15.4.7              | Memory Address Register (MAR)                              |                |

**Contents** xvii

| Paragraph<br>Number | Title N                                                        | Page<br>umber |

|---------------------|----------------------------------------------------------------|---------------|

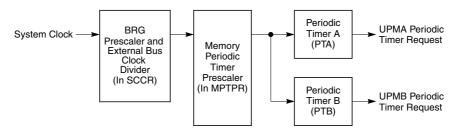

| 15.4.8              | Memory Periodic Timer Prescaler Register (MPTPR)               | 15–18         |

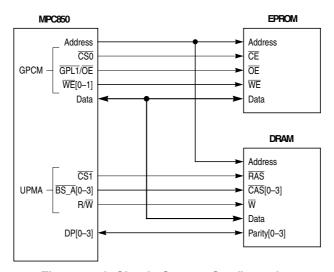

| 15.5                | General-Purpose Chip-Select Machine (GPCM)                     | 15–18         |

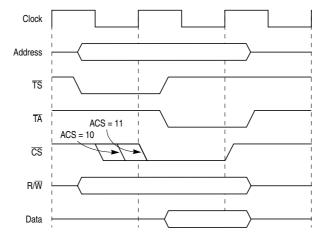

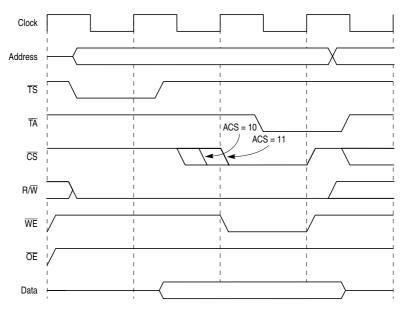

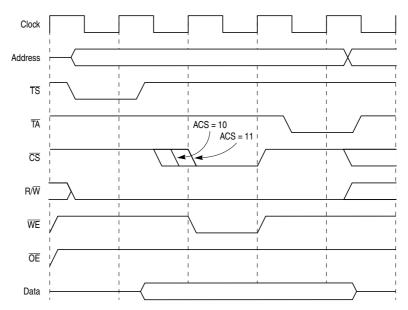

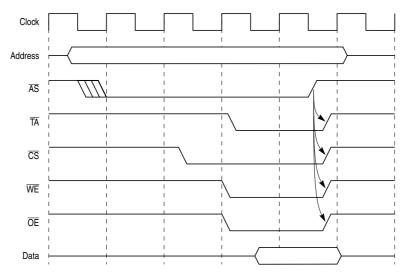

| 15.5.1              | Timing Configuration                                           | 15–19         |

| 15.5.1.1            | Chip-Select Assertion Timing                                   |               |

| 15.5.1.2            | Chip-Select and Write Enable Deassertion Timing                |               |

| 15.5.1.3            | Relaxed Timing                                                 |               |

| 15.5.1.4            | Output Enable (OE) Timing                                      |               |

| 15.5.1.5            | Programmable Wait State Configuration                          |               |

| 15.5.1.6            | Extended Hold Time on Read Accesses                            |               |

| 15.5.2              | Boot Chip-Select Operation                                     | 15–28         |

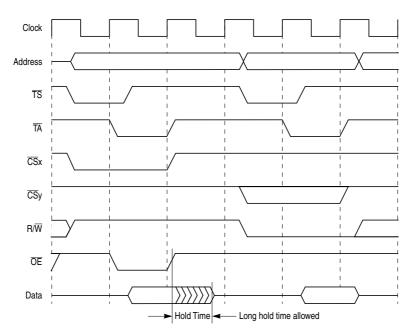

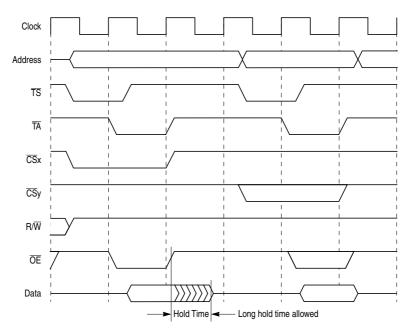

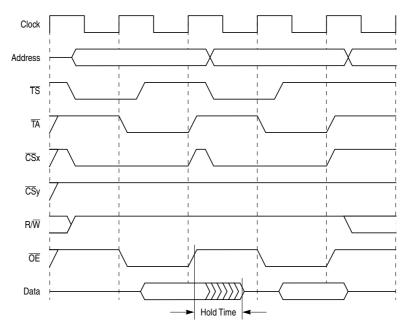

| 15.5.3              | External Asynchronous Master Support                           | 15–29         |

| 15.5.4              | Special Case: Bursting with External Transfer Acknowledge:     | 15–30         |

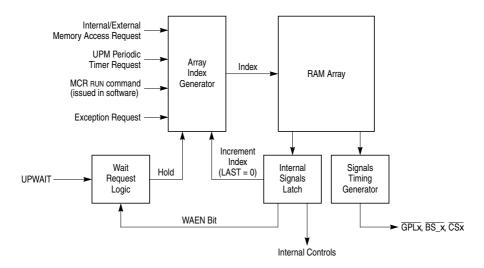

| 15.6                | User-Programmable Machines (UPMs)                              | 15–31         |

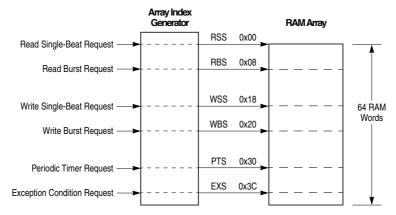

| 15.6.1              | Requests                                                       | 15–32         |

| 15.6.1.1            | Internal/External Memory Access Requests                       | 15–32         |

| 15.6.1.2            | UPM Periodic Timer Requests                                    |               |

| 15.6.1.3            | Software Requests—MCR run Command                              |               |

| 15.6.1.4            | Exception Requests                                             |               |

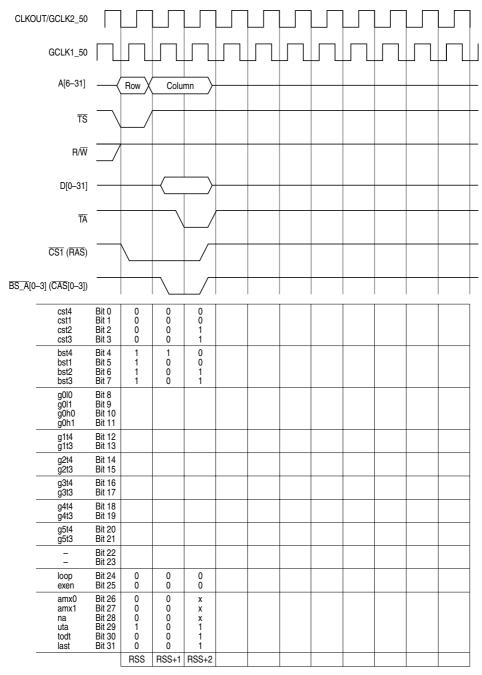

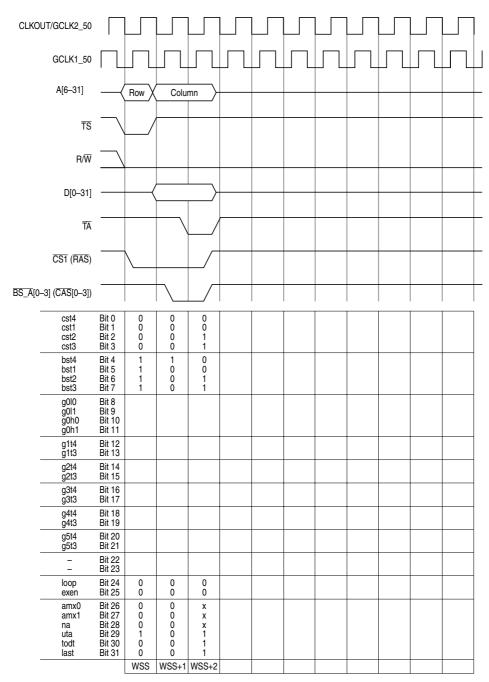

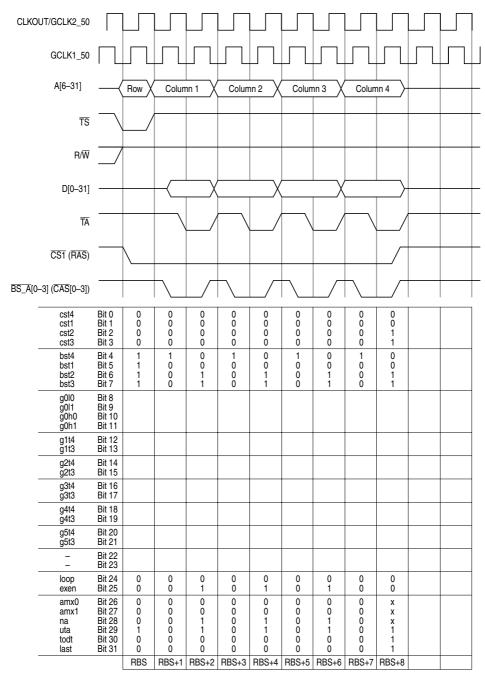

| 15.6.2              | Programming the UPM                                            |               |

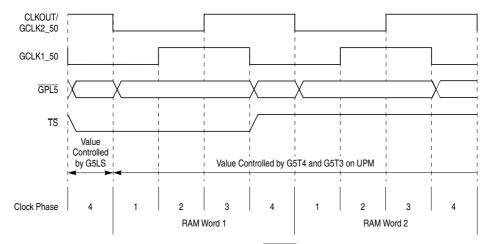

| 15.6.3              | Control Signal Generation Timing                               |               |

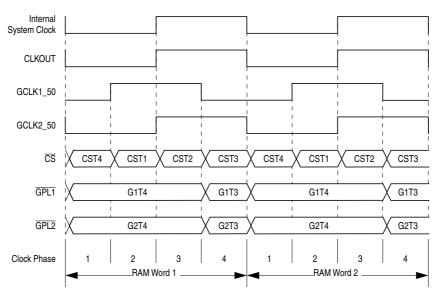

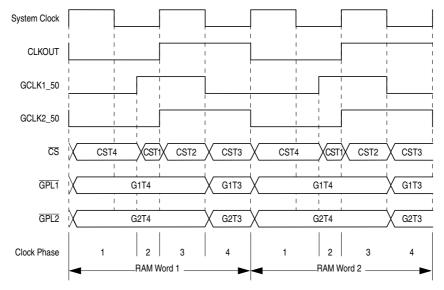

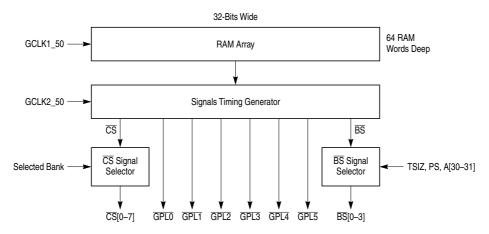

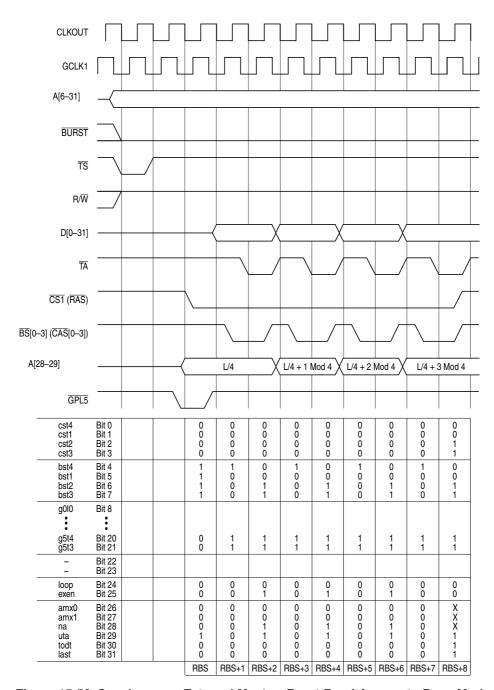

| 15.6.4              | The RAM Array                                                  | 15–37         |

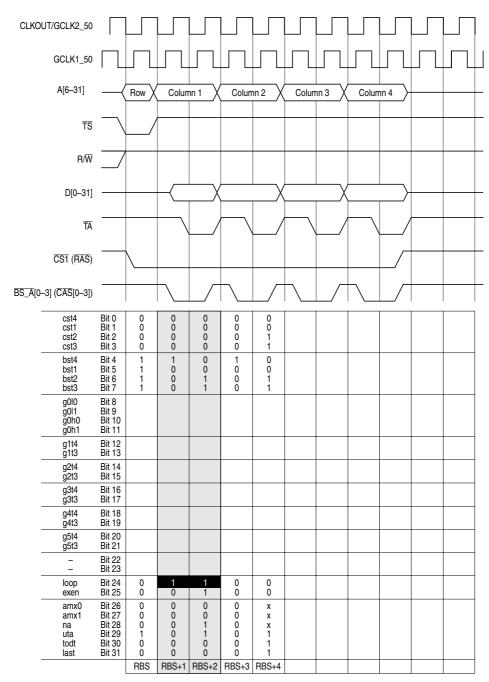

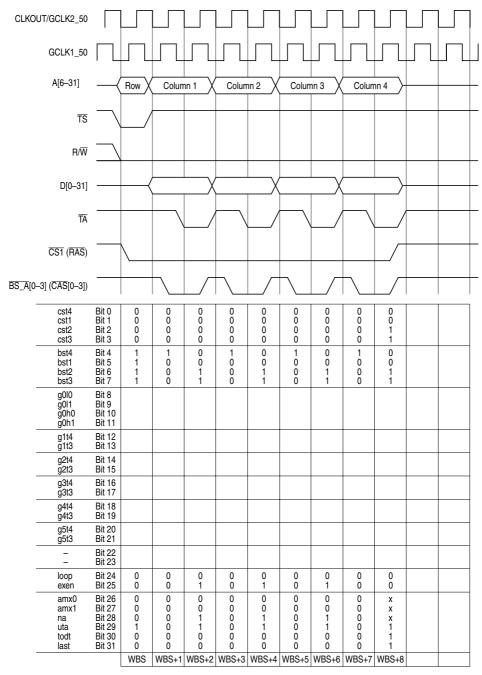

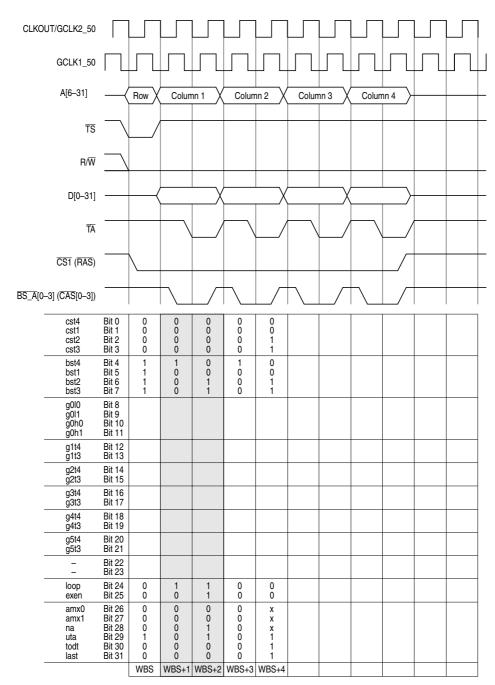

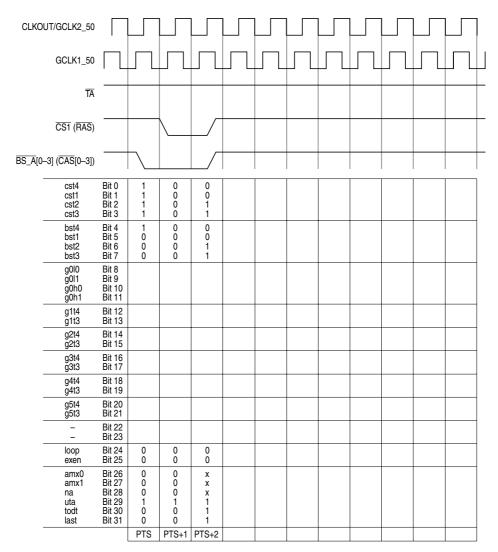

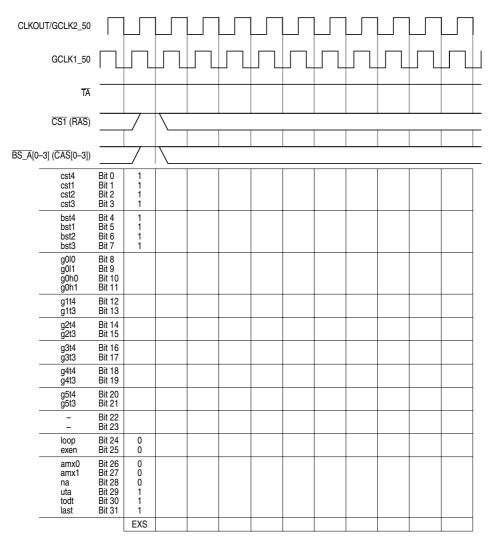

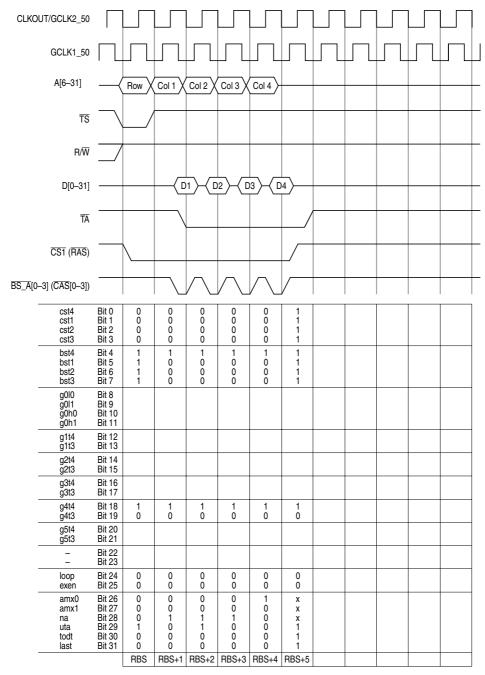

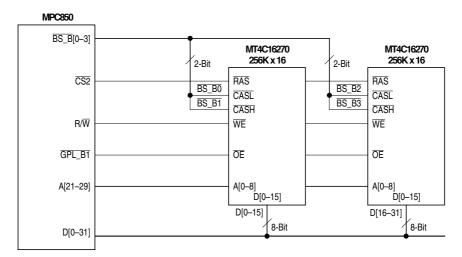

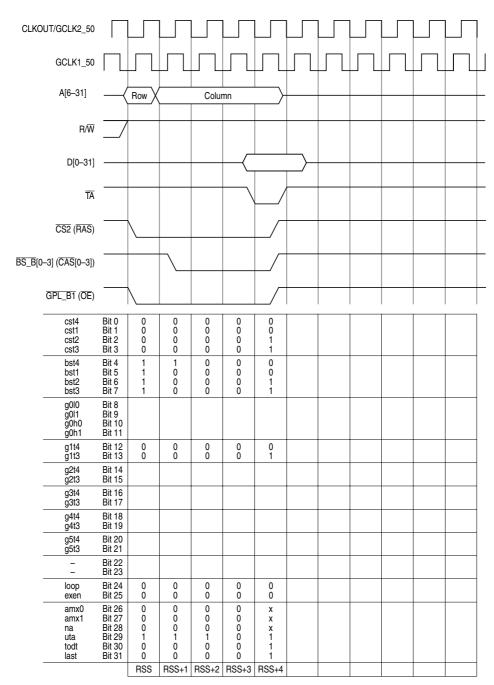

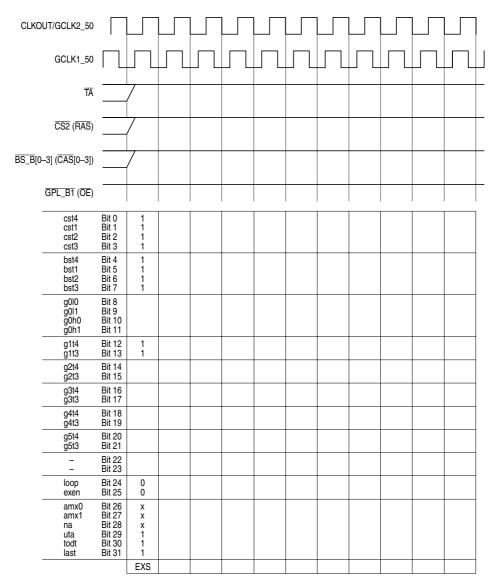

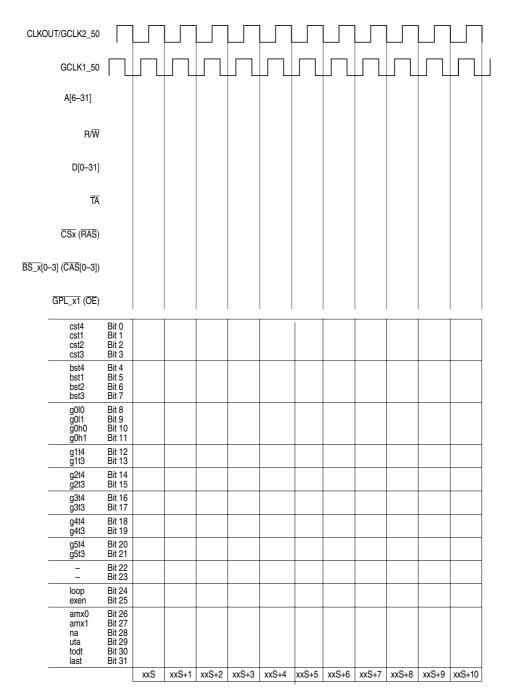

| 15.6.4.1            | RAM Words                                                      |               |

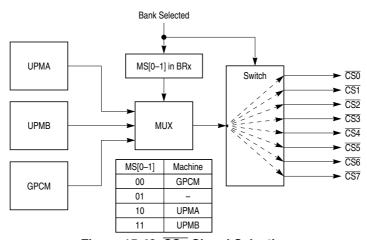

| 15.6.4.2            | Chip-Select Signals (CSTx)                                     | 15–41         |

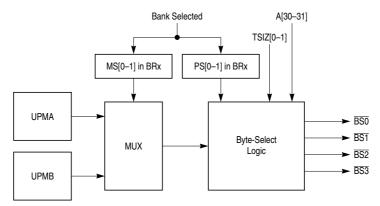

| 15.6.4.3            | Byte-Select Signals (BSTx)                                     |               |

| 15.6.4.4            | General-Purpose Signals (GxTx, G0x)                            |               |

| 15.6.4.5            | Loop Control (LOOP)                                            |               |

| 15.6.4.6            | Exception Pattern Entry (EXEN)                                 |               |

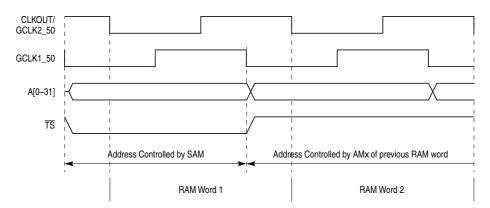

| 15.6.4.7            | Address Multiplexing (AMX)                                     | 15–45         |

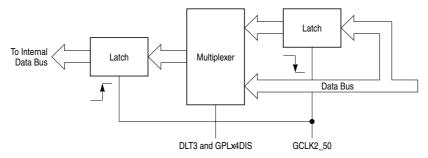

| 15.6.4.8            | Transfer Acknowledge and Data Sample Control (UTA, DLT3)       | 15–50         |

| 15.6.4.9            | Disable Timer Mechanism (TODT)                                 | 15–51         |

| 15.6.4.10           | The Last Word (LAST)                                           | 15–51         |

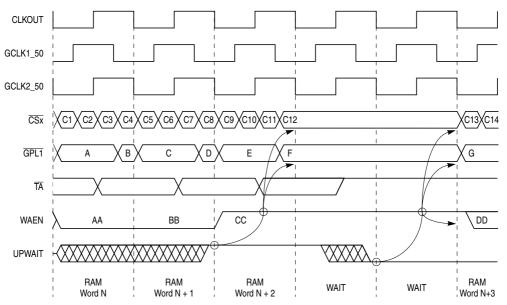

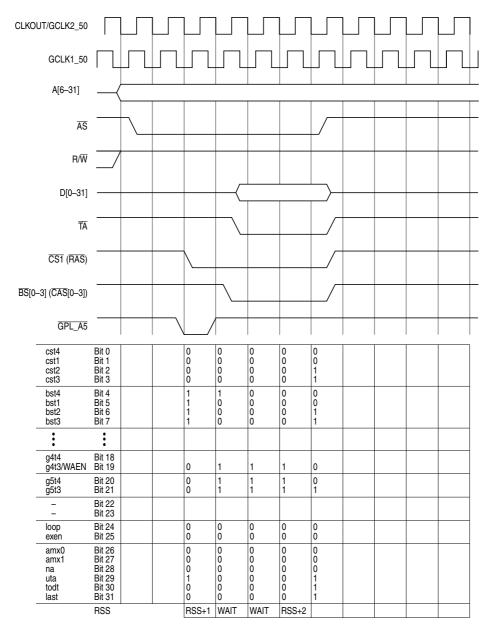

| 15.6.4.11           | The Wait Mechanism (WAEN)                                      | 15–51         |

| 15.6.4.11.1         | Internal and External Synchronous Masters                      |               |

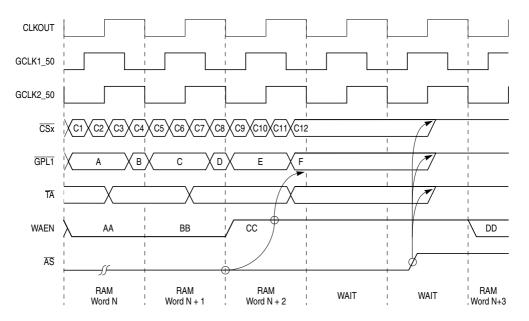

| 15.6.4.11.2         | External Asynchronous Masters                                  | 15–52         |

| 15.7                | Handling Devices with Slow or Variable Access Times            | 15–53         |

| 15.7.1              | Hierarchical Bus Interface Example                             | 15–54         |

| 15.7.2              | Slow Devices Example                                           | 15–54         |

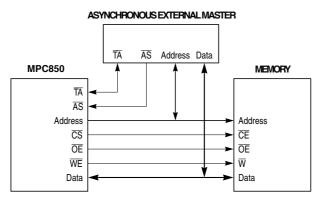

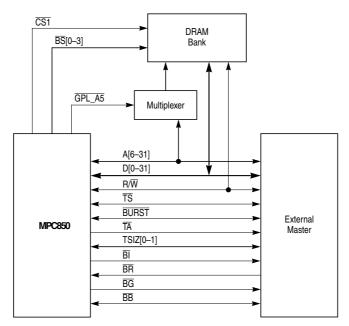

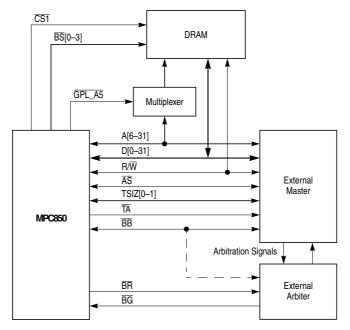

| 15.8                | External Master Support                                        | 15–54         |

| 15.8.1              | Synchronous External Masters                                   | 15–54         |

| 15.8.2              | Asynchronous External Masters                                  |               |

| 15.8.3              | Special Case: Address Type Signals for External Masters        | 15–55         |

| 15.8.4              | UPM Features Supporting External Masters                       |               |

| 15.8.4.1            | Address Incrementing for External Synchronous Bursting Masters | 15–55         |

| Paragraph<br>Number | Title                                                   | Page<br>Number |

|---------------------|---------------------------------------------------------|----------------|

| 15.8.4.2            | Handshake Mechanism for Asynchronous External Masters   | 15–56          |

| 15.8.4.3            | Special Signal for External Address Multiplexer Control |                |

| 15.8.5              | External Master Examples                                |                |

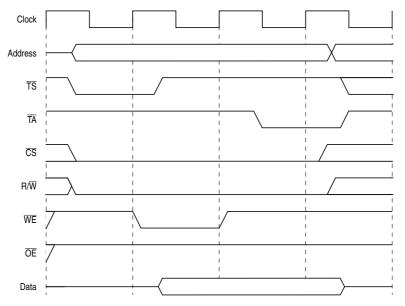

| 15.8.5.1            | External Masters and the GPCM                           | 15–56          |

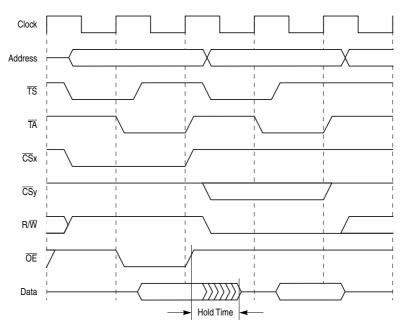

| 15.8.5.2            | External Masters and the UPM                            | 15–58          |

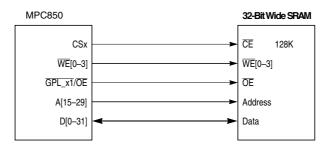

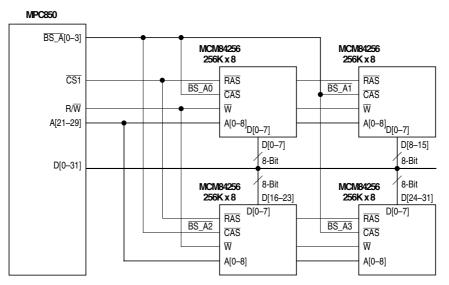

| 15.9                | Memory System Interface Examples                        | 15–63          |

| 15.9.1              | Page-Mode DRAM Interface Example                        | 15–63          |

| 15.9.2              | Page Mode Extended Data-Out Interface Example           | 15–74          |

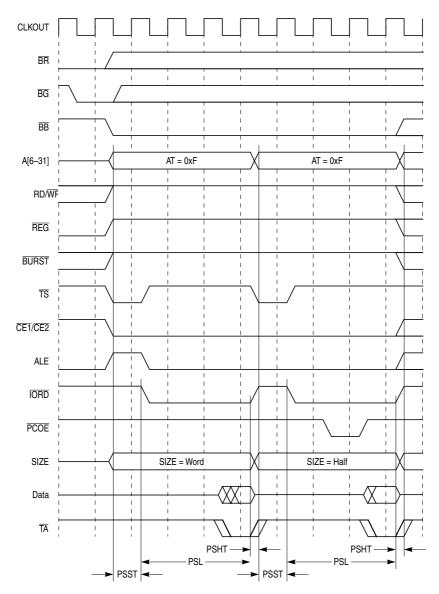

|                     | Chapter 16                                              |                |

|                     | PCMCIA Interface                                        |                |

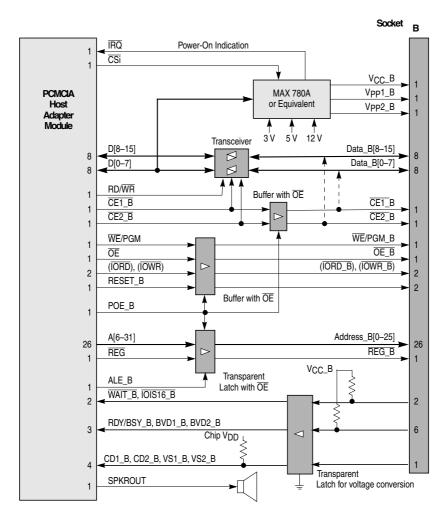

| 16.1                | System Configuration                                    | 16–1           |

| 16.2                | PCMCIA Module Signal Definitions                        |                |

| 16.2.1              | PCMCIA Cycle Control Signals                            | 16–3           |

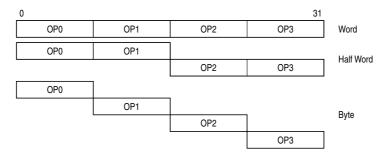

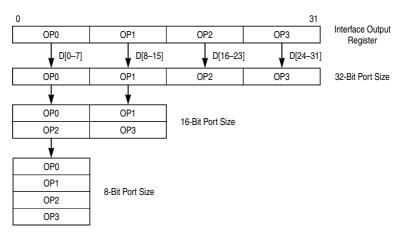

| 16.2.2              | PCMCIA Input Port Signals                               |                |

| 16.2.3              | PCMCIA Output Port Signals (OP[0-4])                    |                |

| 16.2.4              | Other PCMCIA Signals                                    | 16–5           |

| 16.3                | Operation Description                                   | 16–5           |

| 16.3.1              | Memory-Only Cards                                       | 16–6           |

| 16.3.2              | I/O Cards                                               | 16–6           |

| 16.3.3              | Interrupts                                              | 16–6           |

| 16.3.4              | Power Control                                           |                |

| 16.3.5              | Reset and Three-State Control                           | 16–7           |

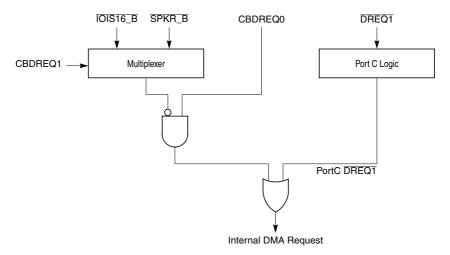

| 16.3.6              | DMA                                                     | 16–7           |

| 16.4                | Programming Model                                       |                |

| 16.4.1              | PCMCIA Interface Input Pins Register (PIPR)             | 16–8           |

| 16.4.2              | PCMCIA Interface Status Changed Register (PSCR)         |                |

| 16.4.3              | PCMCIA Interface Enable Register (PER)                  |                |

| 16.4.4              | PCMCIA Interface General Control Register B (PGCRB)     |                |

| 16.4.5              | PCMCIA Base Registers 0–7 (PBR0–PBR7)                   |                |

| 16.4.6              | PCMCIA Option Register 0–7 (POR0–POR7)                  |                |

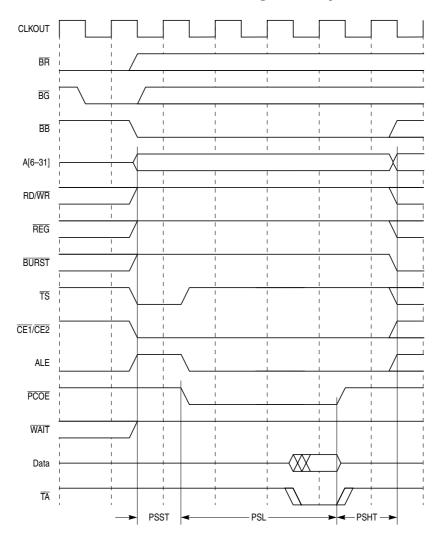

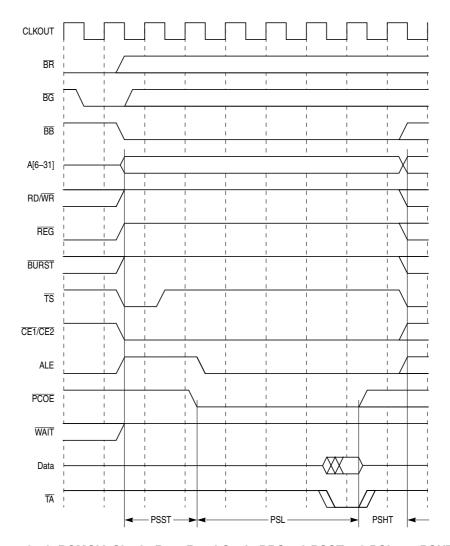

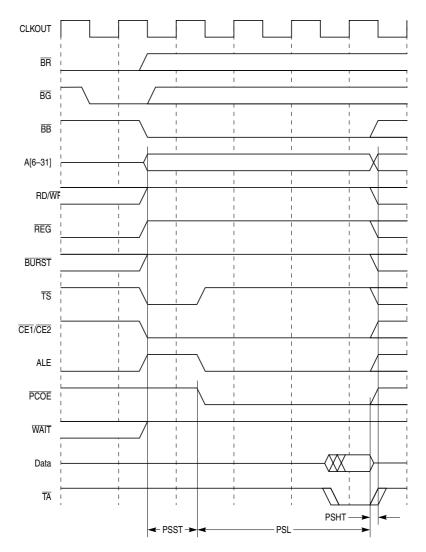

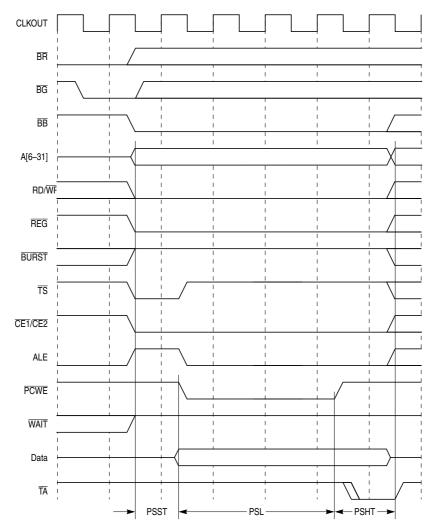

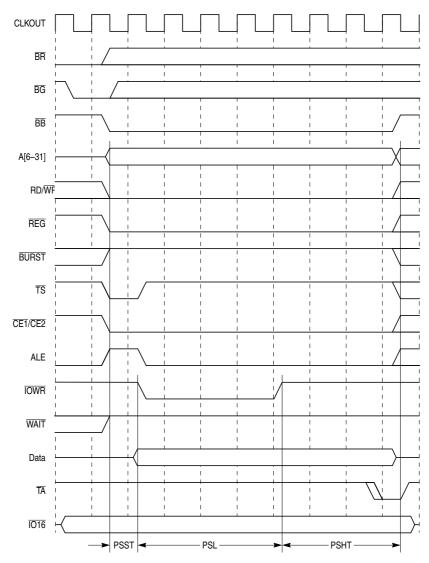

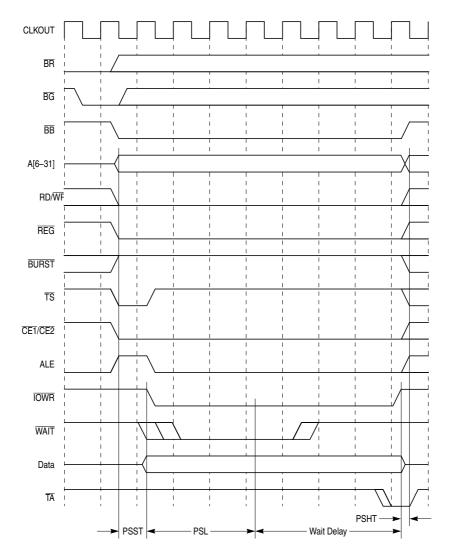

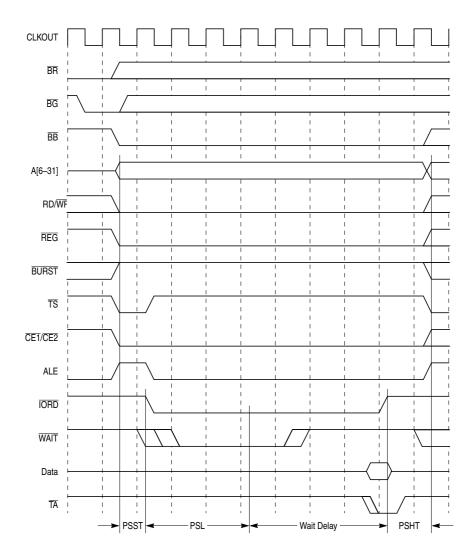

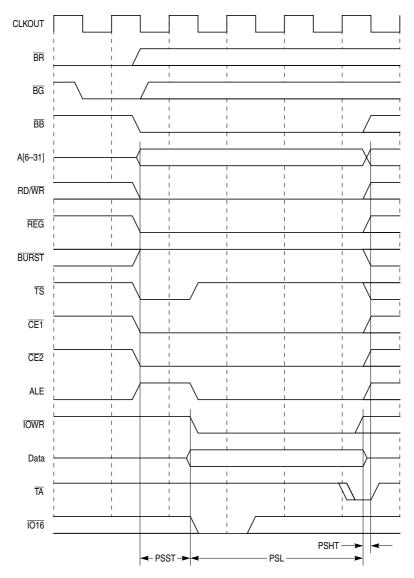

| 16.5                | PCMCIA Controller Timing Examples                       | 16–16          |

**Contents** xix

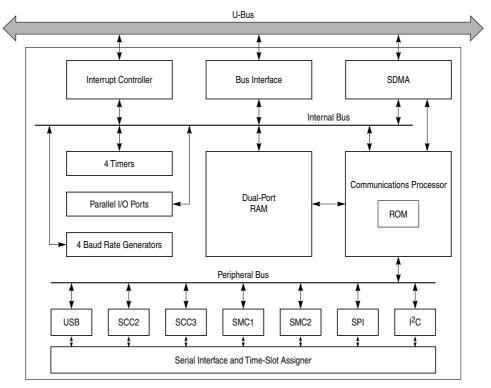

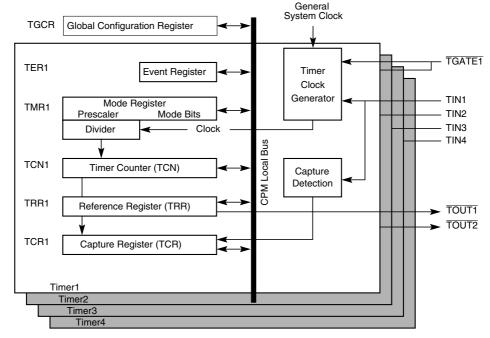

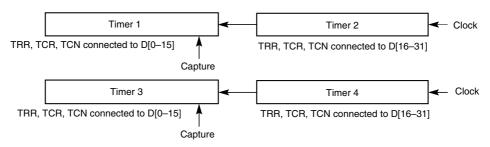

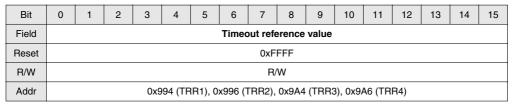

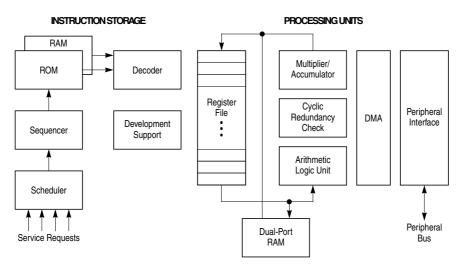

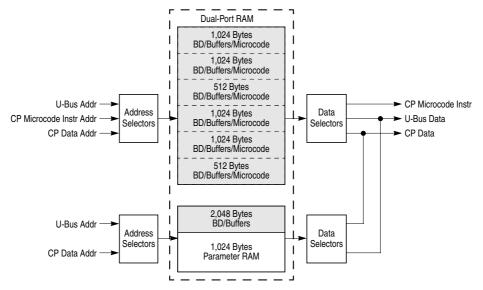

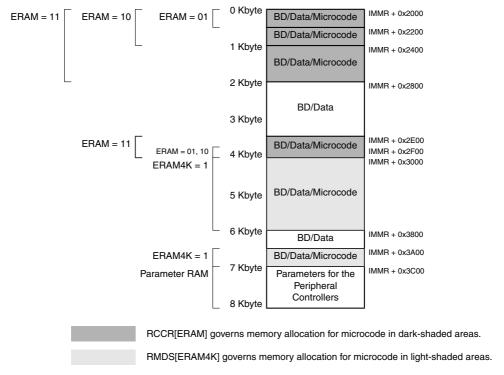

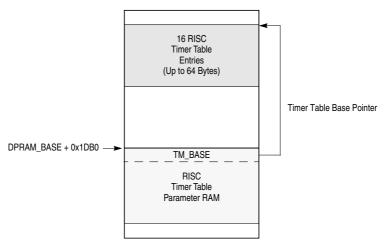

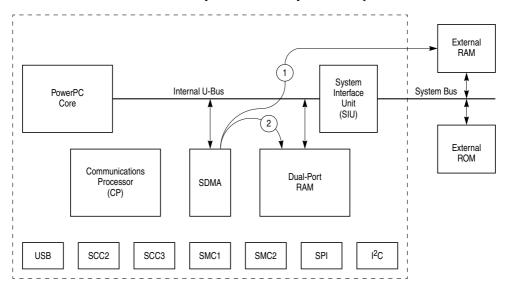

**Paragraph** Page Title Number Number Part V **Communications Processor Module** Chapter 17 Communications Processor Module and CPM Timers 17.1 Features 17–1 17.2 17.2.1 17.2.2 17.2.2.1 Timer Clock Source 17–6 17.2.2.2 17.2.2.3 17.2.2.4 17.2.2.5 17.2.2.6 17.2.3 17.2.3.1 17.2.4 17.2.4.1 17.2.4.2 17.2.4.3 17.2.4.4 17.2.5 Chapter 18 **Communications Processor** Features 18–1 18.1 18.2 18.3 18.4 18.5 18.5.1 18.5.2 RISC Microcode Development Support Control Register (RMDS) .............. 18-5 18.5.3 18.5.4 18.5.4.1 18.5.4.2 18.6 Dual-Port RAM 18–9 18.6.1 18.6.2

| Paragraph<br>Number | Title                                                  | Page<br>Number |

|---------------------|--------------------------------------------------------|----------------|

| 18.6.3              | Parameter RAM                                          | 18–12          |

| 18.7                | The RISC Timer Table                                   |                |

| 18.7.1              | RISC Timer Table Scan Algorithm                        | 18–14          |

| 18.7.2              | The set timer Command                                  |                |

| 18.7.3              | RISC Timer Table Parameter RAM and Timer Table Entries | 18–14          |

| 18.7.3.1            | RISC Timer Command Register (TM_CMD)                   | 18–15          |

| 18.7.3.2            | RISC Timer Table Entries                               |                |

| 18.7.4              | RISC Timer Event Register (RTER)/Mask Register (RTMR)  |                |

| 18.7.5              | PWM Mode                                               |                |

| 18.7.6              | RISC Timer Initialization                              |                |

| 18.7.7              | RISC Timer Interrupt Handling                          |                |

| 18.7.8              | Using the RISC Timers to Track CP Loading              | 18–18          |

|                     | Chapter 19                                             |                |

|                     | SDMA Channels and IDMA Emulation                       |                |

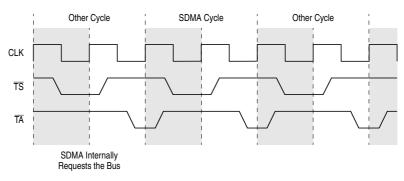

| 19.1                | SDMA Channels                                          | 19–1           |

| 19.1.1              | SDMA Transfers                                         |                |

| 19.1.2              | U-Bus Arbitration and the SDMA Channels                |                |

| 19.2                | SDMA Registers                                         |                |

| 19.2.1              | SDMA Configuration Register (SDCR)                     |                |

| 19.2.2              | SDMA Status Register (SDSR)                            |                |

| 19.2.3              | SDMA Mask Register (SDMR)                              |                |

| 19.2.4              | SDMA Address Register (SDAR)                           | 19–5           |

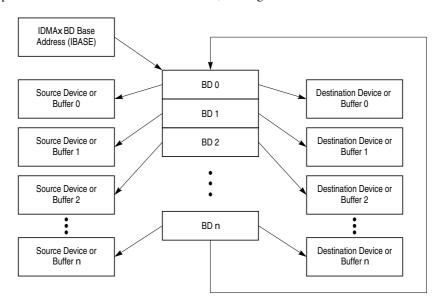

| 19.3                | IDMA Emulation                                         | 19–5           |

| 19.3.1              | IDMA Features                                          |                |

| 19.3.2              | IDMA Parameter RAM                                     |                |

| 19.3.3              | IDMA Registers                                         |                |

| 19.3.3.1            | DMA Channel Mode Registers (DCMR)                      |                |

| 19.3.3.2            | IDMA Status Registers (IDSR1 and IDSR2)                |                |

| 19.3.3.3            | IDMA Mask Registers (IDMR1 and IDMR2)                  |                |

| 19.3.4              | IDMA Buffer Descriptors (BD)                           |                |

| 19.3.4.1            | Function Code Registers—SFCR and DFCR                  |                |

| 19.3.4.2            | Auto-Buffering and Buffer-Chaining                     | 19–12          |

| 19.3.5              | IDMA CP Commands                                       |                |

| 19.3.6              | IDMA Channel Operation                                 |                |

| 19.3.6.1            | Activating an IDMA Channel                             |                |

| 19.3.6.2            | Suspending an IDMA Channel                             |                |

| 19.3.7              | IDMA Interface Signals—DREQ and SDACK                  |                |

| 19.3.7.1            | IDMA Requests for Memory/Memory Transfers              |                |

| 19.3.7.2            | IDMA Requests for Peripheral/Memory Transfers          |                |

| 19.3.7.2.1          | Level-Sensitive Requests                               | 19–14          |

**Contents** xxi

| Paragraph<br>Number | Title                                                    | Page<br>Number |

|---------------------|----------------------------------------------------------|----------------|

| 19.3.7.2.2          | Edge-Sensitive Requests                                  | 19–15          |

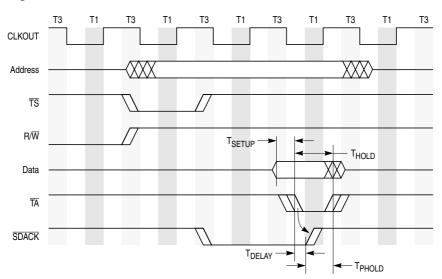

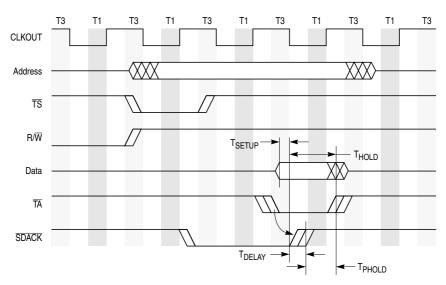

| 19.3.8              | IDMA Transfers — Dual-Address and Single-Address         | 19–15          |

| 19.3.8.1            | Dual-Address (Dual-Cycle) Transfer                       | 19–15          |

| 19.3.8.2            | Single-Address (Single-Cycle) Transfer (Fly-By)          | 19–16          |

| 19.3.9              | Single-Buffer Mode on IDMA1—A Special Case               | 19–18          |

| 19.3.9.1            | IDMA1 Channel Mode Register (DCMR) (Single-Buffer Mode). |                |

| 19.3.9.2            | IDMA1 Status Register (IDSR1) (Single-Buffer Mode)       | 19–19          |

| 19.3.9.3            | IDMA1 Mask Register (IDMR1) (Single-Buffer Mode)         | 19–20          |

| 19.3.9.4            | Burst Timing (Single-Buffer Mode)                        |                |

| 19.3.10             | External Recognition of an IDMA Transfer                 | 19–21          |

| 19.3.11             | Interrupts During an IDMA Bus Transfer                   | 19–22          |

|                     | Chapter 20<br>Serial Interface                           |                |

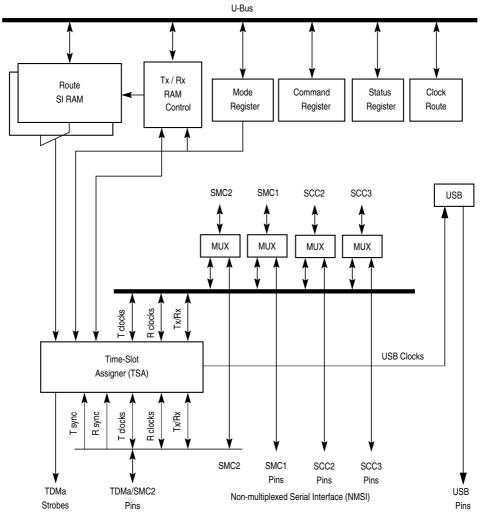

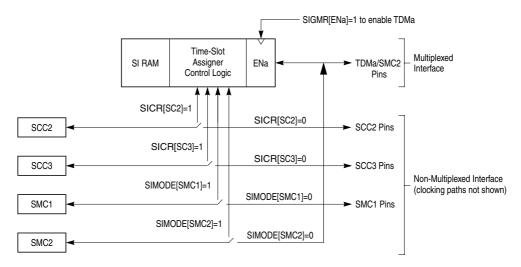

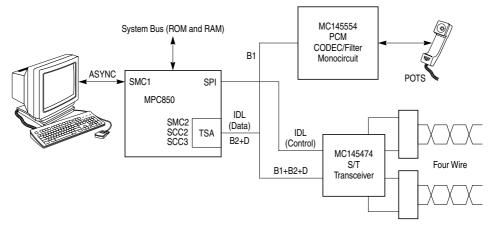

| 20.1                | SI Features                                              | 20–2           |

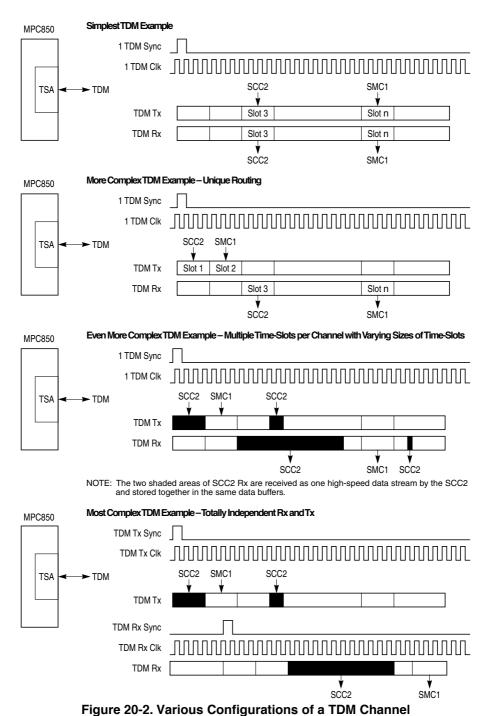

| 20.2                | The Time-Slot Assigner (TSA)                             | 20–3           |

| 20.2.1              | TSA Signals                                              | 20–7           |

| 20.2.2              | Enabling Connections to the TSA                          | 20–7           |

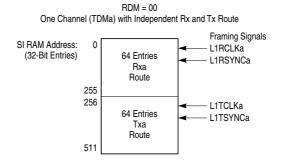

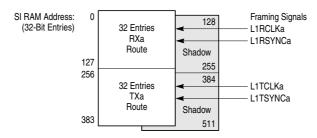

| 20.2.3              | SI RAM                                                   | 20–8           |

| 20.2.3.1            | Disabling and Reenabling the TSA                         | 20–8           |

| 20.2.3.2            | TDMa Channel with Static Frames                          | 20–8           |

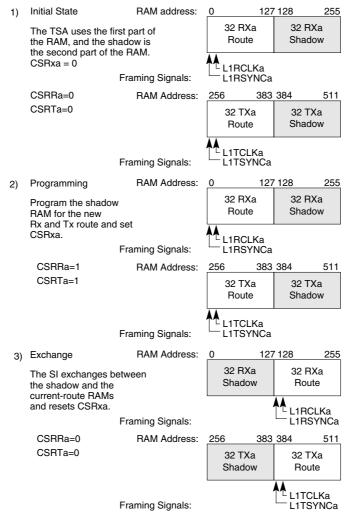

| 20.2.3.3            | SI RAM Dynamic Changes                                   | 20–8           |

| 20.2.3.4            | TDMa Channel with Dynamic Frames                         | 20–10          |

| 20.2.3.5            | Programming the SI RAM                                   | 20–11          |

| 20.2.3.6            | SI RAM Programming Example                               | 20–13          |

| 20.2.4              | The SI Registers                                         | 20–14          |

| 20.2.4.1            | SI Global Mode Register (SIGMR)                          | 20–14          |

| 20.2.4.2            | SI Mode Register (SIMODE)                                | 20–14          |

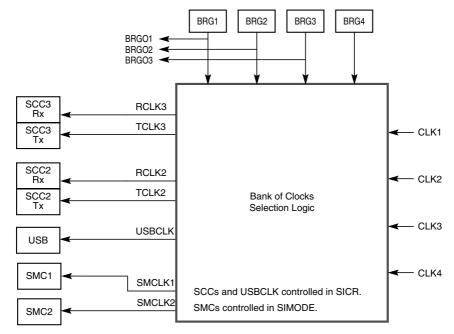

| 20.2.4.3            | SI Clock Route Register (SICR)                           | 20–20          |

| 20.2.4.4            | SI Command Register (SICMR)                              | 20–22          |

| 20.2.4.5            | SI Status Register (SISTR)                               | 20–22          |

| 20.2.4.6            | SI RAM Pointer Register (SIRP)                           | 20–23          |

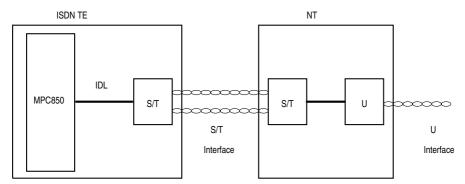

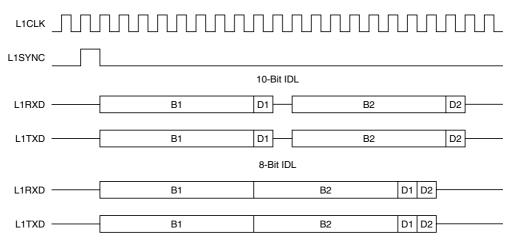

| 20.2.5              | IDL Bus Implementation                                   |                |

| 20.2.5.1            | ISDN Terminal Adaptor Application                        |                |

| 20.2.5.2            | Programming the IDL Interface                            |                |

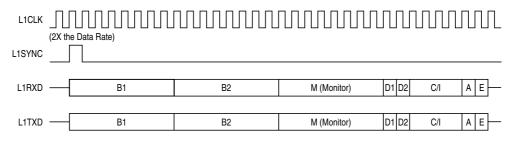

| 20.2.6              | GCI Bus Implementation                                   |                |

| 20.2.6.1            | GCI Activation/Deactivation                              |                |

| 20.2.6.2            | Programming the GCI Interface                            |                |

| 20.2.6.2.1          | Normal Mode                                              | 20–30          |

| 20.2.6.2.2          | SCIT Mode                                                |                |

| 20.2.6.3            | GCI Interface (SCIT Mode) Programming Example            |                |

| Paragraph<br>Number | Title                                                   | Page<br>Number |

|---------------------|---------------------------------------------------------|----------------|

| 20.3                | NMSI Configuration                                      | 20–32          |

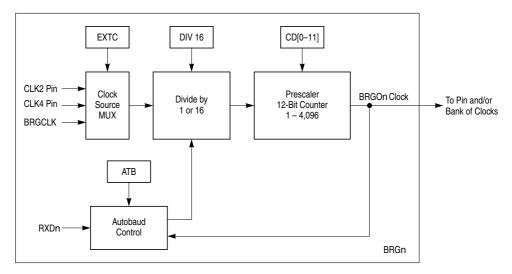

| 20.4                | Baud Rate Generators (BRGs)                             |                |

| 20.4.1              | Baud Rate Generator Configuration Registers (BRGCn)     |                |

| 20.4.2              | Autobaud Operation on the SCC UART                      |                |

| 20.4.3              | UART Baud Rate Examples                                 |                |

|                     | Chapter 21                                              |                |

|                     | Serial Communications Controllers                       |                |

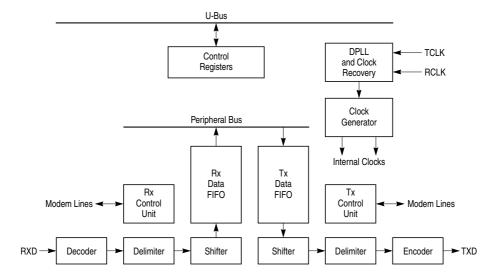

| 21.1                | Features                                                | 21–2           |

| 21.2                | SCC Registers                                           |                |

| 21.2.1              | General SCC Mode Register (GSMR)                        |                |

| 21.2.2              | Protocol-Specific Mode Register (PSMR)                  |                |

| 21.2.3              | Data Synchronization Register (DSR)                     |                |

| 21.2.4              | Transmit-on-Demand Register (TODR)                      |                |

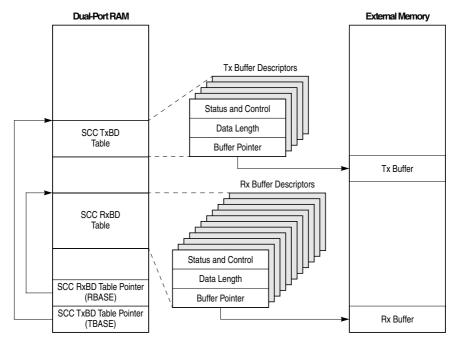

| 21.3                | SCC Buffer Descriptors (BDs)                            |                |

| 21.4                | SCC Parameter RAM                                       |                |

| 21.4.1              | Function Code Registers (RFCR and TFCR)                 |                |

| 21.4.2              | Handling SCC Interrupts                                 |                |

| 21.4.3              | SCC Initialization                                      |                |

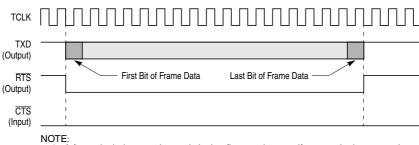

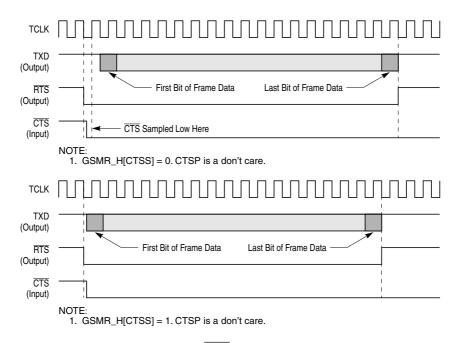

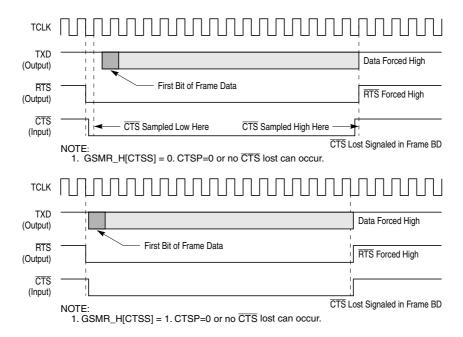

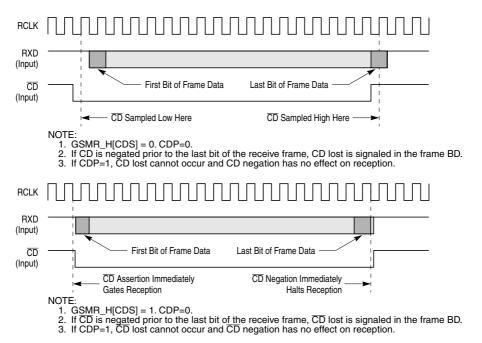

| 21.4.4              | Controlling SCC Timing with RTS, CTS, and CD            |                |

| 21.4.4.1            | Synchronous Protocols                                   |                |

| 21.4.4.2            | Asynchronous Protocols                                  | 21–20          |

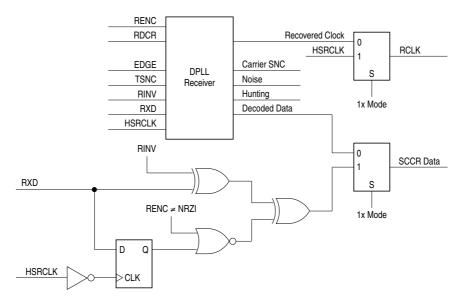

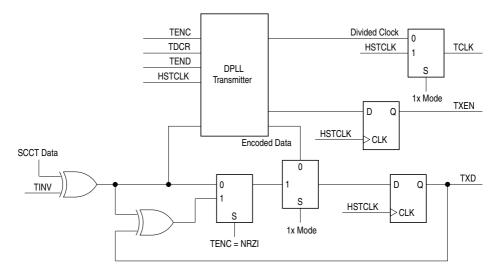

| 21.4.5              | Digital Phase-Locked Loop (DPLL) Operation              |                |

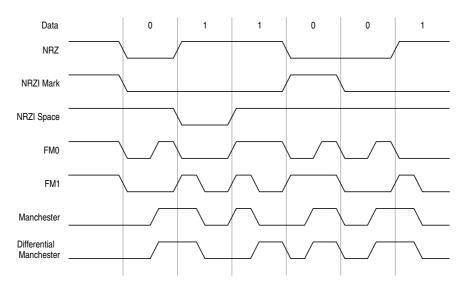

| 21.4.5.1            | Encoding Data with a DPLL                               |                |

| 21.4.6              | Clock Glitch Detection                                  |                |

| 21.4.7              | Reconfiguring the SCCs                                  |                |

| 21.4.7.1            | General Reconfiguration Sequence for an SCC Transmitter |                |

| 21.4.7.2            | Reset Sequence for an SCC Transmitter                   |                |

| 21.4.7.3            | General Reconfiguration Sequence for an SCC Receiver    |                |

| 21.4.7.4            | Reset Sequence for an SCC Receiver                      |                |

| 21.4.7.5            | Switching Protocols                                     |                |

| 21.4.8              | Saving Power                                            |                |

|                     | Chapter 22                                              |                |

|                     | SCC UART Mode                                           |                |

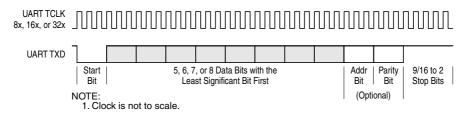

| 22.1                | Features                                                | 22–2           |

| 22.2                | Normal Asynchronous Mode                                | 22–3           |