# Freescale Semiconductor Reference Manual Addendum

# MCF5485 Reference Manual Errata

by: Microcontroller Solutions Group

This errata document describes corrections to the *MCF5485 Reference Manual*, order number MCF5485RM. For convenience, the addenda items are grouped by revision. Please check our website at <a href="http://www.freescale.com/coldfire">http://www.freescale.com/coldfire</a> for the latest updates.

The current version available of the *MCF5485 Reference Manual* is Revision 5.

#### **Table of Contents**

| 1 | Errata for Revision 5   |

|---|-------------------------|

| 2 | Errata for Revision 4   |

| 3 | Errata for Revision 3   |

|   | Errata for Revision 2.1 |

| 5 | Revision History 1      |

# 1 Errata for Revision 5

None to report.

# 2 Errata for Revision 4

Table 1. MCF5485RM Rev 4 Errata

| Location                  | Description                                                                                                                                                                                                                                                             |                                                                                                                                                            |                                                   |                                                                 |                               |  |  |

|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|-----------------------------------------------------------------|-------------------------------|--|--|

| Chapter 1                 | Corrected maximum frequency errors throughout. PCI: 50 MHz, FlexBus: 50 MHz, SDRAM: 100 and 200 MHz                                                                                                                                                                     |                                                                                                                                                            |                                                   |                                                                 |                               |  |  |

| Table 1-2/Page 1-7        | Replace with the following table:                                                                                                                                                                                                                                       |                                                                                                                                                            |                                                   |                                                                 |                               |  |  |

|                           | AD[12:8] <sup>1</sup>                                                                                                                                                                                                                                                   | Clock<br>Ratio                                                                                                                                             | CLKIN–PCI and<br>FlexBus Frequency<br>Range (MHz) | Internal XLB, SDRAM bus,<br>and PSTCLK Frequency<br>Range (MHz) | Core Frequency<br>Range (MHz) |  |  |

|                           | 00011                                                                                                                                                                                                                                                                   | 1:2                                                                                                                                                        | 41.67–50.0                                        | 83.33–100                                                       | 166.66–200                    |  |  |

|                           | 00101                                                                                                                                                                                                                                                                   | 1:2                                                                                                                                                        | 25.0–41.67                                        | 50.0-83.33                                                      | 100.0–166.66                  |  |  |

|                           | 01111                                                                                                                                                                                                                                                                   | 1:4                                                                                                                                                        | 25.0                                              | 100                                                             | 200                           |  |  |

| Section 1.4.6.7/Page 1-10 | Change last s                                                                                                                                                                                                                                                           | entence                                                                                                                                                    | to: "The two CAN cor                              | ntrollers can interface to two                                  | senarate 16 messa             |  |  |

| Section 1.4.6.7/Fage 1-10 |                                                                                                                                                                                                                                                                         | Change last sentence to: "The two CAN controllers can interface to two separate 16 message buffer CAN networks or a single 32 message buffer CAN network." |                                                   |                                                                 |                               |  |  |

| Table 2-1/Page 2-3        | Remove extraneous overbars from the following signals: TSIZ1, TSIZ0 Add overbar to PCITRDY.                                                                                                                                                                             |                                                                                                                                                            |                                                   |                                                                 |                               |  |  |

| Table 2-1/Page 2-6        | E1MDIO entry: Remove 'Y' from pull-up column. This signal cannot be configured as a GPIO so there is no pull-up.  E1MDC entry: Remove 'Y' from pull-up column. This signal cannot be configured as a GPIO so there is no pull-up. Change I/O entry from "O:I/O" to "O". |                                                                                                                                                            |                                                   |                                                                 |                               |  |  |

| Table 2-2/Page 2-10       | Remove extraneous overbars from the following pin/signals: A15/DSI, W23/DSPICS5, AA23/IVDD, AA25/PCS0TXD, AB26/PPSC1PSC02. Add overbar to B13/RSTI.                                                                                                                     |                                                                                                                                                            |                                                   |                                                                 |                               |  |  |

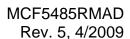

| Table 2-4/Page 2-22       | Replace with the following table:                                                                                                                                                                                                                                       |                                                                                                                                                            |                                                   |                                                                 |                               |  |  |

|                           | AD[12:8] <sup>1</sup>                                                                                                                                                                                                                                                   | Clock<br>Ratio                                                                                                                                             | CLKIN–PCI and<br>FlexBus Frequency<br>Range (MHz) | Internal XLB, SDRAM bus,<br>and PSTCLK Frequency<br>Range (MHz) | Core Frequency<br>Range (MHz) |  |  |

|                           | 00011                                                                                                                                                                                                                                                                   | 1:2                                                                                                                                                        | 41.67–50.0                                        | 83.33–100                                                       | 166.66–200                    |  |  |

|                           | 00101                                                                                                                                                                                                                                                                   | 1:2                                                                                                                                                        | 25.0-41.67                                        | 50.0-83.33                                                      | 100.0–166.66                  |  |  |

|                           | 01111                                                                                                                                                                                                                                                                   | 1:4                                                                                                                                                        | 25.0                                              | 100                                                             | 200                           |  |  |

|                           | NOTES:  1 All other va                                                                                                                                                                                                                                                  | alues of Al                                                                                                                                                | D[12:8] are reserved.                             |                                                                 |                               |  |  |

| Table 2-7/Page 2-24       | Swap the bit s                                                                                                                                                                                                                                                          |                                                                                                                                                            |                                                   | /hen AD3 is asserted, BE[3:0                                    | ] are asserted for bo         |  |  |

| Location                  |                                                                                                              | Description                                                                                                                                                        |           |                          |                               |                            |  |

|---------------------------|--------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--------------------------|-------------------------------|----------------------------|--|

| Section 2.2.8.2/Page 2-26 |                                                                                                              | Change sentence from "This is the USB cable Vbus monitor input." to "This is the USB cable Vbus monitor input, which is 5 V tolerant."                             |           |                          |                               |                            |  |

| Section 7.13/Page 7-30    |                                                                                                              | Change value written to D0 in first line of code from 0xA30C_8100 to 0xA70C_8100 to enable cache-inhibited, imprecise mode.                                        |           |                          |                               |                            |  |

| Table 10-1/Page 10-2      | Re                                                                                                           | place with t                                                                                                                                                       | he follov | ving table:              |                               |                            |  |

|                           |                                                                                                              | AD[12:8] <sup>1</sup> Clock Ratio CLKIN-PCI and FlexBus Frequency Range (MHz) Internal XLB, SDRAM bus, and PSTCLK Frequency Range (MHz) Core Frequency Range (MHz) |           |                          |                               |                            |  |

|                           |                                                                                                              | 00011                                                                                                                                                              | 1:2       | 41.67–50.0               | 83.33–100                     | 166.66–200                 |  |

|                           |                                                                                                              | 00101                                                                                                                                                              | 1:2       | 25.0–41.67               | 50.0-83.33                    | 100.0–166.66               |  |

|                           |                                                                                                              | 01111                                                                                                                                                              | 1:4       | 25.0                     | 100                           | 200                        |  |

| Table 44 4/Days 44 2      | NOTES:  1 All other values of AD[12:8] are reserved.                                                         |                                                                                                                                                                    |           |                          |                               | I becomission of the shape |  |

| Table 11-1/Page 11-2      | Change GSR <i>n</i> 's Access entry to R/W as some status bits may be cleared by writing a 1 to them.        |                                                                                                                                                                    |           |                          |                               |                            |  |

| Figure 11-4/Page 11-7     | Change GSR n[TEXP, PWMP, COMP, CAPT] bits' write row to 'w1c' as they may be written with a 1 to clear them. |                                                                                                                                                                    |           |                          |                               |                            |  |

| Table 12-1/Page 12-1      | Cha                                                                                                          | Change SSRn's Access entry to R/W as some status bits may be cleared by writing a 1 to them.                                                                       |           |                          |                               |                            |  |

| Figure 12-4/Page 12-4     | Ch                                                                                                           | ange SSR <i>r</i>                                                                                                                                                  | BE, ST    | ] bits' write row to 'w1 | c' as they may be written wit | h a 1 to clear them.       |  |

# Table 1. MCF5485RM Rev 4 Errata (continued)

| Location                 | Description                                                                                         |                                                                                  |                      |                                                                |                     |  |

|--------------------------|-----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|----------------------|----------------------------------------------------------------|---------------------|--|

| Table 13-1/Page 13-2     | Replace table with the one below to better illustrate the interrupt priority and level assignments. |                                                                                  |                      |                                                                |                     |  |

|                          |                                                                                                     | Interrupt<br>Level<br>ICR[IL]                                                    | Priority<br>ICR[IP]  | Supported Interrupt<br>Sources                                 |                     |  |

|                          |                                                                                                     |                                                                                  | 7 6                  | 40.62                                                          |                     |  |

|                          |                                                                                                     |                                                                                  | 5<br>4               | - #8–63                                                        |                     |  |

|                          |                                                                                                     | 7                                                                                | — (Mid-point)        | #7 (IRQ7)                                                      |                     |  |

|                          |                                                                                                     |                                                                                  | 2 1 0                | #8–63                                                          |                     |  |

|                          |                                                                                                     |                                                                                  | 7–4                  | #8–63                                                          |                     |  |

|                          |                                                                                                     | 6                                                                                | — (Mid-point)        | #6 (IRQ6)                                                      |                     |  |

|                          |                                                                                                     |                                                                                  | 3–0                  | #8–63                                                          |                     |  |

|                          |                                                                                                     |                                                                                  | 7–4                  | #8–63                                                          |                     |  |

|                          |                                                                                                     | 5                                                                                | — (Mid-point)        | #5 (IRQ5)                                                      |                     |  |

|                          |                                                                                                     |                                                                                  | 3–0                  | #8–63                                                          |                     |  |

|                          |                                                                                                     | _                                                                                | 7–4                  | #8-63                                                          |                     |  |

|                          |                                                                                                     | 4                                                                                | — (Mid-point)        | #4 (IRQ4)                                                      |                     |  |

|                          |                                                                                                     |                                                                                  | 3–0<br>7–4           | #8–63<br>#8–63                                                 |                     |  |

|                          |                                                                                                     | 3                                                                                | — (Mid-point)        | #3 (IRQ3)                                                      |                     |  |

|                          |                                                                                                     | Ŭ                                                                                | 3–0                  | #8-63                                                          |                     |  |

|                          |                                                                                                     |                                                                                  | 7–4                  | #8–63                                                          |                     |  |

|                          |                                                                                                     | 2                                                                                | — (Mid-point)        | #2 (IRQ2)                                                      |                     |  |

|                          |                                                                                                     |                                                                                  | 3–0                  | #8-63                                                          |                     |  |

|                          |                                                                                                     |                                                                                  | 7–4                  | #8–63                                                          |                     |  |

|                          |                                                                                                     | 1                                                                                | — (Mid-point)        | #1 (IRQ1)                                                      |                     |  |

|                          |                                                                                                     |                                                                                  | 3–0                  | #8–63                                                          |                     |  |

| Chapter 17               | Change insta                                                                                        | nces throughout of                                                               | 4-1-1-1 to 3-1-1-1,  | 4-2-2-2 to 3-2-2-2, and 3                                      | 3-1-1-1 to 2-1-1-1. |  |

| Section 17.1.1/Page 17-1 | Change FlexE                                                                                        | Bus maximum oper                                                                 | ating frequency fror | m 66 MHz to 50 MHz.                                            |                     |  |

| Figure 17-28/Page 17-28  |                                                                                                     | Remove internal termination dashed lines for FBCS, BE/BWE, TBST, and OE signals. |                      |                                                                |                     |  |

| Figure 17-32/Page 17-30  |                                                                                                     |                                                                                  |                      | , BE/BWE, TBST, and O                                          |                     |  |

| Figure 17-34/Page 17-31  | Remove inter                                                                                        | nal termination das                                                              | shed lines for FBCS  | , $\overline{BE/BWE}$ , $\overline{TBST}$ , and $\overline{O}$ | E signals.          |  |

| Table 21-2/Page 21-8     | Change MAX                                                                                          | MB description fror                                                              | ກ "This 6-bit field" | to "This 4-bit field"                                          |                     |  |

| Location                      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Section 22.4.4.5/Page 22-8    | Add the following at the end of the RNG section:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                               | There is no known cryptographic proof showing that this is a secure method of generating random data. In fact, there may be an attack against the random number generator if its output is used directly in a cryptographic application (the attack is based on the linearity of the internal shift registers). In light of this, it is highly recommended to use the random data produced by this module as an input seed to a NIST-approved (based on DES or SHA-1) or cryptographically-secure (RSA generator or BBS generator) random number generation algorithm.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                               | It is also recommended to use other sources of entropy along with the RNG to generate the seed to the pseudorandom algorithm. The more random sources combined to create the seed the better. The following is a list of sources which can be easily combined with the output of this module.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                               | <ul> <li>Current time using highest precision possible</li> <li>Mouse and keyboard motions (or equivalent if being used on a cell phone or PDA)</li> <li>Other entropy supplied directly by the user</li> </ul> NOTE Condemnation Details and Details an |

|                               | See Appendix D of the NIST Special Publication 800-90 "Recommendation for Random Number Generation Using Deterministic Random Bit Generators" for more information:  • http://csrc.nist.gov                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Table 27-2/Page 27-4          | Correct PSCRFCR and PSCTFCR from 8 bits to 32 bits wide in memory map.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Section 27.7.2                | Correct PSCRFCR and PSCTFCR values from 0F to 0C00_0000 throughout examples. Change WRITE TAG = 00 to WFR = 0 throughout examples.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Table 27-41/Page 27-49        | In step #1, change value of PSCSICR to 00 and remove the RxDCD sub-row as this bit is not implemented.  In step #6, change value of PSCACR to 01 and remove the IEC1 sub-row as this bit is not implemented.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Table 27-44/Page 27-52        | In step #6, remove the IEC1 sub-row as this bit is not implemented.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Section 28.7.2.4/Page 28-21   | Change second sentence from "The TX FIFO holds from 1 to 16 longwords" to "The TX FIFO holds from 1 to 4 longwords"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Section 28.7.2.5/Page 28-22   | Change second sentence from "The RX FIFO holds from 1 to 16 received" to "The RX FIFO holds from 1 to 4 received"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Chapter 30                    | Add note to beginning of chapter:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                               | CAUTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                               | The MCF548x devices contain a silicon errata that affects the usage of the USB device controller. Please see MCF5485 Device Errata (MCF5485DE) at http://www.freescale.com/coldfire for details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Section 30.3.4.5.2/Page 30-54 | Add the following to the end of step #5: "In the case of a Control Read, an empty Data OUT packet is used in the status stage to indicate a successful transfer. To accomplish this, the TXZERO bit in the EPnOUTSR should also be set."                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Table 31-4/Page 31-6          | Correct MIB block counters end addresses to MBAR + 0x92FF and MBAR + 0x9AFF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Table 32-1/Page 32-1          | Remove extraneous overbars from the following signals: SDDATA31, SDADDR4, SDDATA16, SDDQS2, VSS, EVDD, USBVDD, SDBA1, SDBA0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

# Table 1. MCF5485RM Rev 4 Errata (continued)

| Location                | Description                                                                                                                                                                                                                                                             |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 32-1/Page 32-8   | Remove extraneous overbars from the following pin/signals: B5/SDDQS2, B6/SDDATA21, C6/SDVDD, D4/SDDATA16, D6/VSS. Change F1 from 'SDDDATA10' to 'SDDATA10' (remove extra D). Change B3 from 'SDDDATA18' to 'SDDATA18' (remove extra D).                                 |

| Figure 32-2/Page 32-9   | Remove extraneous overbars from the following pin/signals: A15/DSI/TDI, A16/TCK, A18/MTMOD1, A19/PLLVDD, A21/PSTDDATA1, A23/PSTDDATA7, B15/TMS, B22/E1RXCLK, C15/DSCLK, C21/VSS, C25/SCL, E24/EVDD, H23/IVDD, H24/EVDD.                                                 |

| Figure 32-3/Page 32-10  | Remove extraneous overbars from the following pin/signals: P4/IVDD, AF2/AD25                                                                                                                                                                                            |

| Figure 32-4/Page 32-11  | Remove extraneous overbars from the following pin/signals: U24/EVDD, V26/PCIAD30, AA25/PSC0TXD, AC18/VSS, AC20/IVDD, AC26/PSC2TXD, AE18/USBVDD, AE21/PSC3RXD, AF18/USBRBIAS, AF21/TIN2, AF22/TIN0.                                                                      |

| Figure 32-5/Page 32-12  | Remove extraneous overbars from the following pin/signals: B5/SDDQS2, B6/SDDATA21, C6/SDVDD, D4/SDDATA16, D6/VSS. Change F1 from 'SDDDATA10' to 'SDDATA10' (remove extra D). Change B3 from 'SDDDATA18' to 'SDDATA18' (remove extra D).                                 |

| Figure 32-6/Page 32-13  | Remove extraneous overbars from the following pin/signals: A15/DSI/TDI, A16/TCK, A18/MTMOD1, A19/PLLVDD, A21/PSTDDATA1, A23/PSTDDATA7, B15/TMS, C21/VSS, C25/SCL, E24/EVDD, H23/IVDD, H24/EVDD.                                                                         |

| Figure 32-7/Page 32-14  | Remove extraneous overbars from the following pin/signals: P4/IVDD, AF2/AD25.                                                                                                                                                                                           |

| Figure 32-8/Page 32-15  | Remove extraneous overbars from the following pin/signals: U24/EVDD, V26/PCIAD30, AA25/PSC0TXD, AC18/VSS, AC20/IVDD, AC26/PSC2TXD, AE18/USBVDD, AE21/PSC3RXD, AF18/USBRBIAS, AF21/TIN2, AF22/TIN0.                                                                      |

| Figure 32-9/Page 32-16  | Remove extraneous overbars from the following pin/signals: B5/SDDQS2, B6/SDDATA21, C6/SDVDD, D4/SDDATA16, D6/VSS. Change F1 from 'SDDDATA10' to 'SDDATA10' (remove extra D). Change B3 from 'SDDDATA18' to 'SDDATA18' (remove extra D).                                 |

| Figure 32-10/Page 32-17 | Remove extraneous overbars from the following pin/signals: A15/DSI/TDI, A16/TCK, A18/MTMOD1, A19/PLLVDD, A21/PSTDDATA1, A23/PSTDDATA7, B15/TMS, B22/E1RXCLK, C15/DSCLK, C21/VSS, C25/SCL, E24/EVDD, H23/IVDD, H24/EVDD.                                                 |

| Figure 32-11/Page 32-18 | Remove extraneous overbars from the following pin/signals: P4/IVDD, AF2/AD25                                                                                                                                                                                            |

| Figure 32-12/Page 32-19 | Remove extraneous overbars from the following pin/signals: U24/EVDD, V26/PCIAD30, AA25/PSC0TXD, AC18/VSS, AC20/IVDD, AC26/PSC2TXD, AE21/PSC3RXD, AF18/USBRBIAS, AF21/TIN2, AF22/TIN0. Change figure title from "MCF5485/5484 Lower Right" to "MCF5481/5480 Lower Right" |

| Section 32.6/Page 32-20 | Update package drawing. See <a href="http://www.freescale.com">http://www.freescale.com</a> and do a keyword search for 98ARS23880W for the updated drawing.                                                                                                            |

Table 2. MCF5485RM Rev 3 Errata

| Location                   |                  |                                                                                        | Description                                                                                                                                                            |                           |  |  |

|----------------------------|------------------|----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|--|--|

| Section 29.1.2/Page 29-1   | Added the follow | Added the following note at the end of the features list:                              |                                                                                                                                                                        |                           |  |  |

|                            | NOTE             |                                                                                        |                                                                                                                                                                        |                           |  |  |

|                            |                  | The USB 2.0 device controller requires a minimum XLB/system clock frequency of 66 MHz. |                                                                                                                                                                        |                           |  |  |

| Section 29.1.3.1/Page 29-2 | Added the follow | Added the following note at the end of this section:                                   |                                                                                                                                                                        |                           |  |  |

|                            |                  |                                                                                        | NOTE                                                                                                                                                                   |                           |  |  |

|                            |                  |                                                                                        | device controller requires a ck frequency of 66 MHz.                                                                                                                   | minimum                   |  |  |

| Section 25.1.3/Page 25-3   | Replaced the C   | omm Timer Extern                                                                       | al Clock table with the following                                                                                                                                      |                           |  |  |

|                            |                  | Table 25-1 C                                                                           | omm Timers External Clock                                                                                                                                              |                           |  |  |

|                            |                  | Channel                                                                                | External Signal                                                                                                                                                        |                           |  |  |

|                            |                  | 0                                                                                      | PSC0BCLK                                                                                                                                                               |                           |  |  |

|                            |                  | 1                                                                                      | PSC1BCLK                                                                                                                                                               |                           |  |  |

|                            |                  | 2                                                                                      | PSC2BCLK                                                                                                                                                               |                           |  |  |

|                            |                  | 3                                                                                      | PSC3BCLK                                                                                                                                                               |                           |  |  |

|                            |                  | 4                                                                                      | TIN0                                                                                                                                                                   |                           |  |  |

|                            |                  | 5                                                                                      | TIN1                                                                                                                                                                   |                           |  |  |

|                            |                  | 6                                                                                      | TIN2                                                                                                                                                                   |                           |  |  |

|                            |                  | 7                                                                                      | TIN3                                                                                                                                                                   |                           |  |  |

| _                          | Added FIFO Co    | ntroller chapter tha                                                                   | at describes the features of the FI                                                                                                                                    | FO controller implemented |  |  |

|                            | on many of the   | communication pe                                                                       | ripherals.                                                                                                                                                             | ·                         |  |  |

| Section 29.2.1/Page 29-5   | Added the follow | ving additional not                                                                    | e below the existing note:                                                                                                                                             |                           |  |  |

|                            |                  | not be accessed with a stable VE                                                       | gisters (offsets 0xB000 to 0xB3Ff<br>d until the MCF548x is connected<br>BUS. The interrupt generated at th<br>ling (USBISR[RSTSTOP]) can be<br>stable USB connection. | to a USB<br>ne end of     |  |  |

# Table 2. MCF5485RM Rev 3 Errata (continued)