# Xtrinsic FXLC95000CL Intelligent Motion-Sensing Platform

Hardware Reference Manual

Document Number: FXLC95000CLHWRM

Rev 0.6, May 2013

### **Contents**

| Sec | tion n  | umber Title                                                          | Page |

|-----|---------|----------------------------------------------------------------------|------|

|     |         | Chapter 1 About This Document                                        |      |

| 1.1 | Purpos  | se                                                                   | 25   |

| 1.2 | Audier  | nce                                                                  | 25   |

| 1.3 | Termin  | nology and Conventions                                               | 25   |

|     | 1.3.1   | Terminology                                                          | 25   |

|     | 1.3.2   | Conventions                                                          | 26   |

|     | 1.3.3   | Register figure conventions.                                         | 27   |

| 1.4 | Relate  | d Documentation.                                                     | 28   |

| 1.5 | Refere  | enced documents                                                      | 28   |

|     |         | Chapter 2 Introduction                                               |      |

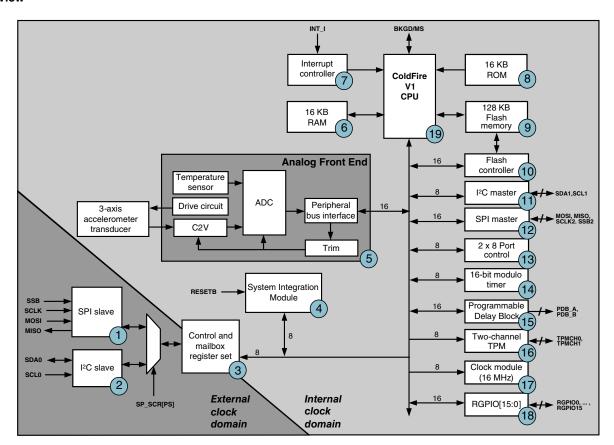

| 2.1 | Overvi  | iew                                                                  | 29   |

| 2.2 | Hardw   | vare features                                                        | 31   |

|     |         | Chapter 3 Pins and Connections (PINS)                                |      |

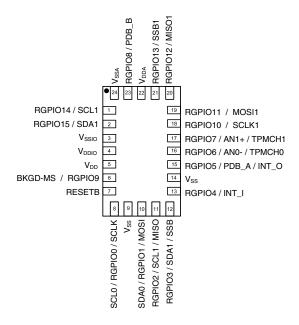

| 3.1 | Pins ar | nd Connections (PINS)                                                | 33   |

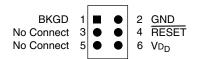

|     | 3.1.1   | Pin function description.                                            | 34   |

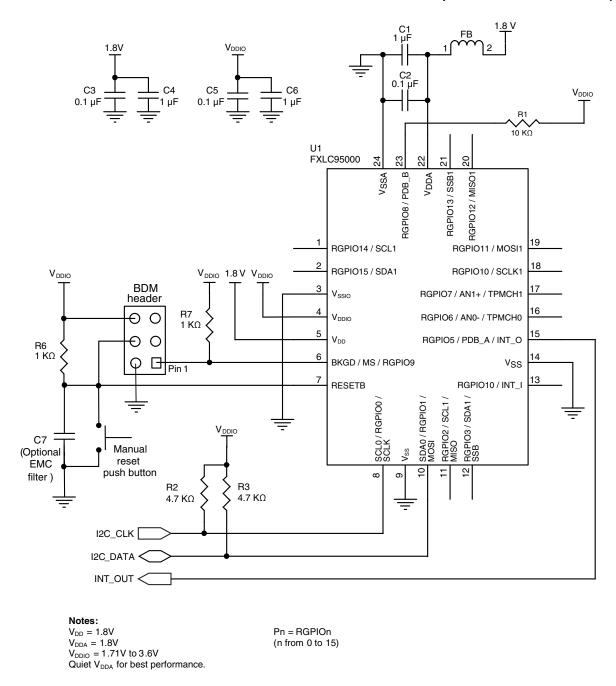

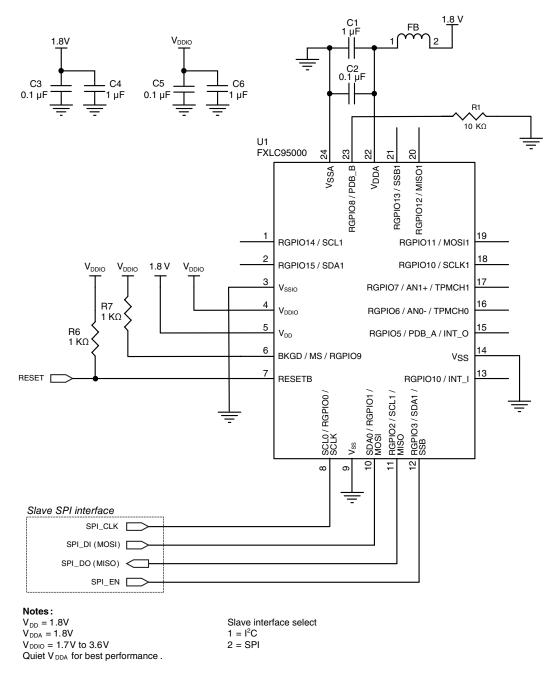

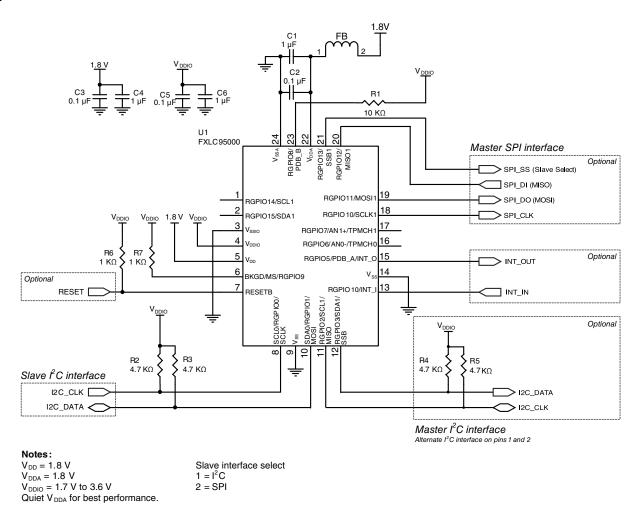

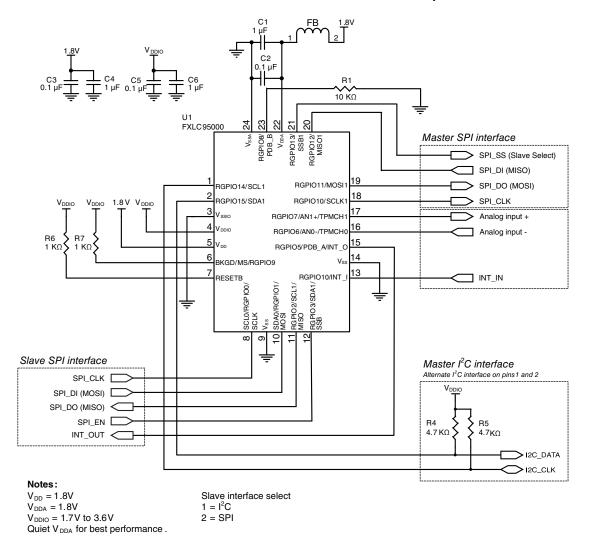

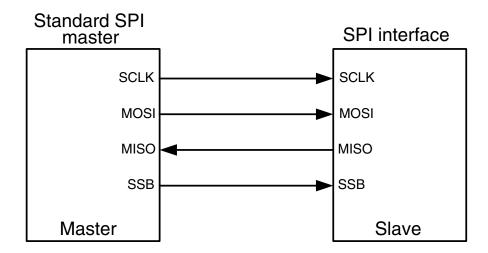

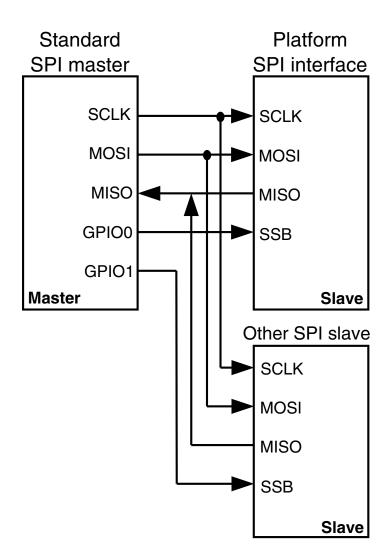

| 3.2 | System  | n connections.                                                       | 37   |

|     | 3.2.1   | Power supply considerations.                                         | 38   |

|     | 3.2.2   | FXLC95000CL as an intelligent slave                                  | 38   |

|     | 3.2.3   | FXLC95000CL as a sensor hub                                          | 40   |

|     | 3.2.4   | RESETB pin.                                                          | 43   |

|     | 3.2.5   | Background/Mode Select (BKGD/MS)                                     | 44   |

|     |         | Chapter 4<br>Memory Maps (MEMORY)                                    |      |

| 4.1 | High-l  | level memory map                                                     | 45   |

| 4.2 | Read-a  | after-write sequence and required serialization of memory operations | 47   |

| Sec | tion nu | umber Title                                                  | Page |

|-----|---------|--------------------------------------------------------------|------|

| 4.3 | Memor   | y alignment issues                                           | 47   |

| 4.4 | Memor   | y maps for on-chip peripherals                               | 48   |

|     | 4.4.1   | Rapid General Purpose Input/Output (RGPIO) register summary  | 48   |

|     | 4.4.2   | Slave Interface (SLAVE) register summary                     | 49   |

|     | 4.4.3   | Master I2C (MI2C) register summary                           | 51   |

|     | 4.4.4   | System Integration Module (SIM) register summary             | 51   |

|     | 4.4.5   | On-Chip Oscillator (CLKGEN) register summary                 | 52   |

|     | 4.4.6   | Modulo Timer 16-bit (MTIM16) register summary                | 52   |

|     | 4.4.7   | Pin Interrupt (IRQ) register summary                         | 53   |

|     | 4.4.8   | Port Control 0 (PC0) register summary                        | 53   |

|     | 4.4.9   | Port Control 1 (PC1) register summary                        | 53   |

|     | 4.4.10  | Timer Pulse-Width Modulator (TPM) register summary           | 54   |

|     | 4.4.11  | Programmable Delay Block (PDB) register summary              | 54   |

|     | 4.4.12  | Flash Memory Controller (FLASH) register summary             | 55   |

|     | 4.4.13  | Analog Front End (AFE) register summary                      | 55   |

|     | 4.4.14  | Queued Serial Peripheral Interface (QSPI) register summary   | 56   |

|     | 4.4.15  | ColdFire V1 Interrupt Controller (CF1_INTC) register summary | 56   |

| 4.5 | Interru | ot vector table                                              | 57   |

| 4.6 | RAM a   | ddressing and data                                           | 60   |

|     |         | Chapter 5 Slave Interface (SLAVE)                            |      |

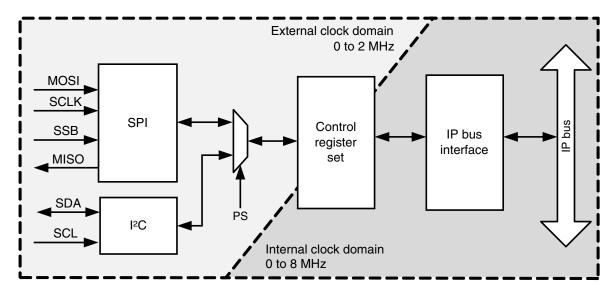

| 5.1 | Introdu | ction                                                        | 61   |

|     | 5.1.1   | I2C features and limitations.                                | 62   |

|     |         | 5.1.1.1 I2C features                                         | 63   |

|     |         | 5.1.1.2 I2C limitations                                      | 63   |

|     | 5.1.2   | SPI features and limitations.                                | 64   |

|     |         | 5.1.2.1 SPI features                                         | 66   |

|     |         | 5.1.2.2 SPI limitations                                      | 67   |

| 5.2 | Slave p | ort module memory map                                        | 67   |

| Sec        | tion nu | umber Title                                                                | Page |

|------------|---------|----------------------------------------------------------------------------|------|

| 5.3        | Data re | ad/write coherency issues                                                  | 68   |

|            | 5.3.1   | Read buffer                                                                | 69   |

|            | 5.3.2   | Binary semaphore (mutex) operation                                         | 71   |

| 5.4        | Slave n | nemory map and register definition                                         | 72   |

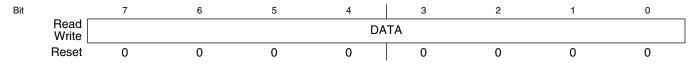

|            | 5.4.1   | Slave port mailbox registers n (SLAVE_SP_MBn)                              | 72   |

|            | 5.4.2   | Slave port binary semaphore (mutex) register n (SLAVE_SP_MUTEXn, n=0 or 1) | 73   |

|            | 5.4.3   | Slave port I2C address register (SLAVE_SP_ADDR)                            | 74   |

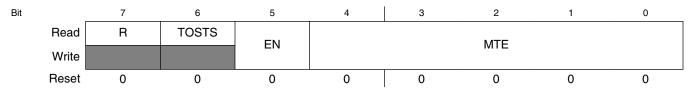

|            | 5.4.4   | Slave port status and control register (SLAVE_SP_SCR)                      | 74   |

|            | 5.4.5   | Slave port write status register 0 (SLAVE_SP_WSTS0)                        | 76   |

|            | 5.4.6   | Slave port write status register 1 (SLAVE_SP_WSTS1)                        | 77   |

|            | 5.4.7   | Slave port write status register 2 (SLAVE_SP_WSTS2)                        | 78   |

|            | 5.4.8   | Slave port write status register 3 (SLAVE_SP_WSTS3)                        | 78   |

|            | 5.4.9   | Slave port read status register 0 (SLAVE_SP_RSTS0)                         | 79   |

|            | 5.4.10  | Slave port read status register 1 (SLAVE_SP_RSTS1)                         | 80   |

|            | 5.4.11  | Slave port read status register 2 (SLAVE_SP_RSTS2)                         | 81   |

|            | 5.4.12  | Slave port read status register 3 (SLAVE_SP_RSTS3)                         | 82   |

|            | 5.4.13  | Slave port mutext timeout register n (SLAVE_SP_MTORn)                      | 82   |

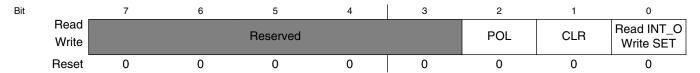

|            | 5.4.14  | Slave port output interrupt control register (SLAVE_SP_OIC)                | 83   |

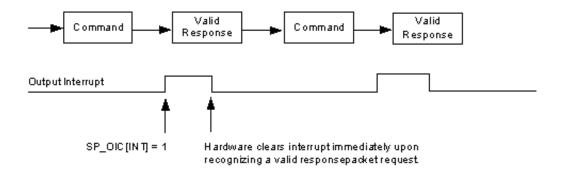

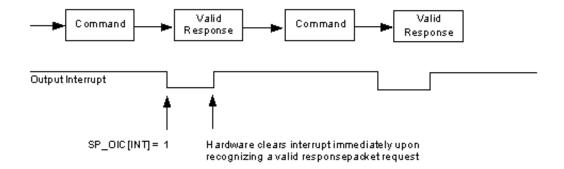

|            | 5.4.15  | Output interrupt details                                                   | 84   |

| 5.5        | I2C ser | ial protocol and timing                                                    | 86   |

|            | 5.5.1   | Baud rates                                                                 | 86   |

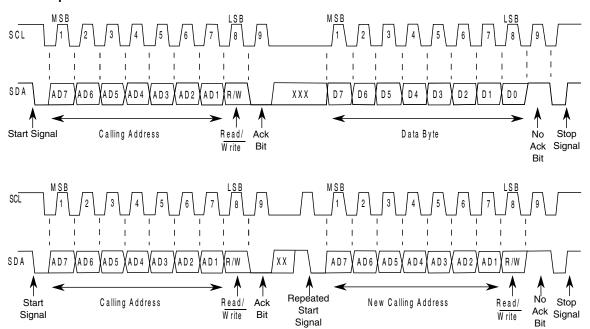

|            | 5.5.2   | I2C serial-addressing.                                                     | 86   |

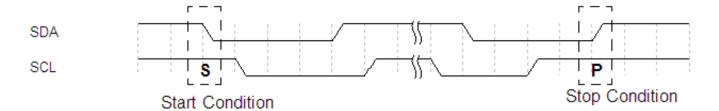

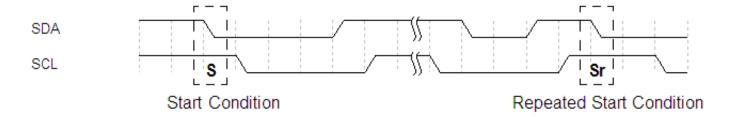

|            | 5.5.3   | I2C START, STOP and REPEATED START conditions                              | 87   |

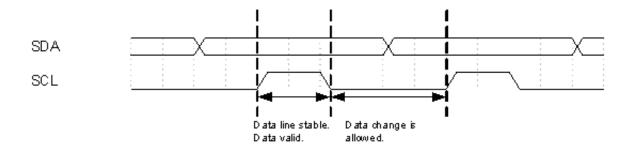

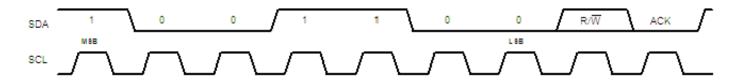

| 5.3<br>5.4 | 5.5.4   | I2C bit transfer                                                           | 88   |

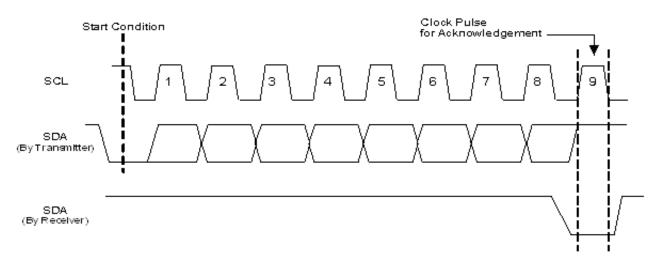

|            | 5.5.5   | I2C acknowledge                                                            | 88   |

|            | 5.5.6   | I2C slave address                                                          | 89   |

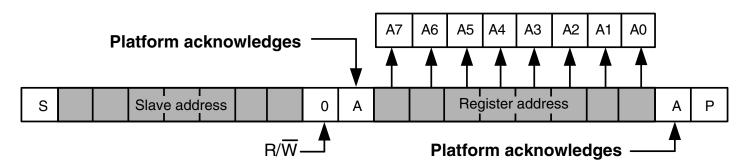

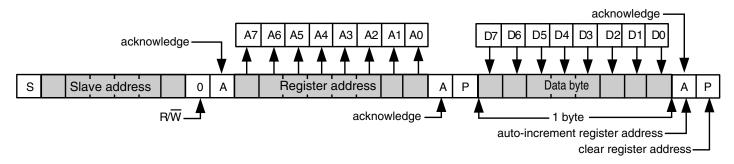

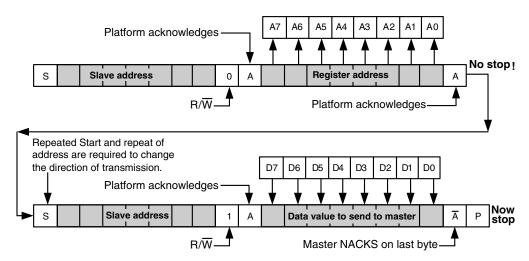

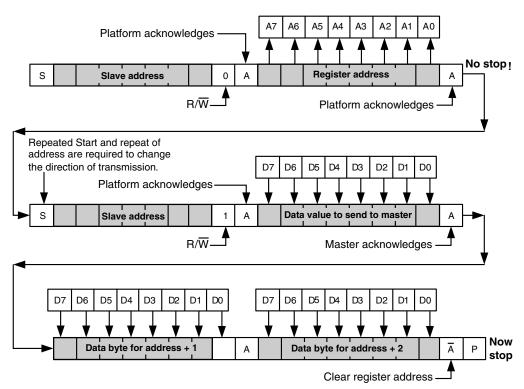

|            | 5.5.7   | I2C message format for writing                                             | 89   |

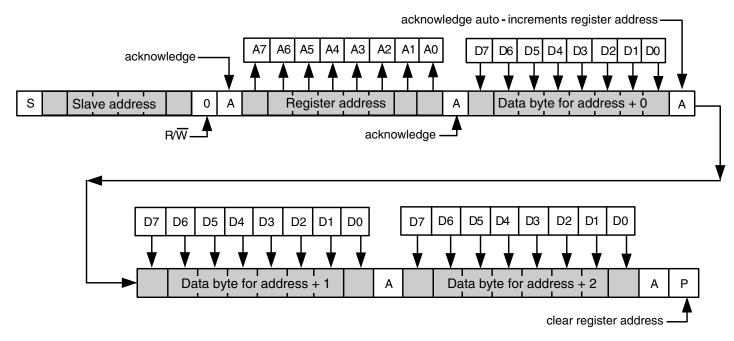

|            | 5.5.8   | I2C message format for reading.                                            | 91   |

| Sec | tion n        | umber Title                                             | Page |

|-----|---------------|---------------------------------------------------------|------|

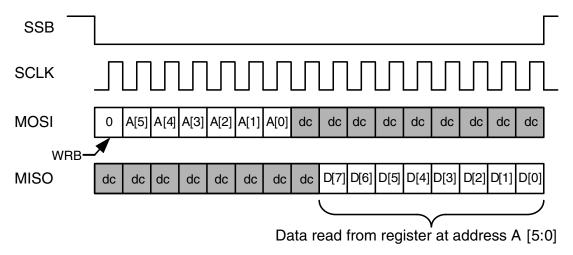

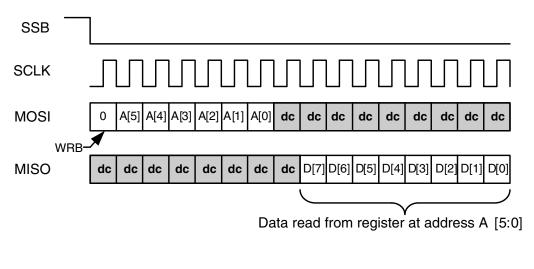

| 5.6 | SPI ser       | rial protocol and timing                                | 93   |

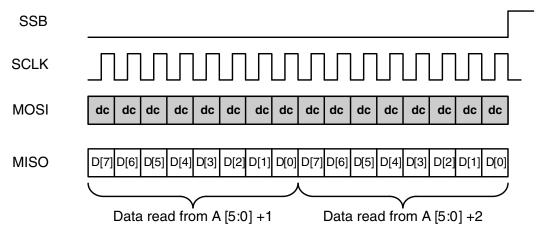

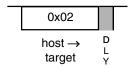

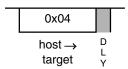

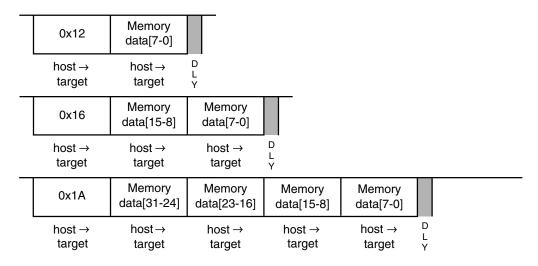

|     | 5.6.1         | SPI read operation.                                     | 93   |

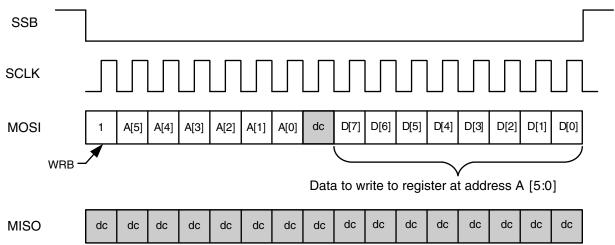

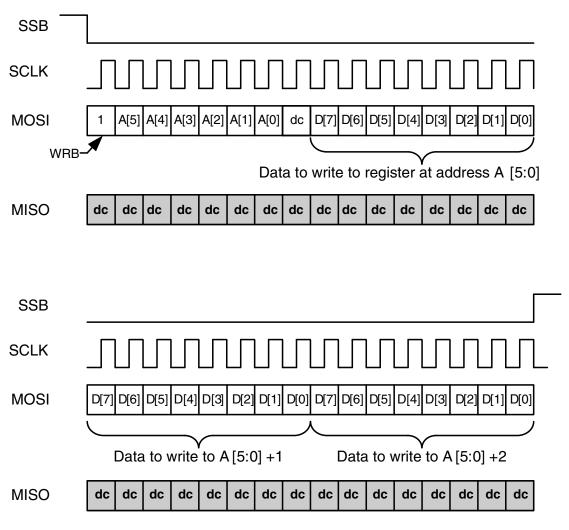

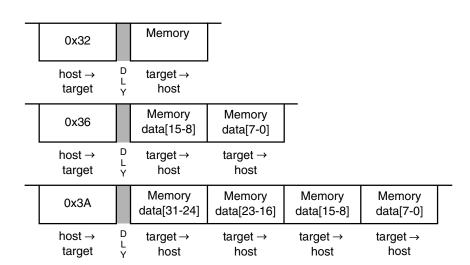

|     | 5.6.2         | SPI write operation                                     | 95   |

| 5.7 | Slave         | port module interrupts                                  | 97   |

|     | 5.7.1         | Mailbox interrupt                                       | 98   |

|     | 5.7.2         | Semaphore interrupts                                    | 98   |

| 5.8 | Reset         | operation                                               | 99   |

|     |               | Chapter 6 Inter-Integrated Circuit (I2C)                |      |

| 6.1 | Chip-s        | pecific details about Master I2C                        | 101  |

|     | 6.1.1         | SCL divider corrections                                 | 101  |

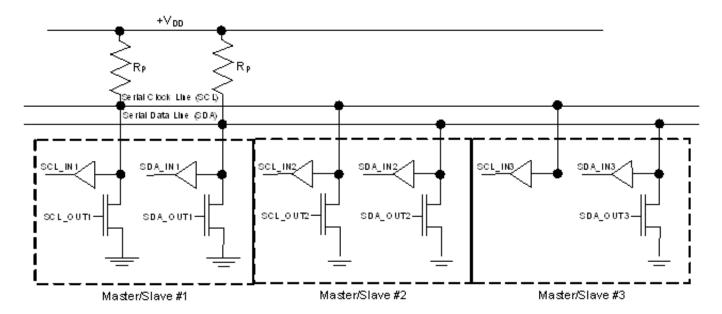

| 6.2 | Introduction. |                                                         |      |

|     | 6.2.1         | Features                                                | 102  |

|     | 6.2.2         | Modes of operation                                      | 103  |

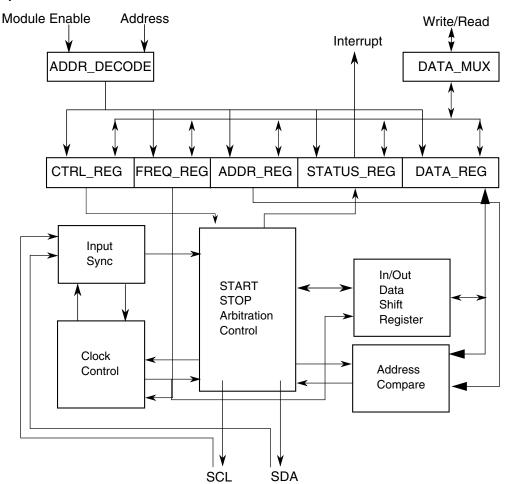

|     | 6.2.3         | Block diagram                                           | 103  |

| 6.3 | I2C sig       | gnal descriptions                                       | 104  |

| 6.4 | Memo          | ry map and register descriptions                        | 104  |

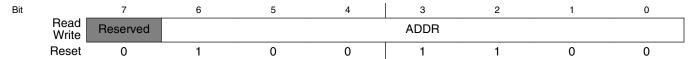

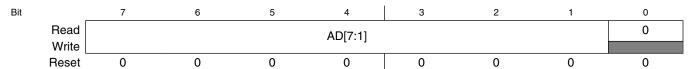

|     | 6.4.1         | I2C Address Register 1 (I2C_A1)                         | 105  |

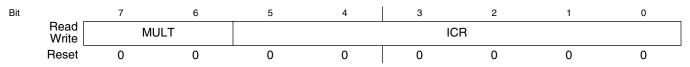

|     | 6.4.2         | I2C Frequency Divider register (I2C_F)                  | 105  |

|     | 6.4.3         | I2C Control Register 1 (I2C_C1)                         | 106  |

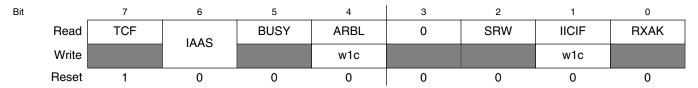

|     | 6.4.4         | I2C Status register (I2C_S)                             | 108  |

|     | 6.4.5         | I2C Data I/O register (I2C_D)                           | 109  |

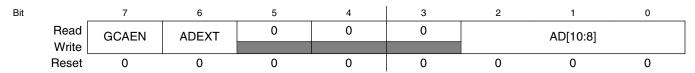

|     | 6.4.6         | I2C Control Register 2 (I2C_C2)                         | 110  |

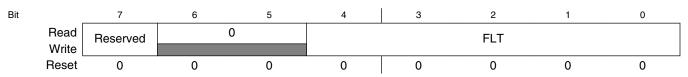

|     | 6.4.7         | I2C Programmable Input Glitch Filter register (I2C_FLT) | 110  |

| 6.5 | Function      | onal description                                        | 111  |

|     | 6.5.1         | I2C protocol                                            | 111  |

|     |               | 6.5.1.1 START signal                                    | 112  |

|     |               | 6.5.1.2 Slave address transmission                      | 112  |

|     |               | 6.5.1.3 Data transfers                                  | 113  |

| Sec | tion n   | umber         | Title                                               | Page |

|-----|----------|---------------|-----------------------------------------------------|------|

|     |          | 6.5.1.4       | STOP signal                                         | 113  |

|     |          | 6.5.1.5       | Repeated START signal                               | 113  |

|     |          | 6.5.1.6       | Arbitration procedure                               | 114  |

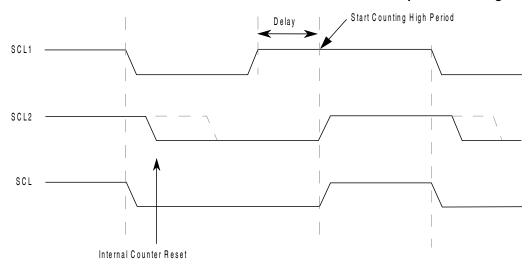

|     |          | 6.5.1.7       | Clock synchronization                               | 114  |

|     |          | 6.5.1.8       | Handshaking                                         | 115  |

|     |          | 6.5.1.9       | Clock stretching.                                   | 115  |

|     |          | 6.5.1.10      | I2C divider and hold values                         | 115  |

|     | 6.5.2    | 10-bit add    | dress                                               | 116  |

|     |          | 6.5.2.1       | Master-transmitter addresses a slave-receiver       | 117  |

|     |          | 6.5.2.2       | Master-receiver addresses a slave-transmitter       | 117  |

|     | 6.5.3    | Address r     | matching                                            | 118  |

|     | 6.5.4    | Resets        |                                                     | 118  |

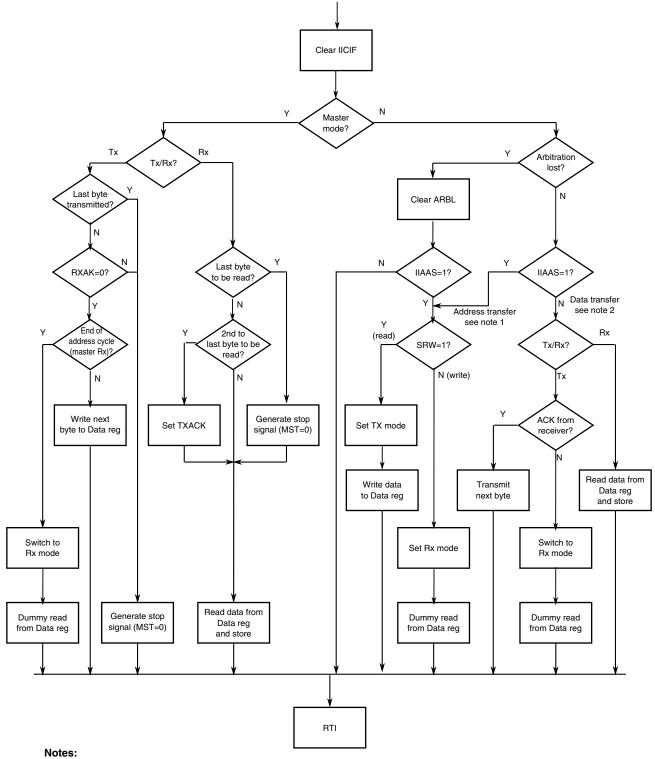

|     | 6.5.5    | Interrupts    | S                                                   | 118  |

|     |          | 6.5.5.1       | Byte transfer interrupt                             | 119  |

|     |          | 6.5.5.2       | Address detect interrupt                            | 119  |

|     |          | 6.5.5.3       | Exit from low-power/stop modes                      | 119  |

|     |          | 6.5.5.4       | Arbitration lost interrupt                          | 119  |

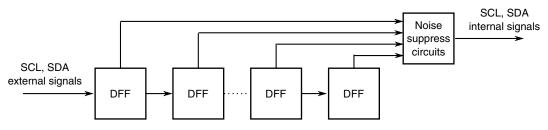

|     | 6.5.6    | Programn      | mable input glitch filter                           | 120  |

|     | 6.5.7    | Address r     | matching wakeup                                     | 121  |

| 6.6 | Initiali | zation/appli  | cation information                                  | 121  |

|     |          |               | Chapter 7 Queued Serial Peripheral Interface (QSPI) |      |

| 7.1 | Chip-s   | pecific infor | rmation about QSPI                                  | 125  |

|     | 7.1.1    | Maximun       | m master mode frequency                             | 125  |

|     | 7.1.2    | Signal na     | imes.                                               | 125  |

| 7.2 | Introdu  | ection        |                                                     | 126  |

|     | 7.2.1    | Overview      | V                                                   | 126  |

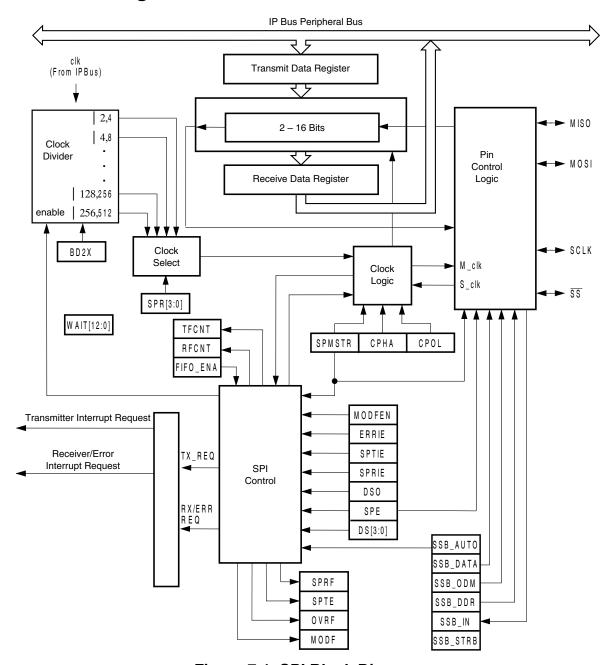

|     | 7.2.2    | Block Dia     | agram                                               | 127  |

| Sec | Section number          |                         | Title                                       | Page |

|-----|-------------------------|-------------------------|---------------------------------------------|------|

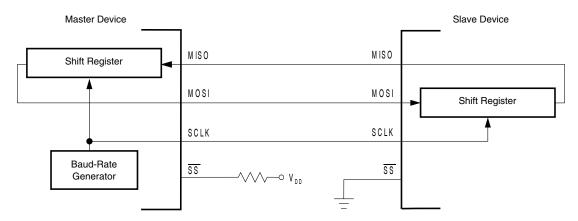

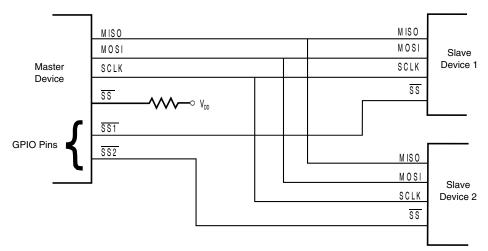

| 7.3 | Signal                  | Description             | ns                                          | 128  |

|     | 7.3.1                   | External                | I/O Signals                                 | 128  |

|     |                         | 7.3.1.1                 | MISO (Master In/Slave Out)                  | 128  |

|     |                         | 7.3.1.2                 | MOSI (Master Out/Slave In)                  | 128  |

|     |                         | 7.3.1.3                 | SCLK (Serial Clock)                         | 128  |

|     |                         | 7.3.1.4                 | SS (Slave Select)                           | 129  |

| 7.4 | Memor                   | ry Map Reg              | gisters                                     | 130  |

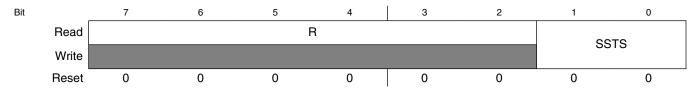

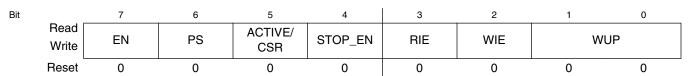

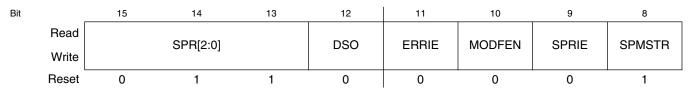

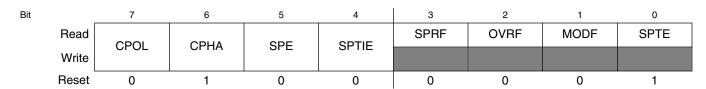

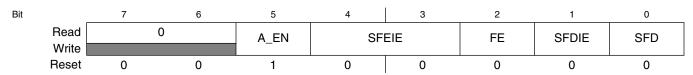

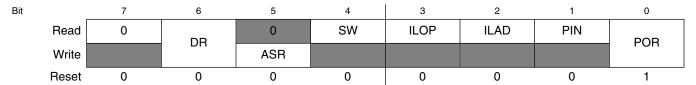

|     | 7.4.1                   | SPI Stati               | us and Control Register (QSPI_SPSCR)        | 130  |

|     | 7.4.2                   | SPI Data                | a Size and Control Register (QSPI_SPDSR)    | 133  |

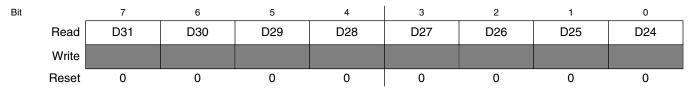

|     | 7.4.3                   | SPI Data                | a Receive Register (QSPI_SPDRR)             | 136  |

|     | 7.4.4                   | SPI Data                | a Transmit Register (QSPI_SPDTR)            | 137  |

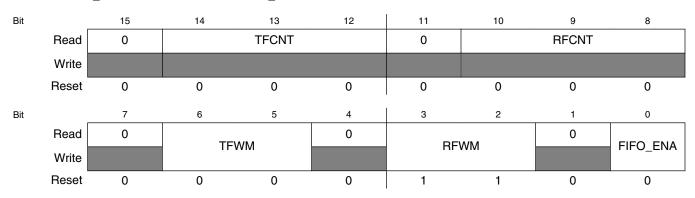

|     | 7.4.5                   | SPI FIFO                | O Control Register (QSPI_SPFIFO)            | 139  |

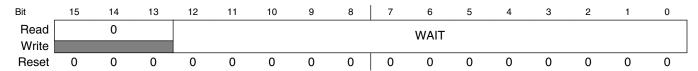

|     | 7.4.6                   | SPI Wor                 | rd Delay Register (QSPI_SPWAIT)             | 141  |

| 7.5 | Functional Description. |                         |                                             | 141  |

|     | 7.5.1                   | Operatin                | ng Modes                                    | 141  |

|     |                         | 7.5.1.1                 | Master Mode                                 | 141  |

|     |                         | 7.5.1.2                 | Slave Mode                                  | 142  |

|     |                         | 7.5.1.3                 | Wired-OR Mode                               | 143  |

|     | 7.5.2                   | Transact                | tion Formats                                | 144  |

|     |                         | 7.5.2.1                 | Data Transaction Length                     | 144  |

|     |                         | 7.5.2.2                 | Data Shift Ordering                         | 144  |

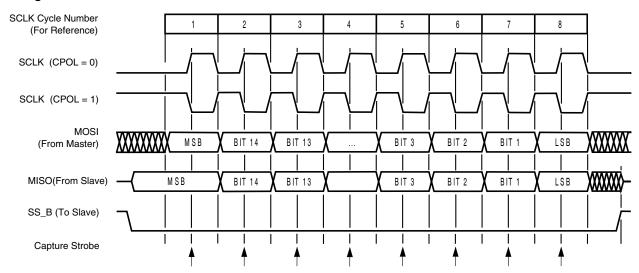

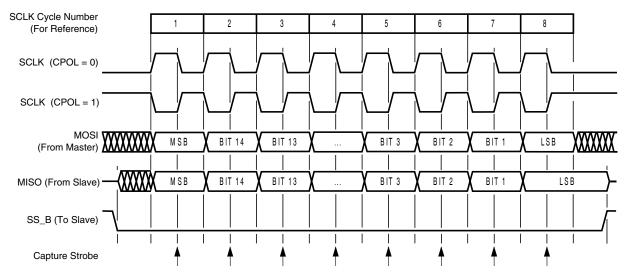

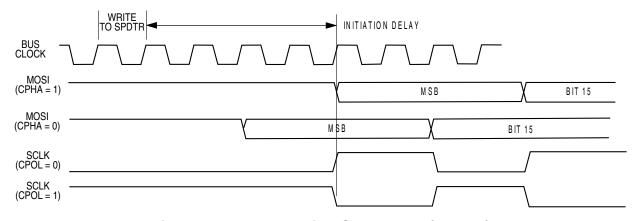

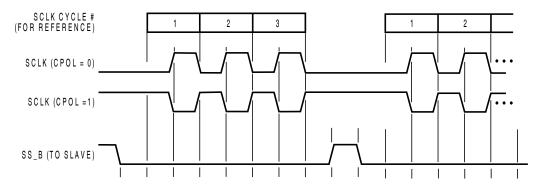

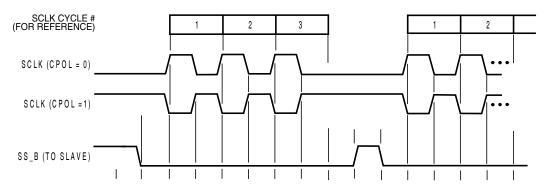

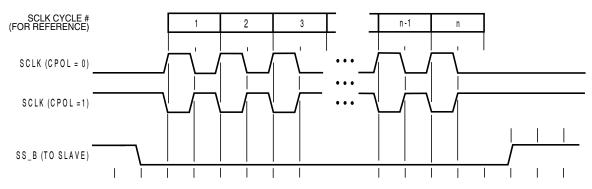

|     |                         | 7.5.2.3                 | Clock Phase and Polarity Controls           | 145  |

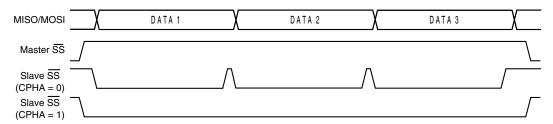

|     |                         | 7.5.2.4                 | Transaction Format When CPHA = 0            | 145  |

|     |                         | 7.5.2.5                 | Transaction Format When CPHA = 1            | 147  |

|     |                         | 7.5.2.6                 | Transaction Initiation Latency              | 148  |

|     |                         | 7.5.2.7                 | SS Hardware-Generated Timing in Master Mode | 148  |

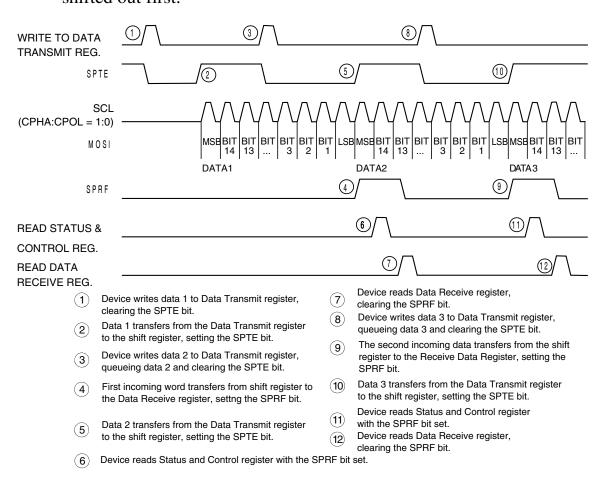

|     | 7.5.3                   | 7.5.3 Transmission Data |                                             | 150  |

|     | 7.5.4                   | Error Co                | onditions                                   | 151  |

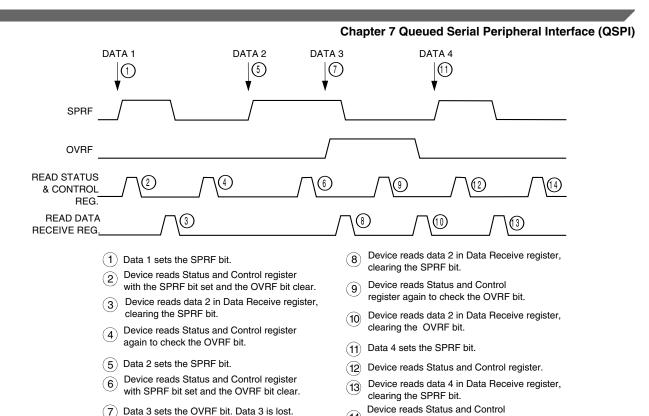

|     |                         | 7.5.4.1                 | Overflow Error                              | 151  |

|     |                         |                         |                                             |      |

| Section number |         |               | Title           | Page                                                |     |

|----------------|---------|---------------|-----------------|-----------------------------------------------------|-----|

|                |         | 7.5.4.2       | Mode Faul       | t Error                                             | 153 |

|                |         |               | 7.5.4.2.1       | Master Mode Fault                                   | 154 |

|                |         |               | 7.5.4.2.2       | Slave Mode Fault                                    | 154 |

|                | 7.5.5   | Resetting     | g the SPI       |                                                     | 155 |

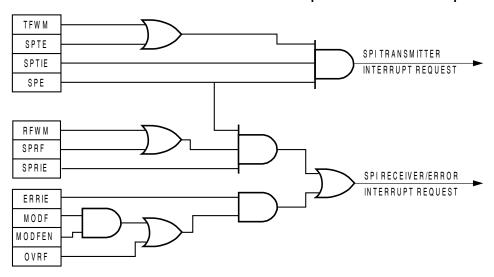

| 7.6            | Interru | pts           |                 |                                                     | 156 |

|                |         | Оре           | erational       | Chapter 8 Phases and Modes of Operation (OP_PHASES) |     |

| 8.1            | Introdu | ction         |                 |                                                     | 159 |

|                | 8.1.1   | Definitio     | ons             |                                                     | 159 |

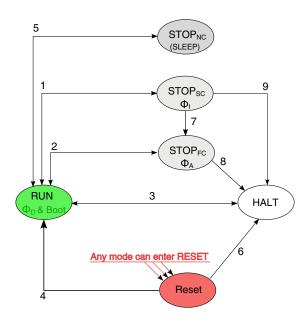

|                | 8.1.2   | Modes of      | f operation     |                                                     | 160 |

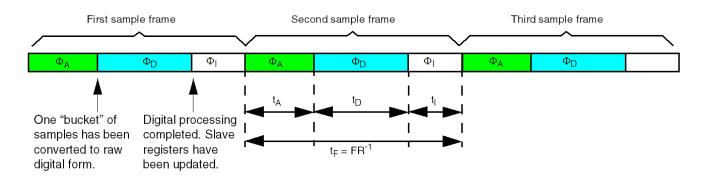

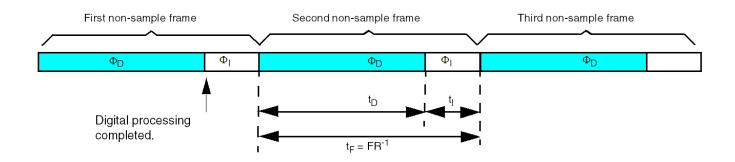

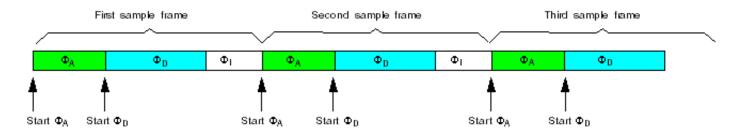

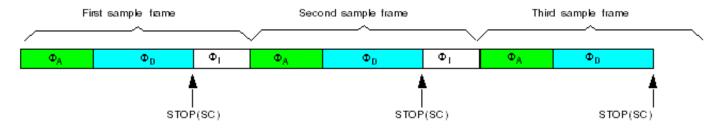

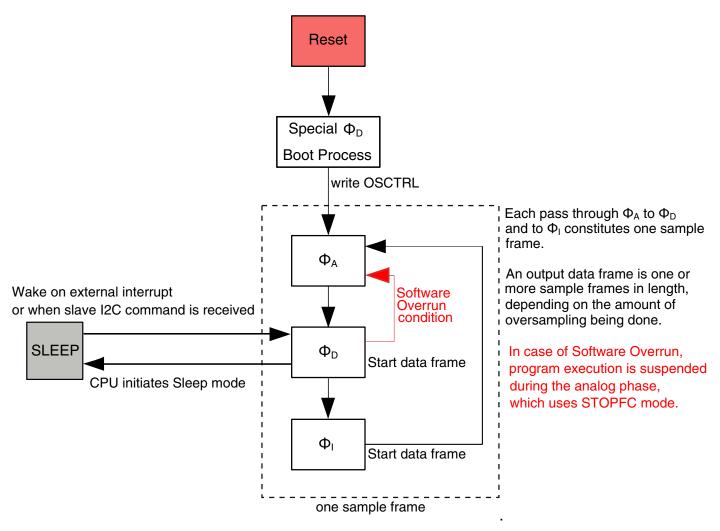

| 8.2            | Frame-  | based samp    | pling           |                                                     | 161 |

|                | 8.2.1   | Overview      | <i>w</i>        |                                                     | 161 |

|                | 8.2.2   | Phase tri     | ggers           |                                                     | 162 |

| 8.3            | Clock   | operation as  | s a function o  | f mode/phase                                        | 164 |

| 8.4            | Power   | control mo    | des of operati  | ion                                                 | 165 |

|                |         |               |                 | Chapter 9 System Integration Module (SIM)           |     |

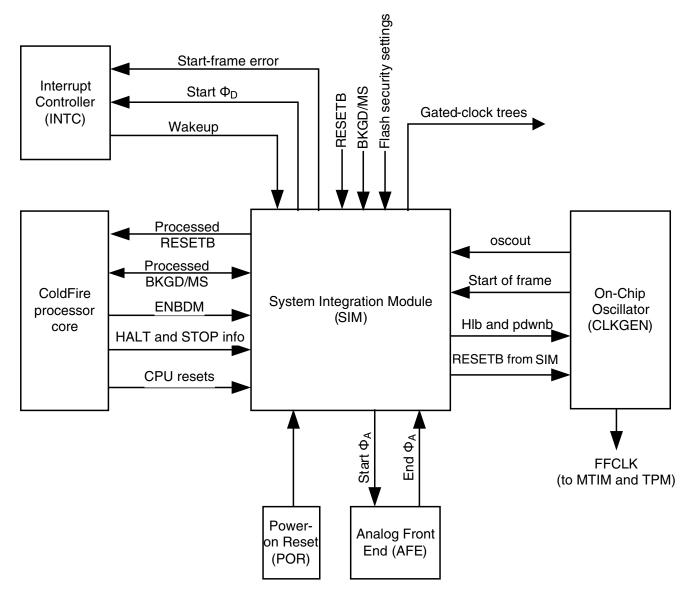

| 9.1            | System  | Integration   | n Module (SI    | M) overview                                         | 167 |

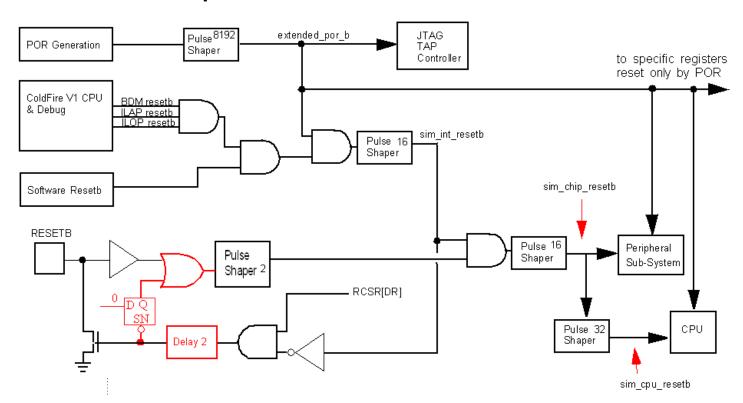

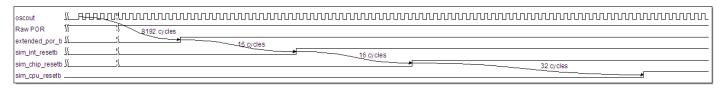

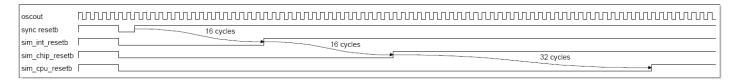

| 9.2            | Reset g | generation    |                 |                                                     | 168 |

|                | 9.2.1   | Reset sou     | urces           |                                                     | 168 |

|                | 9.2.2   | Reset out     | tputs           |                                                     | 169 |

| 9.3            | Operati | ing mode co   | ontrol          |                                                     | 171 |

|                | 9.3.1   | STOP me       | ode control a   | nd operation                                        | 171 |

|                | 9.3.2   | DEBUG         | mode contro     | 1                                                   | 172 |

| 9.4            | Oscilla | tor control.  |                 |                                                     | 173 |

|                | 9.4.1   | General       |                 |                                                     | 173 |

|                | 9.4.2   | CPU           |                 |                                                     | 173 |

| 9.5            | Clock g | gating        |                 |                                                     | 174 |

| 9.6            | Registe | er settings f | for I2C slave 1 | port                                                | 175 |

| Sec  | Section number Title |                                                                  | Page |  |

|------|----------------------|------------------------------------------------------------------|------|--|

| 9.7  | SIM m                | emory map/register definitions                                   | 175  |  |

|      | 9.7.1                | STOP Control and Status Register (SIM_STOPCR)                    | 176  |  |

|      | 9.7.2                | Frame Control and Status Register (SIM_FCSR)                     | 177  |  |

|      | 9.7.3                | Reset Status and Control Register (SIM_RSCR)                     | 178  |  |

|      | 9.7.4                | Peripheral Clock Enable Register 0 for STOPFC mode (SIM_PCESFC0) | 180  |  |

|      | 9.7.5                | Peripheral Clock Enable Register 1 for STOPFC mode (SIM_PCESFC1) | 181  |  |

|      | 9.7.6                | Peripheral Clock Enable Register 0 for STOPSC mode (SIM_PCESSC0) | 182  |  |

|      | 9.7.7                | Peripheral Clock Enable Register 1 for STOPSC mode (SIM_PCESSC1) | 183  |  |

|      | 9.7.8                | Peripheral Clock Enable Register 0 for RUN mode (SIM_PCERUN0)    | 184  |  |

|      | 9.7.9                | Peripheral Clock Enable Register 1 for RUN mode (SIM_PCERUN1)    | 185  |  |

|      | 9.7.10               | Pin Mux Control Register0 (SIM_PMCR0)                            | 186  |  |

|      | 9.7.11               | Pin Mux Control Register1 (SIM_PMCR1)                            | 187  |  |

|      | 9.7.12               | Pin Mux Control Register2 (SIM_PMCR2)                            | 188  |  |

|      |                      | Chapter 10 Analog Front End (AFE)                                |      |  |

| 10.1 | Analog               | Front End Module Overview                                        | 189  |  |

| 10.2 | AFE fe               | eatures                                                          | 189  |  |

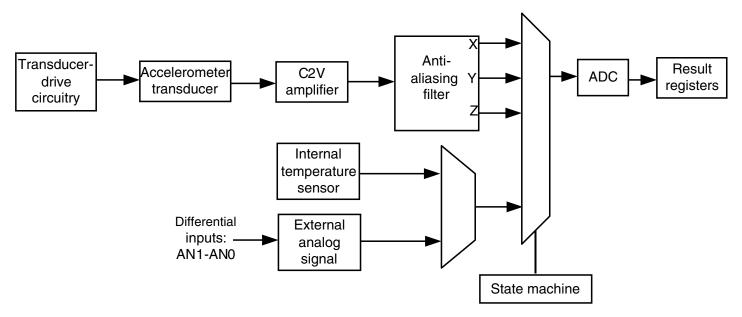

| 10.3 | AFE ar               | chitecture and theory of operation                               | 190  |  |

|      | 10.3.1               | ADC operation                                                    | 190  |  |

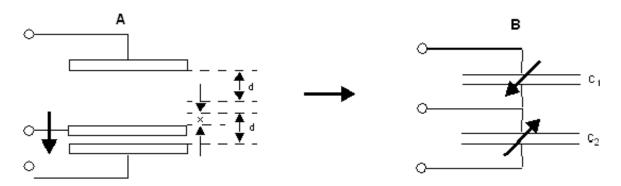

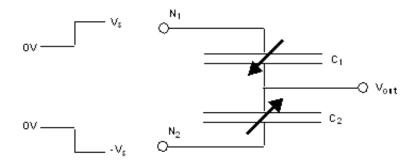

|      | 10.3.2               | Accelerometer principle of operation                             | 191  |  |

| 10.4 | AFE m                | nemory map and register descriptions                             | 195  |  |

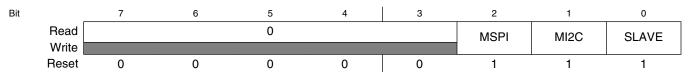

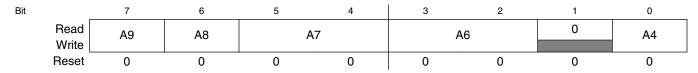

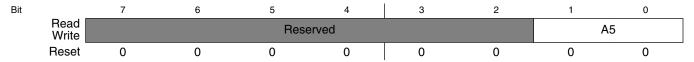

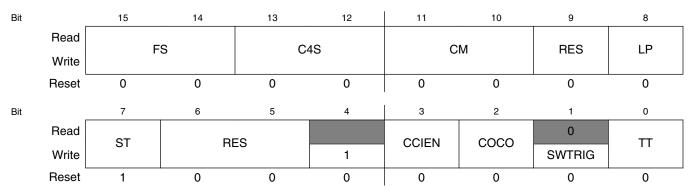

|      | 10.4.1               | AFE Control and Status Register (AFE_CSR)                        | 195  |  |

| 10.5 | Interru              | pts                                                              | 197  |  |

| 10.6 | AFE R                | eset                                                             | 198  |  |

|      |                      | Chapter 11 On-Chip Oscillator (CLKGEN)                           |      |  |

| 11.1 | Introdu              | action                                                           | 199  |  |

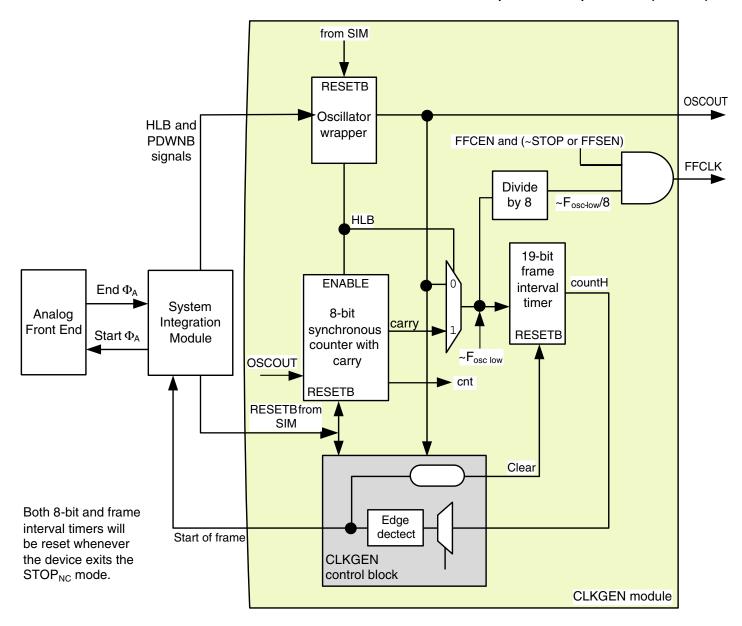

| 11.2 | High-le              | evel overview                                                    | 200  |  |

| 11.3 | CLKG                 | EN register offsets                                              | 202  |  |

| Sect  | tion number Title                                     | Page   |

|-------|-------------------------------------------------------|--------|

| 11.4  | CLKGEN memory map and register descriptions           | 203    |

|       | 11.4.1 Oscillator Control Register (CLKGEN_CK_OSCTRL) | 203    |

| 11.5  | Interrupts                                            | 205    |

|       | Chapter 12<br>Flash Memory Controller (I              | FLASH) |

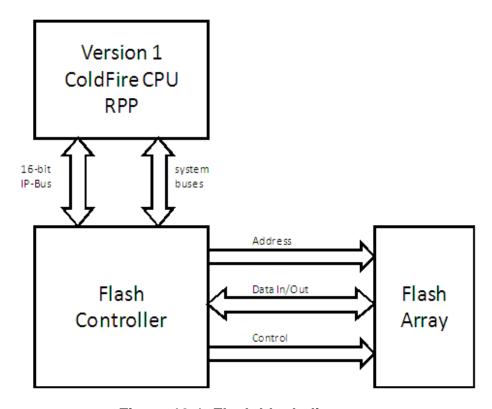

| 12.1  | Flash memory overview                                 | 207    |

| 12.2  | Features.                                             |        |

| 12.3  | Theory of operation                                   | 208    |

| 12.4  | Flash controller modes of operation                   | 209    |

| 12.5  | Memory maps                                           | 210    |

|       | 12.5.1 Flash controller array memory map              | 210    |

| 12.6  | FLASH registers and control bits                      | 210    |

| 12.7  | FLASH memory map and register descriptions            | 211    |

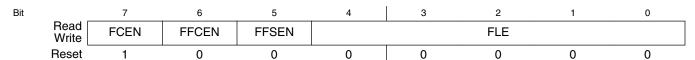

|       | 12.7.1 Flash Options Register (FLASH_FOPT)            | 211    |

| 12.8  | Initialization information                            | 214    |

|       | 12.8.1 Factory                                        | 214    |

|       | 12.8.2 End user                                       | 214    |

| 12.9  | Programming model                                     | 214    |

| 12.10 | Security                                              | 215    |

|       | Chapter 13<br>Port Controls (PC)                      |        |

| 13.1  | FXLC95000CL port control customizations.              | 217    |

|       | 13.1.1 General rules                                  | 218    |

|       | 13.1.2 Exceptions to the general rules                | 218    |

|       | 13.1.3 Pins not covered by the port control modules   | 218    |

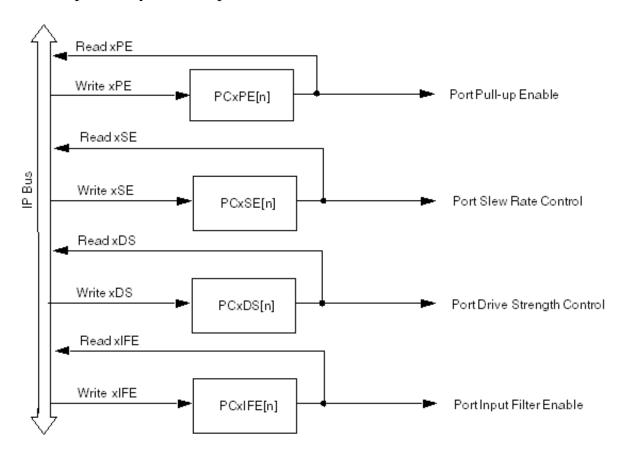

| 13.2  | Standard pin controls.                                | 218    |

|       | 13.2.1 Pin controls                                   | 218    |

|       | 13.2.2 Pin controls programming model                 | 219    |

| Sec  | tion nu   | umber Title                                                   | Page |  |

|------|-----------|---------------------------------------------------------------|------|--|

| 13.3 | PC mer    | mory map/register definition                                  | 220  |  |

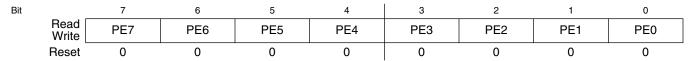

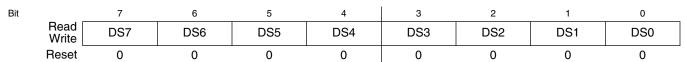

|      | 13.3.1    | Port x Pull-Up Enable Register (PCx_PE)                       | 220  |  |

|      | 13.3.2    | Port x Slew Rate Enable Register (PCx_SE)                     | 222  |  |

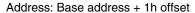

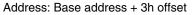

|      | 13.3.3    | Port x Drive Strength Selection Register (PCx_DS)             | 223  |  |

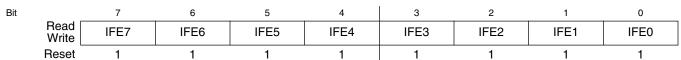

|      | 13.3.4    | Port x Input Filter Enable Register (PCx_IFE)                 | 224  |  |

|      |           | Chapter 14 Rapid General Purpose Input/Output Module (RGPIO)  |      |  |

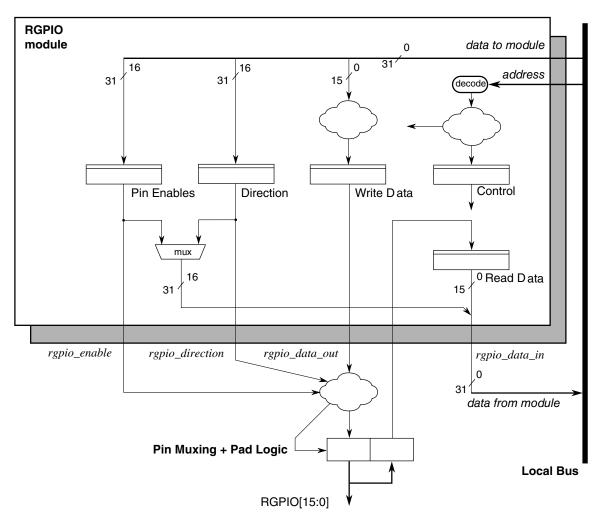

| 14.1 | Introdu   | ction                                                         | 227  |  |

|      | 14.1.1    | Overview                                                      | 227  |  |

|      | 14.1.2    | Features                                                      | 229  |  |

|      | 14.1.3    | Modes of Operation                                            | 229  |  |

| 14.2 | Externa   | al Signal Description                                         | 230  |  |

|      | 14.2.1    | Overview                                                      | 230  |  |

|      | 14.2.2    | Detailed Signal Descriptions.                                 | 230  |  |

| 14.3 | Memor     | y Map and Registers                                           | 231  |  |

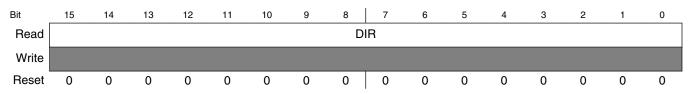

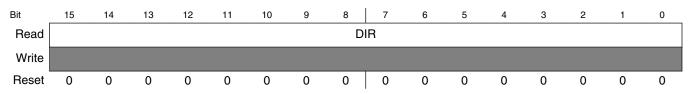

|      | 14.3.1    | RGPIO Data Direction Register (RGPIO_DIR)                     | 231  |  |

|      | 14.3.2    | RGPIO Data Register (RGPIO_DATA)                              | 232  |  |

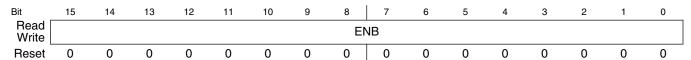

|      | 14.3.3    | RGPIO Pin Enable Register (RGPIO_ENB)                         | 233  |  |

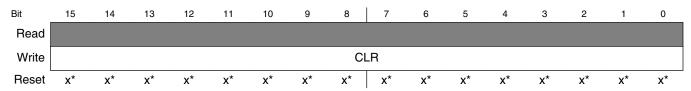

|      | 14.3.4    | RGPIO Clear Data Register (RGPIO_CLR)                         | 234  |  |

|      | 14.3.5    | RGPIO Data Direction Register (RGPIO_DIR)                     | 234  |  |

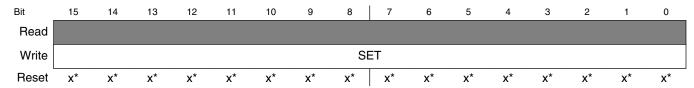

|      | 14.3.6    | RGPIO Set Data Register (RGPIO_SET)                           | 235  |  |

|      | 14.3.7    | RGPIO Data Direction Register (RGPIO_DIR)                     | 235  |  |

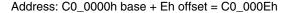

|      | 14.3.8    | RGPIO Toggle Data Register (RGPIO_TOG)                        | 236  |  |

| 14.4 | Functio   | nal Description                                               | 236  |  |

| 14.5 | Initializ | zation Information                                            | 237  |  |

| 14.6 | Applica   | ation Information                                             | 237  |  |

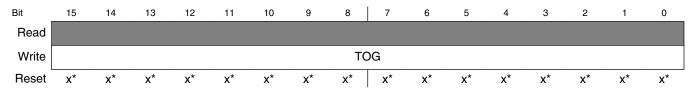

|      | 14.6.1    | Application 1: Simple Square-Wave Generation                  | 237  |  |

|      | 14.6.2    | Application 2: 16-bit Message Transmission using SPI Protocol | 238  |  |

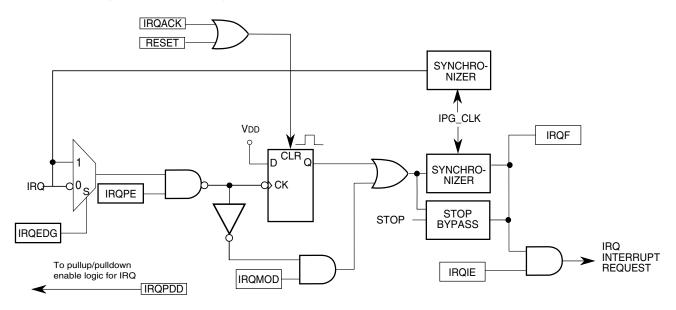

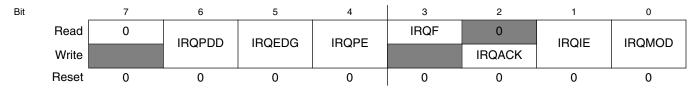

#### **Title** Section number Page Chapter 15 Pin Interrupt Function (IRQ) 15.1 15.1.1 Programming IRQ pin functionality 241 15.1.2 Introduction 241 15.2.1 Features 241 15.2.2 15.2.3 15.3 15.5 15.5.1 15.5.2 IRQ Edge Select. 245 15.5.3 15.5.4 15.5.5 15.5.6 Exit from Low-Power Modes 246 Stop modes 246 15.5.6.1 15.6 Resets. 247 15.7 Chapter 16 Read Only Memory (ROM) 16.1 Introduction 249 16.2 16.2.1 16.2.2

| Sec  | Section number |                                        | Title                                                  | Page |  |

|------|----------------|----------------------------------------|--------------------------------------------------------|------|--|

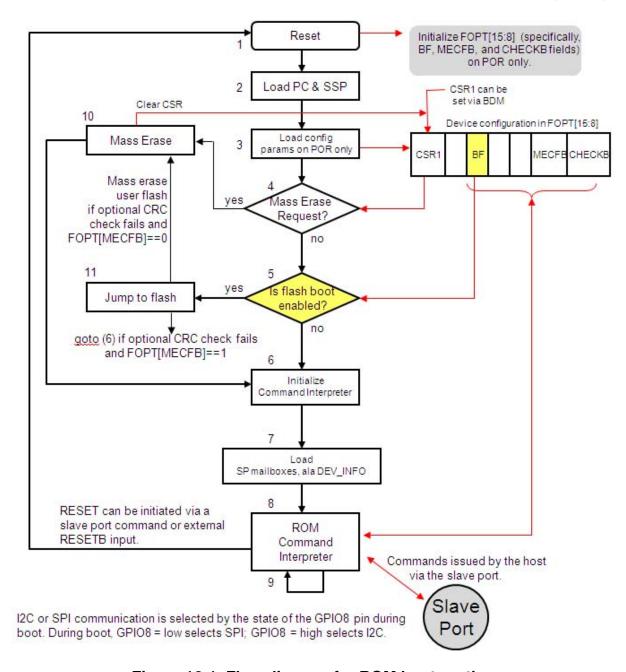

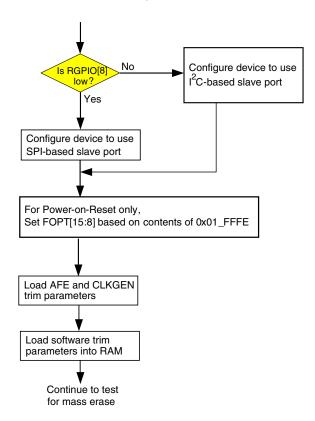

|      | 16.2.3         | Boot Step                              | p 3: Load configuration parameters                     | 252  |  |

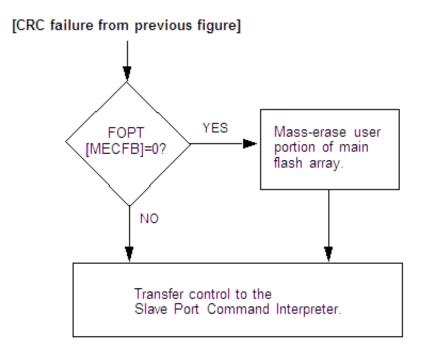

|      | 16.2.4         | Boot Step                              | p 4: Mass erase request                                | 252  |  |

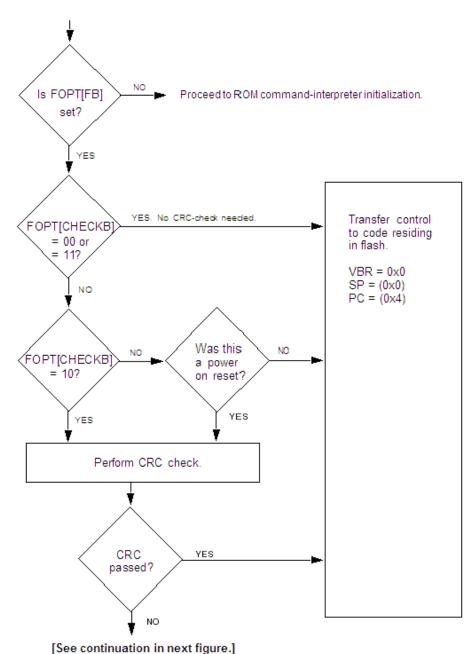

|      | 16.2.5         | Boot Step                              | ps 5 and 11: For flash boots, jump to flash            | 253  |  |

|      | 16.2.6         | Boot Step                              | p 6: Initialize command interpreter                    | 255  |  |

|      | 16.2.7         | Boot Step                              | 9 8: Launch ROM command interpreter                    | 256  |  |

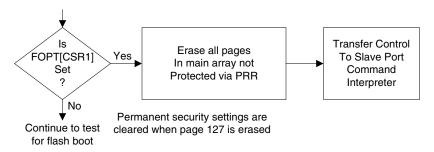

| 16.3 | Security       | /                                      |                                                        | 256  |  |

|      | 16.3.1         | Access an                              | nd security rules of thumb                             | 256  |  |

|      | 16.3.2         | Security                               |                                                        | 257  |  |

| 16.4 | Rights         | nanagemer                              | nt                                                     | 257  |  |

|      | 16.4.1         | Memory-                                | -map restrictions.                                     | 257  |  |

|      | 16.4.2         | Rights-m                               | anagement variables                                    | 258  |  |

|      |                | 16.4.2.1                               | Device ID (DID)                                        | 258  |  |

|      |                | 16.4.2.2                               | Page-Release Register (PRR)                            | 258  |  |

|      |                | 16.4.2.3                               | Hardware restrictions.                                 | 259  |  |

| 16.5 | ROM C          | Command I                              | nterpreter (CI)                                        | 259  |  |

|      | 16.5.1         | 1 Callable utilities.                  |                                                        |      |  |

|      | 16.5.2         | Packet transfers and commands overview |                                                        |      |  |

|      | 16.5.3         | Common                                 | 261                                                    |      |  |

|      | 16.5.4         | CI_DEV_                                | _INFO                                                  | 262  |  |

|      |                | 16.5.4.1                               | CI_DEV_INFO command packet format                      | 262  |  |

|      |                | 16.5.4.2                               | CI_DEV_INFO response packet format.                    | 262  |  |

|      |                | 16.5.4.3                               | CI_DEV_INFO access/security policies                   | 263  |  |

|      | 16.5.5         | CI_REAI                                | D_WRITE                                                | 264  |  |

|      |                | 16.5.5.1                               | CI_READ_WRITE description                              | 264  |  |

|      |                | 16.5.5.2                               | CI_READ_WRITE memory command packet format             | 264  |  |

|      |                | 16.5.5.3                               | CI_READ_WRITE read/write memory response packet format | 266  |  |

|      |                | 16.5.5.4                               | CI_READ_WRITE access/security policies                 | 267  |  |

|      |                | 16.5.5.5                               | CI_READ_WRITE read/write memory example                | 268  |  |

| Section number |        | ımber       | Title                                                              | Page |

|----------------|--------|-------------|--------------------------------------------------------------------|------|

|                | 16.5.6 | CI_ERAS     | SE                                                                 | 269  |

|                |        | 16.5.6.1    | CI_ERASE erase flash function description                          | 269  |

|                |        | 16.5.6.2    | CI_ERASE erase command packet format                               | 269  |

|                |        | 16.5.6.3    | CI_ERASE erase command response packet format                      | 270  |

|                |        | 16.5.6.4    | CI_ERASE access/security policies                                  | 271  |

|                |        | 16.5.6.5    | CI_ERASE example                                                   | 272  |

|                | 16.5.7 | CI_CRC.     |                                                                    | 273  |

|                |        | 16.5.7.1    | CI_CRC checksum command packet format                              | 273  |

|                |        | 16.5.7.2    | CI_CRC response packet format                                      | 274  |

|                |        | 16.5.7.3    | CI_CRC access/security policies                                    | 275  |

|                |        | 16.5.7.4    | CI_CRC example                                                     | 275  |

|                | 16.5.8 | CI_RESE     | ET                                                                 | 276  |

|                |        | 16.5.8.1    | CI_RESET command packet format                                     | 277  |

|                |        | 16.5.8.2    | CI_RESET response packet format                                    | 277  |

|                |        | 16.5.8.3    | CI_RESET access/security policies                                  | 278  |

|                | 16.5.9 | CI_PRO      | TECT and CI_UNPROTECT                                              | 278  |

|                |        | 16.5.9.1    | CI_PROTECT command packet format                                   | 279  |

|                |        | 16.5.9.2    | CI_UNPROTECT command packet format                                 | 279  |

|                |        | 16.5.9.3    | CI_PROTECT and CI_UNPROTECT response packets format                | 279  |

|                |        | 16.5.9.4    | CI_PROTECT and CI_UNPROTECT access/security policies               | 279  |

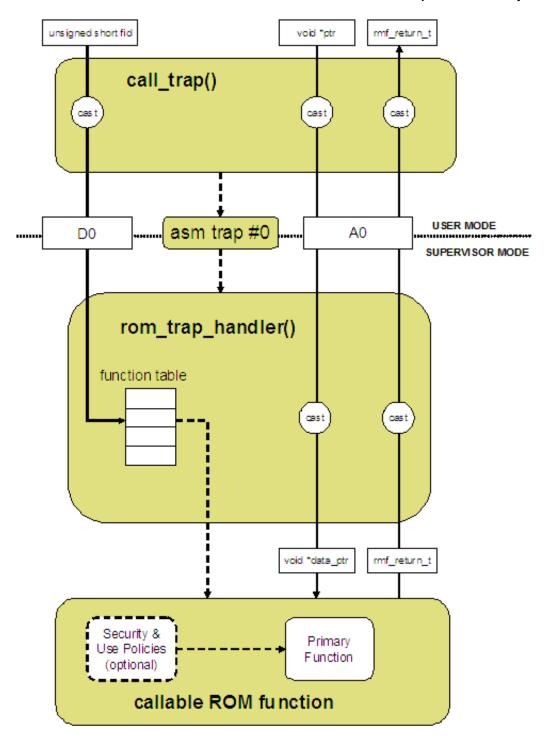

| 16.6           | User-C | allable ROI | M functions                                                        | 280  |

|                | 16.6.1 | RMF_DE      | EV_INFO                                                            | 284  |

|                |        | 16.6.1.1    | RMF_DEV_INFO description                                           | 284  |

|                |        | 16.6.1.2    | RMF_DEV_INFO input structure syntax                                | 284  |

|                |        | 16.6.1.3    | RMF_DEV_INFO output structure syntax                               | 284  |

|                |        | 16.6.1.4    | RMF_DEV_INFO error codes                                           | 285  |

|                |        | 16.6.1.5    | RMF_DEV_INFO operation                                             | 285  |

|                |        | 16.6.1.6    | RMF_DEV_INFO access/security policies                              | 285  |

|                |        | 16.6.1.7    | RMF_DEV_INFO example                                               | 285  |

|                |        | Xtrinsic    | FXLC95000CL Intelligent Motion-Sensing Platform, Rev. 0.6, May 201 | 3    |

| Section number |          | Title                                                              |     |

|----------------|----------|--------------------------------------------------------------------|-----|

| 16.6.2         | RMF_FL   | ASH_PROGRAM                                                        | 286 |

|                | 16.6.2.1 | RMF_FLASH_PROGRAM description                                      | 286 |

|                | 16.6.2.2 | RMF_FLASH_PROGRAM input structure syntax                           | 286 |

|                | 16.6.2.3 | RMF_FLASH_PROGRAM input parameters                                 | 287 |

|                | 16.6.2.4 | RMF_FLASH_PROGRAM output structure syntax                          | 287 |

|                | 16.6.2.5 | RMF_FLASH_PROGRAM output parameters                                | 287 |

|                | 16.6.2.6 | RMF_FLASH_PROGRAM access/security policies                         | 288 |

|                | 16.6.2.7 | RMF_FLASH_PROGRAM example                                          | 288 |

| 16.6.3         | RMF_FL   | ASH_ERASE                                                          | 288 |

|                | 16.6.3.1 | RMF_FLASH_ERASE description                                        | 288 |

|                | 16.6.3.2 | RMF_FLASH_ERASE input structure syntax                             | 289 |

|                | 16.6.3.3 | RMF_FLASH_ERASE input parameters                                   | 289 |

|                | 16.6.3.4 | RMF_FLASH_ERASE output structure syntax                            | 290 |

|                | 16.6.3.5 | RMF_FLASH_ERASE output parameters                                  | 290 |

|                | 16.6.3.6 | RMF_FLASH_ERASE access/security policies                           | 291 |

|                | 16.6.3.7 | RMF_FLASH_ERASE example                                            | 291 |

| 16.6.4         | RMF_FL   | ASH_PROTECT and RMF_FLASH_UNPROTECT                                | 291 |

|                | 16.6.4.1 | RMF_FLASH_PROTECT and RMF_FLASH_UNPROTECT description              | 291 |

|                | 16.6.4.2 | RMF_FLASH_PROTECT and RMF_FLASH_UNPROTECT input structure syntax   | 292 |

|                | 16.6.4.3 | RMF_FLASH_PROTECT and RMF_FLASH_UNPROTECT output structure syntax  | 292 |

|                | 16.6.4.4 | RMF_FLASH_PROTECT and RMF_FLASH_UNPROTECT access/security policies | 292 |

|                | 16.6.4.5 | RMF_FLASH_PROTECT and RMF_FLASH_UNPROTECT example                  | 292 |

| 16.6.5         | RMF_FL   | ASH_UNSECURE                                                       | 292 |

|                | 16.6.5.1 | RMF_FLASH_UNSECURE description                                     | 292 |

|                | 16.6.5.2 | RMF_FLASH_UNSECURE input structure syntax                          | 293 |

|                | 16.6.5.3 | RMF_FLASH_UNSECURE output structure syntax                         | 293 |

|                | 16.6.5.4 | RMF_FLASH_UNSECURE access/security policies                        | 293 |

|                | 16.6.5.5 | RMF_FLASH_UNSECURE example                                         | 293 |

| 16.6.6    | RMF_CRC                                                                                                                                                                         | 293                          |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

|           | 16.664 PMT CDC 1 - 1 - 1                                                                                                                                                        |                              |

|           | 16.6.6.1 RMF_CRC description                                                                                                                                                    | 293                          |

|           | 16.6.6.2 RMF_CRC input structure syntax                                                                                                                                         | 294                          |

|           | 16.6.6.3 RMF_CRC input parameters                                                                                                                                               | 294                          |

|           | 16.6.6.4 RMF_CRC output structure syntax                                                                                                                                        | 294                          |

|           | 16.6.6.5 RMF_CRC error codes                                                                                                                                                    | 294                          |

|           | 16.6.6.6 RMF_CRC example                                                                                                                                                        | 295                          |

|           | 16.6.6.7 RMF_CRC access/security policies                                                                                                                                       | 295                          |

|           | Chapter 17 ColdFire v1 Interrupt Controller (CF1_INTC)                                                                                                                          |                              |

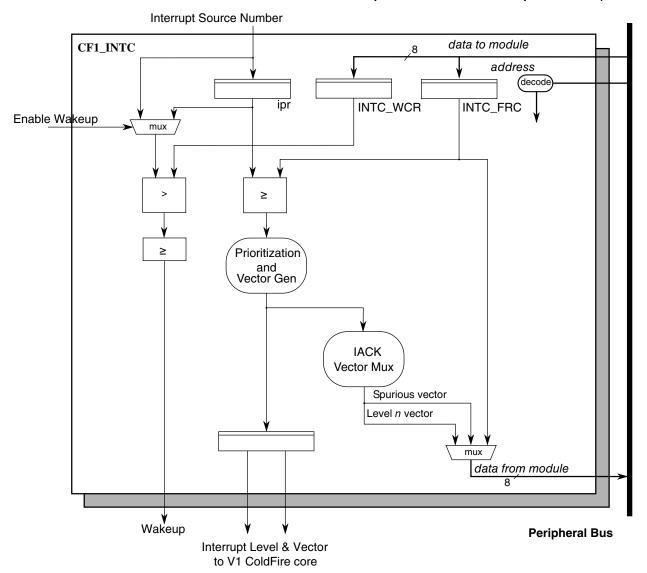

| Introduc  | ction                                                                                                                                                                           | 297                          |

| 17.1.1    | Overview                                                                                                                                                                        | 298                          |

| 17.1.2    | Features                                                                                                                                                                        | 301                          |

| 17.1.3    | Modes of Operation                                                                                                                                                              | 302                          |

| Externa   | l Signal Description                                                                                                                                                            | 302                          |

| Interrup  | ot Request Level and Priority Assignments                                                                                                                                       | 302                          |

| Memory    | y Map and Registers                                                                                                                                                             | 303                          |

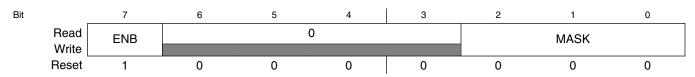

| 17.4.1    | Force Interrupt Register (INTC_FRC)                                                                                                                                             | 304                          |

| 17.4.2    | INTC Programmable Level 6 Priority Registers (INTC_PL6Pn)                                                                                                                       | 305                          |

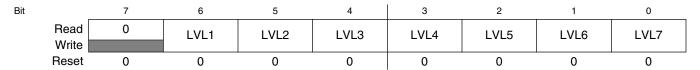

| 17.4.3    | INTC Wakeup Control Register (INTC_WCR)                                                                                                                                         | 306                          |

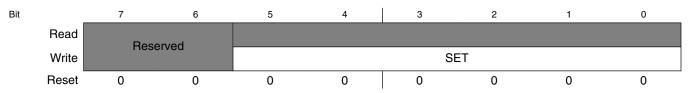

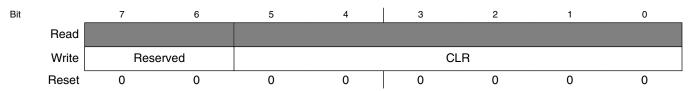

| 17.4.4    | INTC Set Interrupt Force Register (INTC_SFRC)                                                                                                                                   | 307                          |

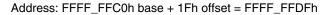

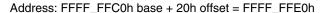

| 17.4.5    | INTC Clear Interrupt Force Register (INTC_CFRC)                                                                                                                                 | 308                          |

| 17.4.6    | INTC Software IACK Register (INTC_SWIACK)                                                                                                                                       | 309                          |

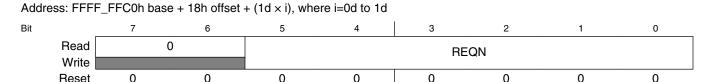

| 17.4.7    | INTC Level-n IACK Registers (INTC_LVLnIACK)                                                                                                                                     | 309                          |

| Functio   | nal Description                                                                                                                                                                 | 310                          |

| 17.5.1    | Handling of Non-Maskable Level 7 Interrupt Requests                                                                                                                             | 310                          |

| Initializ | ation Information                                                                                                                                                               | 311                          |

| Applica   | tion Information                                                                                                                                                                | 311                          |

| 17.7.1    | Emulation of the HCS08's 1-Level IRQ Handling                                                                                                                                   | 311                          |

|           | 17.1.1<br>17.1.2<br>17.1.3<br>External<br>Interrup<br>Memory<br>17.4.1<br>17.4.2<br>17.4.3<br>17.4.4<br>17.4.5<br>17.4.6<br>17.4.7<br>Functio<br>17.5.1<br>Initializ<br>Applica | 16.6.6.5 RMF_CRC error codes |

| Sec  | tion nu  | mber Title                                   | Page |

|------|----------|----------------------------------------------|------|

|      | 17.7.2   | Using INTC_PL6P{7,6} Registers               | 312  |

|      | 17.7.3   | More on Software IACKs                       | 313  |

|      |          | Chapter 18<br>Programmable Delay Block (PDB) |      |

| 18.1 | Introduc | ction                                        | 317  |

|      | 18.1.1   | Features                                     | 317  |

|      | 18.1.2   | Modes of operation.                          | 318  |

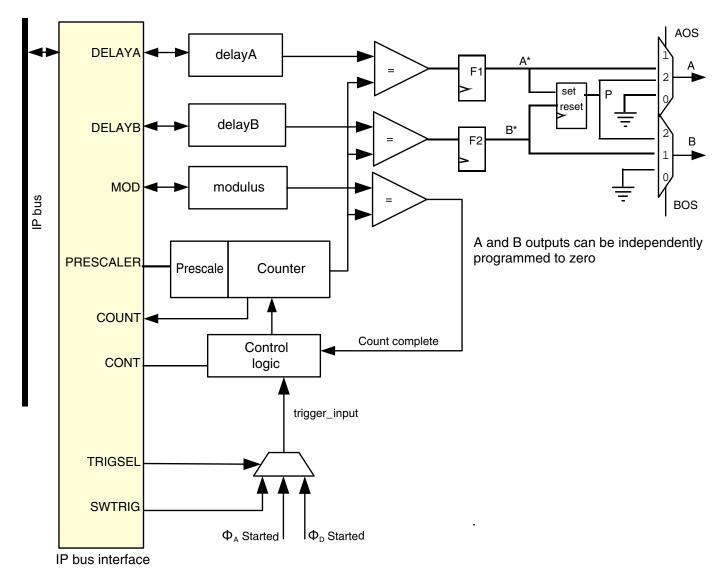

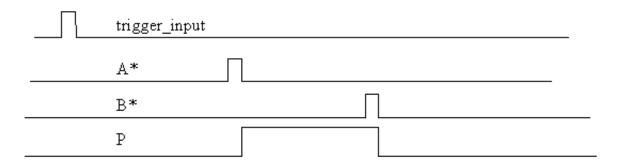

|      | 18.1.3   | Block diagram                                | 318  |

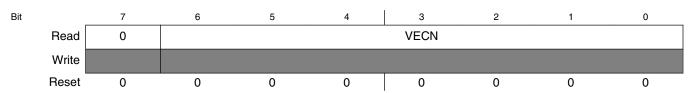

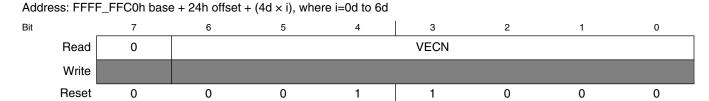

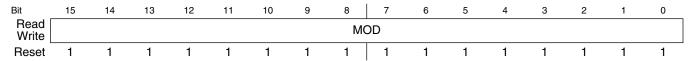

|      | 18.1.4   | PDB memory map/register definition           | 320  |

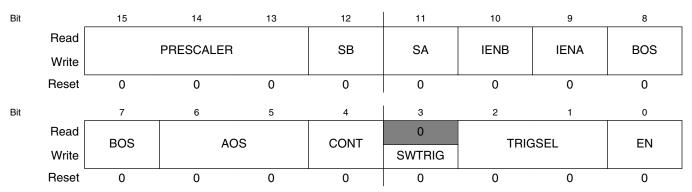

|      | 18.1.5   | PDB Control and Status Register (PDB_CSR)    | 320  |

|      | 18.1.6   | PDB Delay A Register (PDB_DELAYA)            | 322  |

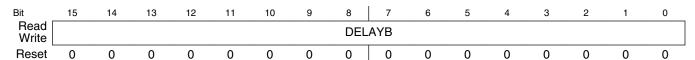

|      | 18.1.7   | PDB Delay B Register (PDB_DELAYB)            | 322  |

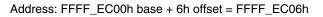

|      | 18.1.8   | PDB Counter Modulus Register (PDB_MOD)       | 323  |

|      | 18.1.9   | PDB Counter Value (PDB_COUNT)                | 323  |

|      | 18.1.10  | Considerations.                              | 323  |

| 18.2 | Resets   |                                              | 324  |

| 18.3 | Clocks.  |                                              | 324  |

| 18.4 | Interrup | ts                                           | 324  |

|      |          | Chapter 19<br>Modulo Timer 16-Bit (MTIM16)   |      |

| 19.1 | Chip-sp  | ecific information about MTIM16              | 325  |

| 19.2 | Introduc | ction                                        | 325  |

| 19.3 | Feature  | S                                            | 325  |

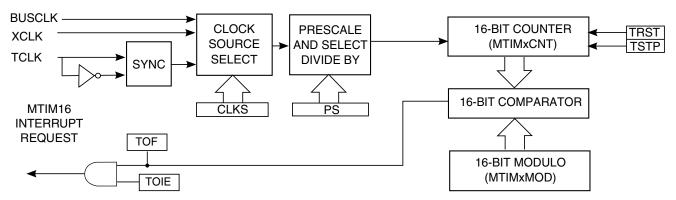

|      | 19.3.1   | Block Diagram                                | 326  |

|      | 19.3.2   | Modes of Operation                           | 326  |

|      |          | 19.3.2.1 MTIM16 in Wait Mode                 | 326  |

|      |          | 19.3.2.2 MTIM16 in Stop Modes                | 327  |

|      |          | 19.3.2.3 MTIM16 in Active Background Mode    | 327  |

| 19.4 | Externa  | l Signal Description                         | 327  |

|      |          |                                              |      |

| Sec  | tion nu  | mber Title                                                              | Page |

|------|----------|-------------------------------------------------------------------------|------|

| 19.5 | Memory   | y Map and Register Descriptions                                         | 328  |

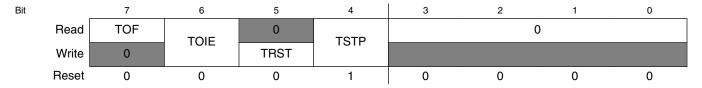

|      | 19.5.1   | MTIM16 status and control register (MTIM_SC)                            | 328  |

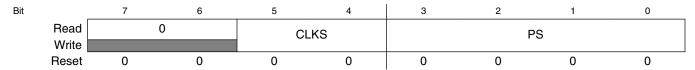

|      | 19.5.2   | MTIM16 clock configuration register (MTIM_CLK)                          | 329  |

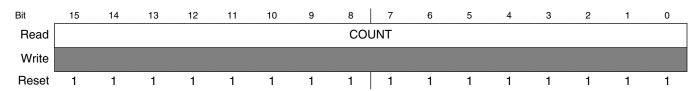

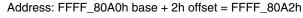

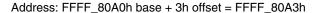

|      | 19.5.3   | MTIM16 counter register high (MTIM_CNTH)                                | 330  |

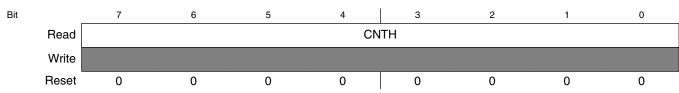

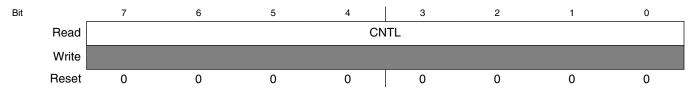

|      | 19.5.4   | MTIM16 counter register low (MTIM_CNTL)                                 | 331  |

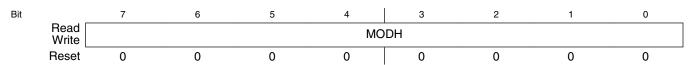

|      | 19.5.5   | MTIM16 modulo register high (MTIM_MODH)                                 | 332  |

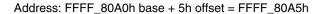

|      | 19.5.6   | MTIM16 modulo register low (MTIM_MODL)                                  | 333  |

| 19.6 | Function | nal Description                                                         | 333  |

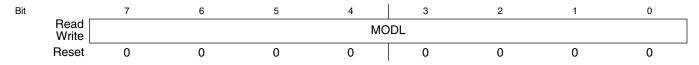

|      | 19.6.1   | MTIM16 Operation Example                                                | 334  |

|      |          | Chapter 20<br>Timer/Pulse-Width Modulator (TPM)                         |      |

| 20.1 | Introduc | ction                                                                   | 337  |

|      | 20.1.1   | Features.                                                               | 338  |

|      | 20.1.2   | Modes of operation                                                      | 338  |

|      |          | 20.1.2.1 Input capture                                                  | 338  |

|      |          | 20.1.2.2 Output compare                                                 | 339  |

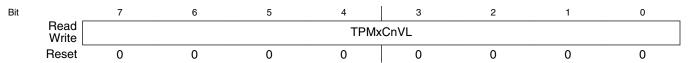

|      |          | 20.1.2.3 Edge-aligned PWM                                               | 339  |

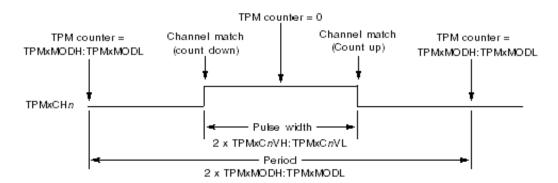

|      |          | 20.1.2.4 Center-aligned PWM                                             | 339  |

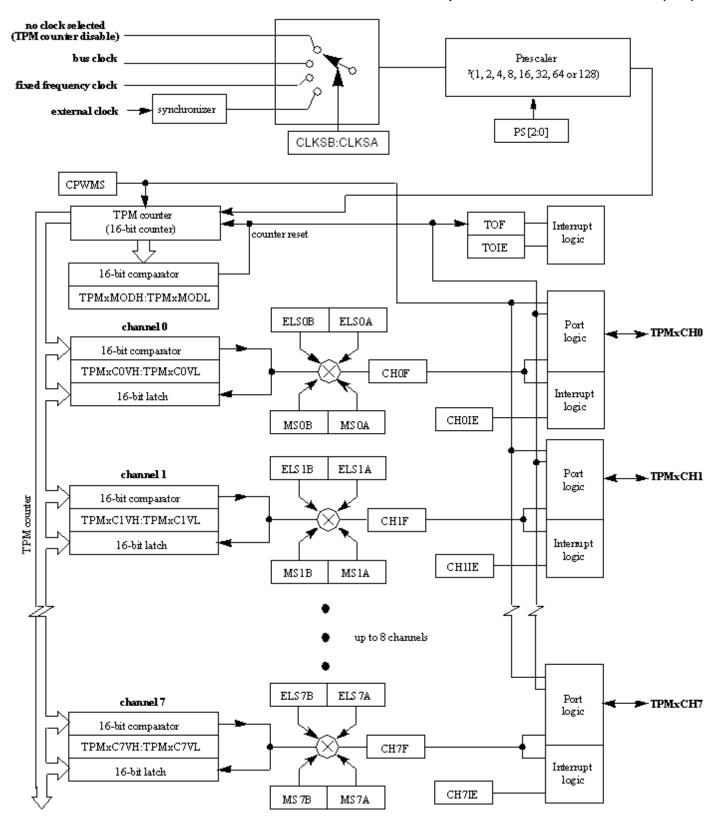

|      | 20.1.3   | Block diagram                                                           | 340  |

| 20.2 | Signal d | lescriptions                                                            | 342  |

|      | 20.2.1   | TPMxCHn - TPM channel n I/O pins                                        | 342  |

| 20.3 | TPM mo   | emory map/register definition                                           | 344  |

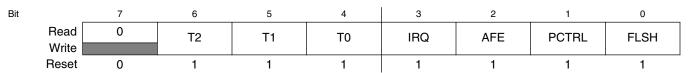

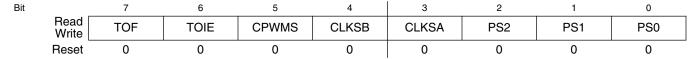

|      | 20.3.1   | TPM Status and Control Register (TPM_TPMxSC)                            | 345  |

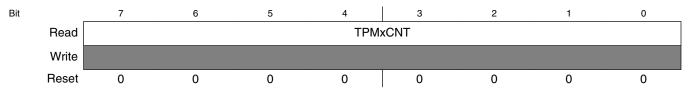

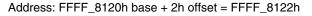

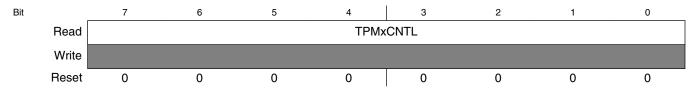

|      | 20.3.2   | TPM Counter Register High (TPM_TPMxCNTH)                                | 347  |

|      | 20.3.3   | TPM Counter Register Low (TPM_TPMxCNTL)                                 | 348  |

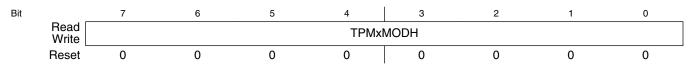

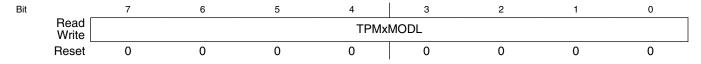

|      | 20.3.4   | TPM Counter Modulo Register High (TPM_TPMxMODH)                         | 349  |

|      | 20.3.5   | TPM Counter Modulo Register Low (TPM_TPMxMODHL)                         | 350  |

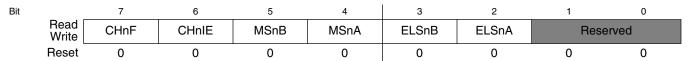

|      | 20.3.6   | TPM Channel n Status and Control Register (TPM_TPMxCnSC)                | 351  |

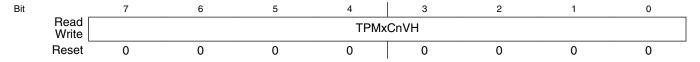

|      | 20.3.7   | TPM Channel Value Register High (TPM_TPMxCnVH)                          | 352  |

|      |          | Xtrinsic FXLC95000CL Intelligent Motion-Sensing Platform, Rev. 0.6, May | 2013 |

| Sect | tion nu  | ımber       | Titl                               | e Pag       |

|------|----------|-------------|------------------------------------|-------------|

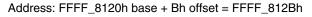

|      | 20.3.8   | TPM Cha     | nel Value Register Low (TPM_TPM    | xCnVL)354   |

| 20.4 | Functio  | nal descrip | on                                 | 355         |

|      | 20.4.1   | Counter     |                                    | 356         |

|      |          | 20.4.1.1    | Counter clock source               | 356         |

|      |          | 20.4.1.2    | Counter overflow and modulo reset. | 356         |

|      |          | 20.4.1.3    | Counting modes                     | 357         |

|      |          | 20.4.1.4    | Manual counter reset               | 357         |

|      | 20.4.2   | Channel r   | ode selection                      | 357         |

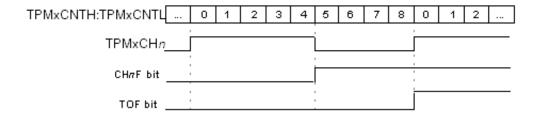

|      |          | 20.4.2.1    | Input capture mode                 |             |

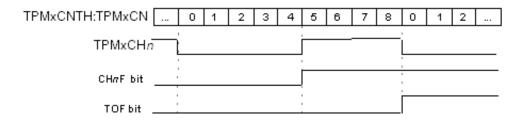

|      |          | 20.4.2.2    | Output compare mode                |             |

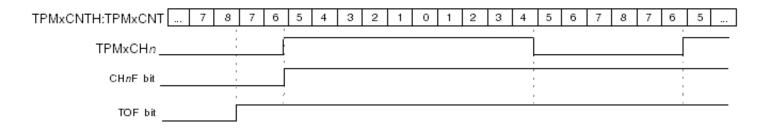

|      |          | 20.4.2.3    | Edge-aligned PWM mode              |             |

|      |          | 20.4.2.4    | Center-aligned PWM mode            |             |

| 20.5 | Reset    |             |                                    |             |

| 20.6 | Interrup | ots         |                                    |             |

|      | 20.6.1   | Two type    | of interrupts                      |             |

|      | 20.6.2   | Interrupt   | peration                           | 363         |

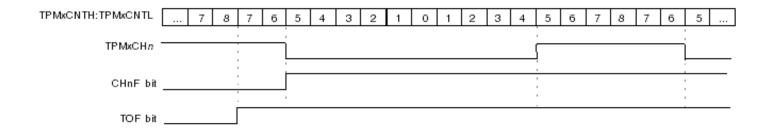

|      |          | 20.6.2.1    | Timer Overflow interrupt (TOF)     | 363         |

|      |          |             | 20.6.2.1.1 Normal case             | 363         |

|      |          |             | 20.6.2.1.2 Center-aligned PWM c    | ase363      |

|      |          | 20.6.2.2    | Channel event interrupt            |             |

|      |          |             | 20.6.2.2.1 Input capture events    | 364         |

|      |          |             | 20.6.2.2.2 Output compare events   | 364         |

|      |          |             | 20.6.2.2.3 PWM end-of-duty-cycl    | e events364 |

|      |          |             | Chapte<br>ColdFire v1 Core         |             |

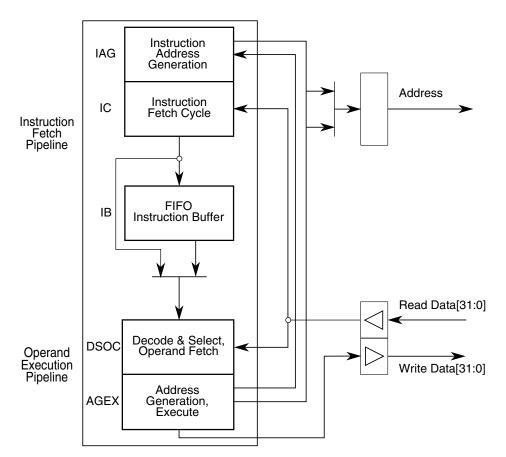

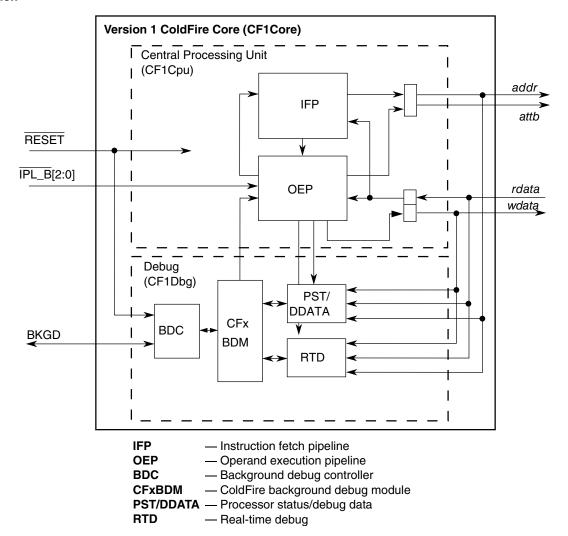

| 21.1 | Introdu  | ction       |                                    | 365         |

|      | 21.1.1   | Overview    |                                    |             |

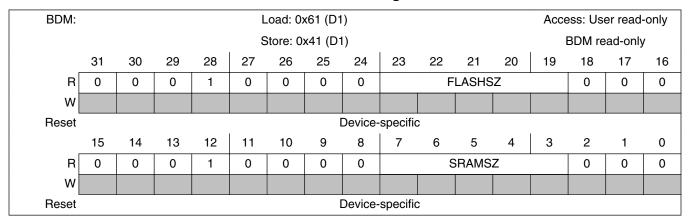

| 21.2 | Memor    | y Map/Regi  | ter Description                    | 367         |

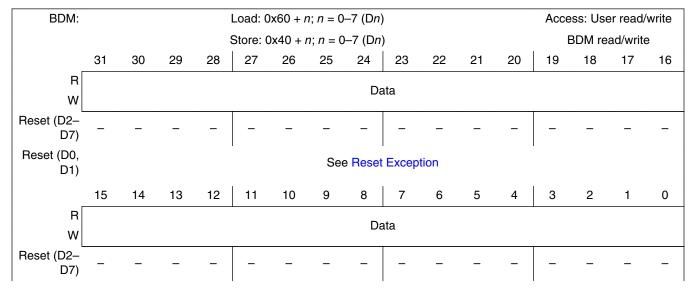

|      | 21.2.1   | Data regis  | ers (D0–D7)                        | 369         |

| tion nu | mber                                                                                              | Title                                                                                                                                                                                                                                                                                                                                                            | Page                             |

|---------|---------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

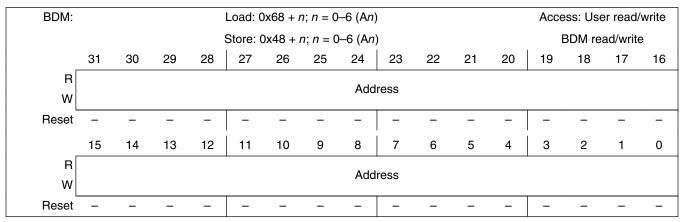

| 21.2.2  | Address re                                                                                        | egisters (A0–A6)                                                                                                                                                                                                                                                                                                                                                 | 370                              |

| 21.2.3  | Supervisor                                                                                        | r/user stack pointers (A7 and OTHER_A7)                                                                                                                                                                                                                                                                                                                          | 370                              |

| 21.2.4  | Condition                                                                                         | code register (CCR)                                                                                                                                                                                                                                                                                                                                              | 371                              |

| 21.2.5  | Program c                                                                                         | counter (PC)                                                                                                                                                                                                                                                                                                                                                     | 372                              |

| 21.2.6  | Vector bas                                                                                        | se register (VBR)                                                                                                                                                                                                                                                                                                                                                | 373                              |

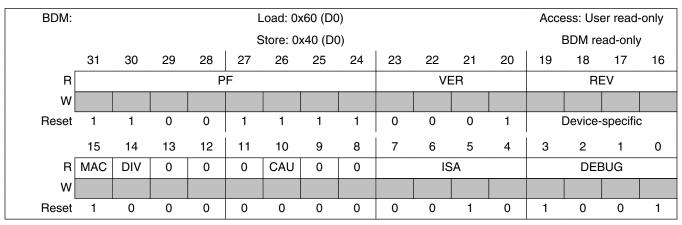

| 21.2.7  | CPU confi                                                                                         | iguration register (CPUCR)                                                                                                                                                                                                                                                                                                                                       | 373                              |

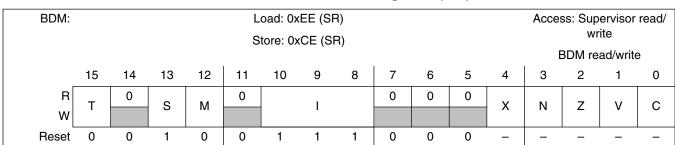

| 21.2.8  | Status regi                                                                                       | ister (SR)                                                                                                                                                                                                                                                                                                                                                       | 375                              |

| Functio | nal Descript                                                                                      | tion                                                                                                                                                                                                                                                                                                                                                             | 376                              |

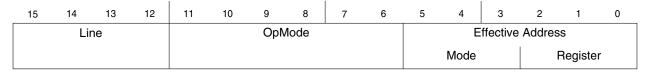

| 21.3.1  | Instruction                                                                                       | n Set Architecture                                                                                                                                                                                                                                                                                                                                               | 376                              |

| 21.3.2  | Exception                                                                                         | Processing Overview                                                                                                                                                                                                                                                                                                                                              | 377                              |

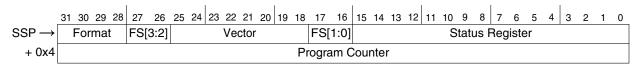

|         | 21.3.2.1                                                                                          | Exception Stack Frame Definition                                                                                                                                                                                                                                                                                                                                 | 380                              |

|         | 21.3.2.2                                                                                          | S08 and ColdFire Exception Processing Comparison                                                                                                                                                                                                                                                                                                                 | 381                              |

| 21.3.3  | Processor                                                                                         | Exceptions                                                                                                                                                                                                                                                                                                                                                       | 383                              |

|         | 21.3.3.1                                                                                          | Access Error Exception                                                                                                                                                                                                                                                                                                                                           | 383                              |

|         | 21.3.3.2                                                                                          | Address Error Exception                                                                                                                                                                                                                                                                                                                                          | 384                              |

|         | 21.3.3.3                                                                                          | Illegal Instruction Exception.                                                                                                                                                                                                                                                                                                                                   | 384                              |

|         | 21.3.3.4                                                                                          | Privilege Violation.                                                                                                                                                                                                                                                                                                                                             | 386                              |

|         | 21.3.3.5                                                                                          | Trace Exception.                                                                                                                                                                                                                                                                                                                                                 | 386                              |

|         | 21.3.3.6                                                                                          | Unimplemented Line-A Opcode                                                                                                                                                                                                                                                                                                                                      | 387                              |

|         | 21.3.3.7                                                                                          | Unimplemented Line-F Opcode                                                                                                                                                                                                                                                                                                                                      | 387                              |

|         | 21.3.3.8                                                                                          | Debug Interrupt                                                                                                                                                                                                                                                                                                                                                  | 387                              |

|         | 21.3.3.9                                                                                          | RTE and Format Error Exception                                                                                                                                                                                                                                                                                                                                   | 387                              |

|         | 21.3.3.10                                                                                         | TRAP Instruction Exception                                                                                                                                                                                                                                                                                                                                       | 388                              |

|         | 21.3.3.11                                                                                         | Unsupported Instruction Exception.                                                                                                                                                                                                                                                                                                                               | 388                              |

|         | 21.3.3.12                                                                                         | Interrupt Exception                                                                                                                                                                                                                                                                                                                                              | 388                              |

|         | 21.3.3.13                                                                                         | Fault-on-Fault Halt.                                                                                                                                                                                                                                                                                                                                             | 389                              |

|         | 21.3.3.14                                                                                         | Reset Exception.                                                                                                                                                                                                                                                                                                                                                 | 389                              |

| 21.3.4  | Instruction                                                                                       | n Execution Timing                                                                                                                                                                                                                                                                                                                                               | 392                              |

|         | 21.3.4.1                                                                                          | Timing Assumptions                                                                                                                                                                                                                                                                                                                                               | 392                              |

|         | 21.2.2<br>21.2.3<br>21.2.4<br>21.2.5<br>21.2.6<br>21.2.7<br>21.2.8<br>Functio<br>21.3.1<br>21.3.2 | 21.2.3 Supervisor 21.2.4 Condition 21.2.5 Program of 21.2.6 Vector back 21.2.7 CPU configures 21.2.8 Status reg Functional Descrip 21.3.1 Instruction 21.3.2 Exception 21.3.2.1 21.3.2.2 21.3.3 Processor 21.3.3.1 21.3.3.2 21.3.3.3 21.3.3.4 21.3.3.5 21.3.3.6 21.3.3.7 21.3.3.8 21.3.3.9 21.3.3.10 21.3.3.11 21.3.3.12 21.3.3.12 21.3.3.14 21.3.3.14 21.3.3.14 | 21.2.2 Address registers (A0-A6) |

| Section number |            | nber Title                                                | Page |

|----------------|------------|-----------------------------------------------------------|------|

|                | 2          | 21.3.4.2 MOVE Instruction Execution Times                 | 393  |

|                | 2          | 21.3.4.3 Standard One Operand Instruction Execution Times | 394  |

|                | 2          | 21.3.4.4 Standard Two Operand Instruction Execution Times | 395  |

|                | 2          | 21.3.4.5 Miscellaneous Instruction Execution Times        | 396  |

|                | 2          | 21.3.4.6 MAC Instruction Execution Times                  | 397  |

|                | 2          | 21.3.4.7 Branch Instruction Execution Times               | 398  |

|                |            | Chapter 22 ColdFire v1 Debug (CF1_DEBUG)                  |      |

| 22.1           | Chip-spec  | cific information about CF1_DEBUG                         | 401  |

| 22.2           | Introducti | ion                                                       | 401  |

|                | 22.2.1     | Overview                                                  | 402  |

|                | 22.2.2     | Features                                                  | 403  |

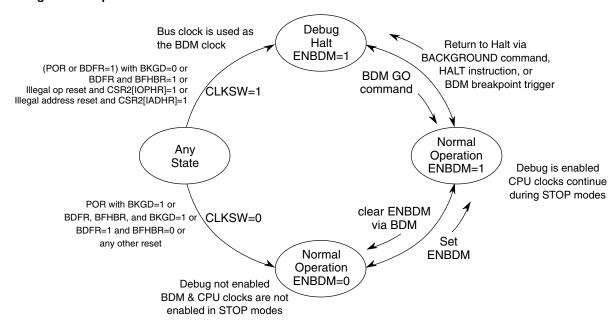

|                | 22.2.3     | Modes of Operation                                        | 404  |

| 22.3           | External S | Signal Descriptions                                       | 406  |

| 22.4           | Memory 1   | Map and Register Descriptions                             | 407  |

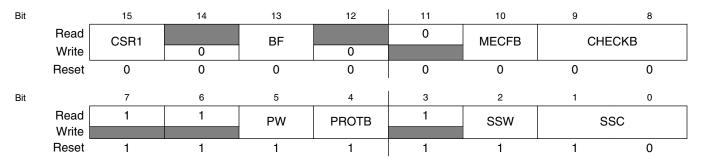

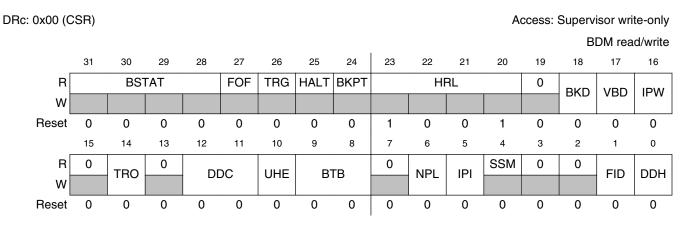

|                | 22.4.1     | Configuration/Status Register (CSR)                       | 409  |

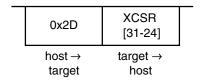

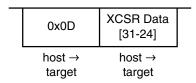

|                | 22.4.2     | Extended Configuration/Status Register (XCSR)             | 412  |

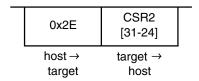

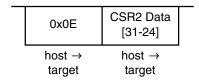

|                | 22.4.3     | Configuration/Status Register 2 (CSR2)                    | 415  |

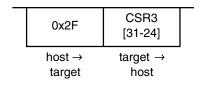

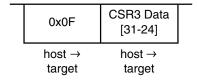

|                | 22.4.4     | Configuration/Status Register 3 (CSR3)                    | 418  |

|                | 22.4.5     | BDM Address Attribute Register (BAAR)                     | 420  |

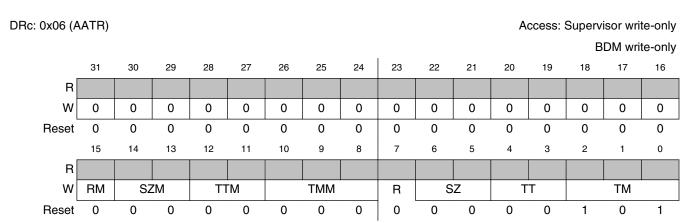

|                | 22.4.6     | Address Attribute Trigger Register (AATR)                 | 421  |

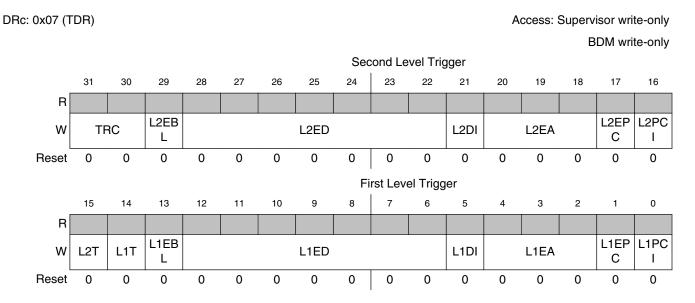

|                | 22.4.7     | Trigger Definition Register (TDR)                         | 422  |

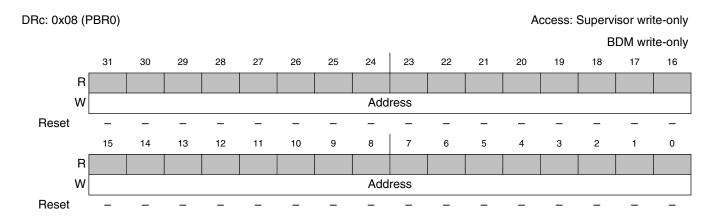

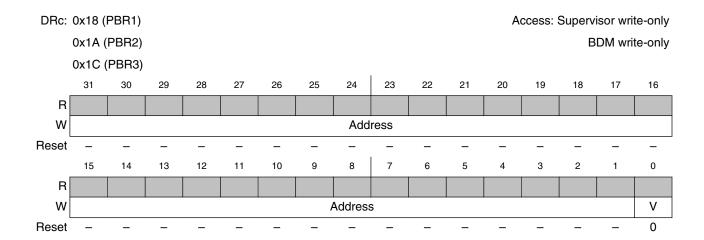

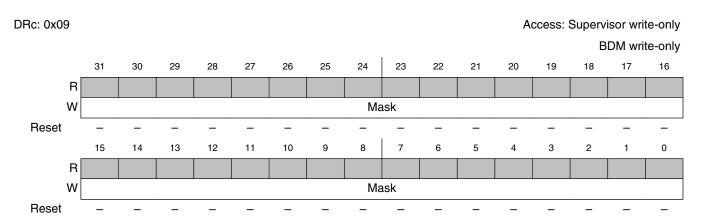

|                | 22.4.8     | Program Counter Breakpoint/Mask Registers (PBR0-3, PBMR)  | 425  |

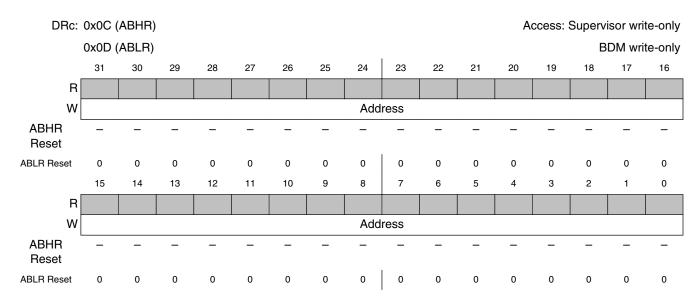

|                | 22.4.9     | Address Breakpoint Registers (ABLR, ABHR)                 | 427  |

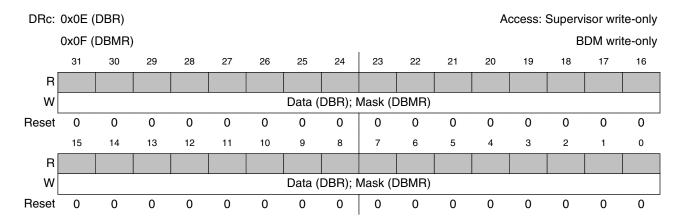

|                | 22.4.10    | Data Breakpoint and Mask Registers (DBR, DBMR)            | 429  |

|                | 22.4.11    | Resulting Set of Possible Trigger Combinations            | 430  |

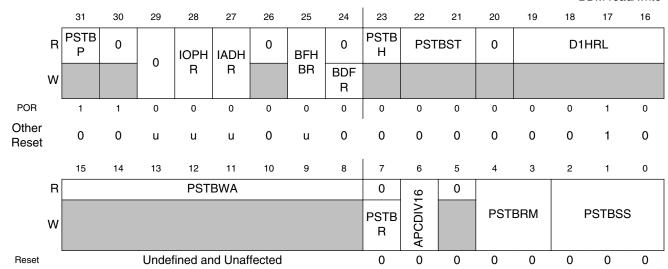

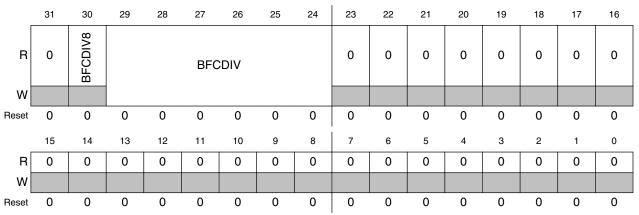

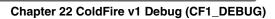

|                | 22.4.12    | PST Buffer (PSTB)                                         | 430  |

| Section number |         |             | Title       |                                         |     |

|----------------|---------|-------------|-------------|-----------------------------------------|-----|

| 22.5           | Functio | nal Descrip | otion       |                                         | 432 |

|                | 22.5.1  | Backgrou    | nd Debug Mo | de (BDM)                                | 432 |

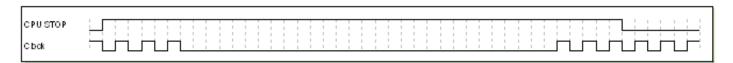

|                |         | 22.5.1.1    | CPU Halt    |                                         | 433 |

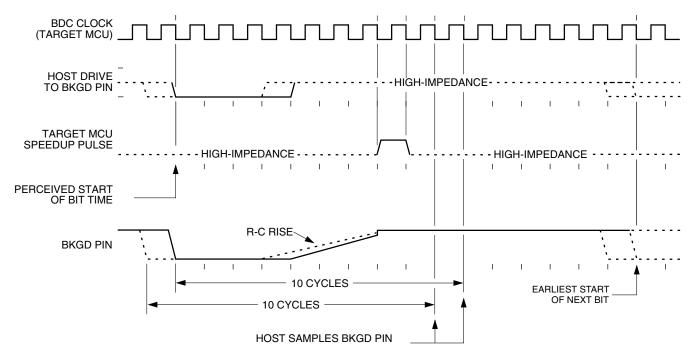

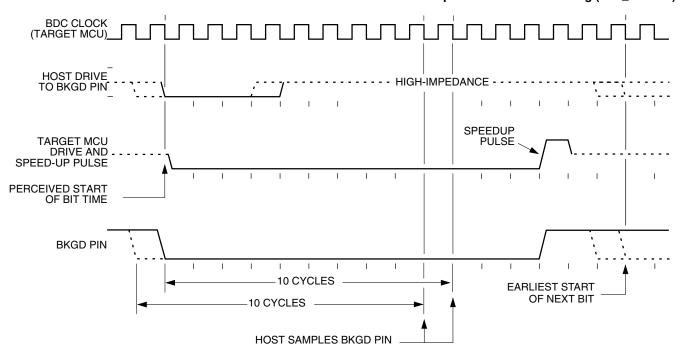

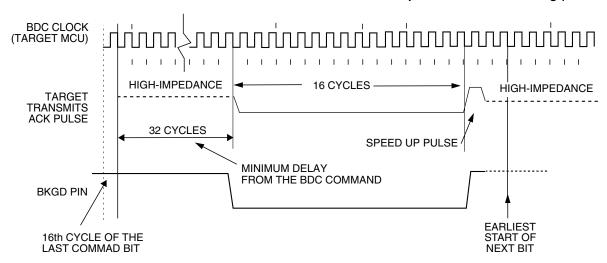

|                |         | 22.5.1.2    | Background  | Debug Serial Interface Controller (BDC) | 435 |

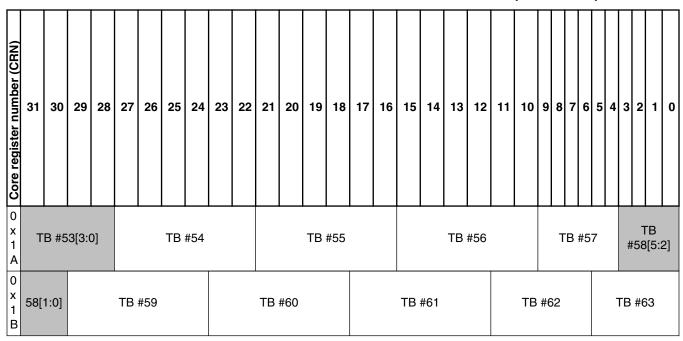

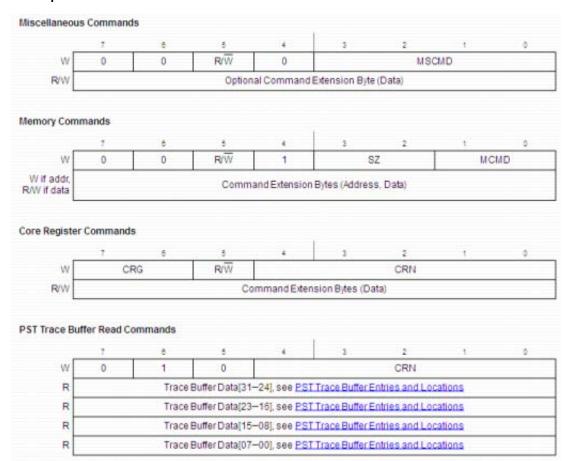

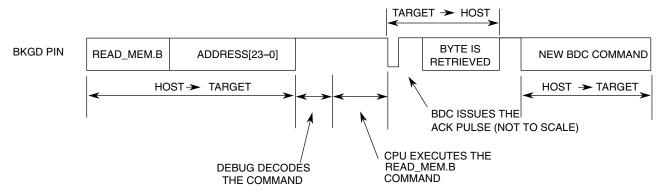

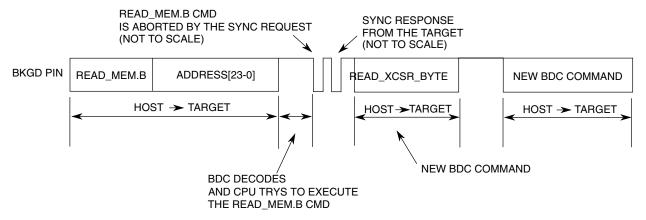

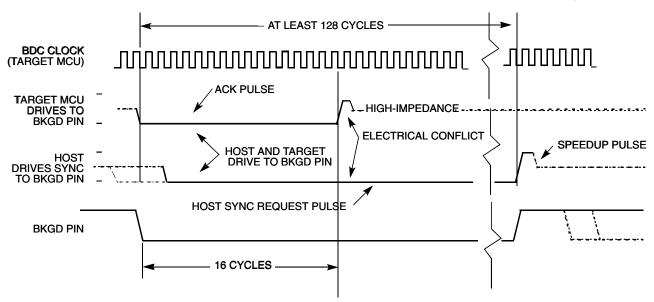

|                |         | 22.5.1.3    | BDM Comn    | nunication Details                      | 436 |

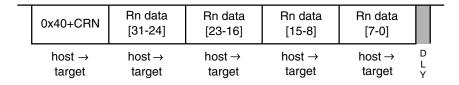

|                |         | 22.5.1.4    | BDM Comn    | nand Set Descriptions                   | 439 |

|                |         | 22.5.1.5    | BDM Comn    | nand Set Summary                        | 441 |

|                |         |             | 22.5.1.5.1  | SYNC                                    | 444 |

|                |         |             | 22.5.1.5.2  | ACK_DISABLE                             | 445 |

|                |         |             | 22.5.1.5.3  | ACK_ENABLE                              | 445 |

|                |         |             | 22.5.1.5.4  | BACKGROUND                              | 445 |

|                |         |             | 22.5.1.5.5  | DUMP_MEM.sz, DUMP_MEM.sz_WS             | 446 |

|                |         |             | 22.5.1.5.6  | FILL_MEM.sz, FILL_MEM.sz_WS             | 447 |

|                |         |             | 22.5.1.5.7  | GO                                      | 449 |

|                |         |             | 22.5.1.5.8  | NOP                                     | 449 |

|                |         |             | 22.5.1.5.9  | READ_CREG                               | 450 |

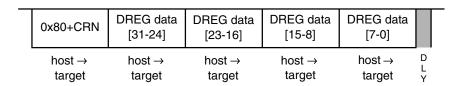

|                |         |             | 22.5.1.5.10 | READ_DREG                               | 450 |

|                |         |             | 22.5.1.5.11 | READ_MEM.sz, READ_MEM.sz_WS             | 450 |

|                |         |             | 22.5.1.5.12 | READ_PSTB                               | 452 |

|                |         |             | 22.5.1.5.13 | READ_Rn                                 | 452 |