# **ATM Switch Line Card**

#### Overview

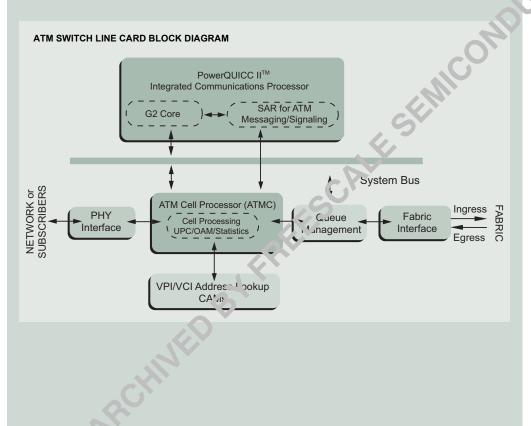

Line cards interconnect the ATM switch to users, other switches, and other network elements. Because information within the cell payload is carried transparently by the ATM network, the switch must process only the cell headers when the cells are received as inputs to the line card. The virtual path identifier/virtual channel identifier (VPI/VCI) information contained in the cell header is directly or indirectly used to route the cell through the switch to the appropriate output port(s). Finally, the egress line card may modify the VPI/VCI as the cell leaves the switch.

### Key Benefits

- Provides intelagence for a smart ATM נ'פווסרת developh סוגל

- > Delive rs features designed startifically for ATM switching tasks

- Processors designed to tightly link forwarding and control planes

| Freescale Ordering Information |                                                                                                                                                                                                                                                                                                                                                |                              |  |  |

|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|--|--|

|                                |                                                                                                                                                                                                                                                                                                                                                |                              |  |  |

| MPC850                         | <ul> <li>&gt; 80 MHz maximum speed</li> <li>&gt; 2K-bytes cache-L1 instructional</li> <li>&gt; 1K-byte cache-L1 data</li> <li>&gt; 8-entry translation lookaside buffers</li> </ul>                                                                                                                                                            | www.freescale.com/netcomm    |  |  |

| MPC860                         | <ul> <li>&gt; 80MHz maximum speed</li> <li>&gt; 4K-bytes cache-L1 instructional (DE, DT, EN, SR, and T)</li> <li>&gt; 16K-bytes cache-L1 instructional (DP and P)</li> <li>&gt; 4K-bytes cache-L1 data (DE, DT, EN, SR, and T)</li> <li>&gt; 8K-bytes cache-L1 data (DP and P)</li> <li>&gt; 32-entry translation lookaside buffers</li> </ul> | www.freescale.com/netcomm    |  |  |

| MPC8260                        | <ul> <li>&gt; 300 MHz maximum speed</li> <li>&gt; 16K-bytes cache-L1 instructional</li> <li>&gt; 16K-bytes cache-L1 data</li> <li>&gt; 64-entry translation lookaside buffers</li> <li>&gt; Floating point unit</li> </ul>                                                                                                                     | www.freescale.com/~ >tcori.m |  |  |

# ATM Switch Line Card

Freescale Semiconductor's comprehensive network infrastructure processor portfolio provides the intelligence for smart ATM switch development platforms. Freescale Semiconductor's processor portfolio delivers features designed specifically for ATM switching tasks.

Within networking applications, communications tasks are typically divided into two areas:

- Forwarding plane (operations on the forwarding path data in real time)

- Control plane (less time-critical management functions)

Freescale Semiconductor's processer, are designed to integrate the for and indig and control planes tightly, helping reduce

the development time devoted to integration tasks while providing greater freedom to shift and share functions across processors as needs change PowerQIUCC™, with a suite of interworking ATM network protocols, makes Freescale Semico intercor the smart choice.

## Design Challenge

- > A feature-rich % in line card is complex and would be very large if all functions vere implemented discremay.

- Consetup and tear-down, intra- and inter-equipment communication, and line card management functions.

- Cell processing functions including address translation; congestion

nanagement (EPD and PPD) and policing (UPC/NPC); operation, administration, and maintenance (OAM); and per-PHY and per-VC statistics gathering.

- VPI/VCI address lookup matching incoming address identifiers with a switching table determining the destination port.

- > The PHY interface includes all the framers, transceivers, and other components required to implement the physical interface with the network or subscribers. Traditional approaches require separate hardware and general purpose CPUs for each interface type and protocol, resulting in many individual designs and limited reuse of software.

# Freescale Semiconductor Solution

Freescale Semiconductor's flexible ATM switch architecture enables the implementation of a broad spectrum of uplink and interworking line cards by adding the appropriate PHY interface for the application. Listed hardware below include designs for OC-3, T-Carrier, High-Density DSL, and Frame Relay Interworking Line Cards and differ only in the PHY interface.

- > Many members of the PowerQUICC and PowerQUICC II<sup>™</sup> families of Integrated Communications Processors integrate ATM support onchip, including all ATM layer functions, per ATM Forum user network interface (UNI) specification, and many AAL functions.

- > The physical interface can be accomplished by two methods: via standard UTOPIA ports, or serially, via multiple on-chip communications

controllers. Additionally, some controllers provide transmission convergence (TC) sub-layer functionality so they can receive any serial ATM data stream with bytealigned synchronization, including T3/ E3 or DSL.

- > For applications requiring less than full rate, full duplex OC-3 performance, PowerQUICC II with Multi-Service Platform (MSP) microcode allows most ATM switching functionality inside the device, significantly lowering design cost.

- Inverse-multiplexing for ATM microcode provides for increasing or decreasing bandwidth by allowing the addition or removal of lower bandwidth ATM links such as E1/T1.

- > PowerQUICC II processors also (ffer eight channels of ATC TC-lave permitting connection to lowe, speed

(E1/T1/xDSL) serial framers, and do not include TC-layer support.

> Freescale Semiconductor's Content Addressable Memories (CAMs) are particularly well suited for VPI/VCI translation in ATM switches. Because they are implemented with standard RAM cells, they enable solutions at a fraction of the price of traditional CAM implementations.

The PowerQUICC Ir the traced Communications Processor supports additional microcode in ROM (also available in CA A packages), thus enabling flectible feature enhancement. The cs.cb/lished code base and broad think party support from Freescale Sciniconductor's Smart Networks Alliance Program members further enable cost-efficient solutions and accelerated time-to-market for ATM switch equipment suppliers.

#### **Development Tools**

|             |                |                           | Description                                                  |

|-------------|----------------|---------------------------|--------------------------------------------------------------|

| Hardware    | MPC8XXFADSMB   | Freescale Semicrdu.*r.    | For MPC8xx Family Application Development System Motherboard |

| Development | MPC8260ADS-P   | Freescale Servicon Juctor | MPC8260 Application Development System                       |

| Development | MPC8260ADS-L2C | Freescale Someonductor    | MPC8260 Application Development System (with L2 Cache)       |

| Development | MPC8260ADS-KIT | Free: a', Semiconductor   | MPC8260 Application Development System Kit                   |

### PowerQUICC Integrated Communications Processors

- > MPC850 family, including the MPC850SR

- > MPC857T with enhanced 4. \*/ support

- > MPC860 family, including the MPC860SAR

- MPC862 with enhanced ATM support

- MPC8255, MPC8260, MPC8264, MPC8265, and MPC8266

PowerQUICC II next-generation family

- > PowerQUICC and PowerQUICC II microcodes packages provide enhanced forwarding plane features

The family of CAMs, Freescale Semiconductor's Smart Networks Alliance Program, is designed to enable the broadest suite of solutions for

communications OEM customers leveraging the Smart Networks Platform.

*Learn More:* Contact the Technical Information Center at +1-800-521-6247 or +1-480-768-2130. For more information about Freescale products, please visit **www.freescale.com**.

Freescale <sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © Freescale Semiconductor, Inc. 2004. All rights reserved.

SG2132 REV 1 12/2004