Advance Information

MPC857TTS/D Rev. 1, 7/2002

MPC857T/857DSL Integrated Communications Controller Technical Summary

This document provides an overview of the MPC857T/857DSL Communications Processor, describing major functions and features.

The MPC857T/857DSL Integrated Communications Controller is a versatile one-chip integrated microprocessor and peripheral combination that can be used in a variety of controller applications. It particularly excels in both communications and networking systems.

The MPC857T/857DSL is a PowerPC architecture-based derivative of Motorola's MPC860 Quad Integrated Communications Controller (PowerQUICC). The CPU on the MPC857T/857DSL is the MPC8xx core, a 32-bit microprocessor which implements the PowerPC architecture, incorporating memory management units (MMUs) and instruction and data caches.

Table 1 shows the functionality supported by the members of the MPC857T/857DSL family:

Table 1. MPC857T/857DSL Functionality Matrix

| Part      | SCC and SMC Support                                                        | ATM Support         |

|-----------|----------------------------------------------------------------------------|---------------------|

| MPC857T   | One SCC (SCC1) - includes Ethernet support. Two SMCs.                      | UTOPIA<br>interface |

| MPC857DSL | One SCC (SCC1) - Ethernet only. No TSA. One SMC (SMC1) (for UART support). | UTOPIA interface    |

### 1.1 Features

The following list summarizes the key MPC857T/857DSL features:

• Embedded MPC8xx core

- Single-issue, 32-bit core (compatible with the PowerPC architecture definition) with 32, 32-bit general-purpose registers (GPRs)

- The core performs branch prediction with conditional prefetch, without conditional execution

- 4-Kbyte data cache and 4-Kbyte instruction cache.

- 4-Kbyte instruction cache is two-way, set-associative with 128 sets.

- 4-Kbyte data cache is two-way, set-associative with 128 sets.

- Cache coherency for both instruction and data caches is maintained on 128-bit (4-word) cache blocks.

- Caches are physically addressed, implement a least recently used (LRU) replacement algorithm, and are lockable on a cache block basis.

- MMUs with 32-entry TLB, fully associative instruction and data TLBs

- MMUs support multiple page sizes of 4, 16, and 512 Kbytes, and 8 Mbytes; 16 virtual address spaces and 16 protection groups

- Advanced on-chip-emulation debug mode

- The MPC857T/857DSL provides enhanced ATM functionality over that of the MPC860SAR. The MPC857T/857DSL adds major new features available in "enhanced SAR" (ESAR) mode, including the following:

- Improved operation, administration and maintenance (OAM) support

- OAM performance monitoring (PM) support

- Multiple APC priority levels available to support a range of traffic pace requirements

- ATM port-to-port switching capability without the need for RAM-based microcode

- Simultaneous MII (10/100Base-T) and UTOPIA (half-duplex) capability

- Optional statistical cell counters per PHY

- UTOPIA level 2 compliant interface with added FIFO buffering to reduce the total cell transmission time. (The earlier UTOPIA level 1 specification is also supported.)

- Multi-PHY support on the MPC857T

- Four PHY support on the MPC857DSL

- Parameter RAM for both SPI and I<sup>2</sup>C can be relocated without RAM-based microcode

- Supports full-duplex UTOPIA both master (ATM side) and slave (PHY side) operation using a "split" bus

- AAL2/VBR is ROM resident

- Up to 32-bit data bus (dynamic bus sizing for 8, 16, and 32 bits)

- 32 address lines

- Memory controller (eight banks)

- Contains complete dynamic RAM (DRAM) controller

- Each bank can be a chip select or  $\overline{RAS}$  to support a DRAM bank

- Up to 30 wait states programmable per memory bank

- Glueless interface to Page mode/EDO/SDRAM, SRAM, EPROMs, flash EPROMs, and other memory devices

- DRAM controller programmable to support most size and speed memory interfaces

- Four  $\overline{CAS}$  lines, four  $\overline{WE}$  lines, one  $\overline{OE}$  line

- Boot chip-select available at reset (options for 8-, 16-, or 32-bit memory)

- Variable block sizes (32 Kbyte–256 Mbyte)

- Selectable write protection

- On-chip bus arbitration logic

- General-purpose timers

- Four 16-bit timers cascadable to be two 32-bit timers

- Gate mode can enable/disable counting

- Interrupt can be masked on reference match and event capture

- Fast Ethernet controller (FEC)

- Simultaneous MII (10/100Base-T) and UTOPIA operation when using the UTOPIA multiplexed bus.

- System integration unit (SIU)

- Bus monitor

- Software watchdog

- Periodic interrupt timer (PIT)

- Low-power stop mode

- Clock synthesizer

- Decrementer and time base

- Real-time clock (RTC)

- Reset controller

- IEEE 1149.1 test access port (JTAG)

- Interrupts

- Seven external interrupt request (IRQ) lines

- 12 port pins with interrupt capability

- 20 internal interrupt sources

- Programmable highest priority request

#### -eatures

- Communications processor module (CPM)

- RISC controller

- Communication-specific commands (for example, GRACEFUL STOP TRANSMIT, ENTER HUNT MODE, and RESTART TRANSMIT)

- Supports continuous mode transmission and reception on all serial channels

- 8-Kbytes of dual-port RAM

- 10 serial DMA (SDMA) channels on the MPC857T. Eight serial DMA (SDMA) channels on the MPC857DSL.

- Three parallel I/O registers with open-drain capability

- Four baud rate generators

- Independent (can be connected to SCC or SMC)

- Allow changes during operation

- Autobaud support option

- One SCC (serial communication controller), SCC1 (On the MPC857DSL, Ethernet is the only functionality of this SCC)

- Serial ATM capability

- Ethernet/IEEE 802.3 supporting full 10-Mbps operation

- HDLC/SDLC

- HDLC bus (implements an HDLC-based local area network (LAN))

- Asynchronous HDLC to support PPP (point-to-point protocol)

- AppleTalk

- Universal asynchronous receiver transmitter (UART)

- Synchronous UART

- Serial infrared (IrDA)

- Binary synchronous communication (BISYNC)

- Totally transparent (bit streams)

- Totally transparent (frame based with optional cyclic redundancy check (CRC))

- Two SMCs (serial management channels)

- UART. The MPC857DSL contains only one SMC, to implement UART.

- Transparent

- General circuit interface (GCI) controller

- Can be connected to the time-division multiplexed (TDM) channel

- One SPI (serial peripheral interface)

- Supports master and slave modes

- Supports multimaster operation on the same bus

- One I<sup>2</sup>C (inter-integrated circuit) port

- Supports master and slave modes

- Multiple-master environment support

- Time-slot assigner (TSA) (There is no TSA on the MPC857DSL)

- Allows SCC and SMCs to run in multiplexed and/or non-multiplexed operation

- Supports T1, CEPT, PCM highway, user defined

- 1- or 8-bit resolution

- Allows independent transmit and receive routing, frame synchronization, clocking

- Allows dynamic changes

- Can be internally connected to three serial channels (one SCC and two SMCs)

- Parallel interface port (PIP)

- Centronics interface support

- Supports fast connection between compatible ports on MPC857T/857DSL or other MPC8xx devices.

- PCMCIA interface

- Master (socket) interface, release 2.1 compliant

- Supports two independent PCMCIA sockets. The MPC857DSL supports only one PCMCIA socket (on Port B).

- 8 memory or I/O windows supported

- Low power support

- Full on—All units fully powered

- Doze—Core functional units disabled except time base decrementer, PLL, memory controller, RTC, and CPM in low-power standby

- Sleep—All units disabled except RTC, PIT, time base, and decrementer with PLL active for fast wake up

- Deep sleep—All units disabled including PLL except RTC, PIT, time base, and decrementer.

- Power down mode— All units powered down except PLL, RTC, PIT, time base and decrementer

- Debug interface

- Eight comparators: four operate on instruction address, two operate on data address, and two operate on data

- Supports conditions: = <>

- Each watchpoint can generate a break point internally

- 3.3 V core, 3.3 V I/O

- 357-pin Plastic Ball Grid Array (PBGA) package

- Operation up to 100MHz

Embedded MPC8xx Core

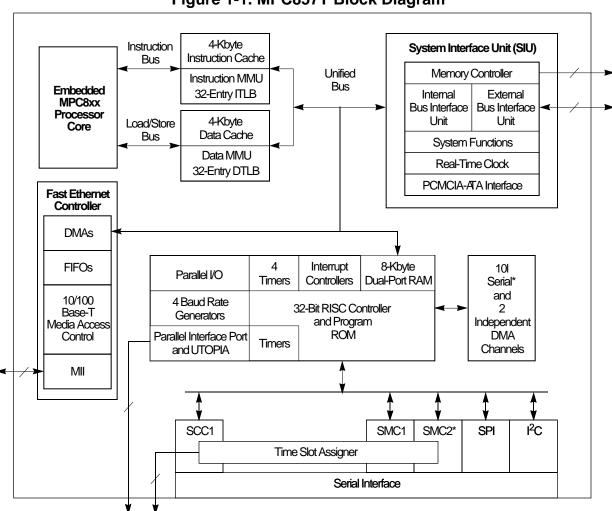

The MPC857T/857DSL is comprised of three modules that each use the 32-bit internal bus: the MPC8xx core, the system integration unit (SIU), and the communication processor module (CPM). The MPC857T block diagram is shown in Figure 1-1.

Figure 1-1. MPC857T Block Diagram

### 1.2 Embedded MPC8xx Core

The MPC857T/857DSL integrates an embedded MPC8xx core with high-performance, low-power peripherals to extend the Motorola data communications family of embedded processors farther into high-end communications and networking products.

The core is compliant with the UISA (user instruction set architecture) portion of the PowerPC architecture. It has an integer unit (IU) and a load/store unit (LSU) that execute all integer and load/store operations in hardware. The core supports integer operations on a 32-bit internal data path and 32-bit arithmetic hardware. The core interface to the internal and external buses is 32 bits.

<sup>\*</sup> The MPC857DSL does not contain SMC2 nor the Time Slot Assigner, and provides eight SDMA controllers.

System Interface Unit (SIU)

The IU uses 32, 32-bit GPRs for source and target operands. Typically, it can execute one integer instruction each clock cycle. Each element in the integer block is clocked only when valid data is in the data queue and is ready for operation. This holds power consumption of the device to the absolute minimum.

The core is integrated with MMUs as well as instruction and data caches. Each MMU provides a 32-entry, fully associative instruction and data TLB, with multiple page sizes of 4, 16, 512, and 256 Kbytes and 8 Mbytes. It supports 16 virtual address spaces with 8 protection groups. Three special scratch registers support software table search and update operations.

The instruction cache is four-way, set associative with physical addressing. It allows single-cycle access on hits with no added latency for misses. It has four words per block, supporting a four-beat burst line fill using an LRU (least recently used) replacement algorithm. The cache can be locked on a per cache block basis for application-critical routines.

The data cache is two-way, set associative with physical addressing. It allows single-cycle accesses on hits with one added clock latency for misses. It has four words per cache block, supporting burst line fill using LRU replacement. The cache can be locked on a per block basis for application critical routines. The data cache can be programmed through the MMU to support copy-back or write-through. Cache-inhibit mode can be programmed per MMU page.

The debug interface provides debug capabilities without degrading operation speed. This interface supports six watchpoint pins that are used to detect software events. Four of its eight internal comparators operate on the effective address on the address bus, two operate on the effective address on the data address bus, and two operate on the data bus. The core can make =, , <, and > comparisons to generate watchpoints. Each watchpoint can then generate a break point that can be configured to trigger in a programmable number of events.

## 1.3 System Interface Unit (SIU)

The SIU on the MPC857T/857DSL integrates general-purpose features useful in almost any 32-bit processor system. Dynamic bus sizing allows 8-, 16-, and 32-bit peripherals and memory to exist in the 32-bit system bus mode.

The SIU also provides power management functions, reset control, decrementer, timebase and the real-time clock.

The memory controller supports up to eight memory banks with glueless interfaces to DRAM, SRAM, SSRAM, EPROM, Flash EPROM, SDRAM, EDO, and other peripherals with 2-clock-cycle access to external SRAM and bursting support. It provides variable block sizes from 32 Kbytes to 256 Mbytes. The memory controller provides 0–30 wait states for each memory bank and can use address type matching to qualify each memory

**PCMCIA** Controller

bank access. It provides four byte-enable signals, an output-enable signal and a boot chip select available at reset.

The DRAM interface supports port sizes of 8, 16, and 32 bits. Memory banks can be defined in depths of 256 or 512 Kbytes or 1, 2, 4, 8, 16, 32, or 64 Mbytes for all port sizes. The memory depth can be 64 and 128 Kbytes for 8-bit memory or 128 and 256 Mbytes for 32-bit memory. The DRAM controller supports page-mode access for successive transfers within bursts. The MPC857T/857DSL supports a glueless interface to one bank of DRAM while external buffers are required for additional memory banks. The refresh unit provides  $\overline{\text{CAS}}$  before  $\overline{\text{RAS}}$ , a programmable refresh timer, refresh active during external reset, disable refresh mode, and stacking up to 7 refresh cycles. The DRAM interface uses a programmable state machine to support almost any memory interface.

### 1.4 PCMCIA Controller

The PCMCIA interface is a master (socket) controller and is compliant with release 2.1. The interface supports up to two independent PCMCIA sockets requiring only external transceivers/buffers. The interface provides eight memory or I/O windows where each window can be allocated to a particular socket. If only one PCMCIA port is used, the unused port may be used as general-purpose input with interrupt capability. On the MPC857DSL, PCMCIA support is provided on Port B only.

### 1.5 Power Management

The MPC857T/857DSL supports a wide range of power management features including full on, doze, sleep, deep sleep, and low power stop.

- Full on mode leaves the MPC857T/857DSL processor fully powered with all internal units operating at the full processor speed. A gear mode is determined by a clock divider, allowing the operating system to reduce the processor's operational frequency.

- Doze mode disables core functional units other than the time base decrementer, PLL, memory controller, RTC, and places the CPM in low-power standby mode.

- Sleep mode disables everything except the RTC and PIT, leaving the PLL active for quick wake-up.

- Deep sleep mode disables the PLL for lower power but slower wake-up.

- Low-power stop disables all logic in the processor except the minimum logic required to restart the device, providing the lowest power consumption but requiring the longest wake-up time.

**Communications Processor Module (CPM)**

#### 1.6 **Communications Processor Module (CPM)**

The MPC857T/857DSL is the next generation MPC8xx family of devices. Like its predecessor it implements a dual-processor architecture, which provides both a high-performance, general-purpose processor for application programming use as well as a special-purpose communication processor (CPM) uniquely designed for communications applications.

The CPM contains features that, like its predecessor, allow the MPC857T/857DSL to excel in communications and networking products. These features are grouped as follows:

- Communications processor (CP)

- Ten serial DMA (SDMA) controllers on the MPC857T; eight serial DMA (SDMA) controllers on the MPC857DSL

- Four general-purpose timers

- Two independent DMA channels

The CP provides the communication features of the MPC857T/857DSL. Included are a RISC processor, one serial communication controller (SCC1), two serial management controllers (SMCs) on the MPC857T and one SMC, SMC1 on the MPC857DSL, a serial peripheral interface (SPI), an I<sup>2</sup>C interface, 8 Kbytes of dual-port RAM, an interrupt controller, a time-slot assigner, three parallel ports, a parallel interface port, four independent baud rate generators, and ten serial DMA channels to support the SCC, SMC(s), SPI, and  $I^2C$ .

The SDMAs provide two channels of general-purpose DMA capability for each communications channel. They offer high-speed transfers, 32-bit data movement, buffer chaining, and independent request and acknowledge logic.

The four general-purpose timers on the CPM are identical to the timers found on all of the MPC8xx devices, and supporting the internal cascading of two timers to form a 32-bit timer.

### 1.7 Applications

The MPC857T/857DSL can be used as an adaptable ATM controller suited for a variety of applications, including the following:

- xDSL modems

- Cable modems

- Remote access routers

- Integrated access devices (IAD)

- Residential gateways

# Freescale Semiconductor, Inc. Differences between the MPC857T and the MPC857DSL

#### 1.8 Differences between the MPC857T and the MPC857DSL

#### MPC857T

All functionality described in this document applies to the MPC857T including 10/100 Ethernet, ATM, UTOPIA Level 2 Multi-PHY, and multi-channel HDLC support

#### MPC857DSL

- No TSA

- SCC1 only supports Ethernet

- One SMC (SMC1) for UART

- One PCMCIA socket (Port B)

- Supports up to 4 UTOPIA Level 2 PHYs

- UTOPIA slave mode not available

#### **Revision History** 1.9

**Table 1-1. Document Revision History**

| Revision | Date   | Change                                                                 |

|----------|--------|------------------------------------------------------------------------|

| 0        | 1/2002 | Original release                                                       |

| 0.1      | 6/2002 | Corrected MPC857DSL verbiage, it contains SMC1 and not SMC2            |

| 1        | 7/2002 | Updated for Rev A/B devices, fully incorporated verbiage for MPC857DSL |

**Revision History**

#### **HOW TO REACH US:**

#### **USA/EUROPE/LOCATIONS NOT LISTED:**

Motorola Literature Distribution P.O. Box 5405, Denver, Colorado 80217 1-303-675-2140 or 1-800-441-2447

#### JAPAN:

Motorola Japan Ltd. SPS, Technical Information Center 3-20-1, Minami-Azabu Minato-ku Tokyo 106-8573 Japan 81-3-3440-3569

#### ASIA/PACIFIC:

Motorola Semiconductors H.K. Ltd. Silicon Harbour Centre, 2 Dai King Street Tai Po Industrial Estate, Tai Po, N.T., Hong Kong 852-26668334

#### **TECHNICAL INFORMATION CENTER:**

1-800-521-6274

#### **HOME PAGE:**

http://www.motorola.com/semiconductors

#### **DOCUMENT COMMENTS:**

FAX (512) 933-2625 Attn: RISC Applications Engineering Information in this document is provided solely to enable system and software implementers to use Motorola products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Motorola data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part.

Motorola and the Stylized M Logo are registered in the U.S. Patent and Trademark Office. digital dna is a trademark of Motorola, Inc. All other product or service names are the property of their respective owners. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

© Motorola, Inc. 2002

MPC857TTS/D