# SJA1124 - SPI TO QUAD-LIN BRIDGE

By decoupling MCU selection from the number of LIN channels, the SJA1124 SPI to Quad-LIN bridge offers unprecedented cost and board space savings in multichannel LIN applications.

# **GENERAL DESCRIPTION**

The SJA1124 is an SPI to Quad-LIN Bridge incorporating four LIN commander channels. Each LIN commander channel contains a LIN controller and LIN transceiver with commander termination.

LIN data communication is accomplished via SPI. The SJA1124 converts the transmit data stream received on the SPI input into LIN commander frames on the LIN bus. The data stream received on the LIN bus can be read via SPI. The SPI replaces the UART-related TXD and RXD pins on the MCU. A complete LIN frame can be transmitted in one single SPI operation.

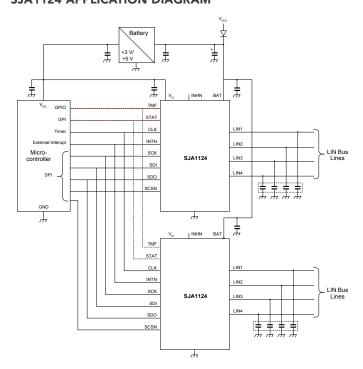

The on-chip LIN controllers allow the use of smaller mainstream low-pin-count MCUs. Performance becomes the primary selection criteria, rather than the number of LIN communication channels. Decoupling the MCU from the channel count not only allows it to be tailored to performance requirements, it also enhances scalability. Adding four additional LIN channels with a second SJA1124 bridge requires only an additional chip select pin on the MCU.

The SJA1124 is ideally suited to multi-LIN commander applications, such as body control and ambient mood lighting. The integrated commander termination further reduces the BOM and board space requirements.

## **APPLICATIONS**

- Body control

- HVAC

- Ambient mood lighting

- Park assist

# **SJA1124 APPLICATION DIAGRAM**

### **KEY FEATURES**

### General

- ISO 17987 (LIN2.x)/SAE J2602 compliant LIN commander controller and LIN transceiver

- Serial peripheral interface (SPI) for LIN data transfer, configuration, control and diagnosis

- Synchronous LIN frame transmission across multiple SJA1124 bridge devices

- Interrupt output with configurable interrupt sources

- Leadless DHVQFN24 package (3.5 x 5.5 mm)

# LIN commander controller

- ullet AUTOSAR $^{\text{\tiny{TM}}}$  compatible

- Baud rate, operating mode, status and interrupt processing configurable per LIN channel

- Complete LIN message handling

- One interrupt per LIN message

An overview of NXP's multi-LIN transceiver portfolio is given in the table below.

## NXP MULTI-LIN TRANSCEIVER PORTFOLIO

| Function / Feature                                 | TJA1022                      | TJA1024                          | TJA1124                          | SJA1124                          |

|----------------------------------------------------|------------------------------|----------------------------------|----------------------------------|----------------------------------|

| # LIN channels                                     | 2                            | 4                                | 4                                | 4                                |

| ISO 17897 (LIN 2.x) /<br>SAE-J2602 compliancy      | 1                            | 1                                | 1                                | 1                                |

| Commander termination (resistor + diode)           | x                            | x                                | 1                                | ✓                                |

| SPI to LIN bridge<br>(replacing TxD / RxD<br>pins) | х                            | x                                | x                                | <b>✓</b>                         |

| High-speed LIN                                     | ×                            | ×                                | ×                                | 100 kBd                          |

| Microntroller interface                            | 3V3 and 5 V                  | 3V3 and 5 V                      | 3V3 and 5 V                      | 3V3 and 5 V                      |

| INHN                                               | ×                            | ×                                | 1                                | 1                                |

| TxD dominant time-out function                     | 1                            | 1                                | 1                                | 1                                |

| Wake-up source recognition                         | 1                            | 1                                | 1                                | 1                                |

| Battery supply voltage range                       | 5 V - 18 V                   | 5 V - 18 V                       | 5 V - 28 V                       | 5 V - 28 V                       |

| Max. voltage pins BAT and LIN                      | + 42 V                       | + 42 V                           | + 43 V                           | + 43 V                           |

| ESD (pin LIN)                                      |                              |                                  |                                  |                                  |

| Human body model                                   | ± 8 kV                       | ± 8 kV                           | ± 6 kV                           | ± 6 kV                           |

| According to IEC61000-<br>4-2                      | ± 6 kV                       | ± 6 kV                           | ± 6 kV                           | ± 6 kV                           |

| Package (supporting<br>AOI)                        | HVSON14 (3.0<br>mm x 4.5 mm) | DHVQFN24<br>(3.5 mm x 5.5<br>mm) | DHVQFN24<br>(3.5 mm x 5.5<br>mm) | DHVQFN24<br>(3.5 mm x 5.5<br>mm) |

|                                                    | SO14 (3.9 mm x<br>8.65 mm)   |                                  |                                  |                                  |

# SJA1124 - SPI TO QUAD-LIN BRIDGE

# TJA1029 in SO8 TJA1024 in DHVQFN24 SJA1124 in DHVQFN24 PC Pin Count Reduction PCB Area and BOM Reduction

### www.nxp.com

NXP, the NXP logo and NXP SECURE CONNECTIONS FOR A SMARTER WORLD are trademarks of NXP B.V. All other product or service names are the property of their respective owners. © 2022 NXP B.V.