## MPC7457 Host Processor Built on Power Architecture™ Technology

The MPC7457 host processor built on Power Architecture<sup>™</sup> technology is a high-performance, low-power 32-bit implementation of the RISC architecture with a full 128-bit implementation of Freescale's AltiVec™ technology. AltiVec technology allows designers to leverage existing code and add AltiVec performance as market and customers' requirements change-helping speed time to market and increase system performance without upgrading hardware. The MPC7457 is ideal for embedded applications in the wired and wireless telecommunications, networking and imaging arenas, computing, embedded network control and signal processing applications. Designed as a pin-compatible replacement for Freescale's MPC7455 device, the MPC7457 reaches speeds upto 1.3 GHz with 512 KB of on-chip L2 cache and up to 2 MB of backside L3 cache. The device benefits from Freescale's silicon-on-insulator (SOI) process technology, engineered to help deliver tremendous power savings without sacrificing speed. A lower power version of the MPC7457 is available, operating at speeds of up to 1 GHz with a core voltage of 1.1V.

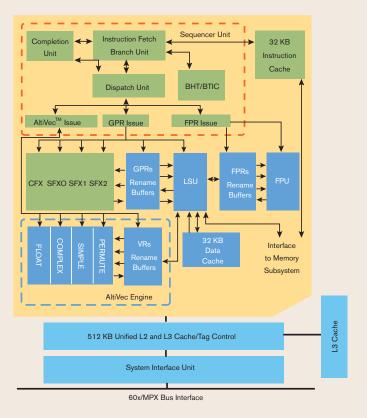

MPC7457 BLOCK DIAGRAM

|                           | MPC7457                                                        | MPC7457<br>Low-Power Version                                  |

|---------------------------|----------------------------------------------------------------|---------------------------------------------------------------|

| CPU Speeds (internal)     | Up to 1.3 GHz                                                  | Up to 1 GHz                                                   |

| Bus Frequency             | 133/166 MHz                                                    | 133/166 MHz                                                   |

| Bus Interface             | 64-bit                                                         | 64-bit                                                        |

| Bus Protocol              | MPX/60x                                                        | MPX/60x                                                       |

| Instructions per Clock    | 4 (3 + Branch)                                                 | 4 (3 + Branch)                                                |

| Integrated L1 Cache       | 32 KB Instruction<br>32 KB Data                                | 32 KB Instruction<br>32 KB Data                               |

| Integrated L2 Cache       | 512 KB                                                         | 512 KB                                                        |

| L3 Cache Support          | 1 or 2 MB                                                      | 1 or 2 MB                                                     |

| Typical Power Consumption | 18.3 W @ 1267 MHz                                              | 8.3 W @ 1 GHz                                                 |

| Package                   | 483 CBGA                                                       | 483 CBGA                                                      |

| Process                   | 0.13μ 9LM CMOS with SOI                                        | 0.13μ 9LM CMOS with SOI                                       |

| Voltage                   | 1.3V Internal, 1.8/2.5V I/O                                    | 1.1V Internal, 1.8/2.5V I/O                                   |

| Performance (est.)        | 3000 Dhrystone 2.1 MIPS @ 1.3 GHz                              | 2310 Dhrystone 2.1 MIPS @ 1 GHz                               |

| Execution Units           | Integer(4), Floating-Point, AltiVec™(4),<br>Branch, Load/Store | Integer(4), Floating-Point, AltiVec(4),<br>Branch, Load/Store |

MPC7457 microprocessors feature a high-frequency superscalar e600 core, capable of issuing four instructions per clock cycle (three instructions + branch) into 11 independent execution units:

- > Four integer units (three simple + one complex)

- > Double-precision floating point unit

- > Four AltiVec units (simple, complex, floating and permute)

- > Load/store unit

- > Branch processing unit

## **Compatibility and Support**

- > The MPC7457 processor is pin for pin compatible with the MPC7455 processor.

- > As with all microprocessors built on Power Architecture technology, the MPC7457 is software compatible with the MPC7xx family of processors from Freescale.

- Microprocessors built on Power Architecture technology enjoy support from a broad suite of operating systems, compilers and development tools from Freescale and members of its Design Alliance Program.

## **Embedded Enhancements**

The MPC7457 offers eight instruction BAT and data BAT registers to help support lightweight embedded operating systems, enabling more large tables of data. The processors also provide cache locking to the L1 caches so that key performance algorithms and code can be locked in the L1 cache.

Learn More: For more information about Freescale products, please visit www.freescale.com.