Freescale Semiconductor Errata

Document Number: MPC860CE Rev. 1.9, 05/2008

# MPC860/855T Family Device Errata Reference

This document is a compilation of all MPC855T, MPC860, MPC860SAR, and MPC860T device errata from Revision A.2 forward. Herein, the errata are classified and numbered, and each erratum is provided with a description and workarounds in the second part of the document. To determine which silicon revision and mask set are associated with which version, please refer to Table 2. To find which errata apply to a particular device, please refer to the errata listings for each revision provided in Table 4. Indications of schedules for errata fixes are provided in the errata listing of the latest revision of each part.

Table 1 provides a revision history for this document.

| Table 1 | Document | Revision | History |

|---------|----------|----------|---------|

|---------|----------|----------|---------|

| Rev. No. | Date   | Significant Change(s)                                                                              |

|----------|--------|----------------------------------------------------------------------------------------------------|

| 1.9      | 5/2008 | Added ATM 11 errata information for D4 to Table 3. Replaced MPC860CESUMM_Rev1_7.doc with this one. |

Table 2. MPC860CE Silicon Revision, Mask Set, and Version Key

| Silicon<br>Revision | Mask Set | 855T | 860 | 860DC        | 860DE        | 860DH        | 860DP | 860DT | 860EN        | 860MH        | 860P | 860SR | 860T |

|---------------------|----------|------|-----|--------------|--------------|--------------|-------|-------|--------------|--------------|------|-------|------|

| A.2                 | 2F84C    |      |     | $\checkmark$ | $\checkmark$ | $\checkmark$ |       |       | $\checkmark$ | $\checkmark$ |      |       |      |

| A.3                 | 4F84C    |      |     | $\checkmark$ | $\checkmark$ | $\checkmark$ |       |       | $\checkmark$ | $\checkmark$ |      |       |      |

© Freescale Semiconductor, Inc., 2008. All rights reserved.

| Silicon<br>Revision | Mask Set         | 855T | 860          | 860DC        | 860DE        | 860DH        | 860DP        | 860DT        | 860EN        | 860MH        | 860P | 860SR        | 860T         |

|---------------------|------------------|------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|------|--------------|--------------|

| B.1                 | 1J24A,<br>0H86G  |      |              |              |              |              |              |              |              |              |      | $\checkmark$ |              |

|                     | 2J24A,<br>9J24A  |      | $\checkmark$ | V            | V            | V            |              |              | V            | V            |      |              |              |

| B.2                 | 2H56S            |      |              |              |              |              |              | $\checkmark$ |              |              |      |              | $\checkmark$ |

| B.3                 | 1J21M            |      |              |              |              |              |              | $\checkmark$ |              |              |      |              | $\checkmark$ |

| B.5                 | 3J21M            |      |              |              |              |              |              | $\checkmark$ |              |              |      |              | $\checkmark$ |

| C.0                 | 0H96G            |      |              |              |              |              |              |              |              |              |      | $\checkmark$ |              |

|                     | 1H96G            |      | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |              |              | $\checkmark$ | $\checkmark$ |      |              |              |

| C.1                 | 2H96G            |      |              |              |              |              |              |              |              |              |      | $\checkmark$ |              |

|                     | 3H96G            |      | $\checkmark$ |              | $\checkmark$ | $\checkmark$ |              |              | $\checkmark$ | $\checkmark$ |      |              |              |

| D.4 (D.3)           | 3K20A<br>(2K20A) |      |              |              | V            |              | $\checkmark$ | $\checkmark$ | $\checkmark$ |              |      | $\checkmark$ | V            |

Table 2. MPC860CE Silicon Revision, Mask Set, and Version Key (continued)

#### Table 3. MPC860CE Errata and Silicon Revision Key

| Erratum | A.2          | A.3          | B.1          | B.1<br>(860SR<br>only) | B.2          | В.3          | B.5          | C.0          | C.0<br>(860SR<br>only) | C.1          | C.1<br>(860SR<br>only) | D.4<br>(D.3) | Workaround |

|---------|--------------|--------------|--------------|------------------------|--------------|--------------|--------------|--------------|------------------------|--------------|------------------------|--------------|------------|

| GLL1    | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$           | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$           | $\checkmark$ | $\checkmark$           | $\checkmark$ | Y          |

| SIU1    | $\checkmark$ |              |              |                        |              |              |              |              |                        |              |                        |              | Ν          |

| SIU2    | $\checkmark$ | $\checkmark$ |              |                        |              |              |              |              |                        |              |                        |              | Y          |

| SIU3    | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$           | $\checkmark$ | $\checkmark$ | $\checkmark$ |              |                        |              |                        |              | Y          |

| SIU4    | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$           | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$           | $\checkmark$ | $\checkmark$           | $\checkmark$ | Y          |

| SIU5    | $\checkmark$ | $\checkmark$ | $\checkmark$ |                        | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$           | $\checkmark$ | $\checkmark$           | $\checkmark$ | Y          |

| SIU6    | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$           | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$           | $\checkmark$ | $\checkmark$           | $\checkmark$ | Y          |

| SIU7    | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$           | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$           | $\checkmark$ | $\checkmark$           |              | Y          |

| SIU8    | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$           | $\checkmark$ | $\checkmark$ | $\checkmark$ |              |                        |              |                        |              | Y          |

| SIU9    | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$           | $\checkmark$ | $\checkmark$ | $\checkmark$ |              | $\checkmark$           | $\checkmark$ | $\checkmark$           |              | Y          |

| SIU10   | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$           | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$           | $\checkmark$ | $\checkmark$           | $\checkmark$ | Ν          |

| CPM1    | $\checkmark$ | $\checkmark$ |              |                        |              |              |              |              |                        |              |                        |              | Y          |

| CPM2    | $\checkmark$ | $\checkmark$ |              |                        |              |              |              |              |                        |              |                        |              | Y          |

| СРМЗ    | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$           | $\checkmark$ | $\checkmark$ | $\checkmark$ |              |                        |              |                        |              | Y          |

| CPM4    | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$           | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |                        | $\checkmark$ | $\checkmark$           |              | Y          |

|         |              |              |              |                        |              |              |              |              | nevisio                |              |                        | -            |            |

|---------|--------------|--------------|--------------|------------------------|--------------|--------------|--------------|--------------|------------------------|--------------|------------------------|--------------|------------|

| Erratum | A.2          | A.3          | B.1          | B.1<br>(860SR<br>only) | B.2          | В.3          | B.5          | C.0          | C.0<br>(860SR<br>only) | C.1          | C.1<br>(860SR<br>only) | D.4<br>(D.3) | Workaround |

| CPM5    | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$           | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$           | $\checkmark$ | $\checkmark$           |              | Y          |

| CPM6    | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$           | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$           | $\checkmark$ | $\checkmark$           |              | Y          |

| CPM7    | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$           | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$           | $\checkmark$ | $\checkmark$           |              | Y          |

| CPM8    | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$           | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$           | $\checkmark$ | $\checkmark$           |              | Ν          |

| CPM9    |              | $\checkmark$ | $\checkmark$ | $\checkmark$           | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$           | $\checkmark$ | $\checkmark$           |              | Ν          |

| CPM10   | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$           | $\checkmark$ | $\checkmark$ |              | $\checkmark$ | $\checkmark$           | $\checkmark$ | $\checkmark$           |              | Ν          |

| CPM11   |              | $\checkmark$ | $\checkmark$ | $\checkmark$           | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$           | $\checkmark$ | $\checkmark$           |              | Y          |

| CPM12   |              |              |              |                        |              |              |              |              |                        |              |                        | $\checkmark$ | Y          |

| G1      | $\checkmark$ | $\checkmark$ |              |                        |              |              |              |              |                        |              |                        |              | Y          |

| G2      | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$           | $\checkmark$ | $\checkmark$ |              | $\checkmark$ | $\checkmark$           | $\checkmark$ | $\checkmark$           | $\checkmark$ | Y          |

| G3      |              | $\checkmark$ | $\checkmark$ | $\checkmark$           | $\checkmark$ | $\checkmark$ | $\checkmark$ |              |                        |              |                        |              | Y          |

| G4      |              | $\checkmark$ |              | $\checkmark$           | $\checkmark$ | $\checkmark$ |              |              |                        |              |                        |              | Y          |

| G5      |              |              | $\checkmark$ | $\checkmark$           | $\checkmark$ | $\checkmark$ |              |              |                        |              |                        |              | Y          |

| G6      |              |              | $\checkmark$ | $\checkmark$           | $\checkmark$ | $\checkmark$ |              |              |                        |              |                        |              | Y          |

| G7      |              |              | $\checkmark$ | $\checkmark$           |              |              |              |              |                        |              |                        |              | Y          |

| G8      |              |              |              |                        |              |              |              | $\checkmark$ | $\checkmark$           | $\checkmark$ | $\checkmark$           |              | Y          |

| G9      | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$           | $\checkmark$ | $\checkmark$ |              | $\checkmark$ | $\checkmark$           | $\checkmark$ | $\checkmark$           | $\checkmark$ | Y          |

| G10     |              |              |              |                        |              |              |              |              |                        |              |                        | $\checkmark$ | Ν          |

| CPU1    |              | $\checkmark$ | $\checkmark$ | $\checkmark$           | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$           | $\checkmark$ | $\checkmark$           |              | Ν          |

| CPU2    |              |              | $\checkmark$ | $\checkmark$           |              |              |              |              |                        |              |                        |              | Ν          |

| CPU3    |              | $\checkmark$ |              |                        |              |              |              |              |                        |              |                        |              | Y          |

| CPU4    |              |              |              |                        |              |              |              |              |                        |              |                        |              | Ν          |

| CPU5    | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$           | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$           | $\checkmark$ | $\checkmark$           | $\checkmark$ | Y          |

| CPU6    | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$           | $\checkmark$ | $\checkmark$ | $\checkmark$ |              |                        |              |                        |              | Y          |

| CPU7    | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$           | $\checkmark$ | $\checkmark$ |              | $\checkmark$ | $\checkmark$           |              |                        |              | Y          |

| CPU8    | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$           | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$           |              |                        |              | Y          |

| CPU9    |              |              |              |                        |              |              |              |              |                        | $\checkmark$ | $\checkmark$           |              | Y          |

| CPU10   | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$           | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$           | $\checkmark$ | $\checkmark$           | $\checkmark$ | Y          |

| CPU11   | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$           | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |                        | $\checkmark$ | $\checkmark$           | $\checkmark$ | Y          |

| CPU12   | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$           | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |                        | $\checkmark$ | $\checkmark$           | $\checkmark$ | Y          |

| CPU13   |              | $\checkmark$ | $\checkmark$ | $\checkmark$           | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$           | $\checkmark$ | $\checkmark$           | $\checkmark$ | Y          |

Table 3. MPC860CE Errata and Silicon Revision Key (continued)

|         |              |              |              | B.1          |              |              |              |              | C.0             |              | C.1          |              |            |

|---------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|-----------------|--------------|--------------|--------------|------------|

| Erratum | A.2          | A.3          | B.1          |              | B.2          | B.3          | B.5          | C.0          | (860SR<br>only) | C.1          |              | D.4<br>(D.3) | Workaround |

| CPU14   | $\checkmark$    | $\checkmark$ | $\checkmark$ | $\checkmark$ | Y          |

| CPU15   | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |              | $\checkmark$ | $\checkmark$    | $\checkmark$ | $\checkmark$ | $\checkmark$ | Y          |

| ATM1    |              |              |              | $\checkmark$ |              |              |              |              |                 |              |              |              | Y          |

| ATM2    |              |              |              | $\checkmark$ |              |              |              |              |                 |              |              |              | Y          |

| ATM3    |              |              |              | $\checkmark$ |              |              |              |              |                 |              |              |              | Y          |

| ATM4    |              |              |              | $\checkmark$ |              |              |              |              |                 |              |              |              | Y          |

| ATM5    |              |              |              | $\checkmark$ |              |              |              |              | $\checkmark$    |              | $\checkmark$ | $\checkmark$ | Y          |

| ATM6    |              |              |              | $\checkmark$ |              |              |              |              |                 |              |              |              | Y          |

| ATM7    |              |              |              | $\checkmark$ |              |              |              |              | $\checkmark$    |              | $\checkmark$ |              | Y          |

| ATM8    |              |              |              | $\checkmark$ |              |              |              |              | $\checkmark$    |              | $\checkmark$ |              | Y          |

| ATM9    |              |              |              | $\checkmark$ |              |              |              |              | $\checkmark$    |              | $\checkmark$ |              | Y          |

| ATM10   |              |              |              | $\checkmark$ |              |              |              |              | $\checkmark$    |              | $\checkmark$ | $\checkmark$ | Y          |

| ATM11   |              |              |              | $\checkmark$ |              |              |              |              | $\checkmark$    |              | $\checkmark$ | $\checkmark$ | Y          |

| FEC1    |              |              |              |              | $\checkmark$ | $\checkmark$ |              |              |                 |              |              |              | Ν          |

| FEC2    |              |              |              |              | $\checkmark$ | $\checkmark$ | $\checkmark$ |              |                 |              |              |              | Y          |

| FEC3    |              |              |              |              | $\checkmark$ | $\checkmark$ | $\checkmark$ |              |                 |              |              | $\checkmark$ | Ν          |

| FEC4    |              |              |              |              | $\checkmark$ |              |              |              |                 |              |              |              | Ν          |

| FEC5    |              |              |              |              | $\checkmark$ | $\checkmark$ | $\checkmark$ |              |                 |              |              |              | Ν          |

| FEC6    |              |              |              |              | $\checkmark$ | $\checkmark$ | $\checkmark$ |              |                 |              |              |              | Ν          |

| FEC7    |              |              |              |              | $\checkmark$ | $\checkmark$ | $\checkmark$ |              |                 |              |              |              | Ν          |

| FEC8    |              |              |              |              | $\checkmark$ |              |              |              |                 |              |              |              | Y          |

| FEC9    |              |              |              |              | $\checkmark$ |              |              |              |                 |              |              |              | Y          |

| FEC10   |              |              |              |              | $\checkmark$ |              |              |              |                 |              |              |              | Y          |

| FEC11   |              |              |              |              | $\checkmark$ | $\checkmark$ | $\checkmark$ |              |                 |              |              |              | Ν          |

| FEC12   |              |              |              |              | $\checkmark$ | $\checkmark$ | $\checkmark$ |              |                 |              |              | $\checkmark$ | Y          |

| FEC13   |              |              |              |              | $\checkmark$ | $\checkmark$ | $\checkmark$ |              |                 |              |              |              | Ν          |

| FEC14   |              |              |              |              | $\checkmark$ | $\checkmark$ |              |              |                 |              |              |              | Y          |

| FEC15   |              |              |              |              | $\checkmark$ | $\checkmark$ | $\checkmark$ |              |                 |              |              | $\checkmark$ | Y          |

Table 3. MPC860CE Errata and Silicon Revision Key (continued)

# **Errata List**

# **Global Errata**

# GLL1 Some registers are not initialized correctly during power-on RESET, HRESET, and SRESET

Table 4 is provided to clarify/correct the power-on  $\overline{\text{RESET}}$  value of many registers and lists whether each register is affected by  $\overline{\text{HRESET}}$  and/or  $\overline{\text{SRESET}}$ . The table applies to the MPC850, the MPC855T, the MPC857T, the MPC860, and the MPC862.

| Register | Value at Power-On RESET | Affected by HRESET | Affected by SRESET |

|----------|-------------------------|--------------------|--------------------|

| SIUMCR   | 01200000                | Yes                | No                 |

| SYPCR    | FFFFF07                 | Yes                | No                 |

| SWSR     | 0                       | Yes                | Yes                |

| SIPEND   | 0000xxxx                | Yes                | Yes                |

| SIMASK   | 0000xxxx                | Yes                | Yes                |

| SIEL     | 0000xxxx                | Yes                | No                 |

| SIVEC    | (xx11)(11xx)xxxxxx      | Yes                | Yes                |

| TESR     | XXXX0000                | Yes                | Yes                |

| SDCR     | 0                       | Yes                | No                 |

| PBR0     | x                       | No                 | No                 |

| POR0     | x                       | No                 | No                 |

| PBR1     | x                       | No                 | No                 |

| POR1     | x                       | No                 | No                 |

| PBR2     | x                       | No                 | No                 |

| POR2     | x                       | No                 | No                 |

| PBR3     | x                       | No                 | No                 |

| POR3     | x                       | No                 | No                 |

| PBR4     | x                       | No                 | No                 |

| POR4     | x                       | No                 | No                 |

| PBR5     | x                       | No                 | No                 |

| POR5     | x                       | No                 | No                 |

| PBR6     | x                       | No                 | No                 |

| POR6     | x                       | No                 | No                 |

| PBR7     | x                       | No                 | No                 |

| POR7     | x                       | No                 | No                 |

| PGCRA    | 0                       | Yes                | No                 |

| PGCRB    | 0                       | Yes                | No                 |

| PSCR     | x                       | No                 | No                 |

| PIPR     | ??00??00                | Yes                | Yes                |

| PER      | 0                       | Yes                | Yes                |

| BR0      | XXXXX(??00)0(000?)      | Yes                | No                 |

| OR0      | 00000FF4                | Yes                | No                 |

| BR1      | XXXXXX(xx00)0           | Yes                | No                 |

#### Table 4. Power-On Reset Value of the Registers

Global Errata

| Register | Value at Power-On RESET      | Affected by HRESET | Affected by SRESET |

|----------|------------------------------|--------------------|--------------------|

| OR1      | XXXXXXX(xxx0)                | Yes                | No                 |

| BR2      | XXXXXX(xx00)0                | Yes                | No                 |

| OR2      | XXXXXXX(xxx0)                | Yes                | No                 |

| BR3      | XXXXXX(xx00)0                | Yes                | No                 |

| OR3      | XXXXXXX(xxx0)                | Yes                | No                 |

| BR4      | XXXXXX(xx00)0                | Yes                | No                 |

| OR4      | XXXXXXX(xxx0)                | Yes                | No                 |

| BR5      | XXXXXX(xx00)0                | Yes                | No                 |

| OR5      | XXXXXXX(xxx0)                | Yes                | No                 |

| BR6      | XXXXXX(xx00)0                | Yes                | No                 |

| OR6      | XXXXXXX(xxx0)                | Yes                | No                 |

| BR7      | XXXXXX(xx00)0                | Yes                | No                 |

| OR7      | XXXXXXX(xxx0)                | Yes                | No                 |

| MAR      | x                            | No                 | No                 |

| MCR      | (xx00)0(x000)0(xxx0)X(00xx)X | Yes                | No                 |

| MAMR     | xx001000                     | Yes                | No                 |

| MBMR     | xx001000                     | Yes                | No                 |

| MSTAT    | 0                            | Yes                | No                 |

| MPTPR    | 0200                         | Yes                | No                 |

| MDR      | x                            | No                 | No                 |

| TBSCR    | 0                            | Yes                | No                 |

| TBREFA   | x                            | No                 | No                 |

| TBREFB   | x                            | No                 | No                 |

| RTCSC    | 00(000x)(000x)               | Yes                | Yes                |

| RTC      | x                            | No                 | Yes                |

| RTSEC    | x                            | No                 | Yes                |

| RTCAL    | x                            | No                 | No                 |

| PISCR    | 0                            | Yes                | No                 |

| PITC     | x                            | No                 | No                 |

| PITR     | x                            | N/A                | N/A                |

| SCCR     | 0(000?)(?000)(0??0)0000      | Yes                | No                 |

| PLPRCR   | ???0(0100)000                | Yes                | Yes                |

| RSR      | 0                            | Yes                | Yes                |

| TBSCRK   | x                            | Yes                | Yes                |

| TBREFAK  | x                            | Yes                | Yes                |

| TBREFBK  | x                            | Yes                | Yes                |

| ТВК      | x                            | Yes                | Yes                |

| RTCSCK   | x                            | Yes                | Yes                |

| RTCK     | x                            | Yes                | Yes                |

| RTSECK   | x                            | Yes                | Yes                |

| RTCALK   | x                            | Yes                | Yes                |

| PISCRK   | x                            | Yes                | Yes                |

| PITCK    | x                            | Yes                | Yes                |

| SCCRK    | x                            | Yes                | Yes                |

| PLPRCRK  | x                            | Yes                | Yes                |

| RSRK     | x                            | Yes                | Yes                |

## Table 4. Power-On Reset Value of the Registers (continued)

\_\_\_\_\_

| Register | Value at Power-On RESET | Affected by HRESET | Affected by SRESET |

|----------|-------------------------|--------------------|--------------------|

| I2MOD    | 0                       | Yes                | Yes                |

| I2ADD    | x                       | No                 | No                 |

| I2BRG    | FFFF                    | Yes                | No                 |

| I2COM    | 0                       | Yes                | Yes                |

| I2CER    | 0                       | Yes                | Yes                |

| I2CMR    | 0                       | Yes                | Yes                |

| SDAR     | x                       | No                 | No                 |

| SDSR     | 0                       | Yes                | Yes                |

| SDMR     | 0                       | Yes                | Yes                |

| IDSR1    | 0                       | Yes                | Yes                |

| IDMR1    | 0                       | Yes                | Yes                |

| IDSR2    | 0                       | Yes                | Yes                |

| IDMR2    | 0                       | Yes                | Yes                |

| CIVR     | 0                       | Yes                | Yes                |

| CICR     | 0                       | Yes                | No                 |

| CIPR     | 0                       | Yes                | Yes                |

| CIMR     | 0                       | Yes                | Yes                |

| CISR     | 0                       | Yes                | Yes                |

| PADIR    | 0                       | Yes                | No                 |

| PAPAR    | 0                       | Yes                | No                 |

| PAODR    | 0                       | Yes                | No                 |

| PADAT    | x                       | No                 | No                 |

| PCDIR    | 0                       | Yes                | No                 |

| PCPAR    | 0                       | Yes                | No                 |

| PCSO     | 0                       | Yes                | No                 |

| PCDAT    | x                       | No                 | No                 |

| PCINT    | 0                       | Yes                | No                 |

| PDDIR    | 0                       | Yes                | No                 |

| PDPAR    | 0                       | Yes                | No                 |

| PDDAT    | x                       | No                 | No                 |

| TGCR     | 0                       | Yes                | Yes                |

| TMR1     | 0                       | Yes                | Yes                |

| TMR2     | 0                       | Yes                | Yes                |

| TRR1     | FFFF                    | Yes                | Yes                |

| TRR2     | FFFF                    | Yes                | Yes                |

| TCR1     | 0                       | Yes                | Yes                |

| TCR2     | 0                       | Yes                | Yes                |

| TCN1     | 0                       | Yes                | Yes                |

| TCN2     | 0                       | Yes                | Yes                |

| TMR3     | 0                       | Yes                | Yes                |

| TMR4     | 0                       | Yes                | Yes                |

| TRR3     | FFFF                    | Yes                | Yes                |

| TRR4     | FFFF                    | Yes                | Yes                |

| TCR3     | 0                       | Yes                | Yes                |

| TCR4     | 0                       | Yes                | Yes                |

| TCN3     | 0                       | Yes                | Yes                |

| Table 4. Power-On Reset Value of the Registers (continued | d) |

|-----------------------------------------------------------|----|

|-----------------------------------------------------------|----|

Global Errata

| Register | Value at Power-On RESET | Affected by HRESET | Affected by SRESET |

|----------|-------------------------|--------------------|--------------------|

| TCN4     | 0                       | Yes                | Yes                |

| TER1     | 0                       | Yes                | Yes                |

| TER2     | 0                       | Yes                | Yes                |

| TER3     | 0                       | Yes                | Yes                |

| TER4     | 0                       | Yes                | Yes                |

| CPCR     | 0                       | Yes                | Yes                |

| RCCR     | 0                       | Yes                | No                 |

| RCTR1    | NA                      | Yes                | Yes                |

| RCTR2    | NA                      | Yes                | Yes                |

| RCTR3    | NA                      | Yes                | Yes                |

| RCTR4    | NA                      | Yes                | Yes                |

| RTER     | 0                       | Yes                | Yes                |

| RTMR     | 0                       | Yes                | Yes                |

| BRGC1    | 0                       | Yes                | No                 |

| BRGC2    | 0                       | Yes                | No                 |

| BRGC3    | 0                       | Yes                | No                 |

| BRGC4    | 0                       | Yes                | No                 |

| GSMR_L1  | 0                       | Yes                | Yes                |

| GSMR_H1  | 0                       | Yes                | Yes                |

| PSMR1    | 0                       | Yes                | Yes                |

| TODR1    | 0                       | Yes                | Yes                |

| DSR1     | 7E7E                    | Yes                | Yes                |

| SCCE1    | 0                       | Yes                | Yes                |

| SCCM1    | 0                       | Yes                | Yes                |

| SCCS1    | 0                       | Yes                | Yes                |

| GSMR_L2  | 0                       | Yes                | Yes                |

| GSMR_H2  | 0                       | Yes                | Yes                |

| PSMR2    | 0                       | Yes                | Yes                |

| TODR2    | 0                       | Yes                | Yes                |

| DSR2     | 7E7E                    | Yes                | Yes                |

| SCCE2    | 0                       | Yes                | Yes                |

| SCCM2    | 0                       | Yes                | Yes                |

| SCCS2    | 0                       | Yes                | Yes                |

| GSMR_L3  | 0                       | Yes                | Yes                |

| GSMR_H3  | 0                       | Yes                | Yes                |

| PSMR3    | 0                       | Yes                | Yes                |

| TODR3    | 0                       | Yes                | Yes                |

| DSR3     | 7E7E                    | Yes                | Yes                |

| SCCE3    | 0                       | Yes                | Yes                |

| SCCM3    | 0                       | Yes                | Yes                |

| SCCS3    | 0                       | Yes                | Yes                |

| GSMR_L4  | 0                       | Yes                | Yes                |

| GSMR_H4  | 0                       | Yes                | Yes                |

| PSMR4    | 0                       | Yes                | Yes                |

| TODR4    | 0                       | Yes                | Yes                |

| DSR4     | 7E7E                    | Yes                | Yes                |

## Table 4. Power-On Reset Value of the Registers (continued)

| Register | Value at Power-On RESET | Affected by HRESET | Affected by SRESET |

|----------|-------------------------|--------------------|--------------------|

| SCCE4    | 0                       | Yes                | Yes                |

| SCCM4    | 0                       | Yes                | Yes                |

| SCCS4    | 0                       | Yes                | Yes                |

| SMCMR1   | 0                       | Yes                | Yes                |

| SMCE1    | 0                       | Yes                | Yes                |

| SMCM1    | 0                       | Yes                | Yes                |

| SMCMR2   | 0                       | Yes                | Yes                |

| SMCE2    | 0                       | Yes                | Yes                |

| SMCM2    | 0                       | Yes                | Yes                |

| SPMODE   | 0                       | Yes                | Yes                |

| SPIE     | 0                       | Yes                | Yes                |

| SPIM     | 0                       | Yes                | Yes                |

| SPCOM    | 0                       | Yes                | Yes                |

| PIPC     | 0                       | Yes                | No                 |

| PTPR     | 0                       | Yes                | No                 |

| PBDIR    | xxx(xx00)0000           | Yes                | No                 |

| PBPAR    | xxx(xx00)0000           | Yes                | No                 |

| PBODR    | 0                       | Yes                | No                 |

| PBDAT    | x                       | Yes                | Yes                |

| SIMODE   | 0                       | Yes                | Yes                |

| SIGMR    | 0                       | Yes                | No                 |

| SISTR    | 0                       | Yes                | No                 |

| SICMR    | 0                       | Yes                | Yes                |

| SICR     | 0                       | Yes                | No                 |

| SIRP     | 0                       | Yes                | Yes                |

Table 4. Power-On Reset Value of the Registers (continued)

Legend:

x or X = "don't care" in either bits, nibbles, or the entire register.

0 = a single zero indicates the entire register is reset to zeros.

() = isolates bits of a nibble of the register.

? = a don't care for POR, but if this register is affected by HRESET or SRESET, indicates that the value will remain the same as what it was before the reset occurred.

NA = Not Applicable, indicates that this register has no POR value.

# SIU Errata

# SIU1 CLKOUT signal drive

## **Description:**

The MPC860's capability to change the strength of the output buffer drive of CLKOUT is not functional. The strength of the output buffer can be modified between the following two states:

- Full strength—COM = 00 or COM = 01 in the SCCR register

- Disabled—COM = 11

## Workaround:

Do not use fractional drive capability.

# SIU2 Data show cycle hang condition

#### **Description:**

If the DSHW bit in the SIUMCR register is set in order to allow data show cycles to take place on the external bus, and the CPM initiates a DMA transfer to/from an internal address (for example the dual port RAM), the chip will hang.

#### Workaround:

If DMA accesses are initiated to internal locations, reset the DSHW bit.

# SIU3 Incorrect timing of PCMCIA slot B ALE signal

#### **Description:**

This erratum only affects designs that use latches for the address in their PCMCIA slot B interfaces.

The intended operation of the PCMCIA ALE signal is that ALE should assert with the address on the rising clock edge (plus the delay specified in Spec P52) and negate on the rising clock edge (plus the delay specified in Spec P53). However, for PCMCIA slot B, the ALE signal asserts and negates on the falling clock edge immediately prior to the intended edge.

This behavior shortens the address setup time for sampling in the external address latches used for PCMCIA slot B.

#### Workarounds:

Either of the following will serve as a workaround to this erratum:

- Verify address latch timing with this new timing information. If it is satisfied, there is no problem.

- Do not use external address latches for the PCMCIA slot B interface.

# SIU4 Spurious external bus transaction following PLPRCR write

#### **Description:**

This erratum only affects designs that execute code from synchronous memories or bus slaves.

Spurious external bus transactions can occur after executing a store to the PLPRCR register, which changes the PLL multiplication factor (MF bits). This store causes the PLL to freeze the clocks while another external bus access is already visible on the pins of the chip. This appears externally as a transaction that begins, has its clocks frozen, and is abruptly aborted without following the bus protocol.

This behavior only affects systems with bus slaves that implement synchronous state machines that are sensitive to bus protocol violations. Synchronous DRAMs are not affected, and synchronous bus slaves that ignore bus signals when not selected (for example, Tundra QSPAN) are not affected.

This erratum will only cause problems in one of the following situations:

- The device is executing code from a slave that implements a state machine dependent on the 60x bus protocol, where that state machine might "get lost."

- There is an external device that snoops the 60x bus and implements a state machine; this state machine might "get lost."

The impact of this erratum has been deemed minimal, and it will therefore not be corrected.

#### Workaround:

The behavior exhibited in this erratum is a secondary symptom of the behavior of SIU9. See the description of SIU9 for the suggested workaround. The workaround described there will also avoid the above-described spurious external bus transaction.

# SIU5 Bus monitor failure after TEA assertion

#### **Description:**

The bus monitor does not activate for the access immediately following an access that terminated with a TEA assertion (either internally or externally generated). Therefore, if the following access is to an unmapped address, the access will not be terminated by the MPC860. If this is allowed to occur, the cycle can potentially be endless, causing the system to hang.

The impact of this erratum has been deemed minimal, and it will therefore not be corrected.

#### Workaround:

Any of the following will serve as a workaround to this erratum:

- Avoid this situation (which should not occur in a normal system).

- Terminate the cycle externally (for example, implement an external bus monitor).

- Rely on the software watchdog timer to reset the system if this error occurs.

SIU Errata

# SIU6 Incorrect reporting of loss-of-lock reset status

## **Description:**

The RSR[LLRS] bit is set by both unintentional and software-initiated loss-of-lock; it should be set only by an unintentional loss-of-lock. Software-initiated loss-of-lock (that is, changing the SPLL multiplication factor or entering low-power modes) should not set this bit.

The impact of this erratum has been deemed minimal, and it will therefore not be corrected.

## Workaround:

The PLPRCR[SPLSS] functions as intended. Reference this bit instead.

# SIU7 Missed DRAM refresh cycles with external masters

#### **Description:**

If the MPC860 is using internal arbitration (SIUMCR[EARB]=0), and the arbitration request level (SIUMCR[EARP]) for external masters is greater than zero, then if a request by an external master (signalled by REQ) occurs simultaneously with a request from the DRAM refresh controller, the request from the DRAM refresh controller is cancelled. This results in a missed refresh cycle. In a system with many bus requests by external masters, this can potentially result in the cancellation of all DRAM refreshes.

#### Workaround:

Any of the following will serve as a workaround to this erratum:

- Program SIUMCR[EARP] to zero.

- Increase the refresh rate to compensate for the potential cancellation of refresh cycles. Treated probabilistically, it should be possible to keep the refresh rate above a minimum intended rate. This is difficult to model exactly but can be roughly estimated. For the following discussion:

- N = proportion of bus bandwidth used by internal MPC860 masters (other than refresh)

- E = proportion of bus bandwidth used by external masters

- A = proportion of bus bandwidth available for refresh

By definition, N + E + A = 1.

The proportion of time that a refresh request can occur is (E+A).

The probability that a refresh request will be cancelled is E / (E+A). If P is the probability that the refresh request will be successfully transacted, P = 1 - [E / (E+A)].

Therefore, to compensate for the cancellation of requests, increase the refresh request rate by 1/P.

For a numerical example, assume that internal and external masters each use 30% of the bus bandwidth. Thus, N = 0.3, E = 0.3, and A = 0.4. In this example, set the refresh rate to 1.75 times the intended rate.

Note, however, that this workaround becomes impractical as A approaches zero.

• Implement a software-controlled refresh initiated by a periodic timer request. The user should program the PIT timer (or a CPM timer) to provide a periodic interrupt. The interrupt service routine should incorporate a software routine to refresh a memory block. This software refresh routine can consist of either reads from the appropriate DRAM page or, more simply, execution of the UPM's refresh routine through a RUN command to the MCR. The second method is recommended, as it is simpler and uses the DRAM's internal counter to keep track of the row to be refreshed. The user should choose the size of memory block to be refreshed per interrupt in order to minimize the impact of the interrupt overhead.

At one extreme, assume a system with two 4Mx32 DRAM banks controlled by  $\overline{\text{CS2}}$  and  $\overline{\text{CS3}}$ . Each bank has 2048 pages (rows), and each page must be refreshed every 15.6 ms. If the UPM refresh pattern called by the software-refresh routine is set up to loop 16 times (and therefore can refresh 16 rows per call), the timer interrupt should occur every (16/2048)\*15.6 ms, or approximately 120 µs. If one iteration of the UPM refresh pattern is 5 clocks, the total time required to execute the software-refresh routine (plus overhead for fetching instructions) for both banks is 5\*16\*2+20 = 180 clocks. Assuming an interrupt service routine entry/exit overhead of 1200 clocks, each refresh interrupt would take approximately 1400 clocks, or 28 µs (assuming a 50-MHz system clock). An ISR consuming 28 µs out of every 120 µs period would consume 23.3% of the CPU, with 8200 interrupts per second.

At the other extreme, the entire memory (2048 refresh cycles per bank) can be refreshed every 15.6 ms. In this case, the software refresh routine would require 1200+(2048/16\*180) = 24240 clocks, or 485 µs. In this case, the ISR would consume 485 µs out of every 15.6 ms, or 3% of the CPU, and would require only 64 interrupts per second. However, system tasks would be stalled for 485 µs while waiting for the refresh task to complete.

The best compromise lies in between. For example, at 64 pages per interrupt, the software refresh routine consumes 1200+(64/16\*18) = 1920 clocks, or  $38.5 \ \mu$ s. The CPU bandwidth consumed would be  $38.5 \ \mu$ s/( $120 \ \mu$ s\*4) or about 8%, with about 2000 interrupts per second.

Example code implementing this software refresh follows below:

#This code initialize the PIT timers to interrupt (number 0) every ~24000 clocks

xor 10,0,0 ori 10,10,0xaa33 oris 10,10,0x55cc stw 10,RTSECK\_OFFSET(20) # OPEN RTC KEY

stw 10,RTSEC\_OFFSET(20) # RESET RTC divider

addis 10,10,0x80 stw 10,PISCR\_OFFSET(20) # CLEAR PIT INT bit

lwz 7, SCCR\_OFFSET(20)

```

andi. 8,7,0xffff

andis. 9,7,0xff7f

or 7,8,9

oris 7,7,0x0100

stw 7,SCCR_OFFSET(20) # RTC_CLK = SYSCLK/512

xor 9,0,0

addis 9,9,0x2f

stw 9,PITC_OFFSET(20) # Int every 24000 system clocks

xor 10,0,0

addis 10,10,0x85

stw 10,PISCR_OFFSET(20) # PIT enable

sync

#====

#The interrupt routine should include the following code:

#======

INT0:

lhz 9, PISCR_OFFSET(20) #

sth 9,PISCR_OFFSET(20) # CLEAR PIT INT bit

andi. 9,9,0x80

bc 0x4,2,INT0_L

xor 8,8,8

ori 8,8,0x0030

oris 8,8,0x8080 # Refresh CS_0 by MCR command

stw 8,MCR_OFFSET(20) # MCR(UPMB,0x30)

stw 8,MCR_OFFSET(20) # MCR(UPMB,0x30)

stw 8,MCR_OFFSET(20) # MCR(UPMB,0x30)

stw 8,MCR_OFFSET(20) # MCR(UPMB,0x30)

ori 8,8,0x2000 # Refresh CS_1 by MCR command

stw 8,MCR_OFFSET(20) # MCR(UPMB,0x30)

```

stw 8,MCR\_OFFSET(20) # MCR(UPMB,0x30)

| INT0_L: |  |  |

|---------|--|--|

| ш       |  |  |

## SIU8 Lock/unlock function of RSR also locks/unlocks SCCR

#### **Description:**

When the RSR is locked or unlocked through the RSRK register, the same function is also performed on the SCCR.

#### Workaround:

This erratum should not affect user software as long as one is aware of it. In order to avoid possible software errors due to this (if, for example, the associated code statements were reordered by the user in a code revision), as a code convention one should always perform the unlock-modify-lock operations in immediate succession on individual registers. That is: unlock the register, modify it, then lock it.

## SIU9 CPU receives machine check after writing to the PLPRCR

#### **Description:**

The CPU may receive a machine check after writing to the PLPRCR. This error is caused by an extra clock generated by the clock block after the SIU releases the bus.

The error occurs when the CPU begins a transaction after the SIU releases the internal bus. Due to the PLPRCR write, the CPU's clocks are stopped. However, the extra clock allows the CPU's transaction to begin before the clocks stop. Therefore, the CPU's clocks are stopped in mid-transaction, and its transaction never receives acknowledgement. When the CPU resumes operation, it receives a machine check.

The failure mechanism is due to an internal logic synchronization issue aggravated by memory refreshes performed by the UPM. The problem is most often exhibited when entering and exiting low-power modes frequently, such as when using doze mode to conserve power. The probability of encountering this problem is small but finite (approximately one in a million).

#### Workaround:

Prevent the CPU from getting the bus during the extra clock following the PLPRCR write. To do so, enable the instruction cache and create a software delay. To calculate how long of a delay is necessary, take the longest bus transaction in CPU clocks (including memory refresh or PCMCIA access). The resultant number of clocks must be executed using instructions such as NOP (1 clock), ISYNC (2 clocks), or DIVW (13 clocks). The instructions for the delay must either fit in one cache line, or some other mechanism must be used to make certain that the instructions for the delay are in the cache. The instructions of the delay must be executed after the PLPRCR write, which can be enforced by the ISYNC instruction. The length of the software delay must also be greater than or equal to the length of the longest bus transaction (in CPU clocks).

SIU Errata

For example, if the longest transaction is eight bus clocks and the CPU is in 1:2 mode, the delay required is 16 clocks. This can be accomplished with two DIVW instructions. The instruction cache must be enabled to make certain that the code sequence is loaded into the cache as a unit, and the PLPRCR write should be aligned to a 16-byte boundary to make sure it is the first instruction in the cache line containing the sequence. The following workaround code is suggested:

## SIU10 RTC/PIT does not count properly when the pre-divider is four

#### **Description:**

The periodic interrupt timer (PIT) consists of a 16-bit counter clocked by the PITRCLK clock supplied by the RTCLK clock (real time clock). The 16-bit counter counts down to zero when loaded with a value from the PITC. After the timer reaches zero, the PS bit is set and, if the PIE bit is a logic one, an interrupt is generated. The user can program the RTC and PIT clock to be divided by 4 or 512 (depending on SCCR[RTDIV]). When the RTC clock is divided by four, an interrupt will not occur due to a bug in the rtclk\_sync\_raw logic. The rtclk\_sync\_raw is the real time clock for the RTC timers, and its frequency is the same as rtclk\_raw. If the PLL output clock is enabled and not in reset state, and the timer has not expired, the rtclk\_sync\_raw clock has a 25% duty cycle synchronous with a system T4 tick; otherwise this clock is the same as rtclk\_raw.

From the ckpspcl schematics, rtclk\_raw also selects rtclk\_sync\_raw. There is no issue with the above statement when the pre-divider is set to 256 clocks because the select line is slower then the selected clock source. However, when the pre-divider is set to four, there is supposed to be a rtclk\_sync\_raw edge every two clocks. The rising edge of this clock will disappear due to a race between rtclk\_sync\_raw (as the select line) and the ckp\_rtclk\_sysd (as the data for the mux).

At room temperature, this generates a spike signal, and at hot temperature, this degrades and disappears. When this happens, the RTC does not count properly, and no interrupt occurs.

# **CPM Errata**

# CPM1 Microcode bug in Async HDLC & IrDA protocol

#### **Description:**

If the first character received of a new buffer descriptor (BD) is either an unmapped (discardable) control character or the control escape character (\$7D), erroneous operation will result.

#### Workaround:

Download and use the microcode patch available from Freescale.

## CPM2 I2C receive problem in arbitration-lost state

#### **Description:**

If the MPC860 I2C master transmitter loses arbitration to another I2C master that is transmitting to the MPC860, the 860 receiver does not accept the message (address byte not acknowledged).

#### Workarounds:

Either of the following will serve as a workaround to this erratum:

- Avoid multiple master configuration.

- The other master should retry the operation through software.

## CPM3 I2C error in FLT bit

#### **Description:**

An error occurs if the FLT bit is set to turn on the digital filter for the I2C. The digital filter is activated by setting the FLT bit in the I2C mode register and is turned off at reset.

(However, note that this digital filter is not required for normal operation. The MPC8xx I2C is fully compliant to the I2C specification even without this digital filter.)

#### Workaround:

Do not turn on the digital filter for the I2C clock filter.

## CPM4 Shared flags in Async HDLC

#### **Description:**

If two Async HDLC frames are separated by a single shared flag, the second frame is discarded.

#### Workaround:

Download and use the microcode patch available from Freescale.

## **CPM5** I2C master fails to receive after executing write

#### **Description:**

If the I2C channel performs a transaction (read or write command) in master mode, it fails to receive a transmission from another master and responds with NACK.

CPM Errata

Furthermore, if the I2C master then attempts to perform another transaction (read or write command) after the failed reception, the transaction fails with an underrun error.

#### Workaround:

After the master I2C channel completes its transmission, disable and re-enable the channel in the I2MOD register (thereby resetting it).

# CPM6 I2C receives single-byte buffers after failed transaction

#### **Description:**

The following is true if the I2C channel is in master mode:

• If the I2C master attempts a transaction (read or write command) that receives a NACK and then attempts to execute a read to another slave, it receives the first byte of the slave's message in one buffer, closes the BD, and continues to receive the rest of the message in the subsequent BDs. This reception of the first byte in a single-byte buffer will happen regardless of the MRBLR.

The following is true if the I2C channel is in slave mode:

• If the I2C slave responds to a read command (that is, performs a transmission) and then responds to a write command (that is, performs a reception), it receives the first byte of the master's message in one buffer, closes the BD, and continues to receive the rest of the message in the subsequent BDs. This reception of the first byte in a single-byte buffer will happen regardless of the MRBLR.

#### Workaround:

After the I2C channel performs a transmission (master read or write, or slave response to read), disable and re-enable the channel in the I2MOD register (thereby resetting it).

# CPM7 I2C receiver locks, holding SDA low

#### **Description:**

The I2C receiver may lock up, holding the SDA line low, in a system that has slow rise/fall time on the I2C clock (SCL) if the environment is noisy.

#### Workaround:

Set the I2C predivider to 32 (by setting I2MOD[PDIV]=00), and restrict the rise/fall time of SCL to 0.5  $\mu$ s. In addition to this, for revision C.0 and later of the MPC860, enable the digital filter through the I2MOD[FLT]. (For previous revisions of the MPC860, the digital filter is not functional.)

# CPM8 I2C master collision after 'double start'

#### **Description:**

The following situation causes the I2C controller to collide with the transmission of another master:

1. Another I2C master performs a 'master write' to the I2C controller of the MPC860.

- 2. The I2C controller waits for the I2C bus to become idle in order to become the master and perform a transaction.

- 3. The other I2C master asserts a new 'START' condition without asserting a 'STOP' condition. In this situation, the I2C master of the MPC860 will incorrectly interpret the new 'START' condition as generated by itself and therefore drive the I2C bus concurrently with the other master.

#### Workaround:

Avoid performing back-to-back START conditions on the I2C bus.

# CPM9 I2C short aborted transmission after NACK

#### **Description:**

The following situation causes the I2C controller of the MPC860 to send a short aborted transmission:

- 1. The I2C controller performs a transaction, transmitting a buffer that has no STOP condition at the end. The next buffer (not yet transmitted) issues a START condition, producing back-to-back transactions without an intervening STOP (also known as 'double start').

- 2. The I2C controller receives a NACK on the last or next-to-last byte of the buffer.

In this situation, the I2C controller will assert a STOP condition (as expected by the I2C protocol). However, when software subsequently issues a new start command (I2COM = 0x81), the I2C master will begin its next transaction erratically. It will issue a START condition, drive one bit of the message, drive a new START condition, and restart the transmission (including the first bit).

#### Workaround:

Do not set up the I2C controller to perform 'double start'.

## **CPM10** I2C split receive buffer between loopback and read

#### **Description:**

If the I2C master of the MPC860 performs a loopback transaction (that is, a master write to its own I2C address or a master write to the general call address with general call reception enabled) and then performs a master read transaction, the receive buffer used for the loopback transaction is closed after the first byte of the read transaction is received, instead of after the loopback transaction. Thus, the received data from the read transaction is split between the loopback buffer and the intended receive buffer.

#### Workaround:

Avoid performing loopback transactions during normal operation.

**CPM Errata**

# CPM11 I2C spurious BSY errors after reception in I2C master mode

## **Description:**

This erratum occurs when the I2C controller of the MPC860 is configured as an I2C master and is the target of another master's write. After the MPC860 receives data from the master (and thus closes the receive buffer appropriately), the controller will attempt to open the next receive buffer (even though there is no receive data). If there is no buffer available, it will generate a BSY error.

## Workaround:

Ignore BSY errors in this case.

# CPM12 RCCR must be written as a word

#### **Description:**

RCCR[ERAM4K] (located at address IMMR+0x9C7) is cleared if the RCCR is written as a byte or halfword (to addresses IMMR+0x9C4, IMMR+0x9C5).

#### Workaround:

To change the RCCR bytes at address IMMR+(0x9C4, 0x9C5), write the whole word (addresses IMMR+0x9C4 to IMMR+0x9C7).

# **General Errata**

## G1 Termination of open drain and active pull-up pins

#### **Description:**

Open drain pins and active pull-up pins drains "high" current when the input voltage to them is higher than VDDH. The excess current at the pin in question is approximately 150 microamps.

Active pull-up pins include:  $\overline{BB}$ ,  $\overline{TS}$ ,  $\overline{TA}$ , and  $\overline{BI}$

Open drain pins include: TEA, HRESET, SRESET, and any general-purpose I/O programmed as open drain

#### Workaround:

Connect the external pull-up resistor on these pins to the VDDH power supply.

# G2 Higher than expected Keep-Alive Power (KAPWR) current when main power (VDDH & VDDL) is removed

#### **Description:**

Four nodes within the MPC860 float when VDDH and VDDL power is not supplied to the device. When this condition, which is typical in power down mode, occurs, the current drain on the keep-alive power rail is greater than expected. (10 - 20 mA versus 10 µA)

#### Workaround:

Provide adequate current source for the KAPWR pin in power down mode.

# G3 EXTCLK and CLKOUT clocks may not be in phase in half-speed bus mode

#### **Description:**

When the MPC860 uses EXTCLK as an input clock source, MF=001 in PLPRCR (that is, the frequency of EXTCLK is half that of the internal clock), and half-speed bus mode is used (EBDF=01 in SCCR), the output clock from CLKOUT can be 90 or 180 degrees out of phase from the input clock. This will affect synchronous designs where the same clock source is used as an input to EXTCLK or to an external synchronous device (for example, a peripheral or ASIC).

#### Workarounds:

Case 1. Multiple external devices need to operate synchronously with the MPC860.

- Use the CLKOUT pin of the MPC860 as the clock source for all external, synchronous devices (that is, CLKOUT is the effective system master clock to be used for distribution).

Case 2. It is necessary to synchronize an external master clock (for example, from a backplane), an MPC860, and external peripherals, to allow data transfer in all three directions.

- There is no known workaround for this case. Use full-speed bus operation.

**General Errata**

# G4 Potential problems caused by skew between EXTCLK and CLKOUT

#### **Description:**

In correct operation, the PLL of the MPC860 will lock on the rising edge of the input clock. However, on these revisions of the MPC860, the PLL locks on the falling edge of the input clock. This affects the skew between EXTCLK and CLKOUT at the rising edge. The skew is dependent on the duty cycle of the input clock (but for a 50% duty cycle will not exceed 2nS). This affects synchronous designs where the same clock source is used as an input to EXTCLK, as well as to an external synchronous device (for example, a peripheral or ASIC).

#### Workarounds:

Case 1. Multiple external devices need to operate synchronously with the MPC860.

Use the CLKOUT pin of the MPC860 as the source of clock for all external, synchronous devices (that is, CLKOUT is the effective system master clock to be used for distribution).

Case 2. It is necessary to synchronize an external master clock (for example, from a backplane), an MPC860, and external peripherals, to allow data transfer in all three directions.

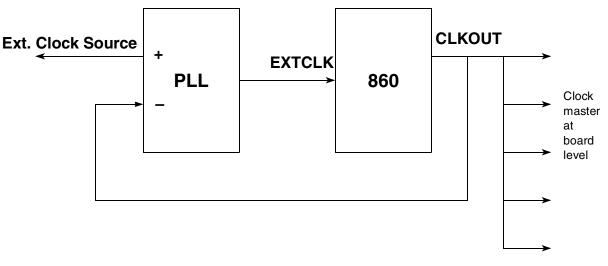

This workaround is a concept only. It has not been verified in hardware.

Insert a PLL between the external master clock and the EXTCLK pin of the MPC860. Connect the phase comparison pin of the PLL to the CLKOUT pin of the MPC 860. Also use the CLKOUT signal as the reference clock for distribution to the local external peripherals.

#### NOTE

The PLL must be capable of operating with a permanent offset of -2nS, therefore the range of lock should extend to about -4nS.

A diagram of this concept is given in Figure 1.

Figure 1. Workaround for Case 2

# G5 ESD breakdown voltage for XFC pin less than Freescale-imposed requirements

#### **Description:**

The XFC pin (T2) of this version of the MPC860 silicon fails Freescale's XC qualification of 1 Kvolt for the electrostatic discharge (ESD) breakdown voltage test. The maximum ESD voltage that can be applied to this pin on this silicon without damage is 750 volts.

#### Workaround:

Ensure that devices are not exposed to greater than 750 volts of electrostatic discharge.

# G6 Possible spikes on IRQ0, IRQ1, and IRQ7

#### **Description:**

For MPC860 Rev B.1 silicon with date codes beginning with 'Q':

If  $\overline{IRQ0}$ ,  $\overline{IRQ1}$ , or  $\overline{IRQ7}$  is pulled up to 3.3 V, the data bus has a light capacitive load, the  $\overline{IRQ}$  pin(s) in question are pulled up weakly and not driven high with an active driver, the  $\overline{IRQ}$  pin(s) in question have a light capacitive load, and the associated interrupt is enabled in SIMASK (except for  $\overline{IRQ0}$ , which is always enabled), ground bounce caused by the data bus switching can potentially couple to the  $\overline{IRQ0}$ ,  $\overline{IRQ1}$ , or  $\overline{IRQ7}$  pin, resulting in a narrow spike being driven to the interrupt logic and possible subsequent erratic operation.

#### Workaround:

The following steps make up the workaround for this erratum.

- 1. Pull up the  $\overline{IRQ0}$ ,  $\overline{IRQ1}$ , and  $\overline{IRQ7}$  pins to 5 V.

- 2. Disable these  $\overline{IRQs}$  by either masking the associated interrupt in SIMASK or connecting the  $\overline{IRQs}$  signal directly to VCC. Note that disabling the interrupts in SIMASK will only work for  $\overline{IRQ1}$  and  $\overline{IRQ7}$  as  $\overline{IRQ0}$  is non-maskable.

- 3. Actively drive these  $\overline{IRQ}$  signals.

General Errata

# G7 Active pull-up drivers switch to high-impedance too early

## **Description:**

The active pull-up drivers (which include  $\overline{\text{TS}}$ ,  $\overline{\text{TA}}$ ,  $\overline{\text{BI}}$ , and  $\overline{\text{BB}}$ ) switch to high-impedance at a threshold voltage that is lower than the specified minimum output voltage level VOH. Thereafter, the pull-up resistor must pull the signal beyond the specified output voltage level. Depending on the pull-up resistor value and the capacitive load of the signal, this can result in a longer negation time than specified.

## Workaround:

Use a 1K pull-up resistor for these drivers.

Notes:

The long rise times do not cause a problem to the processor. Nor will the longer rise times for these signals present a problem for other devices in most systems.

- 1.  $\overline{\text{TS}}$  is normally sampled at the beginning of a bus cycle and is thereafter a 'don't-care' until the cycle is terminated with  $\overline{\text{TA}}$ . Thus, a  $\overline{\text{TS}}$  that extends into the subsequent clock cycles will be ignored.

- 2. BI must only be in its negated state when sampled concurrently with TA when a cycle is to a burstable target. In these systems, typically the only burstable target is the UPM, which will drive the BI actively throughout cycles in which it is in control of the target. Therefore, this behavior will not affect operation of the memory controller. Furthermore, for burstable targets that are not in control of the memory controller, (A) the pull-up resistor should have plenty of time to complete the signal negation before the TA of the cycle, and (B) the worst that can result from a falsely asserted BI is that the master would break the burst into four accesses, resulting in a performance degradation but not a system failure.

- 3. For a non-burst cycle, TA is normally sampled only once after TS is driven. TA is then a 'don't-care' until after the next TS is driven. Therefore, there should be sufficient time for the pull-up resistor to complete the signal negation of TA before termination conditions for the next cycle are sampled. For burst cycles, typically the only burstable target in the system is the UPM, which drives the TA signal actively until the completion of the entire burst cycle, thus avoiding the problem during the burst. And for other burstable targets, it is the responsibility of the target to meet the appropriate assertion/negation timing for TA.

- 4. If this condition results in a long negation time for  $\overline{BB}$ , the only effect is increased latency between bus cycles as the bus is handed off between bus masters. That is, the bus would falsely appear busy for a short period after the on-chip master actually released the bus.

- 5.  $\overline{\text{TS}}$ ,  $\overline{\text{TA}}$ ,  $\overline{\text{BI}}$ , and  $\overline{\text{BB}}$  will typically be lightly loaded.

# G8 TS driver switches to high-impedance too early

#### **Description:**

The active pull-up driver on  $\overline{\text{TS}}$  switches to high-impedance at a threshold voltage that is lower than the specified minimum output voltage level VOH. Thereafter, the pull-up resistor must pull the signal beyond the specified output voltage level. Depending on the pull-up resistor value and the capacitive load of the signal, this can result in a longer negation time than specified.

#### Workaround:

Use a 1K pull-up resistor for this driver.

Notes:

The long rise times do not cause a problem to the processor. Nor will the longer rise times for these signals present a problem for other devices in most systems.

- 1.  $\overline{\text{TS}}$  is normally sampled at the beginning of a bus cycle and is thereafter a 'don't-care' until the cycle is terminated with  $\overline{\text{TA}}$ . Thus, a  $\overline{\text{TS}}$  that extends into the subsequent clock cycles will be ignored.

- 2.  $\overline{\text{TS}}$  will typically be lightly loaded.

## G9 Conflict between data show cycles and SDMA burst writes

#### **Description:**

If data show cycles are enabled through SIUMCR[DSHW], and an internal register or dual-port RAM access is made immediately after a SDMA burst write, the SDMA burst write may be corrupted. The observed phenomenon is that a burst write with four operands will hold the second operand into the third and fourth burst beats. For example, a burst write of A-B-C-D will be observed on the bus as A-B-B.

This behavior can also occur when the SDMA burst is to burst-inhibited memory. Setting the memory to burst-inhibited will not solve the problem.

#### Workaround:

Do not use data show cycles in a system that performs SDMA bursts. This includes systems that use ATM, fast Ethernet, and memory-to-memory IDMA.

## G10 Restriction of open collector pull up

#### **Description:**

The open collector signal may not be able to be pulled to greater than 3.5 V.

#### Workaround:

Use an external buffer if an open collector signal needs to be pulled to greater than 3.5 V.

# **CPU Errata**

# CPU1 Wrong data breakpoint detection on store instructions

## **Description:**

The data breakpoint mechanism comparison of operand data and operand size is faulty. If used, it can cause breakpoints where they should not occur, and conversely it can miss breakpoints where they should occur.

## NOTE

The instruction and address portions of the data breakpoint mechanism operate correctly. It is therefore still possible to use the data breakpoints to break on a store to a particular address and/or on a store instruction in a particular address range. Only the operand comparison portion of the data breakpoints does not function properly at all. However, see CPU11 for further minor limitations.

#### Workaround:

Do not use the operand comparison function of the data breakpoints for store instructions.

# CPU2 Program trace mechanism error

#### **Description:**

In the following case there is an error in the program trace mechanism:

Program 0x00004ff0: divw. r25,r27,r26 0x00004ff4: divw. r28,r27,r26 0x00004ff8: unimplemented 0x00004ffc: b 0x00005010

where 0x00005010 belongs to a page with a page fault.

The divide takes a long time to complete, so the instruction queue gets filled with the unimplemented instruction, the branch, and the branch target (page fault).

When the sequencer takes the unimplemented instruction, it releases the fetch that was blocked by the MMU error. This causes the queue to get another instruction in addition to the first page fault. Since the second fault is sequential to the branch target, it is not reported by the queue flush (VF). This causes an incorrect value to be present in the VF flush information when the unimplemented exception occurs.

# CPU3 Incorrect value used for POW bit of MSR register

## **Description:**