# MPC8308 Chip Errata

This document details all known silicon errata for the MPC8308. The following table provides a revision history for this document.

**Table 1. Document Revision History**

| Revision Date |         | Significant Changes                                                                                                                                                                                                                                                |  |  |

|---------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 5             | 09/2015 | Added the following errata:                                                                                                                                                                                                                                        |  |  |

|               |         | <ul> <li>eSDHC A-005055 and A-009204</li> <li>IEEE1588 A-007734</li> <li>PCle PEX5</li> <li>USB A-003845</li> </ul>                                                                                                                                                |  |  |

|               |         | Added IEEE 1588_19 to Table 3, Summary of Silicon Errata and Applicable Revision.                                                                                                                                                                                  |  |  |

|               |         | Modified eTSEC69.                                                                                                                                                                                                                                                  |  |  |

|               |         | Renamed eTSEC-A002 to A-006502 and modified the write-up.                                                                                                                                                                                                          |  |  |

|               |         | Renamed "PEX" heading to "PCIe".                                                                                                                                                                                                                                   |  |  |

|               |         | Re-ordered the USB errata numerically.                                                                                                                                                                                                                             |  |  |

| 4             | 07/2013 | Renamed USB38 to USB erratum A-003817                                                                                                                                                                                                                              |  |  |

|               |         | Added the following errata:                                                                                                                                                                                                                                        |  |  |

|               |         | <ul><li>USB errata: A-003837, A-003827, A-003829</li><li>eSDHC erratum: A-004577</li></ul>                                                                                                                                                                         |  |  |

|               |         | Removed erratum DDR20                                                                                                                                                                                                                                              |  |  |

| 3             | 05/2012 | <ul> <li>In Table 2, added silicon revision 1.1 SVR and PVR information.</li> <li>In Table 3, added silicon revision 1.1 column.</li> <li>In Table 3, updated the projected solution for the following errata: IEEE1588-A001, PCIe- A002, and A-003985.</li> </ul> |  |  |

| 2             | 12/2011 | <ul> <li>Added eLBC-A002</li> <li>Removed eLBC1, eLBC2, eTSEC29, IEEE1588_8, USB21</li> </ul>                                                                                                                                                                      |  |  |

| 1             | 11/2011 | <ul> <li>Added USB-A005, USB-A007, CPU-A022, PCIe-A002, A-003985</li> <li>Removed SPI6</li> <li>Updated USB-A001</li> </ul>                                                                                                                                        |  |  |

| 0             | 07/2010 | Initial release                                                                                                                                                                                                                                                    |  |  |

The following table provides a cross-reference to match the revision code in the processor version register to the revision level marked on the device.

**Table 2. Revision Level to Part Marking Cross-Reference**

| Part    | Revision | Processor Version Register<br>Value | System Version Register Value | Mask |

|---------|----------|-------------------------------------|-------------------------------|------|

| MPC8308 | 1.1      | 8085_0020                           | 8101_0111                     | M17Y |

| MPC8308 | 1.0      | 8085_0020                           | 8101_0110                     | M17Y |

Table 3 summarizes all known errata.

**Table 3. Summary of Silicon Errata and Applicable Revision**

| Errata     | Name                                                                                                | Projected Solution | Silicon Rev. |     |

|------------|-----------------------------------------------------------------------------------------------------|--------------------|--------------|-----|

|            |                                                                                                     |                    | 1.0          | 1.1 |

|            | CPU                                                                                                 |                    |              | •   |

| CPU6       | DTLB LRU logic does not function correctly                                                          | No plans to fix    | Yes          | Yes |

| CPU-A002   | CPU may hang after load from cache-inhibited, unguarded memory                                      | No plans to fix    | Yes          | Yes |

| CPU-A022   | The e300 core may hang while using critical interrupt                                               | No plans to fix    | Yes          | Yes |

|            | DDR                                                                                                 |                    |              | '   |

| DDR21      | MCK/MCK AC differential crosspoint voltage outside JEDEC specifications                             | No plans to fix    | Yes          | Yes |

| DDR23      | DDR read failure due to t <sub>DISKEW</sub> spec violation                                          | No plans to fix    | Yes          | Yes |

|            | eLBC                                                                                                |                    |              |     |

| eLBC5      | LTEATR and LTEAR may show incorrect values under certain scenarios                                  | No plans to fix    | Yes          | Yes |

| eLBC-A001  | Simultaneous FCM and GPCM or UPM operation may erroneously trigger bus monitor timeout              | No plans to fix    | Yes          | Yes |

| eLBC-A002  | Core may hang while booting from NAND using FCM                                                     | No plans to fix    | Yes          | Yes |

|            | eSDHC                                                                                               |                    |              |     |

| eSDHC16    | Manual Asynchronous CMD12 abort operation causes protocol violations                                | No plans to fix    | Yes          | Yes |

| eSDHC23    | CMD CRC error or CMD index error may be set for CMD without data while CMD with data is in progress | No plans to fix    | Yes          | Yes |

| eSDHC-A002 | BLKATTR[BLKCNT] does not return to 0 after Transfer<br>Complete for multi-block transfer            | No plans to fix    | Yes          | Yes |

| A-004577   | PRSSTAT[DLA] bit does not reflect the data line state when any command with busy (R1b) is issued    | No plans to fix    | Yes          | Yes |

| A-005055   | A glitch is generated on the card clock with software reset or a clock divider change               | No plans to fix    | Yes          | Yes |

Table continues on the next page...

Table 3. Summary of Silicon Errata and Applicable Revision (continued)

| Errata        | Name                                                                                                                | Projected Solution   | Silicon Rev |     |

|---------------|---------------------------------------------------------------------------------------------------------------------|----------------------|-------------|-----|

|               |                                                                                                                     |                      | 1.0         | 1.1 |

| A-009204      | System bus may hang if software register SYSCTL[RSTD] is set while DMA transactions are active                      | No plans to fix      | Yes         | Yes |

|               | eTSEC                                                                                                               |                      |             | •   |

| eTSEC42       | Frame is dropped with collision and HALFDUP[Excess Defer] = 0                                                       | No plans to fix      | Yes         | Yes |

| eTSEC58       | VLAN Insertion corrupts frame if user-defined Tx preamble enabled                                                   | No plans to fix      | Yes         | Yes |

| eTSEC59       | False parity error at Tx startup                                                                                    | No plans to fix      | Yes         | Yes |

| eTSEC64       | User-defined Tx preamble incompatible with Tx Checksum                                                              | No plans to fix      | Yes         | Yes |

| eTSEC67       | ECNTRL[AUTOZ] not guaranteed if reading MIB counters with software                                                  | No plans to fix      | Yes         | Yes |

| eTSEC68       | Half-duplex collision on FCS of Short Frame may cause Tx lockup                                                     | Documentation update | Yes         | Ye  |

| eTSEC69       | Ethernet controller does not exit from Magic Packet mode when an oddly formed Magic Packet is received              | No plans to fix      | Yes         | Ye  |

| eTSEC70       | MAC: Malformed Magic Packet Triggers Magic Packet Exit                                                              | No plans to fix      | Yes         | Ye  |

| eTSEC71       | The value of TSEC_ID2 is incorrect                                                                                  | No plans to fix      | Yes         | Ye  |

| eTSEC73       | TxBD polling loop latency is 1024 bit-times instead of 512                                                          | No plans to fix      | Yes         | Ye  |

| eTSEC74       | MAC: Rx frames of length MAXFRM or MAXFRM-1 are marked as truncated                                                 | No plans to fix      | Yes         | Ye  |

| eTSEC75       | Misfiled Packets Due to Incorrect Rx Filer Set Mask Rollback                                                        | No plans to fix      | Yes         | Ye  |

| eTSEC76       | Excess delays when transmitting TOE=1 large frames                                                                  | No plans to fix      | Yes         | Ye  |

| eTSEC78       | Controller may not be able to transmit pause frame during pause state                                               | No plans to fix      | Yes         | Ye  |

| eTSEC-A001    | MAC: Pause time may be shorter than specified if transmit in progress                                               | No plans to fix      | Yes         | Ye  |

| A-006502      | Incomplete GRS or invalid parser state after receiving a 1- or 2-byte frame                                         | No plans to fix      | Yes         | Ye  |

|               | IEEE 1588                                                                                                           |                      |             |     |

| IEEE 1588_14  | TxPAL timestamp uses TxBD snoop enable instead of Tx data                                                           | No plans to fix      | Yes         | Ye  |

| IEEE 1588_16  | Odd prescale values not supported                                                                                   | No plans to fix      | Yes         | Ye  |

| IEEE 1588_17  | Cannot use inverted 1588 reference clock when selecting eTSEC system clock as source                                | No plans to fix      | Yes         | Ye  |

| IEEE 1588_19  | Tx FIFO data parity error (DPE) may corrupt Tx timestamps if TMR_CTRL[TRTPE]=1                                      | No plans to fix      | Yes         | Ye  |

| IEEE 1588_20  | eTSEC 1588: Write to reserved 1588 register space causes system hang                                                | No plans to fix      | Yes         | Ye  |

| IEEE1588-A001 | Incorrect received timestamp or dropped packet when 1588 time-stamping is enabled                                   | Fixed in Rev 1.1     | Yes         | No  |

| A-007734      | Stale time stamps and over-flow conditions can occur when using an external 1588 input clock at certain frequencies | No plans to fix      | Yes         | Ye  |

|               | General                                                                                                             | 1                    |             | 1   |

Table continues on the next page...

Table 3. Summary of Silicon Errata and Applicable Revision (continued)

| Errata    | Name                                                                                                                                                           | Projected Solution     | Silicon Rev. |     |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|--------------|-----|

|           |                                                                                                                                                                |                        | 1.0          | 1.1 |

| General14 | Electrostatic Discharge (ESD) may fail to meet the 2KV Human body body model (HBM)                                                                             | No plans to fix        | Yes          | Yes |

| General16 | Enabling I <sup>2</sup> C could cause I <sup>2</sup> C bus freeze when other I <sup>2</sup> C devices communicate                                              | No plans to fix        | Yes          | Yes |

| General17 | DUART: Break detection triggered multiple times for a single break assertion                                                                                   | No plans to fix        | Yes          | Yes |

|           | PCIe                                                                                                                                                           |                        |              |     |

| PEX1      | No support of PCI Express completions with BCM bit set (PCIX bridge interface)                                                                                 | No plans to fix        | Yes          | Yes |

| PEX2      | DMA Interrupt descriptor race condition (IDRC)                                                                                                                 | No plans to fix        | Yes          | Yes |

| PEX5      | PCI Express LTSSM may fail to properly train with a link partner following HRESET#                                                                             | No plans to fix        | Yes          | Yes |

| PEX7      | Recovery from hot reset or link down                                                                                                                           | No plans to fix        | Yes          | Yes |

| PCIe-A002 | PCI Express Packets may be transmitted with excess data on x1 link                                                                                             | Partially fixed in 1.1 | Yes          | No  |

|           | RTC                                                                                                                                                            |                        |              |     |

| A-003985  | Real Time Counter Register (RTCTR) may not work correctly                                                                                                      | Fixed in Rev 1.1       | Yes          | No  |

|           | USB                                                                                                                                                            |                        |              |     |

| USB15     | Read of PERIODICLISTBASE after successive writes may return a wrong value in host mode                                                                         | No plans to fix        | Yes          | Yes |

| USB19     | USBDR in Host mode does not generate an interrupt upon detection of a CRC16/PID/Timeout error when a received IN data packet is corrupted                      | No plans to fix        | Yes          | Yes |

| USB25     | In host mode, when the software forces a port resume by writing into the FPR bit of the portsc register, the port change detect interrupt bit is falsely fired | No plans to fix        | Yes          | Yes |

| USB26     | NackCnt field is not decremented when received NYET during FS/LS Bulk/Interrupt mode                                                                           | No plans to fix        | Yes          | Yes |

| USB27     | When an ACK or NAK is sent from the device in response to a PING, the CERR counter value is not being reset to the initial value                               | No plans to fix        | Yes          | Yes |

| USB28     | In device mode, when receiving a Token OUT, if a Rx flush command is issued at the same time, to the same endpoint, the packet will be lost                    | No plans to fix        | Yes          | Yes |

| USB29     | Priming ISO over SOF will cause transmitting bad packet with correct CRC                                                                                       | No plans to fix        | Yes          | Yes |

| USB31     | Transmit data loss based on bus latency                                                                                                                        | No plans to fix        | Yes          | Yes |

| USB32     | Missing SOFs and false babble error due to Rx FIFO overflow                                                                                                    | No plans to fix        | Yes          | Yes |

| USB33     | No error interrupt and no status will be generated due to ISO mult3 fulfillment error                                                                          | No plans to fix        | Yes          | Yes |

| USB34     | NAK counter decremented after receiving a NYET from device                                                                                                     | No plans to fix        | Yes          | Yes |

| USB35     | Core device fails when it receives two OUT transactions in a short time                                                                                        | No plans to fix        | Yes          | Yes |

|           | +                                                                                                                                                              | No plans to fix        |              | t   |

Table continues on the next page...

# Table 3. Summary of Silicon Errata and Applicable Revision (continued)

| Errata   | Name                                                                                                 | Projected Solution | Silicon Rev. |     |

|----------|------------------------------------------------------------------------------------------------------|--------------------|--------------|-----|

|          |                                                                                                      |                    | 1.0          | 1.1 |

| USB37    | OTG Controller as Host does not support Data-line Pulsing Session Request Protocol                   | No plans to fix    | Yes          | Yes |

| USB-A001 | Last read of the current dTD done after USB interrupt                                                | No plans to fix    | Yes          | Yes |

| USB-A002 | Device does not respond to INs after receiving corrupted handshake from previous IN transaction      | No plans to fix    | Yes          | Yes |

| USB-A003 | Illegal NOPID TX CMD issued by USB controller with ULPI interface                                    | No plans to fix    | Yes          | Yes |

| USB-A005 | ULPI Viewport not Working for Read or Write Commands With Extended Address                           | No plans to fix    | Yes          | Yes |

| USB-A007 | Host controller fails to enter the PING state on timeout during High Speed Bulk OUT/DATA transaction | No plans to fix    | Yes          | Yes |

| A-003817 | USB Controller locks after Test mode "Test_K" is completed                                           | No plans to fix    | Yes          | Yes |

| A-003827 | DATA PID error interrupt issued twice for the same high bandwidth ISO transfer                       | No plans to fix    | Yes          | Yes |

| A-003829 | Host detects frame babble but does not halt the port or generate an interrupt                        | No plans to fix    | Yes          | Yes |

| A-003837 | When operating in test mode, the CSC bit does not get set to 1 to indicate a change on CCS           | No plans to fix    | Yes          | Yes |

| A-003845 | Frame scheduling robustness-Host may issue token too close to uframe boundary                        | No plans to fix    | Yes          | Yes |

### CPU6: DTLB LRU logic does not function correctly

Description: The DTLB is implemented as 2-way set associative with 32 entries per way. EA[15:19] is used to determine which one of the 32 entries of both ways. When a DTLB miss occurs, normally the CPU provides information (through SRR1 bit 14, DTLB replacement way) to indicate which of the two ways the software (DTLB exception handler or the software table walk routine) should use to bring in the new page. Presumably, the CPU provides the information, through SRR1 bit 14, based on the LRU (least recently used) algorithm. However, because of this bug, this is not the case.

> In fact, for any given EA[15:19], when a DTLB miss occurs, SRR1 bit 14 always indicates that way1 should be used or replaced. (Except if it is the very first DTLB miss after hard reset. In this case, SRR1 bit 14 indicates way0 should be used.)

In other words, if the DTLB exception routine follows the SRR1 bit 14's suggestion to do the TLB replacement, it always replaces the one in way1. In addition, whatever has been loaded in way0 is effectively locked and is not replaced.

Impact:

Performance degradation due to the reduction of usable DTLB entries.

Workaround: In the software, use one word (32 bits) to keep the record of the DTLB way that is Least Recently Written (LRW). Use this information to overwrite the SRR1 bit 14 (DTLB replacement way) when a Data Translation Miss exception occurs. Basically, the LRU (least recently used) hardware algorithm is changed to an LRW (least recently written) software algorithm.

> For the system that has no secondary storage (such as a hard drive), it is highly recommended to set the C (Change) bit during the DTLB load exception to optimize the performance.

> For a system that has a secondary storage and the OS does a page swap, the OS can choose whether to set the C bit in the DTLB load exception.

> If the C bit is set in the DTLB load exception, it can preempt the subsequent DTLB store exception to the same page. However, since all the pages are marked as changed, during the page swap all pages must be written back to the secondary storage regardless of whether they have really been changed or not.

> If the C bit is not set in the DTLB load exception with the LRW algorithm, a subsequent store to the same page as the previous load will use a separate entry. Therefore, one page occupies both ways. This causes inefficiency for the DTLB allocation but may save time during the page swap since the page change status is correctly marked.

Fix plan:

No plans to fix

### CPU-A002: CPU may hang after load from cache-inhibited, unguarded memory

Description: There is a one-core-clock-cycle window of opportunity for a snoop to collide with the data returned from cache-inhibited memory to a load that has been cancelled. This collision can hang the data cache in a busy state, prohibiting further data cache accesses. The snoop address is immaterial.

> The load can be cancelled if it meets the following conditions: it was executing speculatively beyond a conditional branch that resolved unfavorably or was pre-empted by an external interrupt or decrementer interrupt that took priority. The load must be from a cache-inhibited, non-guarded memory block. A load from cacheable memory, even if it misses in the cache, does not hang the data cache in a busy state, and if the memory block is marked guarded, the load will not be executed out of order.

> An external master must put addresses on the bus with the attribute of memory coherency required (Global) so that the CPU allows snooping of the data cache. External masters have to be programmed to snoop.

### Impact:

CPU halts or stops executing on a subsequent load or store that finds the data cache busy. This load or store does not complete, and the data cache stays busy until a hardware or software reset (HRESET or SRESET). Debug tools will reveal that the program counter is stopped and pointing to the load or store that cannot complete.

Workaround: Use one of the following options:

- Set bit 14 in the HID2 register. This bit disables a minor feature that attempted to take advantage of cache hits under a cancelled cache miss which was still waiting for data. There should be no performance loss from disabling this feature. HID2[14] is not implemented on any other e300 devices. Setting it will have no effect on other devices or any future revisions.

- Mark all data memory blocks from which loads could occur "cacheable" or "guarded."

### CPU-A022: The e300 core may hang while using critical interrupt

**Description:** If BOTH critical interrupt AND normal interrupt types are used in a system, the e300 core may hang.

Impact:

The processor may stop dispatching instructions until a hardware reset(HRESET). Debug tools will not be able to read any register correctly except program counter IAR which points to a location in the critical interrupt vector.

**Workaround:** If both critical interrupt and normal interrupt types are used, then instead of using an **rfi** instruction at the end of every exception handler, replace the **rfi** with the following:

- 1. Disable critical interrupts by setting MSR[CE] to 0 with a **mtspr** instruction.

- 2. Copy SRR0 and SRR1 to CSRR0 and CSRR1, respectively.

- 3. Execute an **rfci** instruction. This enables MSR[CE] and any other bits that the original **rfi** would have set including the MSR[EE].

### Sample Code:

```

// Disable MSR[CE]

mfmsr r2

lis r3, 0xffff

ori r3, r3, 0xff7f

and r2, r2, r3

sync

mtmsr r2

isync

// Copy SRR0, SRR1 to CSRR0 and CSRR1

mfspr r2, srr0

mfspr r3, srr1

mtspr csrr0, r2

mtspr csrr1, r3

...restore GPRs

rfci

```

### DDR21: MCK/MCK AC differential crosspoint voltage outside JEDEC specifications

**Description:** The crossover points of the MCK and MCK signals of the DDR controller are not meeting

JESD79-2C specifications, which indicates that the crossover points should lie within ±125 mV

range of reference voltage.

**Impact:** Disagreement with the JESD79-2C standard.

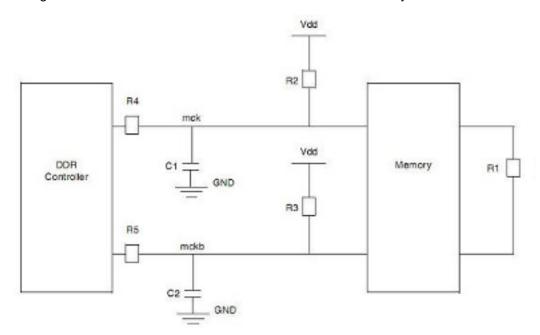

**Workaround:** To meet the JESD79-2C crosspoint voltage specifications, we recommend implementing the following connections between the DDR controller and DDR2 memory:

Figure 1. Recommended connections for DDR controller and memory

Effect of different circuit components on MCK and MCK signals:

- 1. Increasing R2 and R3 shifts signal levels up (used as pull up).

- 2. Increasing C1 increases rise/fall time of mck signal.

- 3. Increasing C2 increases rise/fall time of mckb signal.

- 4. Reducing R1 can help in shifting the signals up.

- 5. R4 and R5 can be used to make termination proper.

### Component Placing:

R4, R5, C1, C2 near to SOC, R1, R2, and R3 have been placed at the end of clock transmission lines.

By considering these suggestions and choosing proper values of components for a particular board layout, one can keep crossover points within range.

We recommend varying termination resistor R1 first. Lowering R1 can help increase the voltage levels up. The only disadvantage is that it may add up more reflections. Therefore, the user must decide accordingly. If it does not give sufficient margin, the user can add the pull-up resistor (R3 and R4) option to further increase the voltage levels.

Exact values of components vary from design to design and some of them may not be required fpr all designs. We recommend that you make provisions for all these options in your design.

## DDR23: DDR read failure due to t<sub>DISKEW</sub> spec violation

Description: When the minimum voltage swing (500 mV) on inputs specified by JEDEC spec is applied,

there will be violation of t<sub>DISKEW</sub> parameter.

**Impact:** DDR read operation is not guaranteed if peak-to-peak input voltage swing is less than 800 mV.

Workaround: Select the parallel termination resistor and configuration such that the peak-to-peak input

voltage swing is more than 800 mV.

### eLBC5: LTEATR and LTEAR may show incorrect values under certain scenarios

Description: The eLBC IP acks any transaction request when FCM special operation is in progress. In such

a scenario when any one of the errors/events occur (such as Bus Monitor Timeout, Write Protect, Parity error, Atomic error, FCM command completion, or UPM command completion except for the CS error), the registers LTEAR and LTEATR capture the address and attributes of the most recently req-acked transaction instead of the FCM special operation that caused

error. Hence indeterministic value may show up in those registers.

**Impact:** LTEAR and LTEATR cannot be used for debugging in this scenario.

Workaround: None

# eLBC-A001: Simultaneous FCM and GPCM or UPM operation may erroneously trigger bus monitor timeout

**Description:** When the FCM is in the middle of a long transaction, such as NAND erase or write, another

transaction on the GPCM or UPM triggers the bus monitor to start immediately for the GPCM or UPM, even though the GPCM or UPM is still waiting for the FCM to finish and has not yet started its transaction. If the bus monitor timeout value is not programmed for a sufficiently large value, the local bus monitor may time out. This timeout corrupts the current NAND Flash

operation and terminate the GPCM or UPM operation.

**Impact:** Local bus monitor may time out unexpectedly and corrupt the NAND transaction.

Workaround: Set the local bus monitor timeout value to the maximum by setting LBCR[BMT] = 0 and

LBCR[BMTPS] = 0xF.

### eLBC-A002: Core may hang while booting from NAND using FCM

**Description:** When FCM is selected as the boot ROM controller via power-on-reset configuration, eLBC

automatically loads 4K Bytes page of boot code into the FCM buffer RAM. These 4K Bytes consist of 8 pages (512 bytes each) of small-page NAND flash OR 2 pages (2048 bytes each) of Large-page NAND flash. The core begins execution as soon as the first page is loaded. If the core tries to execute an instruction that has not been loaded yet, unpredictable behavior

may result.

**Impact:** Core might not be able to boot from NAND.

Workaround: Before execution of any instruction located beyond the first page, wait for LTESR[CC] (offset

0xB0) bit to be set. The bit indicates that all the pages have been loaded from NAND to 4K

Bytes FCM buffer RAM.

### eSDHC16: Manual Asynchronous CMD12 abort operation causes protocol violations

Description: There may be protocol violations if a manual (software) asynchronous CMD12 is used to abort

data transfer. Due to this erratum, the eSDHC controller continues driving data after a manual (software) asynchronous CMD12 is issued. Therefore, it may cause a conflict on the data lines

on the SD bus.

Impact: Manual asynchronous CMD12 to terminate data transfer cannot be used.

**Workaround:** Do not issue a manual asynchronous CMD12. Instead, use a (software) synchronous CMD12 or AUTOCMD12 to abort data transfer.

Due to erratum A-004577, CMD13 needs to be sent after TC of the data transfer command for which AutoCMD12 is enabled. See A-004577 for details.

For a manual synchronous CMD12, the following steps are required:

- 1. Set PROCTL[SABGREQ] = 1

- 2. Wait for IRQSTAT[TC] bit set, or Transfer Complete Interrupt

- 3. Set IRQSTAT[TC] = 1

- 4. Issue CMD12 after checking PRSSTAT[CIHB] = 0

- 5. Set both SYSCTL[RSTD] and SYSCTL[RSTC]

# eSDHC23: CMD CRC error or CMD index error may be set for CMD without data while CMD with data is in progress

Description: While a command with data is in progress and a command without data is issued, for example

CMD13, an invalid command CRC error (IRQSTAT[CCE]) and/or command index error (IRQSTAT[CIE]) might be detected. This can happen when SDHC\_CLK shuts off (due to buffer danger) exactly after START bit of response is detected by the eSDHC. While the clock is gated, the eSDHC samples an incorrect value from the command line thus sampling an incorrect command index in the response and eventually generating a command CRC and

index error.

**Impact:** This issue occurs under a rare condition. The data transfer itself is not impacted.

Workaround: On detecting a command CRC error (IRQSTAT[CCE]) or command index error

(IRQSTAT[CIE]), perform error recovery and re-issue the command without data. If Auto CMD12 is enabled for data transfer then Auto CMD12 won't be issued by hardware, so

software needs to issue it after data transfer completion.

eSDHC-A002: BLKATTR[BLKCNT] does not return to 0 after Transfer Complete for

multi-block transfer

**Description:** For a multi-block transfer, when the XFERTYP[BCEN](block count enable) is 1,

BLKATTR[BLKCNT] should decrement to 0 after Transfer Complete (TC)((IRQSTAT[TC] = 1).

However, due to this erratum, BLKATTR[BLKCNT] returns to the initial value which was

programmed while issuing the multi-block transfer command.

Impact: The value of BLKATTR[BLKCNT] is unreliable and cannot be read to confirm a Transfer

Complete.

Workaround: For a multi-block transfer, after IRQSTAT[TC] = 1, software should not rely on the value of

BLKATTR[BLKCNT].

### A-004577: PRSSTAT[DLA] bit does not reflect the data line state when any command with busy (R1b) is issued

Affects: **eSDHC**

Description: When an AutoCMD12 or any command with busy (R1b) is issued, PRSSTAT[DLA] bit should

reflect the data line state. However, due to this erratum, PRSSTAT[DLA] is not applicable to detect data busy state. Furthermore, the corresponding transfer complete interrupt is not generated. However, the AutoCMD12 or any command with busy (R1b) can still be used with

the restriction that busy needs to be de-asserted before sending new data command.

When an AutoCMD12 or any command with busy (R1b) is issued, PRSSTAT[DLA] bit does not Impact:

reliably reflect the data line state.

Workaround: Software needs to wait for busy de-assertion before issuing any new data command. DAT0 line could be polled, but robust solution would be to keep sending CMD13(SEND STATUS)

until card reaches "trans" state.

• For AutoCMD12, CMD13 needs to be sent after TC of the data transfer command for which AutoCMD12 is enabled.

• For other command with busy, CMD13 needs to be sent after the command with busy

completion(IRQSTAT[CC] = 1).

# A-005055: A glitch is generated on the card clock with software reset or a clock divider change

Affects: eSDHC

Description: A glitch may occur on the SDHC card clock when the software sets the SYSCTL[RSTA] bit

(that is, performs a software reset). It can also be generated by setting the clock divider value.

The glitch produced can cause the external card to switch to an unknown state. The

occurrence is not deterministic and it happens rarely. The next command causes a timeout

error(IRQSTAT[CTOE]) after this issue occurs.

**Impact:** Changing the frequency or performing a software reset for all may not work reliably.

Workaround: When the timeout error occurs for the command right after the SYSCTL[RSTA] is set or the

clock divider value is changed, send CMD0 to bring the card to idle state, and perform reinitialization again. If the error occurs again, repeat this step until the initialization process

completes.

# A-009204: System bus may hang if software register SYSCTL[RSTD] is set while DMA transactions are active

Affects: eSDHC

Description: In the event of that any data error (like, IRQSTAT[DCE]) occurs during an eSDHC data

transaction where DMA is used for data transfer to/from the system memory, setting the

SYSCTL[RSTD] register may cause a system hang. If software sets the register

SYSCTL[RSTD] to 1 for error recovery while DMA transferring is not complete, eSDHC may hang the system bus. This happens because the software register SYSCTL[RSTD] resets the

DMA engine without waiting for the completion of pending system transactions.

**Impact:** Causes system bus to hang.

Workaround: Add a 5 ms delay before setting SYSCTL[RSTD] to make sure all the DMA transfers are

finished.

## eTSEC42: Frame is dropped with collision and HALFDUP[Excess Defer] = 0

Description: eTSEC drops excessively deferred frames without reporting error status when

HALFDUP[Excess Defer] = 0. This erratum affects 10/100 Half Duplex modes only.

**Impact:** The eTSEC does not correctly abort frames that are excessively deferred. Instead it closes the

BD as if the frame is transmitted successfully. This results in the frame being dropped (because it is never transmitted) without any error status being reported to software.

Workaround: Do not change HALFDUP[Excess Defer] from its default of 1.Thus eTSEC always tries to

transmit frames regardless of the length of time the transmitter defers to carrier.

### eTSEC58: VLAN Insertion corrupts frame if user-defined Tx preamble enabled

**Description:** When TCTRL[VLINS] = 1, the VLAN is supposed to be inserted into the Tx frame 12 bytes

after start of the Destination Address (after DA and SA). If user-defined Tx preamble is enabled (MACCFG2[PreAmTxEn] = 1), the VLAN ID is inserted 12 bytes after the start of the

preamble (4 bytes after start of DA), thus overwriting part of DA and SA.

Impact: If VLAN insertion is enabled with user-defined Tx preamble, the VLAN ID corrupts the Tx frame

destination and source addresses.

Workaround: Use one of the following workarounds:

• Disable user-defined Tx preamble by setting MACCFG2[PreAmTxEn] = 0.

• Disable VLAN insertion by setting TCTRL[VLINS] = 0.

## eTSEC59: False parity error at Tx startup

Description: The 10 KB TxFIFO comes out of reset in an unitialized state. Each FIFO entry is initialized as

Tx frame data is written to it. Under certain internal resource contention conditions, the

controller may read uninitialized data and falsely signal a parity error in IEVENT.

**Impact:** If parity errors are enabled before the first 10KB of Tx frame data is written to the TxFIFO,

pause frames or Tx frames may trigger a false data parity error event.

Workaround: Disable parity error detection by setting EDIS[DPEDIS]=1 until at least 10 KB of Tx data has

been transmitted.

### eTSEC64: User-defined Tx preamble incompatible with Tx Checksum

Description: If user-defined Tx preamble is enabled (by setting MACCFG2[PreAmTxEn]=1), an extra 8

bytes of data is added to the frame in the Tx data FIFO. IP and TCP/UDP checksum generation do not take these extra bytes into account and write to the wrong locations in the

frame.

Impact: Enabling both user-defined Tx preamble and IP or TCP/UDP checksum causes corruption of

part of the corresponding header.

Workaround: Use one of the following workarounds:

Disable user-defined Tx preamble by setting MACCFG2[PreAmTxEn] = 0.

• Disable IP and TCP/UDP checksum generation by setting TCTRL[IPCSEN]=0 and TCTRL[TUCSEN] = 0.

### eTSEC67: ECNTRL[AUTOZ] not guaranteed if reading MIB counters with software

**Description:** The MIB function of the Ethernet controller has a feature to automatically zero out the registers when reading them if ECNTRL[AUTOZ] = 1. If the register read occurs in the same cycle as a hardware update of the register, then the register clear will not occur. Any software periodically reading MIB registers would expect to read A the first time, B the second, and C the third, with each value representing only the events that occurred in the interval between reads. If the first read collides with a hardware update, the second read would return A + B instead of B.

> Hardware updates for MIB registers occur once per frame. For streaming 64-byte frames, the update would be every 84 Rx or Tx clocks (8 bytes of preamble, 64 bytes of data and 12 cycles of IPG).

Impact:

Software polling of MIB counters with ECNTRL[AUTOZ] = 1 will over an extended period read a larger number of events than actually seen by the controller.

Workaround: Disable automatic clearing of the MIB counters by writing ECNTRL[AUTOZ] = 0. Software routines which periodically read MIB counters and accumulate the results should accumulate only when an MIB counter overflows, as in the description that follows: Assuming a 32-bit MIB counter (MIB\_VALUE), a 64-bit accumulator consisting of two 32-bit registers (ACCUM\_HI, ACCUM\_LO), and a Carry Out bit (ACCUM\_LO\_CO), change the 64-bit accumulator update as follows:

Previous accumulate method (with ECNTRL[AUTOZ] = 1):

```

// Accumulate the MIB_VALUE into the lower half of the accumulator

{ACCUM\_LO\_CO,ACCUM\_LO} = {1'b0,ACCUM\_LO} + {1'b0,MIB\_VALUE};

// Accumulate the Carry Out from the step above, as well as the MIB register

OVFRFLW, which is detected through the CARn register.

{ACCUM_HI_CO,ACCUM_HI} = {1'b0,ACCUM_HI} + ACCUM_LO_CO + OVRFLW;

```

New accumulate method (with ECNTRL[AUTOZ]=0):

```

// Read instead of accumulate since we are not clearing MIB_VALUE

ACCUM LO = MIB VALUE;

// Accumulate the MIB register OVRFLW, which is detected through the CARn

register

{ACCUM_HI_CO,ACCUM_HI} = {1'b0,ACCUM_HI} + OVRFLW;

```

### eTSEC68: Half-duplex collision on FCS of Short Frame may cause Tx lockup

**Description:** In half-duplex mode, if a collision occurs in the FCS bytes of a short (fewer than 64 bytes)

frame, then the Ethernet MAC may lock up and stop transmitting data or control frames. Only a

reset of the controller can restore proper operation once it is locked up.

Impact: A collision on hardware-generated FCS bytes of a short frame in half-duplex mode may cause

a Tx lockup.

Workaround: Option 1:

Set MACCFG2[PAD/CRC] = 1, which pads all short Tx frames to 64 bytes.

Option 2:

Use software-generated CRC (MACCFG2[PAD/CRC] = 0, MACCFG2[CRC EN] = 0 and

TxBD[TC] = 0

Fix plan: Documentation update

The reference manual will be updated to require padding of all short Tx frames when in half-

duplex mode (MACCFG2[Full Duplex] = 0).

### eTSEC69: Ethernet controller does not exit from Magic Packet mode when an oddly formed Magic Packet is received

Description: The Ethernet MAC should recognize as a Magic Packet any Ethernet frame with the following contents:

- A valid Ethernet header (Destination and Source Addresses)

- A valid FCS (CRC-32)

- A payload that includes the specific MagicPacket byte sequence at any offset from the start of data payload.

The specific byte sequence comprises an unbroken stream of 102 bytes, the first 6 bytes of which are 0xFFs followed by 16 copies of the MAC's unique IEEE station address in the normal byte order for Ethernet addresses.

However, if a complete Magic Packet sequence (including 6 bytes of 0xFF) immediately follows a partial Magic Packet sequence the complete sequence will not be recognized and the MAC will not exit Magic Packet mode.

The following are examples of partial sequences followed by the start of a complete sequence for a station address 01 02 03 04 05 06:

FF\_FF\_FF\_FF\_FF\_FF\_01\_02\_03\_04\_05\_06\_01...

Seventh byte of 0xFF does not match next expected byte of Magic Packet sequence (01). Pattern search restarts looking for 6 bytes of FF at byte 01.

• FF\_FF\_FF\_FF\_FF\_01\_FF\_FF\_FF\_FF\_FF\_01\_02\_03\_04\_05\_06\_01...

First FF byte following 01 does not match Magic Packet sequence.

Pattern search restarts looking for 6 bytes of FF at second byte of FF following 01.

Impact:

The Ethernet controller does not exit Magic Packet mode if the Magic Packet sequence is placed immediately after other frame data that partially matches the Magic Packet sequence.

Workaround: There is no on-chip software or hardware workaround that can be performed to avoid or recover from this behavior. The controller does not wake up if one of these oddly formed magic packets is received, but any subsequent, properly formatted magic packet does wake up the controller.

If the received magic packet is properly formed, this erratum is avoided.

Fix plan:

No plans to fix

### eTSEC70: MAC: Malformed Magic Packet Triggers Magic Packet Exit

**Description:** The Ethernet MAC should recognize Magic Packet sequences as follows:

Any Ethernet frame containing a valid Ethernet header DA/SA (Destination and Source Addresses) and valid FCS (CRC-32), and whose payload includes the specific Magic Packet byte sequence at any offset from the start of data payload. The specific byte sequence comprises an unbroken stream of 102 bytes, the first 6 bytes of which are 0xFFs, followed by 16 copies of the MAC's unique IEEE station address in the normal byte order for Ethernet addresses.

Once the Ethernet MAC has recognized a valid DA for one frame, it continues searching for valid 102-byte Magic Packet sequences through multiple frames without checking for valid DA on each frame. The only events that cause the MAC to go back to check for valid DA before checking for a Magic Packet sequence on new frames are:

- 1. A frame containing a recognized full Magic Packet sequence (with valid or invalid FCS)

- 2. Software disable of Magic Packet mode (MACCFG2[MPEN]=0)

- 3. MAC soft reset (MACCFG1[Soft\_Reset]=1)

Impact:

The Ethernet controller may exit Magic Packet mode if it receives a frame with DA not matching station address, or invalid unicast or broadcast address, but a valid Magic Packet sequence for the device.

Workaround: None

## eTSEC71: The value of TSEC\_ID2 is incorrect

**Description:** The eTSEC1 and eTSEC2 TSEC\_ID2 registers (0x24004, 0x25004) have a wrong default

value of 0x00EC00F0, not according to the Reference Manual. The correct value, as in the

Reference Manual, should be 0x00E000F0.

**Impact:** There is no functional impact.

Workaround: None

### eTSEC73: TxBD polling loop latency is 1024 bit-times instead of 512

**Description:** Register bit DMACTRL[WOP] defines the use of wait on poll when transmit ring scheduling

algorithm is set to single polled ring mode. (TCTRL[TXSCHED]=00). When the use polling is selected by setting DMACTRL[WOP]=0, the poll to TxBD on ring 0 should occur every 512 bit-

times. Due to the errata the poll occurs every 1024 bit-times.

**Impact:** The duration of the polling is twice as long as originally specified.

Workaround: None

### eTSEC74: MAC: Rx frames of length MAXFRM or MAXFRM-1 are marked as truncated

Description: If MACCFG2[Huge Frame]=0 and the Ethernet controller receives frames which are larger

than MAXFRM, the controller truncates the frames to length MAXFRM and marks RxBD[TR]=1 to indicate the error. The controller also erroneously marks RxBD[TR]=1 if the received frame

length is MAXFRM or MAXFRM-1, even though those frames are not truncated.

No truncation or truncation error occurs if MACCFG2[Huge Frame]=1.

Impact: If MACCFG2[Huge Frame]=0, Rx frames of length MAXFRM or MAXFRM-1 are received

normally, but RxBD[TR] is set to 1.

Workaround: Option 1:

Set MACCFG2[Huge Frame]=1, so no truncation occurs for invalid large frames. Software can determine if a frame is larger than MAXFRM by reading RxBD[LG] or RxBD[Data Length].

Option 2:

Set MAXFRM to 1538 (0x602) instead of the default 1536 (0x600), so normal-length frames are not marked as truncated. Software can examine RxBD[Data Length] to determine if the

frame was larger than MAXFRM-2.

### eTSEC75: Misfiled Packets Due to Incorrect Rx Filer Set Mask Rollback

Description: When the eTSEC Rx filer exits a cluster or AND chain that does not produce a match, it should roll back the mask to the value at the beginning of the chain or cluster. If that cluster or AND chain does not contain a Set Mask rule, however, the mask rolls back to the value prior to the previous Set Mask rule due to this erratum.

> The following list provides an example of how a rule sequence should maintain a Mask for filer frame matching (the mask value is as it should be starting evaluation of the rule):

Rule #1: <Mask = default, 0xFFFF\_FFFF>

Set Mask to 0x0000\_8000 to search for frame data pattern that would match, as programmed by RQFPR's property field, and RQFCR[PID, Property ID].

Rule #2: <Mask = 0x0000 8000>

Look for a frame with status of having Broadcast address as the destination address.

Rule #3: <Mask = 0x0000 8000>

Start a Cluster of rules, grouped together for a special match.

Rule #4: <Mask = 0x0000\_8000>

Set Mask to 0x0000\_0210 inside Cluster, to search for frame data pattern that would match, as programmed by RQFPR's property field, and RQFCR[PID, Property ID].

Rule #5: <Mask = 0x0000 0210>

Inside Cluster, exit cluster and look for frame with status IPv4 header and UDP. Roll back mask to value at start of cluster.

Rule #6: <Mask =  $0x0000_8000>$

Set Mask (outside of cluster) to new value 0xFF00\_FFFF.

Rule #7: <Mask = 0xFF00\_FFFF>

Start of AND chain of 2 rules, the 1st rule, look for Destination Address 24-bits & Mask greater than RQPROP

Rule #8: <Mask = 0xFF00 FFFF>

End of AND chain, the 2nd rule, look for Destination Address low 24-bits & Mask greater than RQPROP. Roll back mask to value at start of chain.

Rule #9: <Mask = 0xFF00\_FFFF>

Start of AND chain of 2 rules, the 1st rule, look for Source Address high 24-bits & Mask less than RQPROP

Rule #10: <Mask = 0xFF00 FFFF>

End of AND chain, the 2nd rule, look for Source Address low 24-bits & Mask less than **RQPROP**

Rule #11: <Mask = 0xFF00\_FFFF>

etc.

The incorrect behavior in this example starts after rule #8:

Rule #8: <Mask = 0xFF00\_FFFF>

End of AND chain, the 2nd rule, look for Destination Address low 24-bits & Mask greater than RQPROP. Roll back mask to value at start of chain.

After rule #8, the mask should roll back to the mask set by the last Set Mask rule outside the cluster (rule #6), but instead rolls back to the previous mask value (set by rule #1, and restored after cluster exit between rule 5 and 6).

Rule #9: <Mask = 0x0000\_8000>

Start of AND chain of 2 rules, the 1st rule, look for Source Address high 24-bits & Mask less than RQPROP. Mask should be 0xFF00\_FFFF.

Rule #10: <Mask = 0x0000\_8000>

End of AND chain, the 2nd rule, look for Source Address low 24-bits & Mask less than RQPROP. Mask should be 0xFF00\_FFFF.

Rule #11: <Mask = 0x0000\_8000>

Mask should be 0xFF00\_FFFF.

etc.

The AND chain of rule #9 and 10, or any rule that follows it, could falsely reject or misfile an incoming frame because the wrong mask is being applied.

**Impact:** The Filer can accept or reject a frame based on filer rule matching using incorrect mask.

Workaround: Use one of the following workarounds:

- Have all clusters or AND chains contain a Set Mask rule.

- After a stand alone Set Mask rule, the next cluster or AND chain in a sequence of filer rules should have immediately following it a repeat of the previous stand alone Set Mask rule.

### eTSEC76: Excess delays when transmitting TOE=1 large frames

Description: The Ethernet controller supports generation of TCP or IP checksum in frames of all sizes. If TxBD[TOE]=1 and TCTRL[TUCSEN]=1 or TCTRL[IPCSEN]=1, the controller holds the frame in the TxFIFO while it fetches the data necessary to calculate the enabled checksum(s). Because the checksums are inserted near the beginning of the frame, transmission cannot start on a TOE=1 frame until the checksum calculation and insertion are complete.

> For TOE=1 huge or jumbo frames, the data required to generate the checksum may exceed the 2500-byte threshold beyond which the controller constrains itself to one memory fetch every 256 eTSEC system clocks. This throttling threshold is supposed to trigger only when the controller has sufficient data to keep transmit active for the duration of the memory fetches. The state machine handling this threshold, however, fails to take large TOE frames into account. As a result, TOE=1 frames larger than 2500 bytes often see excess delays before start of transmission.

Impact: TOE=1 frames larger than 2500 bytes may see excess delays before start of transmission.

Workaround: Limit TOE=1 frames to less than 2500 bytes to avoid excess delays due to memory throttling.

When using packets larger than 2700 bytes, it is recommended to turn TOE off.

### eTSEC78: Controller may not be able to transmit pause frame during pause state

Description: When the Ethernet controller pauses transmit of normal frames after receiving a pause control

frame with PTV!=0, it should still be able to transmit pause control frames. The Ethernet controller, however, does not check whether the MAC is paused before initiating a start-of-frame request to the MAC. Once it has initiated a start-of-frame request, the Ethernet controller cannot initiate a pause control frame request until the normal frame completes transmission. Since the MAC will not transmit the normal frame until the pause time expires, this means the controller may be unable to transmit a pause frame while it is in pause state if there is a normal

frame ready to transmit.

Impact: The Ethernet controller may be unable to transmit a pause frame during pause state if a

normal frame is ready to transmit.

This applies to pause frame generation as a result of RxFIFO over threshold (ordinary flow control), free BDs below threshold (lossless flow control), or software-generated pause frame

(TCTRL[TFC\_PAUSE]).

Workaround: None

## eTSEC-A001: MAC: Pause time may be shorter than specified if transmit in progress

Description: When the Ethernet controller receives a pause frame with PTV!=0, and MACCFG1[Rx

Flow]=1, it completes transmitting any current frame in progress, then should pause for PTV\*512 bit times. The MAC, however, does not take the full transmission time of the current frame into account when calculating the Tx pause time, and may pause for 1-2 pause quanta

(512-1024 bit times) less than the PTV value.

Impact: The eTSEC transmitter may pause transmission for up to 1024 bit times less than requested in

a receive pause frame. If the PTV value does not contain at least 2 pause quanta worth of

margin, this may lead to receive buffer overflows in the link partner.

Since the transmit pause does not take effect until after the current frame completes transmitting, the link partner's pause frame generator must already include the maximum frame size as margin when calculating the pause time value to use to prevent overflow of the

receiver's buffers.

Workaround: Add 2 pause quanta to the pause time value used when generating pause frames to prevent

receive buffer overflow.

#### A-006502: Incomplete GRS or invalid parser state after receiving a 1- or 2-byte frame

Affects: eTSEC

Description: Ethernet standards define the minimum frame size as 64 bytes. The eTSEC controller also supports receiving short frames less than 64 bytes, and can accept frames more than 16 bytes and less than 64 bytes if RCTRL[RSF] = 1. Frames shorter than 17 bytes are supposed to be silently dropped with no side-effects. There are, however, two scenarios in which receiving frames <= 2 bytes cause erroneous behavior in the controller.

> In the first scenario, if the last frame (such as an illegal runt packet or a packet with RX ER asserted) received prior to asserting graceful receive stop (DMACTRL[GRS]=1) is <= 2 bytes, then the controller fails to signal graceful receive stop complete (IEVENT[GRSC]) even though the GRS has successfully executed and the receive logic is completely idle. Any subsequent receive frame that is larger than 2 bytes resets the state so the graceful stop can complete (IEVENT[GRSC] = 1). A MAC Rx reset also resets the state.

> In the second scenario, the parser and filer are enabled (RCTRL[PRSDEP] = 01,10,11). If a 1or 1.5-byte frame is received, the controller carries over some state from that frame to the next, causing the next frame to be parsed incorrectly. This, in turn, may cause incorrect parser results in RxFCB and incorrect filing (accept versus reject, or accept to wrong queue) for that following frame. The parser state recovers itself after receiving any frame >= 2 bytes in length.

Impact:

If software initiates a graceful receive stop after a 1- or 2-byte frame is received, the stop may not complete until another frame has been received.

A frame following a 1 or 1.5B frame may be parsed and filed incorrectly.

Workaround: For GRS scenario:

After asserting graceful receive stop (DMACTRL[GRS] = 1), initiate a timeout counter. The wait time is system and memory dependent, but a reasonable worst-case time is the receive time for a 9.6 Kbyte frame at 10/100/1000 Mbps. If IEVENT[GRSC] is still not set after the timeout, read the eTSEC register at offset 0xD1C. If bits 7-14 are the same as bits 23-30, the eTSEC Rx is assumed to be idle and the Rx can be safely reset. If the register fields are not equal, wait for another timeout period and check again.

MAX Rx reset procedure:

- 1) Clear MACCFG[RX\_EN].

- Wait three Rx clocks.

- 3) Set MACCFG2[RX\_EN].

### IEEE 1588\_14: TxPAL timestamp uses TxBD snoop enable instead of Tx data

Description: The DMACTRL register contains two snoop enable bits for Tx: TBDSEN for buffer descriptors

and TDSEN for frame data. Tx timestamp writes should use TDSEN to determine transaction

snoop enable, but use TBDSEN instead.

Impact: If DMACTRL[TBDSEN] = 0, Tx timestamp writes to memory will not be snooped by the core

regardless of the setting of DMACTRL[TDSEN].

If DMACTRL[TBDSEN] = 1, Tx timestamp writes to memory will be snooped by the core even

if DMACTRL[TDSEN] = 0.

**Workaround:** Set DMACTRL[TBDSEN] = 1 if snooping of Tx timestamp writes to memory is desired.

### IEEE 1588\_16: Odd prescale values not supported

**Description:** The 1588 timer prescale register (TMR\_PRSC) defines the timer prescale as follows:

PRSC\_OCK: Output clock division/prescale factor. Output clock is generated by dividing the timer input clock by this number. Programmed value in this field must be greater than 1. Any

value less than 1 is treated as 2.

The output pulse (TSEC\_TMR\_PPn) width should be 1x the output clock width. For odd

prescale values, the pulse width is 1.5x the output clock width instead.

**Impact:** Odd 1588 timer prescale values are not supported.

Workaround: Use only even timer prescale values.

## IEEE 1588\_17: Cannot use inverted 1588 reference clock when selecting eTSEC system clock as source

**Description:** The source of the 1588 reference clock can be selected with TMR\_CTRL[CKSEL] register bit

field, while the TMR\_CTRL[CIPH] register bit field allows the user to invert the selected 1588

reference clock.

If the eTSEC system clock is chosen as the source for the 1588 reference clock (TMR\_CTRL[CKSEL]=01), then selecting an inverted version of such clock (by setting

TMR\_CTRL[CIPH]=1) results in an improperly controlled 1588 reference clock, and boundedly

undefined errors.

Impact: Cannot select an inverted 1588 reference clock if the eTSEC system clock is chosen as the

source for the 1588 reference clock.

Workaround: None

#### IEEE 1588 19: Tx FIFO data parity error (DPE) may corrupt Tx timestamps if TMR CTRL[TRTPE]=1

**Description:** If TMR\_CTRL[TRPTE] = 1, the Ethernet controller writes Tx timestamp information for frames with TxFCB[PTP] = 1 to external memory in a PAL region. There is a queue of TxPAL addresses in the Ethernet controller that doesn't get cleared upon recovery from a Tx FIFO data parity error. As a result, if there were any frames with TxFCB[PTP]=1 in the Tx FIFO at the time the data parity error occurred (other than the frame with the error), a latent timestamp write for those frames may occur any time within the transmission of the first 8 TxBDs after DPE recovery. There may be up to three frames in the Tx FIFO in addition to the one with the parity error.

#### Example:

Suppose there are 4 frames in the Tx FIFO at time of the DPE, each with TxFCB[PTP] = 1 and each therefore using 2 BDs: BD0-BD7. When the DPE occurs, BD0 and BD1 are closed normally with an underflow indication, and BDs 2-7 are closed with an underrun indication, but TxPAL addresses for BD2, BD4 and BD6 are saved to a TxPAL queue and left valid. After the DPE recovery, the first 8 BDs transmitted trigger a write of invalid timestamp state to the TxPAL addresses of BD2, BD4 and BD6.

Impact:

If TMR CTRL[TRTPE]=1, data parity error may cause corruption of Tx timestamp data for PTP frames flushed due to the DPE.

Workaround: Transmit 8 or more non-TxPAL BDs which do not use any of the previously flushed PTP BDs, before allowing retransmission of those PTP BDs. These BDs must either be non-PTP frames (TxFCB[PTP]=0), or TMR CTRL[TRTPE] must be 0. This can be done for example by:

> Keeping the ring(s) containing the flushed PTP BDs in halt while enabling other ring(s) containing at least 8 ready BDs. The 8 BDs can be for frames already programmed for transmission, or new ones for dummy frames in a queue enabled just for the purpose of clearing the TxPAL state.

#### OR

Reordering the PTP BDs in the ring—moving them at least 8 entries down—so that least 8 other BDs in the ring are transmitted first.

In both cases, if the 8 BDs to be transmitted cannot be guaranteed to have TxFCB[PTP] = 0, then TMR CTRL[TRTPE] must be set to 0 until those 8 BDs have been transmitted. Note that while TMR CTRL[TRTPE] = 0, there will be no true Tx timestamp writes to memory for PTP frames, so it is preferable to ensure that only non-PTP frames are transmitted for the first 8 BDs.

Either workaround guarantees the true Tx timestamp write to memory for the flushed PTP frames (if enabled) will occur after the corrupted Tx timestamp write. Disabling TxPAL by setting TMR\_CTRL[TRTPE] = 0 does not prevent the data corruption.

No plans to fix Fix plan:

### IEEE 1588\_20: eTSEC 1588: Write to reserved 1588 register space causes system hang

**Description:** The IEEE 1588 control block contains a set of memory-mapped registers shared by all eTSEC controllers. These shared IEEE 1588 registers are located in the eTSEC1 controller memory space and support both read and write operations. The shared registers are located at the following addresses relative to the eTSEC1 base address 0x2\_4000:

- 0xE20 (TMR\_ADD)

- 0xE28 (TMR\_PRSC)

- 0xE30 (TMR\_OFF\_H)

- 0xE34 (TMR\_OFF\_L)

- 0xE40 (TMR\_ALARM1\_H)

- 0xE44 (TMR\_ALARM1\_L)

- 0xE48 (TMR\_ALARM2\_H)

- 0xE4C (TMR\_ALARM2\_L)

- 0xE80 (TMR\_FIPER1)

- 0xE84 (TMR\_FIPER2)

- 0xE88 (TIMER\_FIPER3)

Reads to 1588 shared registers from any other eTSEC return 0's. Writes to 1588 shared registers from any other eTSEC should be silently dropped, but instead cause a hang of the memory-mapped register IP interface.

**Impact:** A programming error (write to reserved address space) may cause a hang.

Workaround: Do not write to 1588 shared registers from any eTSEC other than eTSEC1.

## IEEE1588-A001: Incorrect received timestamp or dropped packet when 1588 timestamping is enabled

**Description:** When timestamping is enabled for all packets arriving on an Ethernet port (TMR\_CTRL[TE] =

1 and RCTRL[TS] = 1), the port may fail to properly recognize the timestamp point for received frames. As a result, the timestamp value for the frame may be larger than the correct value, or

the frame may be dropped.

**Impact:** For all modes except RMII, the timestamp value for a received frame may be larger than the

correct value, or the frame may be dropped.

This erratum does not affect the operation of the TRIGGER\_IN inputs, ALARM outputs, or

FIPER outputs.

This erratum does not affect the operation of an Ethernet port when time-stamping is disabled

(TMR\_CTRL[TE]=0 and RCTRL[TS]=0); HRESET default is disabled.

Workaround: There is no workaround for the issue other than disabling receive time-stamping

(RCTRL[TS]=0).

Fix plan: Fixed in Rev 1.1

## A-007734: Stale time stamps and over-flow conditions can occur when using an external 1588 input clock at certain frequencies

Affects: IEEE 1588

Description: When the time stamp logic is enabled using an external 1588 input clock at certain

frequencies, the eTSEC receiver can fail to update with the latest time stamp. This results in a stale time stamp in the Rx buffer padding even though eTSEC TMR RXTS is updated

correctly.

In addition, the eTSEC receiver can hang because of over-flow conditions. The setting of bit[6]

of eTSEC RSTAT indicates the over-flow condition has occurred.

**Impact:** User cannot use the full frequency ranges of the 1588 input clock as specified in the data

sheet:

17.85 MHz to 200 MHz for 1000 Mbps mode

3.57 MHz to 200 MHz for 100 Mbps mode

3.60 MHz to 200 MHz for 100 Mbps mode

• 0.36 MHz to 200 MHz for 10 Mbps mode

Workaround: Limit the 1588 input clock frequency to:

• 66 MHz to 200 MHz for 1000 Mbps mode

13.2 MHz to 200 MHz for 100 Mbps mode

• 1.32 MHz to 200 MHz for 10 Mbps mode

Limit the maximum frequency of the 1588 input clock to the CCB frequency if it is lower than

200 MHz.

## General14: Electrostatic Discharge (ESD) may fail to meet the 2KV Human body body model (HBM)

**Description:** HBM (Human Body Model) ESD testing has shown that some USB and SGMII / PCIe PHY

pins do not meet the 2kV HBM ESD criteria. HBM passes at 1kV. The following pins are

impacted:

USB\_DP, USB\_DM, USB\_RBIAS, USB\_VBUS, USB\_VDDA, USB\_VDDA\_BIAS, SD\_PLL\_TPA\_ANA, TXA, TXA, TXB, TXB, SD\_IMP\_CAL\_TX, SDAVDD, XPADVDD,

XCOREVDD

**Impact:** Excessive ESD can cause damage to the device.

Workaround: Ensure personnel and equipment used in handling of the device is properly grounded. Ensure

parts are handled in an environment that is compliant with current ESD standard

### General16: Enabling I<sup>2</sup>C could cause I<sup>2</sup>C bus freeze when other I<sup>2</sup>C devices communicate

**Description:** When the I<sup>2</sup>C controller is enabled by software, if the signal SCL is high and the signal SDA is low, and the I<sup>2</sup>C address matches the data pattern on the SDA bus right after the enabling, an ACK is issued on the bus. The ACK is issued because the I2C controller detects a START condition due to the nature of the SCL and SDA signals at the point of enablement. When this occurs, it may cause the I<sup>2</sup>C bus to freeze. However, it happens very rarely due to the need of two conditions occurring at the same time.

Impact:

Enabling the I<sup>2</sup>C controller may cause the I<sup>2</sup>C bus to freeze while other I<sup>2</sup>C devices communicate on the bus.

Workaround: Use one of the following options:

- Enable the I<sup>2</sup>C controller before starting any I<sup>2</sup>C communications on the bus. This is preferred solution.

- If the I<sup>2</sup>C is configured as a slave, implement the following steps:

- a. Software enables the device by setting I2CnCR[MEN] = 1, and start a timer.

- b. Delay for four I<sup>2</sup>C bus clocks.

- c. Check Bus Busy bit (I2CnSR[MBB])

```

if MBB == 0

Jump to Step 6; (Good condition. Go to normal operation.)

else

Disable device (I2CnCR[MEN] = 0)

```

- d. Reconfigure all the I<sup>2</sup>C registers if necessary.

- e. Go back to Step 1

- f. Normal operation.

### General17: DUART: Break detection triggered multiple times for a single break assertion

Description: A DUART break signal is defined as a logic zero being present on the UART data pin for a time longer than (START bit + Data bits + Parity bit + Stop bits). The break signal persists until the data signal rises to a logic one.

> A received break is detected by reading the ULSRn and checking for BI=1. This read to ULSRn will clear the BI bit. Once the break is detected, the normal handling of the break condition is to read the URBR to clear the ULSRn[DR] bit. The expected behavior is that the ULSRn[BI] and ULSRn[DR] bits will not get set again for the duration of the break signal assertion. However, the ULSRn[BI] and ULSRn[DR] bits will continue to get set each character period after they are cleared. This will continue for the entire duration of the break signal.

> At the end of the break signal, a random character may be falsely detected and received in the URBR, with the ULSRn[DR] being set.

Impact:

The ULSRn[BI] and ULSRn[DR] bits will get set multiple times, approximately once every character period, for a single break signal. A random character may be mistakenly received at the end of the break.

Workaround: The break is first detected when ULSRn is read and ULSRn[BI]=1. To prevent the problem from occuring, perform the following sequence when a break is detected:

- 1. Read URBRn, which will return a value of zero, and will clear the ULSRn[DR] bit

- 2. Delay at least 1 character period

- 3. Read URBRn again

ULSR[BI] will remain asserted for the duration of the break. The UART block will not trigger any additional interrupts for the duration of the break.

This workaround requires that the break signal be at least 2 character-lengths in duration.

This workaround applies to both polling and interrupt-driven implementations.

### PEX1: No support of PCI Express completions with BCM bit set (PCIX bridge interface)

Description: To satisfy certain PCI-X protocol constraints, a PCI-X Bridge or PCI-X Completer for a PCI-X burst read in some cases will set the Byte Count field in the first PCI-X transaction of the Split Completion sequence to indicate the size of just that first transaction instead of the entire burst read. When this occurs, the PCI-X Bridge/PCI-X Completer will also set the BCM bit in that first PCI-X transaction, to indicate that the Byte Count field has been modified from its normal usage. A PCI Express Memory Read Requester needs to correctly handle the case when a PCI-X Bridge/PCI-X Completer sets the BCM bit. PCI Express Completers will never set the BCM bit.

> The device does not expect the BCM to be set. A packet received with the BCM bit will cause unexpected behavior.

Impact:

The device does not support the BCM behavior described in the PCI Express standard, and may not support PCI Express to PCI-X bridges.

Workaround: None

### PEX2: DMA Interrupt descriptor race condition (IDRC)

Description: The DMA DONE bit is set and issues an interrupt before the buffer descriptor (BD) is written to

memory.

**Impact:** After detecting the interrupt, the software may read wrong data from the descriptor status.

Workaround: When serving the interrupt, Software must check that the done bit in the chain descriptor is set.

If it is not set, software should poll the DONE bit until it is set.

## PEX5: PCI Express LTSSM may fail to properly train with a link partner following HRESET#

**Description:** Following HRESET#, the PCI Express controller will enter the internal LTSSM (Link Training

and Status State Machine), and may fail to properly detect a receiver as defined in the PCI Express Base Specification. Failing to properly detect a receiver can be determined by reading the LTSSM State Status Registers (offset 0x404) in the PCI Express extended configuration space. When this failure has occurred the status code can be either 0 or 1h, indicating that it is

still in a detect state. If the link has properly trained, the status code will read 0x16h.

**Impact:** Following HRESET#, (or a hot swap and/or dynamic power up/down on the link partner) the

PCI Express controller may fail to properly train with an active link partner, causing the PCI

Express controller to hang.

Workaround: During PEX initialization sequence, once the serdes reset sequence is over (RDONE bit is set

in Serdes Reset Control Register - IMMRBAR offset 0xE\_3020), wait for 1 ms before bringing the pex controller out of reset (setting the link reset, pab reset and csr reset bits in pex control

register 1/2 - IMMRBAR offset 0x0\_0140/0x0\_0144)

### PEX7: Recovery from hot reset or link down

Description: The PCI Express CSB bridge enters a suspend mode as a result of a hot reset or link down event in either endpoint (EP) or root complex (RC) mode. When this happens, the PCI Express controller flushes all outstanding CSB transactions and does not accept new inbound transactions involving CSB and ATMU translation until the CSB bridge is unlocked, even though the link is automatically retrained properly and is stable in L0.

> The CSB bridge cannot be unlocked without a soft reset. Software running on the local CPU must wait until the PCI Express CSB bridge is idle before performing a soft reset as well as reenabling and reconfiguring the CSB bridge registers.

Further, even in RC mode, the PCI configuration space also gets reset as a result of a link down event (and not a hot reset event). This space needs to be reprogrammed during recovery.

A link down scenario can be caused by various reasons, and could occur even during the link negotiation phase of the initial link training coming out of a power-on reset. In this case, the LTSSM can temporarily go to L0, re-train after a quick link down, and then reach a stable linkup L0 state.

Note: If the MPC8308E initiated the link recovery, this is not considered a link down event and the PCI Express CSB bridge does not enter suspend mode. In this case, the device is fully operational when the link is back to L0 state and there is no need for a soft reset.

#### Impact:

When the system is in EP mode, the system will fail if the link goes up and the RC issues transactions involving CSB and ATMU translation to the endpoint before the PCI Express CSB bridge is unlocked.

Additionally, reconfiguring the CSB bridge registers and PCI configuration space (when in RC mode during a link down event) can complicate and slow down the software.