# ES\_P89LPC914 Errata sheet P89LPC914 Rev. 02 — 23 February 2010

**Errata sheet**

### **Document information**

| Info     | Content                                                                                                                                                          |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Keywords | P89LPC914 errata                                                                                                                                                 |

| Abstract | This errata sheet describes both the known functional problems and any deviations from the electrical specifications known at the release date of this document. |

|          | Each deviation is assigned a number and its history is tracked in a table at the end of the document.                                                            |

ES\_P89LPC914

Errata sheet P89LPC914

# **Revision history**

| Rev | Date     | Description                                                                                                                                                                                           |

|-----|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 02  | 20100223 | <ul> <li>The format of this errata sheet has been redesigned to comply with the new identity guidelines of NXP Semiconductors.</li> <li>Added Revision Identifier "A" and "C" information.</li> </ul> |

| 01  | 20080310 | Initial version                                                                                                                                                                                       |

# **Contact information**

For more information, please visit: <a href="http://www.nxp.com">http://www.nxp.com</a>

For sales office addresses, please send an email to: <a href="mailto:salesaddresses@nxp.com">salesaddresses@nxp.com</a>

# 1. Product identification

The P89LPC914 devices typically have the following top-side marking:

P89LPC914x x xxxxxxx xx xxYYWW R

The last letter in the last line (field 'R') will identify the device revision. This Errata Sheet covers the following revisions of the P89LPC914:

Table 1. Device revision table

| Revision identifier (R) | Revision description    |

|-------------------------|-------------------------|

| $\phi$                  | Initial device revision |

| 'A'                     | Second device revision  |

| 'C'                     | Third device revision   |

Field 'YY' states the year the device was manufactured. Field 'WW' states the week the device was manufactured during that year.

# 2. Errata overview

Table 2. Functional problems table

| Functional problems | Short description                                          | Fixed in revision |

|---------------------|------------------------------------------------------------|-------------------|

| DIVM.1              | Using DIVM in power-down mode                              | none              |

| I/O.1               | Port Configuration                                         | A                 |

| I/O.2               | Port 2.4 can draw additional power                         | A                 |

| ICP.1               | ICP Global Erase                                           | A                 |

| RESET.1             | External reset does not function correctly when using DIVM | Α                 |

| UART.1              | Breakdetect trips after 10 zero bits                       | none              |

Table 3. AC/DC deviations table

| AC/DC deviations | Short description | Fixed in revision |

|------------------|-------------------|-------------------|

| -                | -                 | -                 |

Table 4. Errata notes

| Note               | Short description               | Fixed in revision |

|--------------------|---------------------------------|-------------------|

| V <sub>DD</sub> .1 | V <sub>DD</sub> Power cycling   | С                 |

| IRC.1              | Internal RC oscillator accuracy | none              |

# 3. Functional problems detail

# 3.1 DIVM.1: Using DIVM in power-down mode

### Introduction:

The P89LPC914 has a DIVM register that can be used to divide the cclk down. Using DIVM can greatly reduce power when in active mode.

### **Problem:**

When DIVM is used in active mode and power-down mode is then entered the P89LPC914 can not be waken up from power down mode.

### Work-around:

Before entering powerdown mode set DIVM back to 0x00. This way the P89LPC914 will be operating full speed for one instruction before entering power-down mode. After the P89LPC914 has been waken up DIVM can be set back to its original value.

# 3.2 I/O.1: Port configuration

### Introduction:

The I/O ports of the P89LPC914 can be configured to 4 different modes by writing to the PxM1 and PxM2 registers. The default mode after Reset is 'Input Only'.

### **Problem:**

Coming out of Reset, the P89LPC914 port registers should be initialized as follows. Without executing this sequence, the P89LPC914 could consume additional power.

# Work-around:

Initialize the P89LPC914 ports in two steps:

Step 1: Configure all port registers with this initialization.

```

POM1 = 0x00;  // set P0 to quasi-bidirectional

P1M1 = 0x00;  // set P1 to quasi-bidirectional

P2M1 = 0x00;  // set P2 to quasi-bidirectional

P3M1 = 0x00;  // set P3 to quasi-bidirectional

```

Step 2: Configure the port pins on the P89LPC914 to their required mode **using only AND and OR** operations. Make sure to modify only the port pins available on the P89LPC914.

# 3.3 I/O.2: Port 2.4 can draw additional power

### Introduction:

Port 2.4 is a general purpose I/O pin.

### **Problem:**

P2.4 always has an active interanl pull-up, which will draw additional power when the port is written low.

### Work-around:

No known workaround.

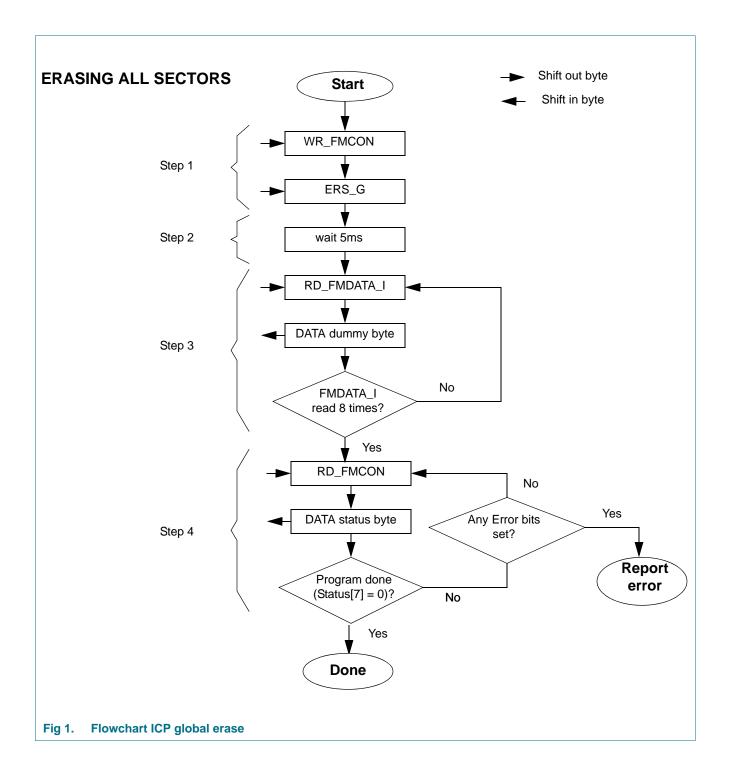

# 3.4 ICP.1: ICP Global Erase

### Introduction:

The P89LPC914 can be programmed using ICP (In Circuit Programming). One of the ICP functions is the Erase Global command, which will erase the entire chip including the security bytes and configuration information.

### **Problem:**

When giving the Erase Global command through the ICP interface the P89LPC914 will not clear the busy flag and stay busy forever.

### Work-around:

The workaround can be done in 4 steps:

- Step 1: Shift out the WR\_FMCON command followed by the Erase Global opcode.

- Step 2: Wait 5ms.

- Step 3: Do 8 dummy reads with the RD\_FMDATA\_I command.

- Step 4: Read FMCON until the busy flag gets cleared.

Please also see Figure 1.

# 3.5 RESET.1: External reset does not function correctly when using DIVM

### Introduction:

The P89LPC914 can be set up to use either an internal reset or an external reset pin on P1.5. The DIVM register can be used to divide down the internal CCLK down.

### **Problem:**

When the P89LPC914 is configured to have an external reset pin on P1.5 and in the program the DIVM register is programmed to a value different from 0x00 to slow down CCLK, then the next reset pulse will not generate a proper reset for the P89LPC914. A power cycle has to be applied for the P89LPC914 to start up again properly.

### Work-around:

Use the internal reset function.

# 3.6 UART.1: Breakdetect trips after 10 zero bits

### Introduction:

The UART on the P89LPC914 has the ability to detect a breakdetect signal, a break signal is a 11 bit long low signal on the RxD input of the UART.

### **Problem:**

The breakdetect flag will be set after 10 low bits on the RxD input of the UART. When 9 bit mode is used and all 9 data bits are 0 and the start bit is zero this will be detected as a breakdetect.

## Work-around:

No known workaround.

# 4. AC/DC deviations detail

# 4.1 No known errata

# 5. Errata notes

# 5.1 V<sub>DD</sub>.1: V<sub>DD</sub> power cycling

To generate a proper Power-On-Reset (POR),  $V_{DD}$  must have dropped below 0.2V before being powered back up. Power-cycling without  $V_{DD}$  having dropped below 0.2V may result in incorrect Program Counter values.

Please also see the VPOR specification in LPC912 Datasheet, DC electrical characteristics. Section 8.15 (Reset) states that during a power cycle, V<sub>DD</sub> must fall below VPOR.

# 5.2 IRC.1: Internal RC oscillator accuracy

To be able to guarantee the Internal RC oscillator accuracy over the full operating range the  $V_{DD}$  supply has to be decoupled sufficiently. Sufficient decoupling is dependant on the noise level in the application, typically a 0.1uF should be sufficient for most applications.

Noise on the  $V_{DD}$  supply pins can cause the Internal RC oscillator to go slightly outside of the specified range.

# 6. Legal information

# 6.1 Definitions

**Draft** — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.

### 6.2 Disclaimers

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information.

In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the *Terms and conditions of commercial sale* of NXP Semiconductors.

Right to make changes — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in medical, military, aircraft, space or life support equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors accepts no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on a weakness or default in the customer application/use or the application/use of customer's third party customer(s) (hereinafter both referred to as "Application"). It is customer's sole responsibility to check whether the NXP Semiconductors product is suitable and fit for the Application planned. Customer has to do all necessary testing for the Application in order to avoid a default of the Application and the product. NXP Semiconductors does not accept any liability in this respect.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from national authorities.

### 6.3 Trademarks

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

# 7. Contents

| 1   | Product identification                            | . 3 |

|-----|---------------------------------------------------|-----|

| 2   | Errata overview                                   | . 3 |

| 3   | Functional problems detail                        | . 4 |

| 3.1 | DIVM.1: Using DIVM in power-down mode             |     |

|     | Introduction:                                     |     |

|     | Problem:                                          |     |

|     | Work-around:                                      |     |

| 3.2 | I/O.1: Port configuration                         |     |

|     | Introduction:                                     |     |

|     | Problem:                                          |     |

| 3.3 | I/O.2: Port 2.4 can draw additional power         |     |

| 5.5 | Introduction:                                     |     |

|     | Problem:                                          |     |

|     | Work-around:                                      |     |

| 3.4 | ICP.1: ICP Global Erase                           |     |

|     | Introduction:                                     |     |

|     | Problem:                                          | 5   |

|     | Work-around:                                      | 5   |

| 3.5 | RESET.1: External reset does not function         | _   |

|     | correctly when using DIVM                         |     |

|     | Introduction:                                     |     |

|     | Problem:                                          |     |

| 3.6 | UART.1: Breakdetect trips after 10 zero bits      |     |

| 5.0 | Introduction:                                     |     |

|     | Problem:                                          |     |

|     | Work-around:                                      | 7   |

| 4   | AC/DC deviations detail                           | . 7 |

| 4.1 | No known errata                                   |     |

| 5   | Errata notes                                      |     |

| 5.1 | V <sub>DD</sub> .1: V <sub>DD</sub> power cycling |     |

| 5.2 | IRC.1: Internal RC oscillator accuracy            |     |

| 6   | Legal information                                 |     |

| 6.1 | Definitions                                       |     |

| 6.2 | Disclaimers                                       |     |

| 6.3 | Trademarks                                        | . 9 |

| 7   | Contents                                          | 10  |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.