**Errata sheet COMPANY PUBLIC**

#### **Document information**

| Information | Content                                                                                                                                                                                                                                    |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Keywords    | FXLS8962AF                                                                                                                                                                                                                                 |

| Abstract    | This errata sheet describes the known functional problems and/or deviations from the product electrical specifications as of the release date of this document. Each deviation is assigned a number and its history is tracked in a table. |

## **1** Revision history

| Table 1. Revision history |          |                  |  |  |  |  |

|---------------------------|----------|------------------|--|--|--|--|

| Rev                       | Date     | Description      |  |  |  |  |

| 1                         | 20171221 | Added E1, E2, E3 |  |  |  |  |

Rev. 1 — 21 December 2017

## 2 Product identification

The WHO\_AM\_I register (address 13h) identifies the device.

The PROD\_REV register (address 12h) identifies the device revision.

This Errata sheet covers the following devices:

Table 2. Device identification table

| Identifier | WHO_AM_I | PROD_REV | Device     | Revision |

|------------|----------|----------|------------|----------|

| 'A'        | 62h      | 11h      | FXLS8962AF | 1.0      |

## 3 Errata overview

#### Table 3. Functional problems table

| Functional problems | Short description                                                                 | Identifier | Detailed description |

|---------------------|-----------------------------------------------------------------------------------|------------|----------------------|

| E1                  | Noise coupling in analog front end (AFE) measurements during serial communication | 'A'        | Section 4.1          |

| E2                  | Unintended pulse during boot phase                                                | 'A'        | Section 4.2          |

| E3                  | FIFO burst read operation error using I2C interface                               | 'A'        | Section 4.3          |

## 4 Functional problems detail

# 4.1 E1: Noise coupling in analog front end (AFE) measurements during serial communication

#### Introduction

This erratum is related to the noise coupling in sensor measurements when serial communications (through  $I^2C$  or SPI) overlaps with the measurement phase of the device.

#### Problem

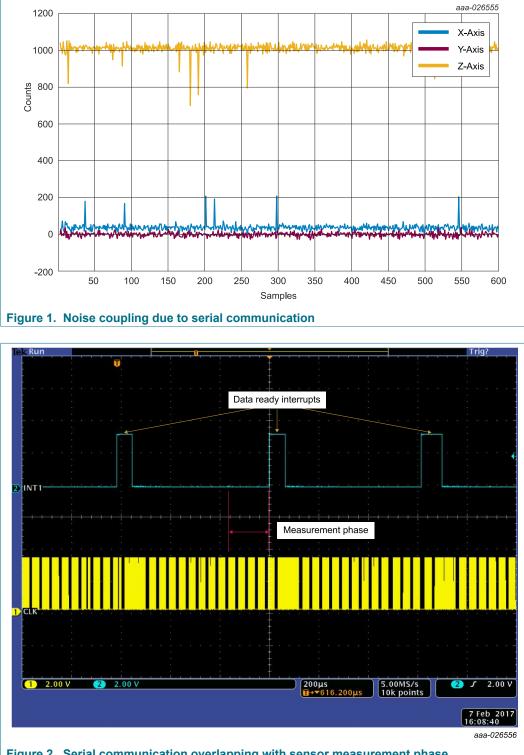

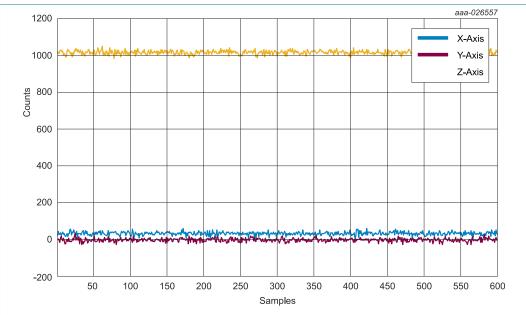

Serial bus signals (I<sup>2</sup>C/SPI) through the SA0, SPI\_MISO, SPI\_MOSI, SPI\_DATA, SDA, SCL and SCLK pins couple noise to the sensor's internal voltage shield. If communication occurs during the measurement phase of the device, then the coupled noise to the voltage shield affects the magnitude of the current measurements (see <u>Figure 1</u> and <u>Figure 2</u>), causing the device to exceed its noise specification.

Errata sheet - FXLS8962AF

Figure 2. Serial communication overlapping with sensor measurement phase

### Workaround

Reduce the susceptibility of the sensor measurements to induced noise by minimizing the communication traffic on the serial interface during the measurement phase of the

ES\_FXLS8962AF Errata sheet **COMPANY PUBLIC**

Errata sheet - FXLS8962AF

sensor. Configure the system such that the host MCU collects sensor data using data ready interrupts before the next measurement phase begins. (see <u>Figure 3</u> and <u>Figure 4</u>).

#### Using data ready interrupts

The data ready interrupt in FXLS8962 is enabled using the INT\_EN register (address 20h) and INT\_PIN\_SEL register (address 21h) (<u>Table 4</u> and <u>Table 5</u>).

- 1. Enable **INT\_EN[**DRDY\_EN].

- Map the data ready interrupt to one of the INTx pins available on the device. Set DRDY\_INT2 bit to route data ready interrupt to INT2 pin or clear the bit to route to INT1 pin.

#### Note:

In the case of  $BT_MODE = V_{DD}$  (motion detect mode), only INT1 pin can be used. The INT2 pin function is reserved for the boot output pulse and, therefore, is not available for this purpose.

Also, when the INT2 pin is configured for the external trigger function, for example, when **SENS\_CONFIG4[**INT2\_FUNC**]** = 1, a logic '1' value in DRDY\_INT2 bit field is ignored.

| Bit                 | 7       | 6      | 5              | 4              | 3             | 2       | 1        | 0               |

|---------------------|---------|--------|----------------|----------------|---------------|---------|----------|-----------------|

| Name                | DRDY_EN | BUF_EN | SDCD_<br>OT_EN | SDCD_<br>WT_EN | ORIEN<br>T_EN | ASLP_EN | BOOT_DIS | WAKE_<br>OUT_EN |

| Reset (BT_MODE = 0) | 0       | 0      | 0              | 0              | 0             | 0       | 0        | 0               |

| Reset (BT_MODE = 1) | 0       | 0      | 1              | 0              | 0             | 0       | 0        | 0               |

| Access              | R/W     | R/W    | R/W            | R/W            | R/W           | R/W     | R/W      | R/W             |

#### Table 4. INT\_EN register (address 20h)

#### Table 5. INT\_PIN\_SEL register (address 21h)

| Bit    | 7         | 6   | 5                | 4                | 3               | 2         | 1         | 0                 |

|--------|-----------|-----|------------------|------------------|-----------------|-----------|-----------|-------------------|

| Read   | DRDY_INT2 | —   | SDCD_<br>OT_INT2 | SDCD_<br>WT_INT2 | ORIEN<br>T_INT2 | ASLP_INT2 | BOOT_INT2 | WAKE_O<br>UT_INT2 |

| Reset  | 0         | 0   | 0                | 0                | 0               | 0         | 0         | 0                 |

| Access | R/W       | R/W | R/W              | R/W              | R/W             | R/W       | R/W       | R/W               |

#### Time window to perform serial communication after receiving data ready interrupt

Note that upon reception of the data ready interrupt on the selected interrupt pin, the host must quickly do a burst read of the data registers before the next measurement cycle begins for the successive data sample. This ensures that the bus communications associated with reading the current data sample does not couple noise to the successive data sample measurement.

In addition, if FXLS8962 is used in a shared I<sup>2</sup>C/SPI bus along with other devices, the communication with other devices must complete before the next measurement cycle in FXLS8962 begins, in order to prevent bus traffic from inducing noise to the sensor measurement.

#### Table 6. Measurement phase timings

Sample size = 30

| Mean (μs) | Standard deviation (µs) |

|-----------|-------------------------|

| 126.1     | 0.88                    |

Errata sheet - FXLS8962AF

<u>Table 7</u> identifies the maximum time window (from the starting edge of the data ready interrupt) within which all the serial communications must complete before the measurement phase for the next sample begins.

## Table 7. Time window allowed for serial communications after the rising edge of the data ready interrupt

Average value from 30 samples.

| Mode                   | Time (μs)                                                                                                                                                  |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LPM<br>(ODR dependent) | $Time \ window = \frac{1.0 \times 10^6}{1.1 \times ODR} - 1.1 \ \times measurement \ phase$<br>where: measurement phase = 126.1 µs (Table 6),              |

| НРМ                    | Time window = $\frac{1.0 \times 10^6}{1.1 \times 3200} - 1.1 \times measurement phase = 145.38$<br>where: measurement phase = 126.1 µs ( <u>Table 6</u> ), |

For example, with the device operating with ODR = 200 Hz in LPM mode, the time window allowed for serial communications after the starting edge of the DRDY interrupt =  $4406 \ \mu$ s.

#### **Fix plan**

None.

### 4.2 E2: Unintended pulse during boot phase

#### Introduction

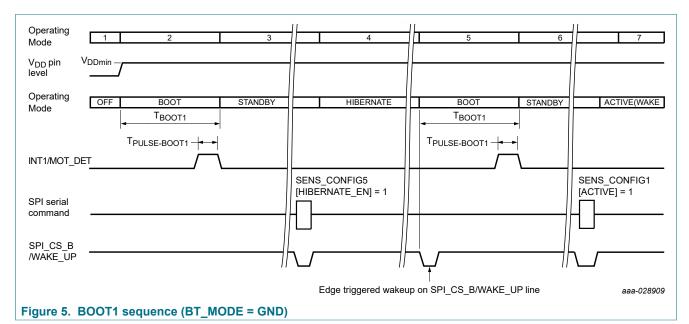

During boot phase execution of FXLS8962AF with BT\_MODE = GND, the device is initialized and any default configuration parameters are loaded from OTP memory. When this phase is complete, the SRC\_BOOT bit is set and a  $T_{PULSE-BOOT1}$  ms pulse may be signaled on either one of the INT1/2 pins (defaults to enabled on the INT1 pin after POR) (see Figure 5).

### **NXP Semiconductors**

## ES\_FXLS8962AF

Errata sheet - FXLS8962AF

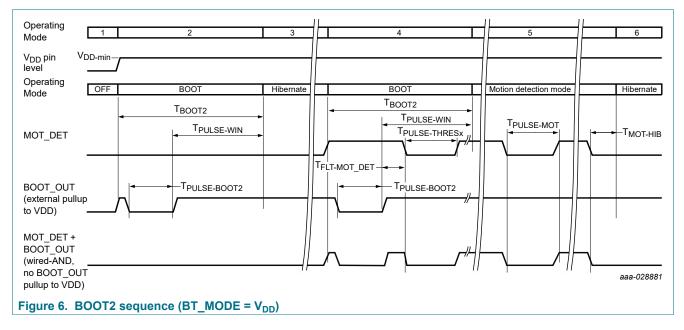

Similarly, during boot phase execution with BT\_MODE = VDD, this device is initialized and any default configuration parameters are loaded from OTP memory, along with any default Motion Detection function specific parameters. When this phase is complete, the SRC\_BOOT bit is set and a  $T_{PULSE-BOOT2}$  ms pulse is signaled on the INT2 pin (see Figure 6).

**Note:** With BT\_MODE = VDD, the boot pulse is routed to the INT2 pin and cannot be routed to the INT1 pin.

#### Problem

An unintended pulse occurs just before the occurrence of  $T_{PULSE-BOOT1}$  or  $T_{PULSE_BOOT2}$  under the following boot execution scenarios:

- Power on Reset (POR) when BT\_MODE = GND

- POR when BT\_MODE = VDD

- Soft reset when BT\_MODE = VDD

The unintended pulse leads to a double pulse observation.

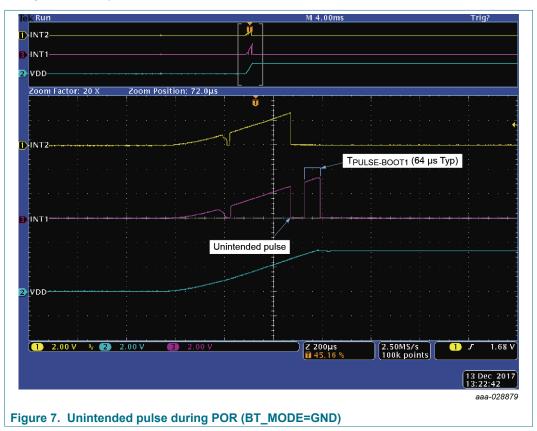

#### POR when **BT\_MODE = GND**

Upon POR, the boot pulse is issued for  $T_{PULSE-BOOT1}$  ms at the completion of boot phase on either the INT1 or INT2 lines depending on the device configuration (see Figure 5). However, an unintended pulse approximately 50 µs in duration occurs just before the starting edge of the boot pulse, as shown in Figure 7.

**Note:** The unintended pulse occurs on POR only when there is a pull-up resistor on the configured interrupt.

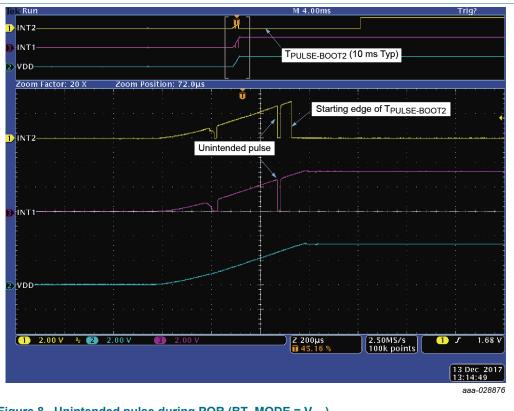

#### POR when BT\_MODE = VDD

Upon POR, the boot pulse is issued for  $T_{PULSE-BOOT2}$  ms upon completion of the boot phase (see <u>Figure 6</u>). However, an unintended pulse approximately 10 µs in duration occurs just before the starting edge of the  $T_{PULSE-BOOT2}$  pulse, as shown in <u>Figure 8</u>.

Errata sheet - FXLS8962AF

Figure 8. Unintended pulse during POR (BT\_MODE = V<sub>DD</sub>)

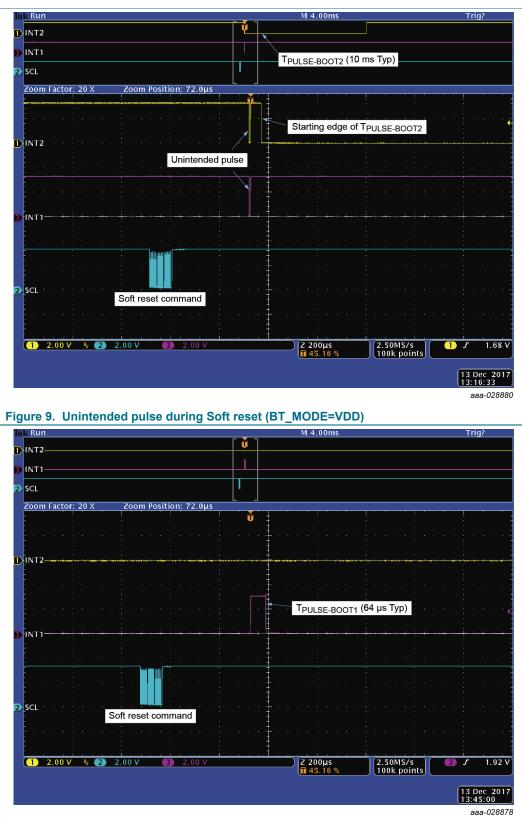

#### Soft reset when BT\_MODE = VDD

Upon issuing a soft reset command through setting the RST bit in SENS\_CONFIG1 (address 15h) register (see <u>Table 8</u>), the boot pulse is issued for  $T_{PULSE-BOOT2}$  ms upon completion of the boot phase (see <u>Figure 6</u>). However, an unintended pulse approximately 10 µs in duration occurs just before the starting edge of the  $T_{PULSE-BOOT2}$  pulse, as shown in <u>Figure 9</u>.

**Note:** No unintended pulse is seen on issuing a soft reset command when BT\_MODE = GND and when .setting the RST bit in the SENS\_CONFIG1 register (see Figure 10).

| Bit                 | 7   | 6       | 5         | 4      | 3     | 2   | 1     | 0      |

|---------------------|-----|---------|-----------|--------|-------|-----|-------|--------|

| Name                | RST | ST_AXIS | _SEL[1:0] | ST_POL | SPI_M | FSR | [1:0] | ACTIVE |

| Reset (BT_MODE = 0) | 0   | 0       | 0         | 0      | 0     | 0   | 0     | 0      |

| Reset (BT_MODE = 1) | 0   | 0       | 0         | 0      | 0     | 0   | 1     | 1      |

| Access              | R/W | R/W     | R/W       | R/W    | R/W   | R/W | R/W   | R/W    |

#### Table 8. SENS\_CONFIG1 register (address 15h) bit allocation

Errata sheet - FXLS8962AF

Figure 10. No unintended pulse during soft reset (BT\_MODE=GND)

ES\_FXLS8962AF Errata sheet COMPANY PUBLIC

#### Workaround

#### Workaround 1

To avoid the unintended pulse from being mistaken for a boot pulse, the host MCU should measure the time between the starting and the ending edges of the pulse and validate it with boot pulse timing parameters. Typical boot pulse timing parameters for  $T_{PULSE-BOOT1}$  is 64 µs and  $T_{PULSE-BOOT2}$  is 10 ms.

#### Workaround 2

Alternatively, if the host MCU enables the sensor VDD supply under software control, or if the boot sequence is initialized through a soft-reset command, configure the host software to ignore the first edge triggered interrupt corresponding to the unintended boot pulse event (rising edge when BT\_MODE = GND or falling edge when BT\_MODE = VDD).

#### **Fix plan**

None.

### 4.3 E3: FIFO burst read operation error using I2C interface

#### Introduction

FXLS8962AF has a 32-sample FIFO buffer that can hold up to 144 bytes of data (32 12bit X, Y, Z data triplets) at a time.

The FIFO buffer is intended for saving power by allowing the host MCU to read out multiple samples using a burst read operation.

#### Problem

In I<sup>2</sup>C mode, a burst read attempt for three or more samples results in incorrect data beginning with the third sample. For example, a burst read attempt for 144 bytes of data results in unique and correct data for samples 1 and 2, but incorrect data starting from sample 3. The data returned starting with sample 3 is a replica of sample 2 (see <u>Table 8</u>), due the FIFO read pointer not incrementing as expected and continuing to point to sample 2.

Additionally, as a result of the FIFO read pointer not incrementing, the buffer sample counter BUF\_CNT[5:0] in BUF\_STATUS register (0Bh) does not decremented as expected.

| Sample No. | X  | Y  | Z    | Buffer count<br>(BUF_CNT) |

|------------|----|----|------|---------------------------|

| 1          | 29 | 34 | 1024 | 31                        |

| 2          | 23 | 32 | 1019 | 31                        |

| 3          | 23 | 32 | 1019 | 31                        |

| 4          | 23 | 32 | 1019 | 31                        |

Table 9. Example of incorrect data starting at sample 3 (burst read - I<sup>2</sup>C)

© NXP B.V. 2017. All rights reserved.

### **NXP Semiconductors**

#### Errata sheet - FXLS8962AF

| Sample No.           | X  | Y  | Z    | Buffer count<br>(BUF_CNT) |

|----------------------|----|----|------|---------------------------|

| 5 and so on up to 32 | 23 | 32 | 1019 | 31                        |

#### Workaround

#### Workaround 1 (preferred)

Use SPI interface.

#### Workaround 2 (interface restricted to I<sup>2</sup>C)

Limit the burst read operation to a discrete sample frame block. For example, read the 32-sample FIFO as 32 one-sample frame (6 bytes) burst reads. In this case, since each burst read consists of one sample, the FIFO read pointer properly increments automatically to the next sample frame through all samples. Additionally, the buffer counter BUF\_CNT[5:0] in BUF\_STATUS register (0Bh) properly decrements as each discrete sample frame is read. Thus, all samples are read as intended (see <u>Table 9</u>), and the undesirable behavior is avoided.

#### Table 10. Reading 6 bytes of data (1 sample at a time)

| Sample No.           | X  | Y  | Z    | Buffer count<br>(BUF_CNT) |

|----------------------|----|----|------|---------------------------|

| 1                    | 29 | 34 | 1024 | 31                        |

| 2                    | 23 | 32 | 1019 | 30                        |

| 3                    | 19 | 22 | 1020 | 29                        |

| 4                    | 18 | 27 | 1027 | 28                        |

| 5 and so on up to 32 | 19 | 30 | 1030 | 27                        |

#### **Fix plan**

None.

Errata sheet - FXLS8962AF

## 5 Legal information

## 5.1 Definitions

**Draft** — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.

### 5.2 Disclaimers

Limited warranty and liability - Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. NXP Semiconductors takes no responsibility for the content in this document if provided by an information source outside of NXP Semiconductors. In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory. Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of NXF Semiconductors.

**Right to make changes** — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors and its suppliers accept no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

Applications — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification. Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products. NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications

and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this respect.

Limiting values — Stress above one or more limiting values (as defined in the Absolute Maximum Ratings System of IEC 60134) will cause permanent damage to the device. Limiting values are stress ratings only and (proper) operation of the device at these or any other conditions above those given in the Recommended operating conditions section (if present) or the Characteristics sections of this document is not warranted. Constant or repeated exposure to limiting values will permanently and irreversibly affect the quality and reliability of the device.

Terms and conditions of commercial sale — NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at http://www.nxp.com/profile/terms, unless otherwise agreed in a valid written individual agreement. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. NXP Semiconductors hereby expressly objects to applying the customer's general terms and conditions with regard to the purchase of NXP Semiconductors products by customer.

**No offer to sell or license** — Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights.

**Quick reference data** — The Quick reference data is an extract of the product data given in the Limiting values and Characteristics sections of this document, and as such is not complete, exhaustive or legally binding.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

Non-automotive gualified products — Unless this data sheet expressly states that this specific NXP Semiconductors product is automotive qualified, the product is not suitable for automotive use. It is neither qualified nor tested in accordance with automotive testing or application requirements. NXP Semiconductors accepts no liability for inclusion and/or use of nonautomotive qualified products in automotive equipment or applications. In the event that customer uses the product for design-in and use in automotive applications to automotive specifications and standards, customer (a) shall use the product without NXP Semiconductors' warranty of the product for such automotive applications, use and specifications, and (b) whenever customer uses the product for automotive applications beyond NXP Semiconductors' specifications such use shall be solely at customer's own risk, and (c) customer fully indemnifies NXP Semiconductors for any liability, damages or failed product claims resulting from customer design and use of the product for automotive applications beyond NXP Semiconductors' standard warranty and NXP Semiconductors' product specifications

**Translations** — A non-English (translated) version of a document is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.

### 5.3 Trademarks

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

I<sup>2</sup>C-bus — logo is a trademark of NXP B.V.

### **NXP Semiconductors**

# ES\_FXLS8962AF

Errata sheet - FXLS8962AF

## Contents

| 1   | Revision history                             | 2  |

|-----|----------------------------------------------|----|

| 2   | Product identification                       |    |

| 3   | Errata overview                              | 3  |

| 4   | Functional problems detail                   | 3  |

| 4.1 | E1: Noise coupling in analog front end (AFE) |    |

|     | measurements during serial communication .   | 3  |

| 4.2 | E2: Unintended pulse during boot phase       | 7  |

| 4.3 | E3: FIFO burst read operation error using    |    |

|     | I2C interface                                | 12 |

| 5   | Legal information                            | 14 |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.

© NXP B.V. 2017.

All rights reserved.

For more information, please visit: http://www.nxp.com For sales office addresses, please send an email to: salesaddresses@nxp.com

Date of release: 21 December 2017 Document identifier: ES\_FXLS8962AF