Process Clarification

### Freescale Semiconductor, Inc.

Neil Farnham

TECD Applications

#### 1. Abstract

This Engineering Note attempts to clarify documentation on the TouCAN Receive Process.

### 2. TouCAN Receive Process

To be able to receive CAN frames, the CPU must prepare one or more Message Buffers for reception by executing the following steps:

- Write '0000' to the Code field of the Control and Status word to keep the MB inactive

- Write the ID word

- Write '0100' to the Code field of the Control and Status word to activate the MB

The first and last steps are mandatory. The first write to the Control and Status word is important in case there was a pending reception or transmission. The write operation immediately deactivates the MB, removing it from any currently ongoing arbitration or matching process, giving time for the CPU to program the rest of the MB. Once the MB is activated in the third step, it will be able to receive CAN frames that match the programmed ID. At the end of a successful reception, the MB is updated by the MBM as follows:

- The value of the Free Running Timer is written into the Time Stamp field.

- The received ID, Data (8 bytes at most) and Length fields are stored.

- The Code field in the Control and Status word is updated.

- A status flag is set in the Interrupt Flag Register and an interrupt is generated if allowed by the corresponding Interrupt Mask Register bit.

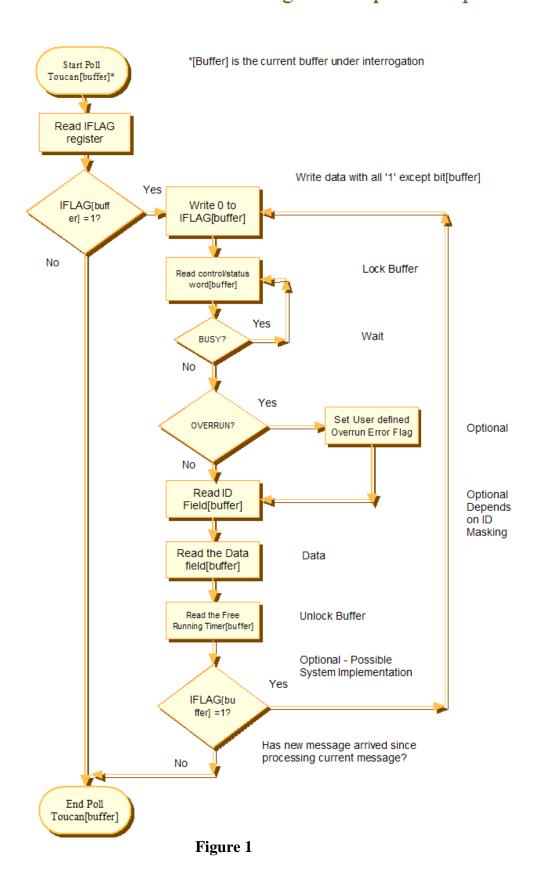

Upon receiving the MB interrupt, the CPU should service the received frame using the following procedure:

- Read the Control and Status word (mandatory activates an internal lock for this buffer)

- Read the ID field (optional needed only if a mask was used)

- Read the Data field

- Read the Free Running Timer (optional releases the internal lock)

Upon reading the Control and Status word, if the BUSY bit is set in the Code field, then the CPU should defer the access to the MB until this bit is negated. Reading the Free Running Timer is not mandatory. If not executed the MB remains locked, unless the CPU reads the C/S word of another MB. Note that only a single MB is locked at a time. The only mandatory CPU read operation is the one on the Control and Status word to assure data coherency.

Once an MB is read, a new frame that arrives will not set the code to OVERRUN. It will remain FULL. There is no need to write to the C/S word to detect overrun.

If the MB is FULL and a new frame is overwritten to this MB before the CPU had time to read it, the code is automatically updated to OVERRUN.

If the code indicates OVERRUN but the CPU reads the C/S word and then unlocks the MB, when a new frame is written to the MB the code returns to FULL.

If the code already indicates OVERRUN, and yet another new frame must be written, the MB will be overwritten again, and the code will remain OVERRUN.

The CPU should synchronize to frame reception by the status flag bit for the specific MB in one of the IFLAG Registers and not by the Code field of that MB.

Polling the Code field does not work because once a frame was received and the CPU services the MB (by reading the C/S word followed by unlocking the MB), the Code field will not return to EMPTY. It will remain FULL. If the CPU tries to workaround this behavior by writing to the C/S word to force an EMPTY code after reading the MB, the MB is actually deactivated from any currently

ongoing matching process. As a result, a newly received frame matching the ID of that MB may be lost. In summary: *never do polling by reading directly the C/S word of the MBs. Instead, read the IFLAG registers.*

Note that the received ID field is always stored in the matching MB, thus the contents of the ID field in an MB may change if the match was due to masking.

See flow in Figure 1 for TouCAN receive process polling technique sample.

## Toucan Receive Process Polling Technique Example

### THIS PAGE INTENTIONALLY LEFT BLANK

### THIS PAGE INTENTIONALLY LEFT BLANK

### THIS PAGE INTENTIONALLY LEFT BLANK

#### **HOW TO REACH US:**

#### USA / EUROPE / Locations Not Listed:

Motorola Literature Distribution P.O. Box 5405 Denver, Colorado 80217 1-800-521-6274 or 480-768-2130

#### JAPAN:

Motorola Japan Ltd. SPS, Technical Information Center 3-20-1, Minami-Azabu Minato-ku Tokyo, 106-8573 Japan 81-3-3440-3569

#### ASIA/PACIFIC:

Motorola Semiconductors H.K. Ltd. Silicon Harbour Centre 2 Dai King Street Tai Po Industrial Estate Tai Po, N.T., Hong Kong 852-26668334

#### **HOME PAGE:**

http://motorola.com/semiconductors

Information in this document is provided solely to enable system and software implementers to use Motorola products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Motorola data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part.

MOTOROLA and the Stylized M Logo are registered in the U.S. Patent and Trademark Office. The described product contains a PowerPC processor core. The PowerPC name is a trademark of IBM Corp. and used under license. The described product is a PowerPC microprocessor. The PowerPC name is a trademark of IBM Corp. and used under license. The described product is a PowerPC microprocessor core. The PowerPC name is a trademark of IBM Corp. and is used under license. The PowerPC name is a trademark of IBM Corp. and is used under license. All other product or service names are the property of their respective owners. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

© Motorola, Inc. 2004

EB634/D Rev. 0