# EB00913

# LPDDR2/LPDDR3 Parameter Optimizations for i.MX 7ULP

Rev. 0 — 06/2020 Engineering Bulletin

Contents

1 Introduction...... 1

this document.....1

optimize the DDR interface...... 3

4 References..... 4

2 LPDDR2/3 parameters covered by

3 General recommendations to

by: NXP Semiconductors

### 1 Introduction

The intent of this document is to describe the configuration for specific LPDDR2/3 parameters that can help you to achieve the best performance as well as debug target application hardware.

The software and hardware modifications recommended in this document are based on i.MX 7ULP evaluation using NXP software and validation development boards. It is important to highlight that i.MX 7ULP LPDDR2/3

achieved 380 MHz performance, confirmed by the product test data and bench long duration stress testing.

### 2 LPDDR2/3 parameters covered by this document

The following LPDDR2/3 parameters are covered by this document:

- · DDR clock configuration

- · Duty cycle

- · VIX (differential clock crosspoint voltage)

- · IO driver strength adjustment

- · IO per-bit de-skew

### 2.1 DDR clock configuration

It is recommended to use SCG1 APLL:PFD0 as the clock source for the DDR interface. PFD0 is specifically tuned to provide more precise duty cycle accuracy over process variation.

The LPDDR2/3 maximum frequency for i.MX 7ULP is 380.16 MHz, which corresponds to the following configuration (combination of APLLCFG and available in the 7ULP reference manual)

APLLvco Frequency = Fref \* (MULT + NUM/DENOM)

#### PFD Clock Frequency = APLLvco output frequency \* 18/frac value

The APLL frequency is tuned for operation at 528 MHz, so it is recommended for the DDR clock to use a combination of MULT and NUM/DENOM that matches 528 MHz.

For example, if a 24-MHz crystal is used for Fref (reference clock), then you should configure 22 for MULT and keep NUM/DENOM at the default values (or DENOM>>NUM). The i.MX 7ULP validation is performed with NUM = 0.

The final frequency is achieved by the fractional value adjustment. 380.16 MHz is achieved with PFD = 25.

### 2.2 Duty cycle

There are two configurations available in i.MX 7ULP for adjusting the DDR clock duty cycle.

#### 2.2.1 DDR IO duty cycle configuration

The DDR IO configuration reference is in the i.MX7ULP Reference Manual (document IMX7ULPRM) section "IOMUXC1 memory map".

DDR IO duty cycle adjustment is available for both DDR differential clocks and DDR single IO pins and corresponds to the DCYCLE\_TRIM parameter. The description extracted from the documentation is as follows:

- DCYCLE\_TRIM: Duty Cycle Control Field

- 00 DCYCLE\_TRIM\_0\_no\_duty\_cycle\_change no duty cycle change

- 01 DCYCLE\_TRIM\_1\_duty\_cycle\_increased duty cycle increased ~3.7 %

- EXAMPLE: from 46.3 % HIGH / 53.7 % LOW -> 50 % HIGH / 50 % LOW

- 10 DCYCLE\_TRIM\_2\_duty\_cycle\_decreased duty cycle decreased ~3.7 %

- EXAMPLE: from 53.7 % HIGH / 46.3 % LOW -> 50 % HIGH / 50 % LOW

- 11 DCYCLE\_TRIM\_3\_no\_duty\_cycle\_change no duty cycle change

#### 2.2.2 MMDC MPDCCR register

Additional duty cycle adjustment is available at DDR controller register MMDC MPDCCR. See the detailed description in the i.MX 7ULP Reference Manual (document IMX7ULPRM).

The differential DQS3-0 duty cycle can be adjusted by ~1.5 %, independently for read and write paths.

Differential CK0 has two steps of ~1.5 % duty cycle adjustment that can be programmed independently.

Any duty cycle adjustments must be applied before running the calibration. NXP i.MX 7ULP development boards achieve the best performance results with the default configuration values.

### 2.3 VIX (differential clock crosspoint voltage)

DDR IO VIX adjustment is available only for DDR differential clocks (DDR\_CLK0 and DDR\_CLK0\_B) and strobes (DDR\_DQS[0-3] and DDR\_DQS[0-3]\_B). The crosspoint adjustment is controlled by the CRPOINT\_TRIM field in the pad control registers IOMUXC1\_DDR\_SW\_PAD\_CTL\_PAD\_DDR\_CLK0 and IOMUXC1\_DDR\_SW\_PAD\_CTL\_PAD\_DDR\_DQSn.

The description extracted from the reference manual is as follows:

- Crosspoint Adjustment Field:

- 00 CRPOINT\_TRIM\_0\_no\_output\_crosspoint\_Vix\_change no output crosspoint (Vix) change

- 01 CRPOINT\_TRIM\_1\_100mV\_Vix\_shift\_down 100 mV Vix shift down

- 10 CRPOINT\_TRIM\_2\_100mV\_Vix\_shift\_up 100 mV Vix shift up

- 11 CRPOINT\_TRIM\_3\_200mV\_Vix\_shift\_up 200 mV Vix shift up

#### NOTE

Any VIX adjustments must be applied before running the calibration. NXP i.MX 7ULP development boards achieve the best performance results with the default configuration of CRPOINT\_TRIM.

#### 2.4 IO driver strength adjustment

DDR provides different driver strength configuration to allow the best power vs. performance solution for a given application. On lower performance applications, weaker driver strength can be chosen to reduce power consumption.

The following MMDC registers are available for IO driver configuration:

IOMUXC1\_DDR\_SW\_PAD\_CTL\_PAD\_DDR\_DQS0-3

IOMUXC1\_DDR\_SW\_PAD\_CTL\_PAD\_DDR\_DQM0-3

IOMUXC1\_DDR\_SW\_PAD\_CTL\_PAD\_DDR\_CLK0

IOMUXC1\_DDR\_SW\_PAD\_CTL\_GRP\_DS\_ADDR (CA0-9 pad groups)

IOMUXC1\_DDR\_SW\_PAD\_CTL\_GRP\_DS\_CTRL (CKE0-1, CS0-1\_B)

IOMUXC1\_DDR\_SW\_PAD\_CTL\_GRP\_DS\_DAT0 (DQ0-7 pad groups)

IOMUXC1\_DDR\_SW\_PAD\_CTL\_GRP\_DS\_DAT1 (DQ8-15 pad groups)

IOMUXC1\_DDR\_SW\_PAD\_CTL\_GRP\_DS\_DAT2 (DQ16-23 pad groups)

IOMUXC1\_DDR\_SW\_PAD\_CTL\_GRP\_DS\_DAT3 (DQ24-31 pad groups)

#### NOTE

Drive strength should be adjusted with a sufficient margin for operation. The i.MX 7ULP DDR Stress Test tool can be used to evaluate configuration settings and assess the design margin for a target board.

### 2.5 IO per-bit de-skew

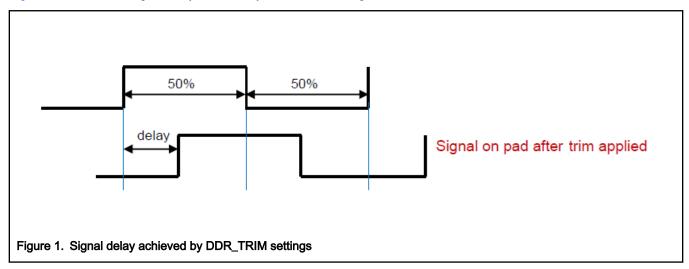

DDR IO de-skew adjustment is available only for single IO (non-differential) signals and corresponds to the DDR\_TRIM parameter.

- · Output Driver Delay Trim Field:

- 00 DDR\_TRIM\_0\_0pS 0 pS

- 01 DDR\_TRIM\_1\_50pS 50 pS

- 10 DDR\_TRIM\_2\_100pS 100 pS

- 11 DDR\_TRIM\_3\_150pS 150 pS

Figure 1 illustrates the signal delay achieved by DDR\_TRIM settings.

#### NOTE

Any PAD delay adjustments must be applied before running the calibration. NXP i.MX 7ULP development boards achieve the best performance results with the default configuration of PAD delay settings.

## 3 General recommendations to optimize the DDR interface

The following section provides brief recommendations on how to further optimize the DDR interface. The following recommendations are not absolutely necessary to optimize various parameters and may also have limited applicability on certain customer designs.

### 3.1 Drive strength configuration

NXP testing shows that lowering the drive strengths can degrade the SDCLK Duty Cycle performance. NXP does not recommend using 60 Ohms (or lower) for any customer design. For the IOPAD Drive Strength, you should set the DSE = 110b (40 Ohms (default value) bits 5, 4, 3) in the IOMUXC1\_DDR\* registers listed in IO driver strength adjustment .

NXP testing also shows that using DSE = 110b (40 Ohms (default value) bits 5, 4, 3) provides optimal VIX and tDSQH performance. Note that drive strength configuration and optimization is dependent on the customer board layout and design.

### 3.2 Supply configurations

NXP testing showns that increasing the A7 VDD\_PMC11\_DIG1\_CAP/VDD\_DIG1 core voltage level from the default specification can improve the SDCLK jitter and VIX marginally. This is valid for both LDO-enabled (achieved by internal PMC configuration) and LDO-bypass (achieved by configuring external PMIC) modes. See the recommended operating conditions in the i.MX 7ULP Data Sheet (document IMX7ULPCEC).

### 3.3 Supply ripple

Regulation instabilities and ripples on the LDO output can also increase the system clock jitter, which can impact the SDCLK duty cycle and other DDR signal parameters. Ensure correct capacitors sizing and placement on VDD\_PMC11\_DIG1\_CAP, VDD\_DDR, VDD18\_DDR, and VDD\_PLL18.

To minimize jitter, follow the layout and decoupling recommendations in the i.MX7ULP Hardware Development Guide (document IMX7ULPHDG).

#### 4 References

- JEDEC LPDDR2/LPDDR3 SDRAM Standard (document JEDEC- JESD209-2F / JESD209-3C)

- i.MX7 Hardware Development Guide (document IMX7ULPHDG)

- i.MX 7ULP Data Sheet (document IMX7ULPCEC)

- i.MX 7ULP Reference Manual (document IMX7ULPRM)

- i.MX 7ULP LPDDR2/LPDDR3 Register Programming Aid

- i.MX 7ULP DDR Stress Test Tool

How To Reach Us

Home Page:

nxp.com

Web Support:

nxp.com/support

Information in this document is provided solely to enable system and software implementers to use NXP products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document. NXP reserves the right to make changes without further notice to any products herein.

NXP makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does NXP assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in NXP data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must be validated for each customer application by customer's technical experts. NXP does not convey any license under its patent rights nor the rights of others. NXP sells products pursuant to standard terms and conditions of sale, which can be found at the following address: nxp.com/

SalesTermsandConditions.

While NXP has implemented advanced security features, all products may be subject to unidentified vulnerabilities. Customers are responsible for the design and operation of their applications and products to reduce the effect of these vulnerabilities on customer's applications and products, and NXP accepts no liability for any vulnerability that is discovered. Customers should implement appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP, the NXP logo, NXP SECURE CONNECTIONS FOR A SMARTER WORLD, COOLFLUX, EMBRACE, GREENCHIP, HITAG, ICODE, JCOP, LIFE VIBES, MIFARE, MIFARE CLASSIC. MIFARE DESFire, MIFARE PLUS, MIFARE FLEX, MANTIS, MIFARE ULTRALIGHT, MIFARE4MOBILE, MIGLO, NTAG, ROADLINK, SMARTLX, SMARTMX, STARPLUG, TOPFET, TRENCHMOS, UCODE, Freescale, the Freescale logo, AltiVec, CodeWarrior, ColdFire, ColdFire+, the Energy Efficient Solutions logo, Kinetis, Layerscape, MagniV, mobileGT, PEG, PowerQUICC, Processor Expert, QorlQ, QorlQ Qonverge, SafeAssure, the SafeAssure logo, StarCore, Symphony, VortiQa, Vybrid, Airfast, BeeKit, BeeStack, CoreNet, Flexis, MXC, Platformin a Package, QUICC Engine, Tower, TurboLink, EdgeScale, EdgeLock, eIQ, and Immersive3D are trademarks of NXP B.V. All other product or service names are the property of their respective owners. AMBA, Arm, Arm7, Arm7TDMI, Arm9, Arm11, Artisan, big.LITTLE, Cordio, CoreLink, CoreSight, Cortex, DesignStart, DynamlQ, Jazelle, Keil, Mali, Mbed, Mbed Enabled, NEON, POP, RealView, SecurCore, Socrates, Thumb, TrustZone, ULINK, ULINK2, ULINK-ME, ULINK-PLUS, ULINKpro, µVision, Versatile are trademarks or registered trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. The related technology may be protected by any or all of patents, copyrights, designs and trade secrets. All rights reserved. Oracle and Java are registered trademarks of Oracle and/or its affiliates. The Power Architecture and Power.org word marks and the Power and Power.org logos and related marks are trademarks and service marks licensed by Power.org.

© NXP B.V. 2020.

All rights reserved.

For more information, please visit: http://www.nxp.com

For sales office addresses, please send an email to: salesaddresses@nxp.com

Date of release: 06/2020 Document identifier: EB00913