#### Document Number: EB00901

#### Rev. 1, 11/2019

# MPC5674F: Flash Memory Accessibility Issues for Non-POR Reset

## 1 Description

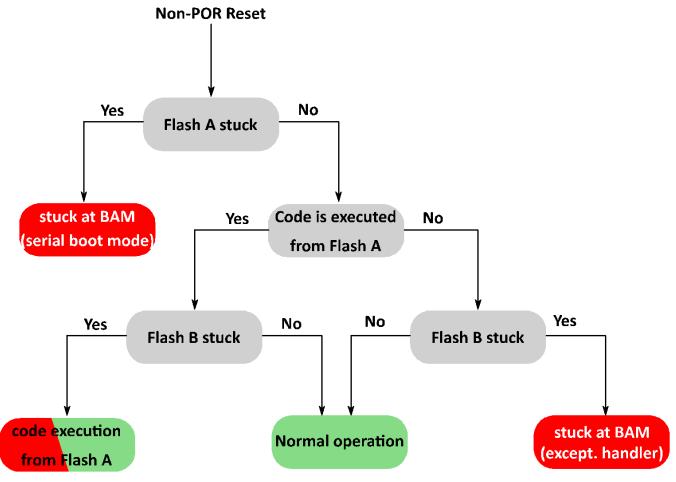

Whenever a non-POR reset occurs, it can generate a glitch on the internal Flash A and B modules clock. There is a chance that this glitch may result in either (or both) flash modules becoming unresponsive.

The generation of the clock glitch is conditioned by a 5-degree temperature window (at high temperature) and voltage window which varies from device to device with normal process variation.

There are three different failure scenarios:

- Flash A is impacted or both flashes are impacted

When Flash A is impacted, the device is not able to exit

Boot Assist Monitor (BAM) code and the device will

stay in serial boot mode, due to not finding the valid

reset configuration word (RCHW) in flash memory.

There is an active Software Watchdog Timer (SWT)

during execution of BAM serial boot code which will

assert reset after a duration that is based on the crystal

frequency (see Figure 2).

- Flash B is impacted and the code is executed from Flash A

#### **Contents**

|   | Description     | 1 |

|---|-----------------|---|

| 2 | Risk assessment | 4 |

| 3 | Mitigation      | 4 |

| ļ | Workaround      | 4 |

#### Description

When the code is executed from Flash A and Flash B is impacted and is accessed an exception (machine check—IVOR1) is generated.

• Flash B is impacted and the code is also executed from Flash B

When the code is executed from Flash B (the RCHW in Flash A is pointing the code execution into Flash B) and Flash B is stuck, the device stays in BAM code because the exception handler triggered by flash issue is part of BAM code. Software Watchdog Timer (SWT) is configurable during execution of BAM exception handler that is based on the crystal frequency (see Figure 3).

Figure 1. Possible scenarios of flash memory issues

3

| Serial Boot Mode — Baud Rate and | d Watchdog Summary <sup>1</sup> |

|----------------------------------|---------------------------------|

|----------------------------------|---------------------------------|

| Crystal<br>Frequency<br>(MHz) | System<br>Clock<br>Frequency<br>(MHz) | Desired<br>Baud Rate<br>(baud) | Actual eSCI<br>Baud Rate<br>(baud) | CAN Baud<br>Rate<br>(baud) | Core Watchdog<br>Timeout<br>period <sup>2</sup><br>(s) | SWT Timeout<br>period during<br>serial boot <sup>3</sup><br>(s) |

|-------------------------------|---------------------------------------|--------------------------------|------------------------------------|----------------------------|--------------------------------------------------------|-----------------------------------------------------------------|

| f <sub>xtal</sub>             | $f_{sys} = 1.5*f_{xtal}$              | _                              | f <sub>sys</sub> / 1248            | f <sub>sys</sub> / 60      | 2.5 * 2 <sup>27</sup> / f <sub>sys</sub>               | 2.5 * 2 <sup>27</sup> / f <sub>xtal</sub>                       |

| 8                             | 12                                    | 9600                           | 9615                               | 200k                       | 27.96                                                  | 41.9                                                            |

| 12                            | 18                                    | 14400                          | 14423                              | 300k                       | 18.64                                                  | 28                                                              |

| 16                            | 24                                    | 19200                          | 19230                              | 400k                       | 13.98                                                  | 21                                                              |

| 20                            | 30                                    | 24000                          | 24038                              | 500k                       | 11.18                                                  | 16.8                                                            |

| 40                            | 60                                    | 48000                          | 48077                              | 1000k                      |                                                        | 8.4                                                             |

With the PLL in normal mode and crystal oscillator as a reference clock source.

Figure 2. Serial boot mode - Baud rate and Watchdog summary

Watchdog Timeout vs. Crystal Frequency<sup>1</sup>

| Crystal Frequency (MHz) | Core WD Timeout (ms) | SWT Timeout (ms) |

|-------------------------|----------------------|------------------|

| 8                       | 27.3                 | 49               |

| 12                      | 18.3                 | 32.7             |

| 16                      | 13.7                 | 24.5             |

| 20                      | 11                   | 19.6             |

| 40                      |                      | 9.8              |

With the PLL in normal mode and crystal oscillator as a reference clock source.

Figure 3. Watchdog timer vs crystal frequency

MPC5674F: Flash Memory Accessibility Issues for Non-POR Reset, Rev. 1, 11/2019

The core WD is disabled during serial boot and is then enabled after serial boot finishes (with timeouts indicated here)

The SWT is enabled during serial boot, but disabled after serial boot finishes.

### 2 Risk assessment

The risk of flash being stuck depends on the number of non-POR resets, the specific application profile of operation over voltage and temperature, and as noted above, the normal process variation from device to device. It is therefore not possible to specify an absolute risk for all conditions. A statement of impact is being included in an updated Design Failure Mode and Effect Analysis (DFMEA) document for this device.

# 3 Mitigation

Reduce the number of non-POR resets, which is the trigger of the issue, as much as possible.

### 4 Workaround

When the issue occurs, only a POR (power down/up cycle) is guaranteed to recover every time. Another source of reset (SWT reset, External reset, or Software reset) can recover the device, although there is some chance of the problem occurring again on that reset.

When Flash A is affected, an external watchdog that only asserts external RESET may work but is not guaranteed to work every time.

If Flash B is affected and the code is executed from Flash A, application code may detect the condition by checking Flash B's Module Control Register DONE bit (MCR[DONE]) and then issuing an external hardware reset via an external circuit, an internal software reset, or a system reset caused by SWT expiration. With these methods, there is some chance the issue will occur again after the reset.

When Flash B is affected and the code is executed from Flash B, you can use the system reset caused by the internal SWT to recover Flash B (SWT needs to be enabled in the RCHW configuration), although there is some chance of the problem occurring again on that reset.

4 NXP Semiconductors

How to Reach Us:

Home Page:

nxp.com

Web Support: nxp.com/support

Information in this document is provided solely to enable system and software implementers to use NXP products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document. NXP reserves the right to make changes without further notice to any products herein.

NXP makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does NXP assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in NXP data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must be validated for each customer application by customer's technical experts. NXP does not convey any license under its patent rights nor the rights of others. NXP sells products pursuant to standard terms and conditions of sale, which can be found at the following address: nxp.com/SalesTermsandConditions.

While NXP has implemented advanced security features, all products may be subject to unidentified vulnerabilities. Customers are responsible for the design and operation of their applications and products to reduce the effect of these vulnerabilities on customer's applications and products, and NXP accepts no liability for any vulnerability that is discovered. Customers should implement appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP. the NXP logo. NXP SECURE CONNECTIONS FOR A SMARTER WORLD. COOLFLUX. EMBRACE, GREENCHIP, HITAG, I2C BUS, ICODE, JCOP, LIFE VIBES, MIFARE, MIFARE CLASSIC, MIFARE DESFire, MIFARE PLUS, MIFARE FLEX, MANTIS, MIFARE ULTRALIGHT, MIFARE4MOBILE, MIGLO, NTAG, ROADLINK, SMARTLX, SMARTMX, STARPLUG, TOPFET, TRENCHMOS, UCODE, Freescale, the Freescale logo, AltiVec, C-5, CodeTEST, CodeWarrior, ColdFire, ColdFire+, C-Ware, the Energy Efficient Solutions logo, Kinetis, Layerscape, MagniV, mobileGT, PEG, PowerQUICC, Processor Expert, QorlQ, QorlQ Qonverge, Ready Play, SafeAssure, the SafeAssure logo, StarCore, Symphony, VortiQa, Vybrid, Airfast, BeeKit, BeeStack, CoreNet, Flexis, MXC, Platform in a Package, QUICC Engine, SMARTMOS, Tower, TurboLink, and UMEMS are trademarks of NXP B.V. All other product or service names are the property of their respective owners. AMBA, Arm, Arm7, Arm7TDMI, Arm9, Arm11, Artisan, big.LITTLE, Cordio, CoreLink, CoreSight, Cortex, DesignStart, DynamlQ, Jazelle, Keil, Mali, Mbed, Mbed Enabled, NEON, POP, RealView, SecurCore, Socrates, Thumb, TrustZone, ULINK, ULINK2, ULINK-ME, ULINK-PLUS, ULINKpro, µVision, Versatile are trademarks or registered trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. The related technology may be protected by any or all of patents, copyrights, designs and trade secrets. All rights reserved. Oracle and Java are registered trademarks of Oracle and/or its affiliates. The Power Architecture and Power.org word marks and the Power and Power.org logos and related marks are trademarks and service marks licensed by Power.org.

© 2019 NXP B.V.

Document Number EB00901 Revision 1, 11/2019