- This document provides electrical specifications for S32E2, which includes the Application Extension (AE) subsystem.

- For functional characteristics and the programming model, see the S32E2 Reference Manual.

# 1 Introduction: S32E2/S32Z2 Family

### 1.1 Overview

S32E2 and S32Z2 are 32-bit Arm<sup>®</sup>-based real-time processors. They target real-time applications that require low latency and high performance, including applications for:

- Braking

- Hybrid and electric vehicles (HEVs/EVs)

- · Safety

- Chassis

- Domain control

S32E2 builds on and expands NXP's HEV/EV portfolio that includes products such as MPC5744P, MPC5777C, MPC5775B, and MPC5775E. S32E2 is an EV integration platform that supports applications such as:

- Electric traction motor control

- Hybrid control unit (HCU) control

- · Advanced combustion engine management

S32Z2 is a safety and domain controller that supports applications such as:

- Drive-by-wire

- · Chassis control

- · Autonomous vehicle drive control

- Domain control

- · Battery management systems (BMS)

S32E2 and S32Z2 are developed with 16 nm FinFET technology and target ISO 26262 Automotive Safety Integrity Level D (ASIL D).

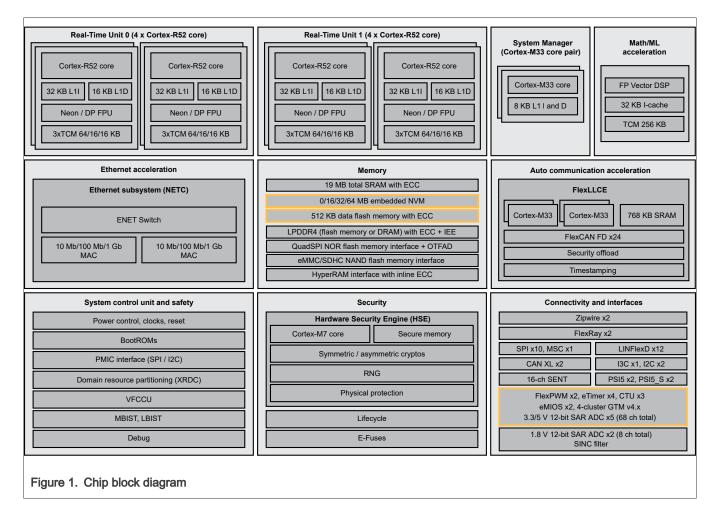

## 1.2 Block diagram

Figure 1 shows the chip components. In this figure, orange component blocks vary across S32E2 and S32Z2. For details, see Feature summary.

# S32E27

#### S32E2 Data Sheet

### 1.3 Feature summary

S32E2 and S32Z2 features include:

- Two core clusters, each of which:

- Has four Arm Cortex<sup>®</sup>-R52 cores operating in two lockstep pairs, offering ASIL D performance with more than 6 kDMIPS

- Can operate in non-lockstep, offering a total of up to 12 kDMIPS

- Arm Cortex-M33 system manager core operating in lockstep

- · ISO 26262 ASIL D, including fail-operational modes, targeted throughout

- 25 GFLOPs math coprocessor and Arm Neon<sup>™</sup> single instruction multiple data (SIMD) technology to execute advanced control algorithms

- Hardware support for virtualization throughout the system, from core to pin, to enable multi-application integration with freedom from interference

- Flash-memory options of 0, 16, 32, and 64 MB for S32E2 (all S32Z2 devices have 0 MB)

- Low-Power Double Data Rate flash-memory (LPDDR-F) interface supporting:

- LPDDR flash memory for larger code footprints

- LPDDR4 DRAM for temporary buffer storage

- Flexible low-latency communications engine (FlexLLCE), operating safely and securely with lockstep AES accelerator, to support CAN communications

- · Zero-downtime over-the-air (OTA) updates

- Multiple options for motor control and combustion engine management:

- GTM (optional for both S32E2 and S32Z2)

- FlexPWM (S32E2 only)

- eMIOS

| Table 1. | Feature | summary |

|----------|---------|---------|

|----------|---------|---------|

| Feature                                                                                                     | \$32E2                                                                                                      | S32E2 S32Z2               |                                 |  |  | S32E2 S32Z2 |  |  |

|-------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|---------------------------|---------------------------------|--|--|-------------|--|--|

| Package: MAPBGA with<br>0.8 mm pitch                                                                        | 27 mm × 27 mm with 975 balls 21 mm × 21 mm with 594 balls                                                   |                           | 17 mm × 17 mm with<br>400 balls |  |  |             |  |  |

| Core complex                                                                                                |                                                                                                             |                           |                                 |  |  |             |  |  |

| Cores 8 Arm Cortex-R52 processors arranged in 2 identical clusters                                          |                                                                                                             |                           |                                 |  |  |             |  |  |

|                                                                                                             | • Each cluster contains 4 cores organized as 2 lockstep pairs: 2 usable cores and 2 shadow cores.           |                           |                                 |  |  |             |  |  |

|                                                                                                             | • The 4 cores in each cluster can operate in a split-lock configuration, resulting in up to 8 usable cores. |                           |                                 |  |  |             |  |  |

| Core operating frequency                                                                                    | 800 MHz (nominal) up to 1 GHz                                                                               |                           |                                 |  |  |             |  |  |

| Core performance                                                                                            | 8 non-lockstep cores: 13 kl                                                                                 | DMIPS (800 MHz), 16 kDMIP | PS (1 GHz)                      |  |  |             |  |  |

| <ul> <li>2 lockstep core pairs and 4 non-lockstep cores: 10 kDMIPS (800 MHz), 12 kDI<br/>(1 GHz)</li> </ul> |                                                                                                             |                           |                                 |  |  |             |  |  |

|                                                                                                             | • 4 lockstep core pairs: 6.5 k                                                                              | DMIPS (800 MHz), 8 kDMIP  | S (1 GHz)                       |  |  |             |  |  |

| 1                                                                                                           | Table continues on the                                                                                      | next page                 | I                               |  |  |             |  |  |

All information provided in this document is subject to legal disclaimers.

© 2020 - 2024 NXP B.V. All rights

reserved.

Table 1. Feature summary...continued

| Feature                                       | S32E2                                                 | S                               | S32Z2                           |  |  |  |

|-----------------------------------------------|-------------------------------------------------------|---------------------------------|---------------------------------|--|--|--|

| Package: MAPBGA with<br>0.8 mm pitch          | 27 mm × 27 mm with 975 balls                          | 21 mm × 21 mm with<br>594 balls | 17 mm × 17 mm with<br>400 balls |  |  |  |

| Arm Neon SIMD technology                      | 8 Neon—1 per core                                     | -                               |                                 |  |  |  |

| Floating-Point Unit (FPU)                     | 1 single-precision FPU per co                         | re                              |                                 |  |  |  |

|                                               | 1 double-precision FPU (Neor                          | ı) per core                     |                                 |  |  |  |

| Tightly Coupled Memory (TCM)                  | Per core:                                             |                                 |                                 |  |  |  |

|                                               | TCM instance                                          | Size                            | Wait states                     |  |  |  |

|                                               | ТСМА                                                  | 64 KB                           | 1                               |  |  |  |

|                                               | ТСМВ                                                  | 16 KB                           | 0                               |  |  |  |

|                                               | ТСМС                                                  | 16 KB                           | 1                               |  |  |  |

| Cache memory                                  | 32 KB I-cache and 16 KB D-ca                          | ache per core                   |                                 |  |  |  |

| L2 cache memory                               | 2 MB, reusable as code RAM:                           | 1 MB per core cluster           |                                 |  |  |  |

| System manager core                           | 1 Arm Cortex-M33 processor                            | lockstep pair                   |                                 |  |  |  |

|                                               | Memory                                                |                                 |                                 |  |  |  |

| Data RAM                                      | 2 MB arranged as 1 MB per co                          | ore cluster                     |                                 |  |  |  |

| Code RAM                                      | 14 MB arranged as 7 MB per                            | core cluster                    |                                 |  |  |  |

| System RAM                                    | 1 MB                                                  |                                 |                                 |  |  |  |

| Flash memory                                  | 0, 16, 32, or 64 MB, with ECC —                       |                                 |                                 |  |  |  |

|                                               | Zero-downtime OTA support                             |                                 |                                 |  |  |  |

| Electrically Erasable                         | 512 KB: arranged as eight                             | _                               |                                 |  |  |  |

| Programmable Read-Only<br>Memory (EEPROM)     | 64 KB sectors, with 4 read-while-write partitions for |                                 |                                 |  |  |  |

|                                               | EEPROM emulation                                      |                                 |                                 |  |  |  |

|                                               | Memory prote                                          | ection                          |                                 |  |  |  |

| Core Memory Protection                        | Level 1: 20 regions                                   |                                 |                                 |  |  |  |

| Unit (MPU)                                    | Level 2: 20 regions for hypervisor support            |                                 |                                 |  |  |  |

| Extended Resource Domain<br>Controller (XRDC) | 16 domains (region descriptor                         | s allocated for each periphe    | ral and 16 for SRAM)            |  |  |  |

|                                               | Accelerato                                            | ors                             |                                 |  |  |  |

| Math coprocessor (optional)                   | 25 GFLOPs                                             |                                 |                                 |  |  |  |

|                                               | External memory                                       | interfaces                      |                                 |  |  |  |

| LPDDR flash memory /                          | LPDDR4-1600 (×16, 800 MHz                             | <u>z</u> )                      | _                               |  |  |  |

#### Table 1. Feature summary...continued

| Feature                                                | S32E2                                                                     | S32Z2                           |                                 |  |  |  |

|--------------------------------------------------------|---------------------------------------------------------------------------|---------------------------------|---------------------------------|--|--|--|

| Package: MAPBGA with<br>0.8 mm pitch                   | 27 mm × 27 mm with 975 balls                                              | 21 mm × 21 mm with<br>594 balls | 17 mm × 17 mm with<br>400 balls |  |  |  |

| Quad Serial Peripheral                                 | 1 (2 on 0 MB flash memory ver                                             | sion) supporting interfaces fo  | r:                              |  |  |  |

| Interface (QuadSPI)                                    | <ul> <li>NOR flash memory: up to<br/>SDR/DDR possible)</li> </ul>         | 200 MHz DDR octal flash mei     | mory (×1, ×4, ×8                |  |  |  |

|                                                        | HyperRAM: up to 166 MHz                                                   | z with inline ECC               |                                 |  |  |  |

| Ultra Secured Digital Host<br>Controller (uSDHC)       | 1 (supports SD and eMMC)                                                  |                                 |                                 |  |  |  |

|                                                        | Enhanced Direct Memory Acce                                               | ess (eDMA) modules              |                                 |  |  |  |

| System eDMA controller                                 | 1 lockstep pair with 32 channe                                            | s and Cyclic Redundancy Ch      | eck (CRC)                       |  |  |  |

| Peripheral eDMA controllers                            | 1 with 32 channels                                                        |                                 |                                 |  |  |  |

|                                                        | 3 with 16 channels each                                                   |                                 |                                 |  |  |  |

| Application Extension<br>eDMA (eDMA_AE)                | 1 with 16 channels —                                                      |                                 |                                 |  |  |  |

|                                                        | Debug                                                                     | I                               |                                 |  |  |  |

| Trace                                                  | ne with data input through Zip                                            | owire                           |                                 |  |  |  |

|                                                        | Peripheral                                                                | 5                               |                                 |  |  |  |

| Analog-to-digital converters<br>(ADCs): 3.3 V or 5.0 V | Five 12-bit Successive<br>Approximation (SAR) ADCs<br>(68 channels total) | _                               |                                 |  |  |  |

| ADCs: 1.8 V                                            | Two 12-bit SAR ADCs (8 chan                                               | nels total)                     |                                 |  |  |  |

| Motor control peripherals                              | 2 FlexPWMs (12<br>channels each)                                          | _                               |                                 |  |  |  |

|                                                        | 4 eTimers (6 channels each)                                               |                                 |                                 |  |  |  |

|                                                        | 3 Cross-Triggering<br>Units (CTUs)                                        | 1 CTU                           |                                 |  |  |  |

|                                                        | 1 SINC (4 channels)                                                       |                                 | _                               |  |  |  |

| Timer modules                                          | 4-cluster Generic Timer Modul<br>support (optional)                       | e (GTM4), up to 400 MHz, wit    | h high-resolution PWM           |  |  |  |

|                                                        | 2 Enhanced Modular Input/Out                                              | put Subsystems (eMIOSs) (2      | 4 channels each)                |  |  |  |

| Logic Control Units (LCUs)                             | 2                                                                         |                                 |                                 |  |  |  |

| Periodic Interrupt Timers (PITs)                       | 14                                                                        | 13                              |                                 |  |  |  |

| Software Watchdog Timers (SWTs)                        | 13                                                                        |                                 |                                 |  |  |  |

| System Timer Modules (STMs)                            | 13                                                                        |                                 |                                 |  |  |  |

| Semaphores2 (SEMA42)                                   | 9                                                                         |                                 |                                 |  |  |  |

Table continues on the next page...

Product Data Sheet

<sup>©</sup> 2020 - 2024 NXP B.V. All rights reserved.

### Table 1. Feature summary...continued

| 0.8 mm pitch27 mm × 27 mm with 975 balls594 balls400 ballsCyclic Redundancy Check (CRC)8CommunicationsCANEXCEL (CANXL)2FlexCAN FD (CAN)24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Feature                            | \$32E2                           | S3                            | 32Z2                                   |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|----------------------------------|-------------------------------|----------------------------------------|--|--|

| Communications         Communications         CANEXCEL (CANXL)       2         FlexCAN FD (CAN)       24         FlexRay Communication<br>Controller (FlexRay)       2 dual-channel       1 dual-channel or 2 sir<br>channel         LINFlexD       12         Ethernet (MAC)       2 Ethernet controllers supporting 10/100 Mbit/s MII/RMII and 10/100/1000 Mbit/s RI         Ethernet switch       1         Peripheral Sensor Interface (PSI5)       2 (4 channels each)       1 (4 channels)         Peripheral Sensor Interface (SPI)       10       8         MicroSecond Channel (MSC)       1 that includes 1 LINFlexD and 1 LVDS deserial SPI (DSPI)         Single Edge Nibble<br>Transmission (SENT)       2 (8 channels each)       1 (8 channels)         Zipwire       2       1       1         Improved Inter-Integrated<br>Circuit (I3C)       2       2       1         Low-Power Inter-Integrated<br>Circuit (LPI2C)       2       2       1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | -                                  | 27 mm x 27 mm with 975 balls     |                               | 17 mm × 17 mm with<br>400 balls        |  |  |

| CANEXCEL (CANXL)         2           FlexCAN FD (CAN)         24           FlexRay Communication<br>Controller (FlexRay)         2 dual-channel         1 dual-channel or 2 sir<br>channel           LINFlexD         12           Ethernet (MAC)         2 Ethernet controllers supporting 10/100 Mbit/s MII/RMII and 10/1000 Mbit/s RI           Ethernet switch         1           Peripheral Sensor Interface (PSI5)         2 (4 channels each)         1 (4 channels)           Peripheral Sensor Interface (PSI5)         2 (4 channels each)         1 (4 channels)           Serial Peripheral Interface (SPI)         10         8           MicroSecond Channel (MSC)         1 that includes 1 LINFlexD and 1 LVDS deserial SPI (DSPI)           Single Edge Nibble<br>Transmission (SENT)         2 (8 channels each)         1 (8 channels)           Zipwire         2         2 (8 channels each)         1 (8 channels)           Zipwire         2         1         1         1           Linproved Inter-Integrated<br>Circuit (I3C)         2         1         1           Low-Power Inter-Integrated<br>Circuit (LPI2C)         2         2         1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Cyclic Redundancy Check (CRC)      | 8                                |                               | 1                                      |  |  |

| FlexCAN FD (CAN)       24         FlexRay Communication<br>Controller (FlexRay)       2 dual-channel       1 dual-channel or 2 sin<br>channel         LINFlexD       12         Ethernet (MAC)       2 Ethernet controllers supporting 10/100 Mbit/s MII/RMII and 10/1000 Mbit/s RMI         Ethernet switch       1         Peripheral Sensor Interface (PSI5)       2 (4 channels each)       1 (4 channels)         Peripheral Sensor Interface (SPI)       10       8         MicroSecond Channel (MSC)       1 that includes 1 LINFlexD and 1 LVDS deserial SPI (DSPI)         Single Edge Nibble<br>Transmission (SENT)       2 (8 channels each)       1 (8 channels)         Zipwire       2       1       1         Linproved Inter-Integrated<br>Circuit (IGC)       2       2       1         Low-Power Inter-Integrated<br>Circuit (LPI2C)       2       2       1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                    | Communicatio                     | ons                           |                                        |  |  |

| FlexRay Communication<br>Controller (FlexRay)       2 dual-channel       1 dual-channel or 2 sin channel         LINFlexD       12         Ethernet (MAC)       2 Ethernet controllers supporting 10/100 Mbit/s MII/RMII and 10/100/1000 Mbit/s Rd         Ethernet switch       1         Peripheral Sensor Interface (PSI5)       2 (4 channels each)       1 (4 channels)         Peripheral Sensor Interface (PSI5)       2 (4 channels each)       1 (4 channels)         Serial Peripheral Interface (SPI)       10       8         MicroSecond Channel (MSC)       1 that includes 1 LINFlexD and 1 LVDS deserial SPI (DSPI)         Single Edge Nibble<br>Transmission (SENT)       2 (8 channels each)       1 (8 channels)         Zipwire       2       1       1         Low-Power Inter-Integrated<br>Circuit (I3C)       2       2       1         Low-Power Inter-Integrated<br>Circuit (LPI2C)       2       2       1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | CANEXCEL (CANXL)                   | 2                                |                               |                                        |  |  |

| Controller (FlexRay)         Image: channel           LINFlexD         12           Ethernet (MAC)         2 Ethernet controllers supporting 10/100 Mbit/s MII/RMII and 10/1000 Mbit/s RI           Ethernet switch         1           Peripheral Sensor Interface (PSI5)         2 (4 channels each)         1 (4 channels)           Peripheral Sensor Interface-         2         1         1           Serial Peripheral Interface (SPI)         10         8         1           MicroSecond Channel (MSC)         1 that includes 1 LINFlexD and 1 LVDS deserial SPI (DSPI)         1           Single Edge Nibble<br>Transmission (SENT)         2 (8 channels each)         1 (8 channels)           Zipwire         2         2 (8 channels each)         1           Low-Power Inter-Integrated<br>Circuit (ISC)         1         2         2           Low-Power Inter-Integrated         2         2         2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | FlexCAN FD (CAN)                   | 24                               |                               |                                        |  |  |

| Ethernet (MAC)2 Ethernet controllers supporting 10/100 Mbit/s MII/RMII and 10/1000 Mbit/s RIEthernet switch1Peripheral Sensor Interface (PSI5)2 (4 channels each)1 (4 channels)Peripheral Sensor Interface-<br>Support Module (PSI5_S)2 (4 channels each)1 (4 channels)Serial Peripheral Interface (SPI)108MicroSecond Channel (MSC)1 that includes 1 LINFlexD and 1 LVDS deserial SPI (DSPI)Single Edge Nibble<br>Transmission (SENT)2 (8 channels each)1 (8 channels)Zipwire21Low-Power Inter-Integrated<br>Circuit (LPI2C)22Security                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | -                                  | 2 dual-channel                   |                               | 1 dual-channel or 2 single-<br>channel |  |  |

| Ethernet switch1Peripheral Sensor Interface (PSI5)2 (4 channels each)1 (4 channels)Peripheral Sensor Interface-<br>Support Module (PSI5_S)21Serial Peripheral Interface (SPI)108MicroSecond Channel (MSC)1 that includes 1 LINFlexD and 1 LVDS deserial SPI (DSPI)Single Edge Nibble<br>Transmission (SENT)2 (8 channels each)1 (8 channels)Zipwire22 (8 channels each)1 (8 channels)Low-Power Inter-Integrated<br>Circuit (LPI2C)221Security                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | LINFlexD                           | 12                               |                               |                                        |  |  |

| Peripheral Sensor Interface (PSI5)2 (4 channels each)1 (4 channels)Peripheral Sensor Interface-<br>Support Module (PSI5_S)21Serial Peripheral Interface (SPI)108MicroSecond Channel (MSC)1 that includes 1 LINFlexD and 1 LVDS deserial SPI (DSPI)Single Edge Nibble<br>Transmission (SENT)2 (8 channels each)1 (8 channels)Zipwire221Improved Inter-Integrated<br>Circuit (I3C)21Low-Power Inter-Integrated<br>Circuit (LPI2C)22Security                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Ethernet (MAC)                     | 2 Ethernet controllers supportin | ng 10/100 Mbit/s MII/RMII and | d 10/100/1000 Mbit/s RGMII             |  |  |

| Peripheral Sensor Interface-<br>Support Module (PSI5_S)21Serial Peripheral Interface (SPI)108MicroSecond Channel (MSC)1 that includes 1 LINFlexD and 1 LVDS deserial SPI (DSPI)Single Edge Nibble<br>Transmission (SENT)2 (8 channels each)1 (8 channels)Zipwire221Improved Inter-Integrated<br>Circuit (I3C)12Low-Power Inter-Integrated<br>Circuit (LPI2C)22Security                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Ethernet switch                    | 1                                |                               |                                        |  |  |

| Support Module (PSI5_S)Indext Content of the second se | Peripheral Sensor Interface (PSI5) | 2 (4 channels each)              |                               | 1 (4 channels)                         |  |  |

| MicroSecond Channel (MSC)1 that includes 1 LINFlexD and 1 LVDS deserial SPI (DSPI)Single Edge Nibble<br>Transmission (SENT)2 (8 channels each)1 (8 channels)Zipwire221Improved Inter-Integrated<br>Circuit (I3C)11Low-Power Inter-Integrated<br>Circuit (LPI2C)22Security                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | •                                  | 2                                |                               | 1                                      |  |  |

| Single Edge Nibble<br>Transmission (SENT)     2 (8 channels each)     1 (8 channels)       Zipwire     2     1       Improved Inter-Integrated<br>Circuit (I3C)     1     1       Low-Power Inter-Integrated<br>Circuit (LPI2C)     2     1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Serial Peripheral Interface (SPI)  | 10                               |                               | 8                                      |  |  |

| Transmission (SENT)     Image: Security                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | MicroSecond Channel (MSC)          | 1 that includes 1 LINFlexD and   | 1 LVDS deserial SPI (DSPI)    |                                        |  |  |

| Improved Inter-Integrated<br>Circuit (I3C)     1       Low-Power Inter-Integrated<br>Circuit (LPI2C)     2       Security                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                    | 2 (8 channels each)              |                               | 1 (8 channels)                         |  |  |

| Circuit (I3C)       Low-Power Inter-Integrated<br>Circuit (LPI2C)       2       Security                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Zipwire                            | 2                                |                               | 1                                      |  |  |

| Circuit (LPI2C) Security                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                    | 1                                |                               |                                        |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                    | 2                                |                               |                                        |  |  |

| Hardware Security Engine (HSE) Yes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                    | Security                         |                               |                                        |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Hardware Security Engine (HSE)     | Yes                              |                               |                                        |  |  |

| Lockstep AES encryption module Yes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Lockstep AES encryption module     | Yes                              |                               |                                        |  |  |

| In-line Encryption Engine (IEE) Yes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | In-line Encryption Engine (IEE)    | Yes                              |                               |                                        |  |  |

| Functional safety                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                    | Functional saf                   | fety                          |                                        |  |  |

| Safety ISO 26262 Safety Element out of Context (SEooC) ASIL D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Safety                             | ISO 26262 Safety Element out     | of Context (SEooC) ASIL D     |                                        |  |  |

| Flexible core recovery options                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                    | Flexible core recovery options   |                               |                                        |  |  |

| Memory Built-In Self-Test (MBIST) Yes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Memory Built-In Self-Test (MBIST)  | Yes                              |                               |                                        |  |  |

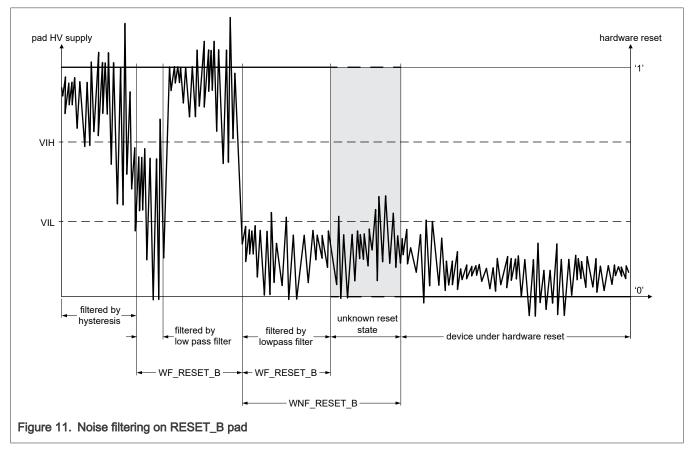

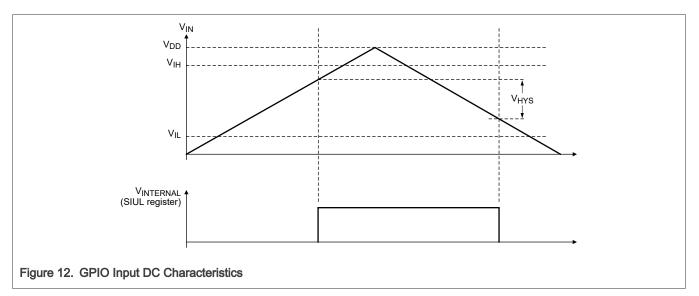

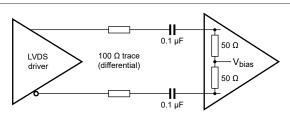

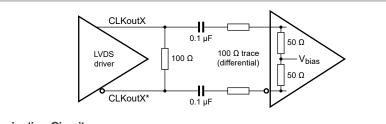

| On-chip temperature sensors Yes and monitoring                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                    | Yes                              |                               |                                        |  |  |