Product data sheet

# NXLS9XXX0

Single channel inertial sensor

Rev. 1.0 — 27 March 2025

# 1 General description

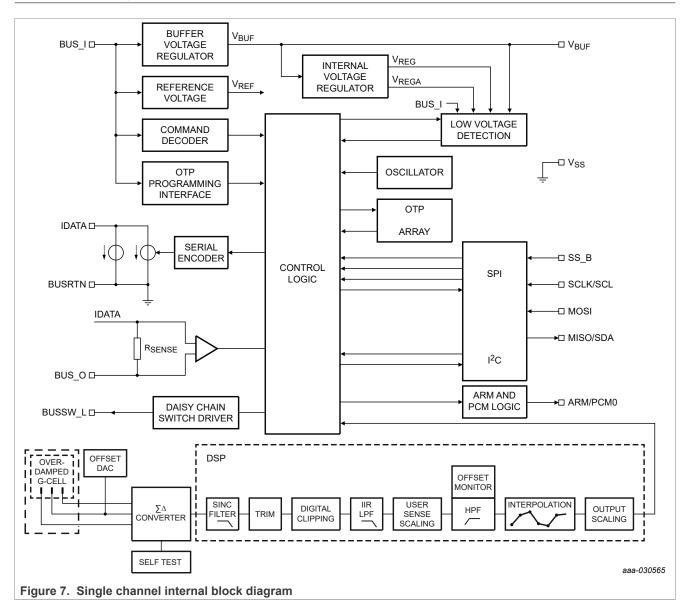

The NXLS9xxx0 is a single channel DSI3, PSI5, SPI, and I<sup>2</sup>C compatible lateral (X-axis or Y-axis) or vertical (Z-axis) inertial sensor.

# 2 Features

- X-axis, Y-axis, or Z-axis

- Medium g ranges from  $\pm$  15.5 g to  $\pm$  150 g nominal full-scale range - High g ranges from  $\pm$  50 g to  $\pm$  500 g nominal full-scale range

- -40 °C to 125 °C operating temperature range

- DSI3 compatible

- Discovery mode for physical location identification

- High side bus switch output driver

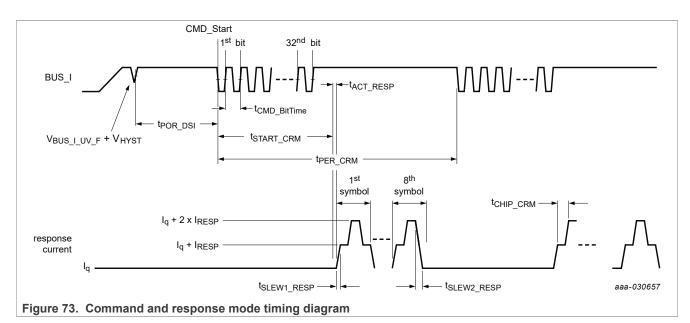

- Command and response mode support for device configuration

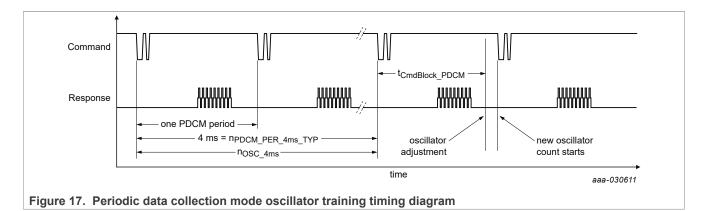

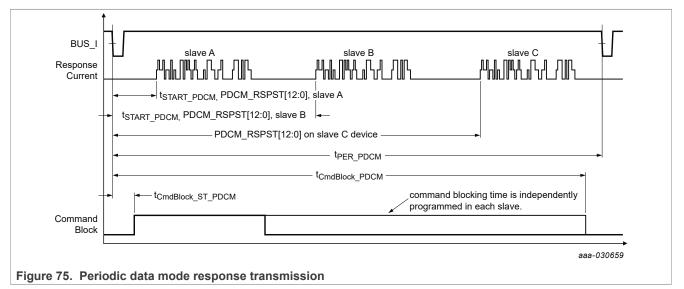

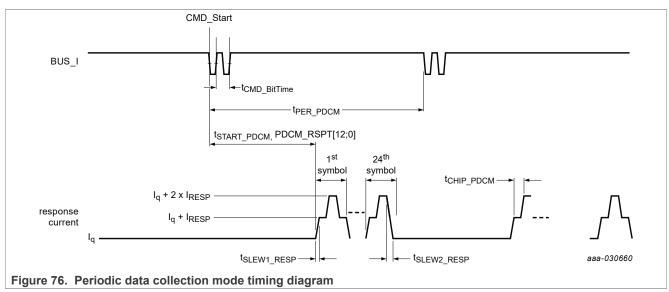

- Periodic data collection mode support for sensor data transfers.

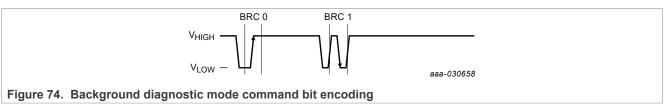

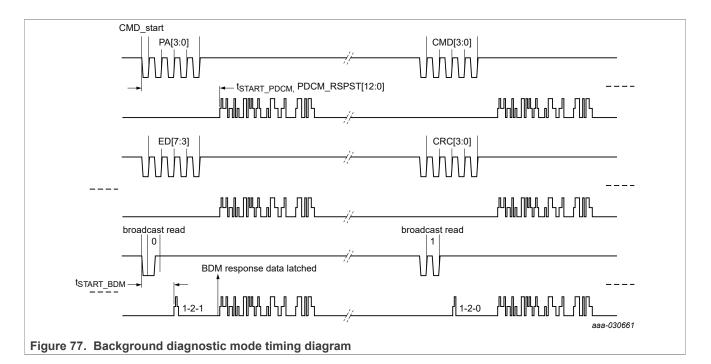

- Background diagnostic mode support during periodic data collection mode

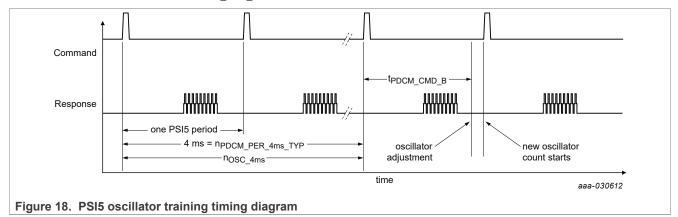

- PSI5 Version 2.1 compatible

- Compatible modes:

- P10P-500/3L

- P10P-500/4H

- A10P-228/1L

- P10CRC-xxx/xx

- P16CRC-xxx/xx

- and many others

- Programmable time slots with 1 µs resolution

- Selectable baud rate: 125 kBd or 189 kBd

- 10- and 16-bit data options

- Selectable error detection: even parity, or 3-bit CRC

- Optional daisy chain with external low side switch

- Two-wire programming mode

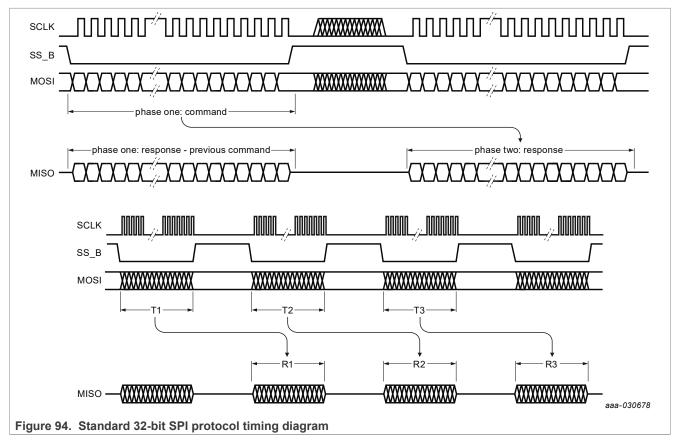

- 32-bit SPI compatible serial interface

- 3.3 V or 5 V single supply operation

- Register read and write commands

- Sensor data transmission commands

- 12-bit data, left justified in a 16-bit data field

- Command echo with 3-bit source identification

Single channel inertial sensor

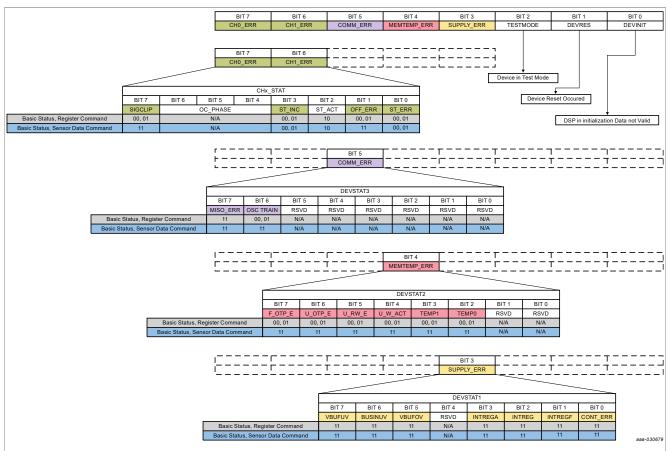

- 2-bit basic status and 2-bit detailed status fields

- 8-bit CRC

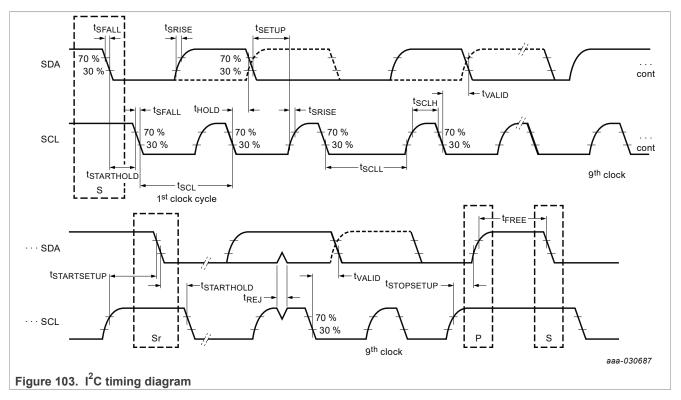

- I<sup>2</sup>C compatible serial interface (UM10204<sup>[1]</sup>)

- Slave mode operation

- Standard mode, fast mode, and fast mode plus support

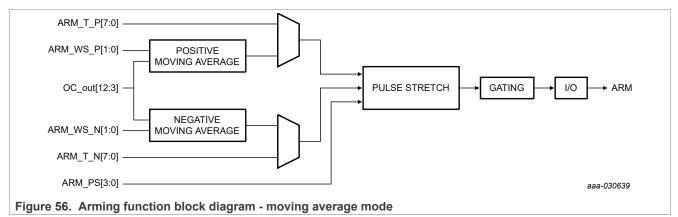

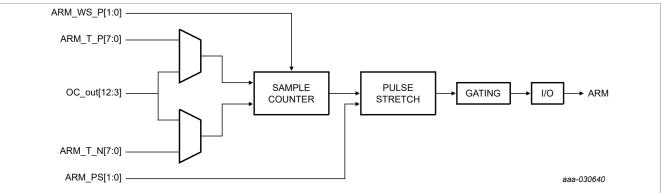

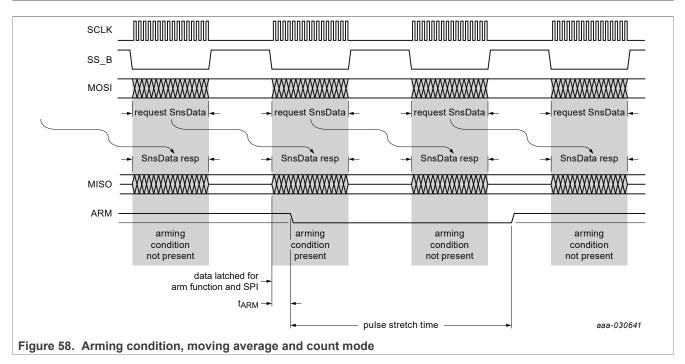

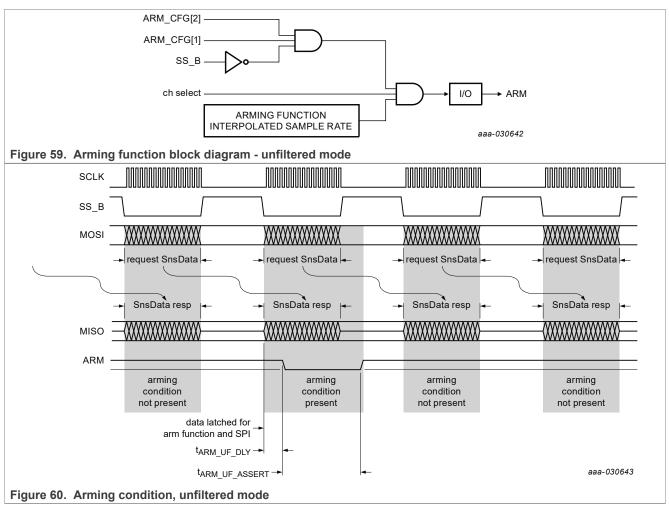

- Programmable arming function

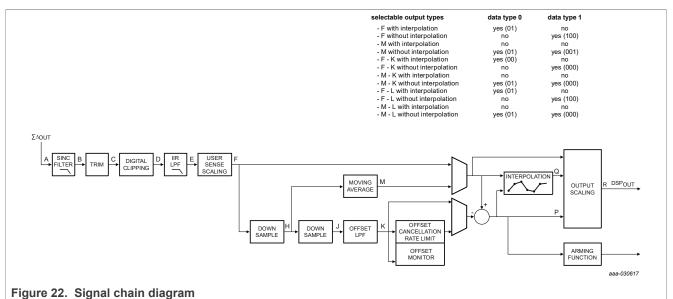

- DSP

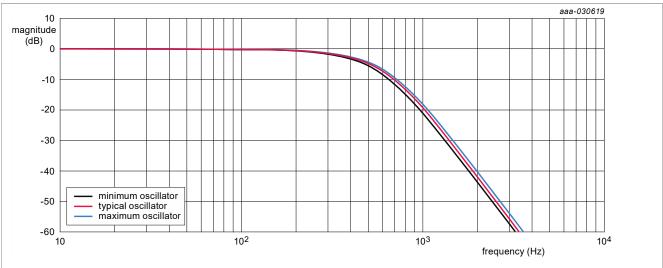

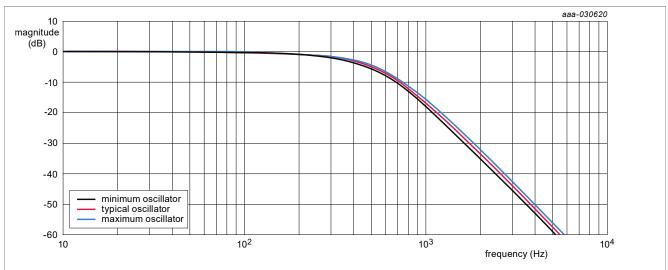

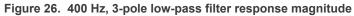

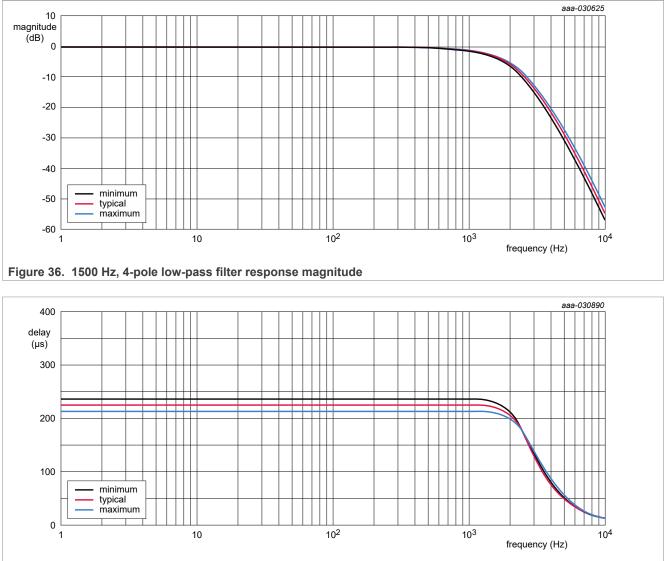

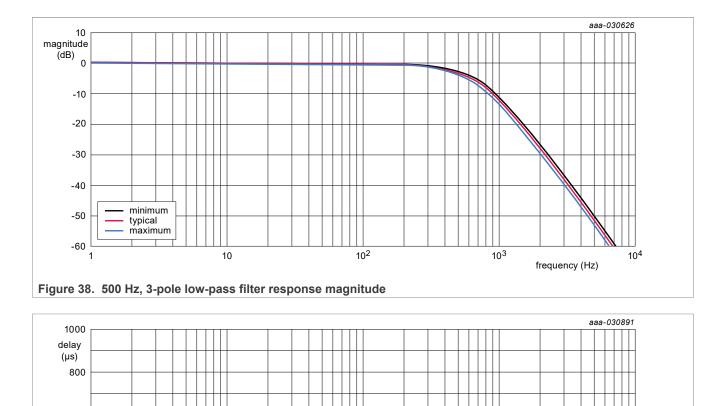

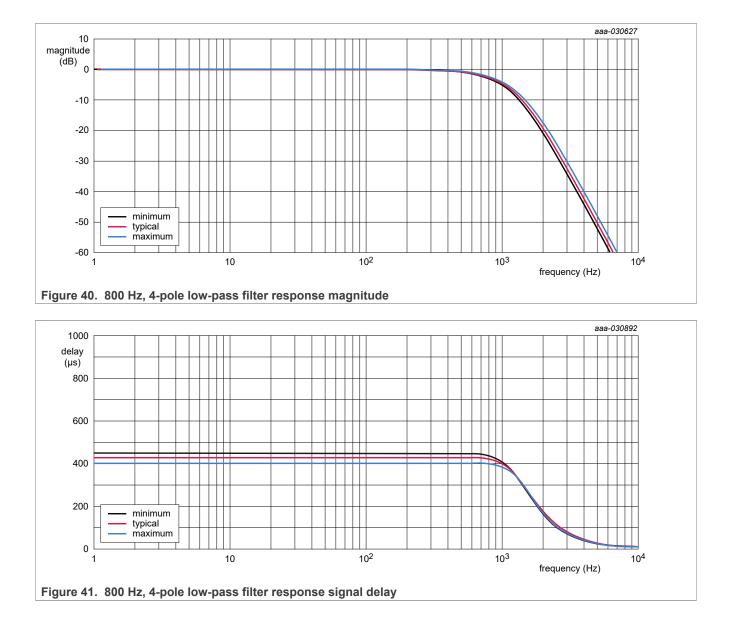

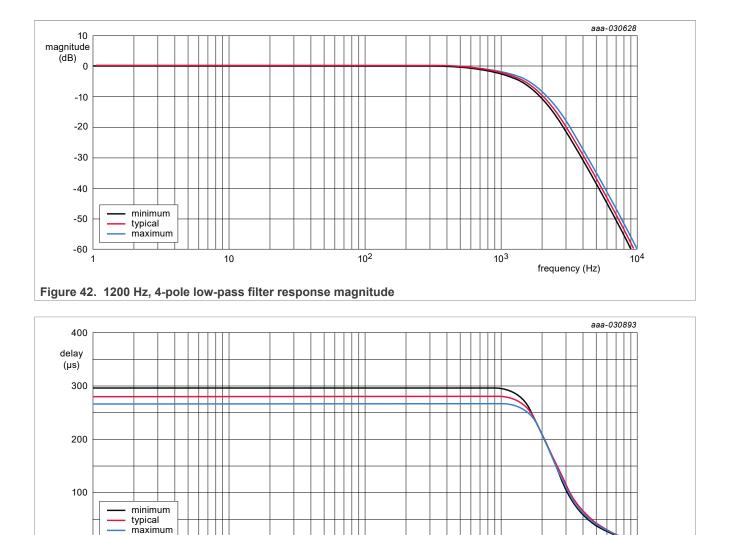

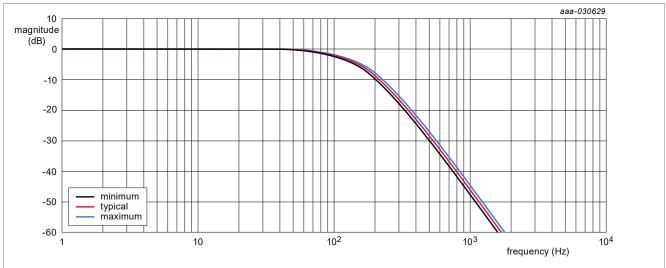

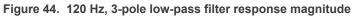

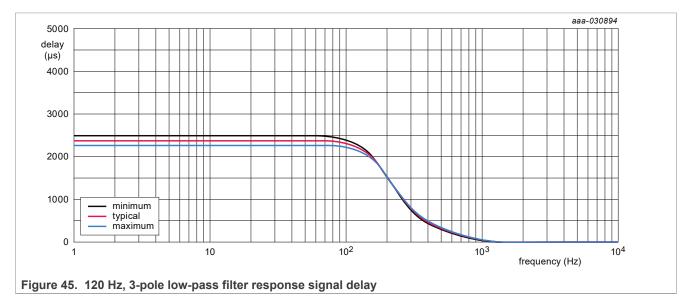

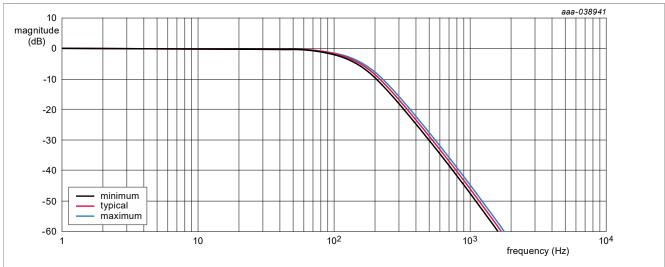

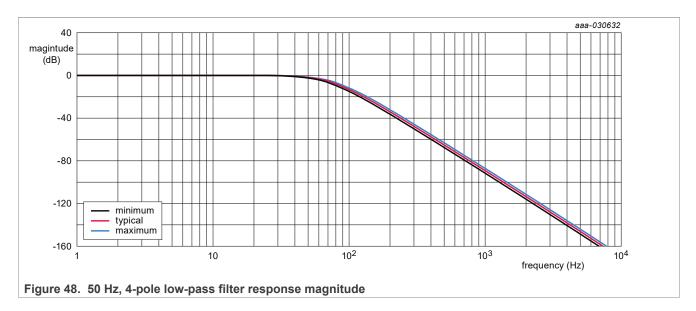

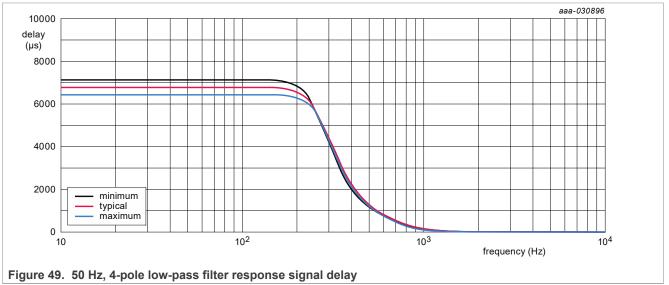

- Up to a fourth order low-pass filter with rolloff frequency options from 12.5 Hz to 1500 Hz

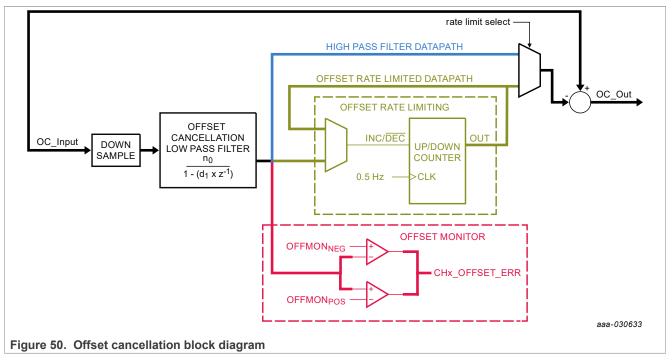

- Optional single pole high pass filter with fast startup and output rate limiting

- Optional moving average

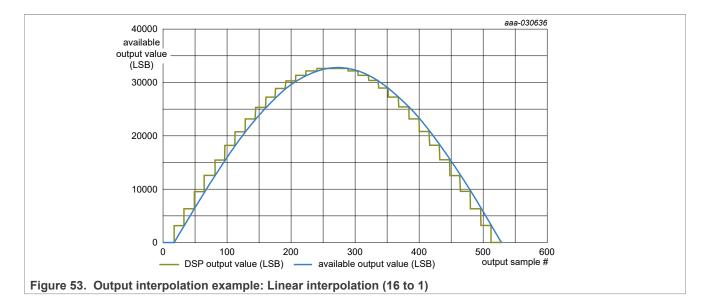

- Optional 16 to 1 output interpolation

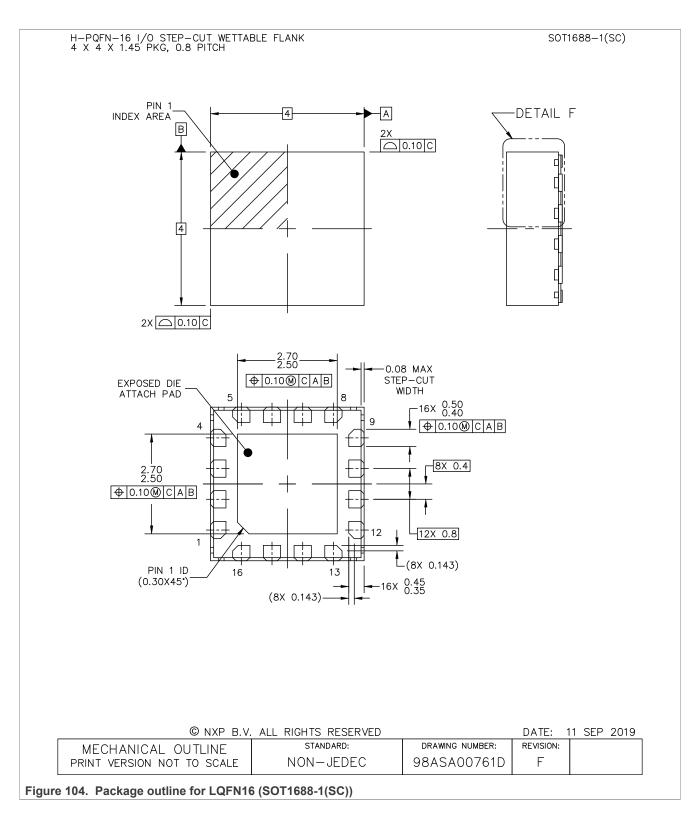

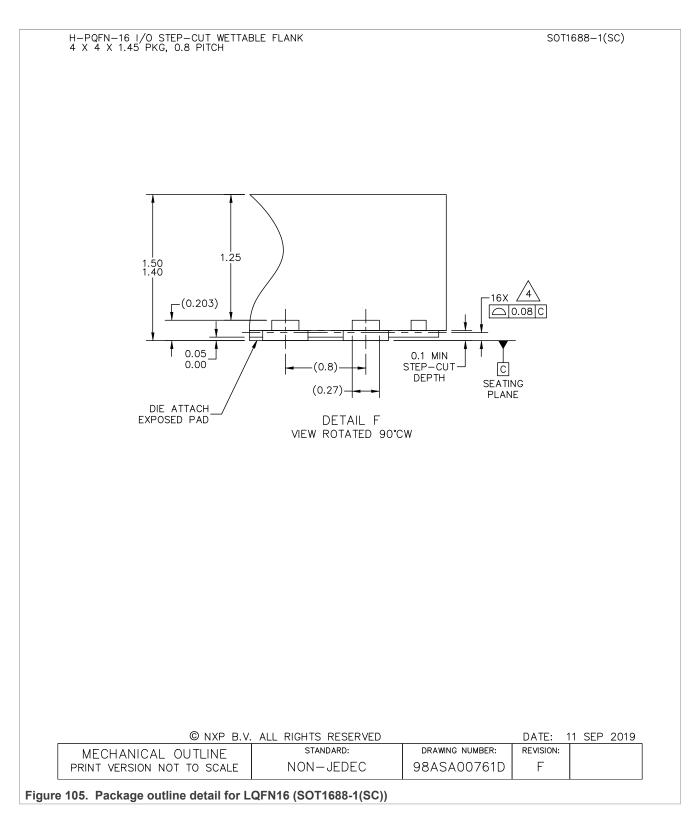

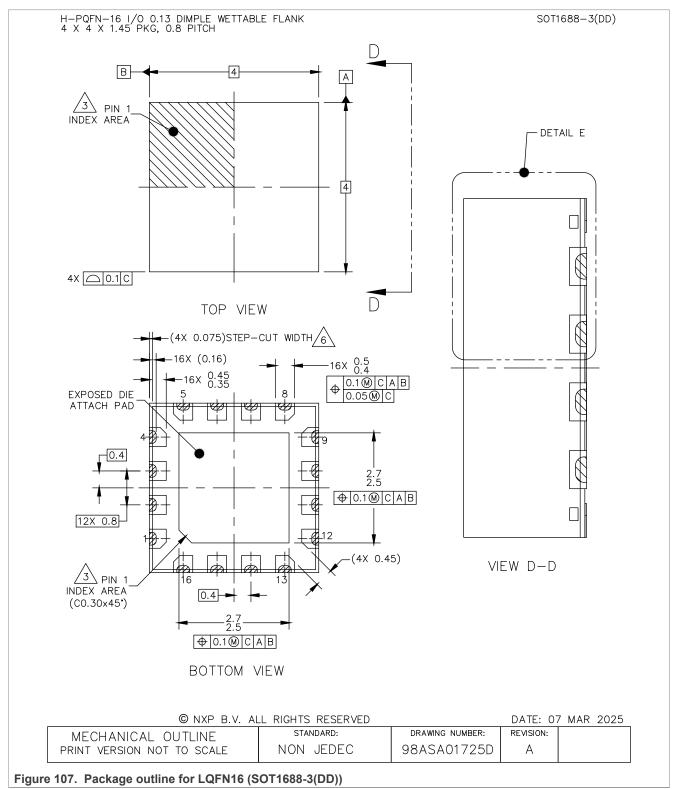

- Pb-free 16-Pin QFN 4 mm x 4 mm x 1.45 mm package

# **3** Applications

### 3.1 Automotive

- Airbag, Collision/Crash detection

- Active suspension vibration monitoring

## 3.2 Industrial

• Machine condition monitoring

# 4 Ordering information

#### Table 1. Ordering information

| Type number          | Package |                                                                                                                                                          |                      |  |  |

|----------------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--|--|

| Name Description Ver |         | Version                                                                                                                                                  |                      |  |  |

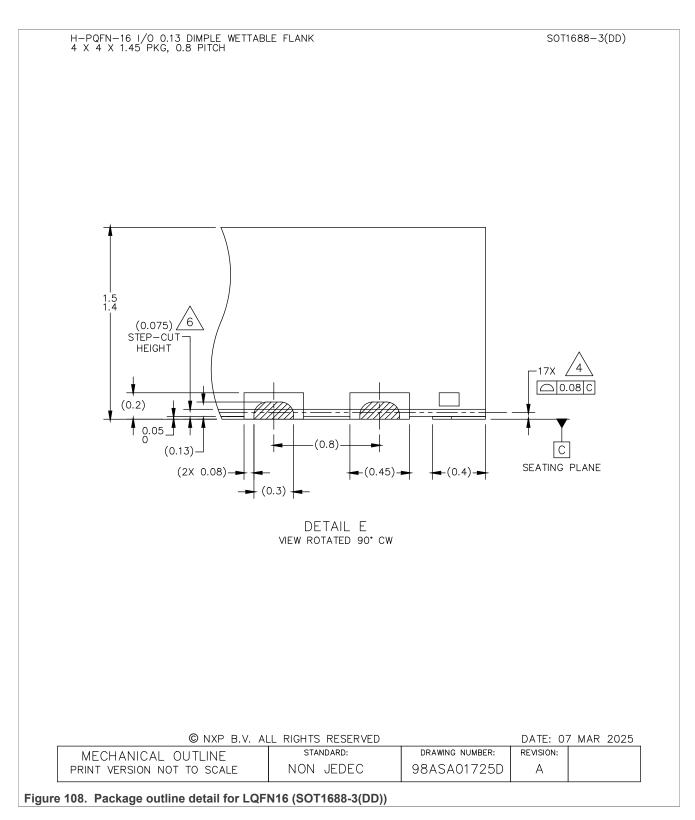

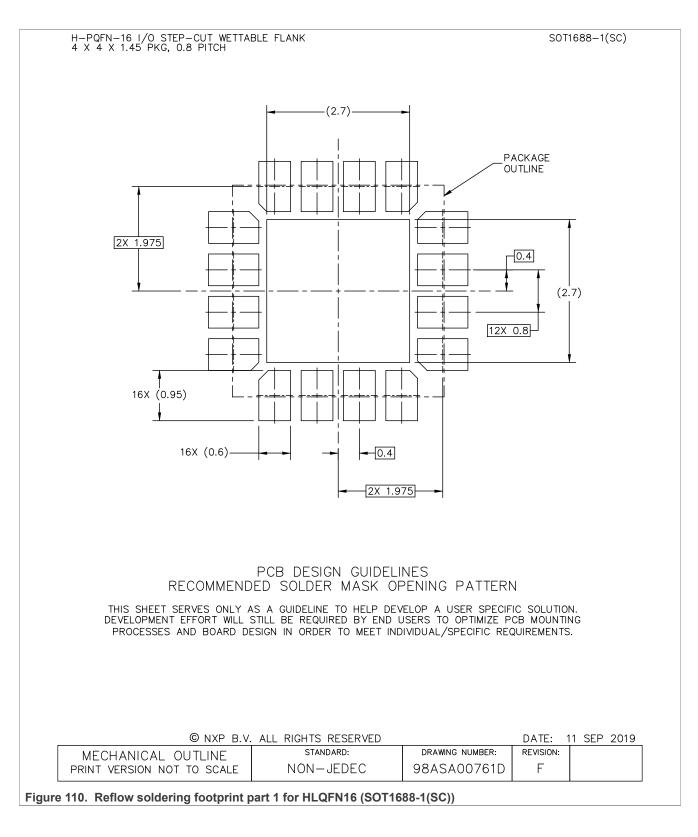

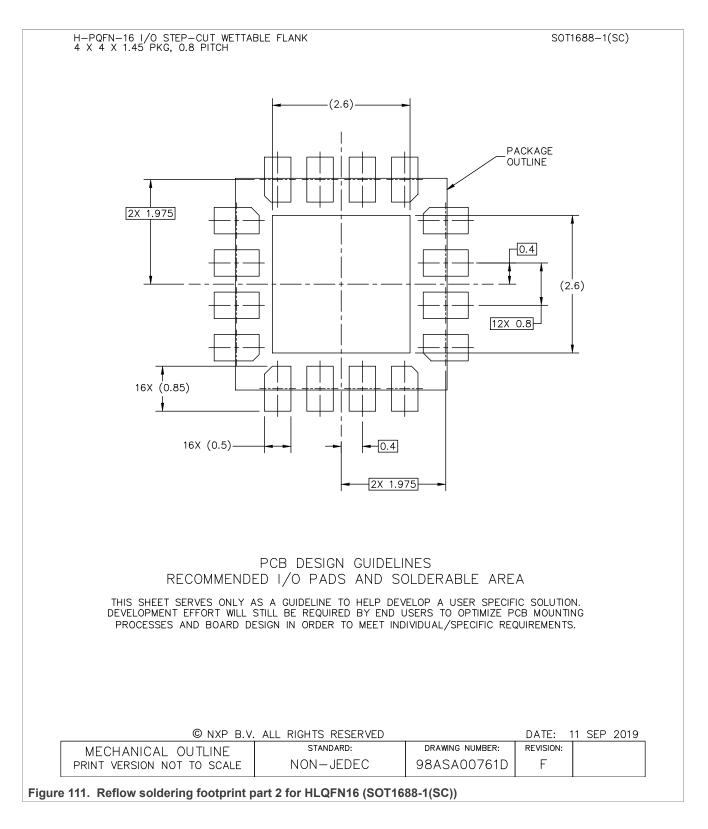

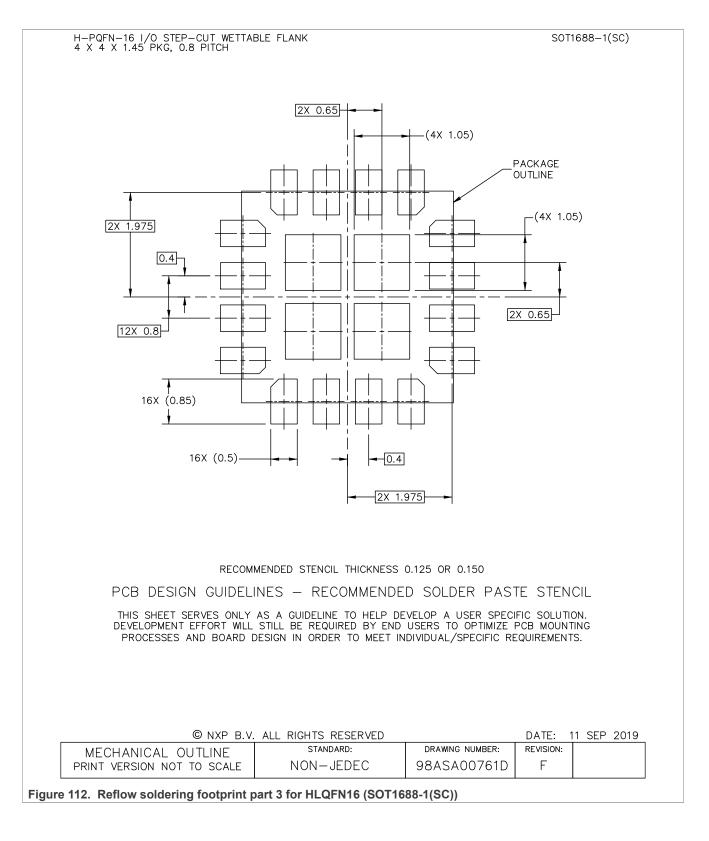

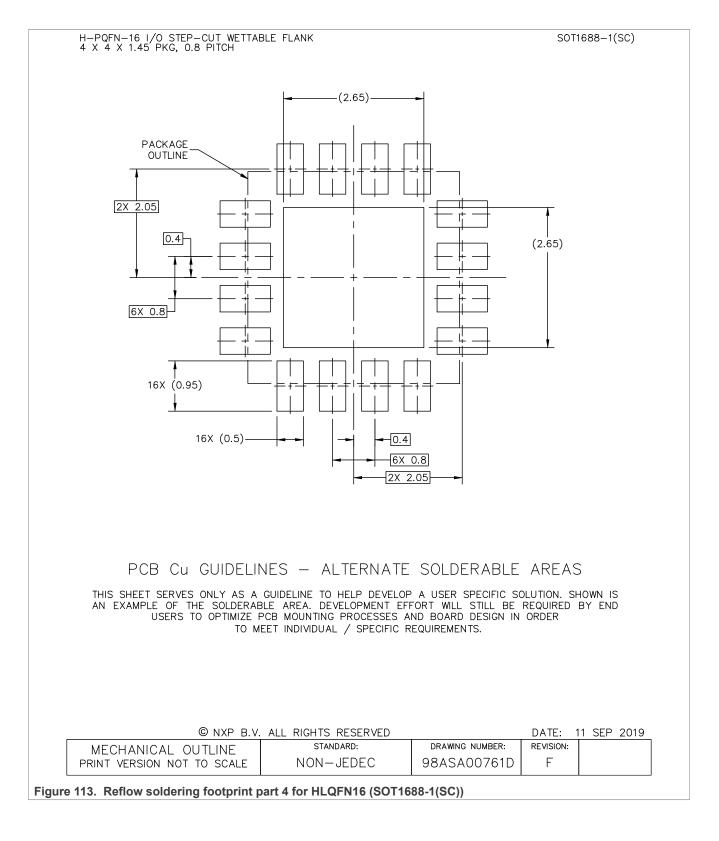

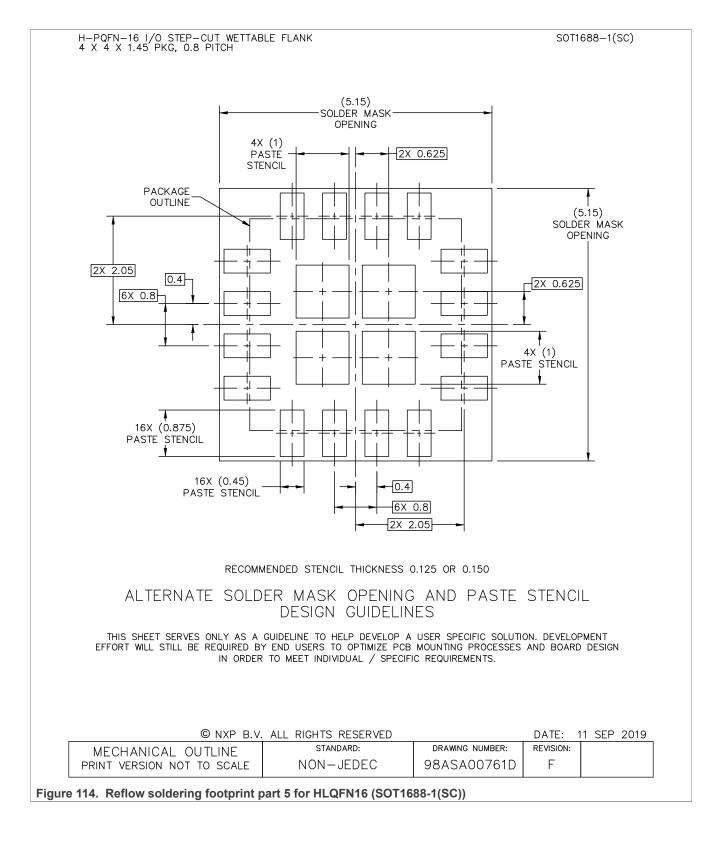

| NXLS9xxxxAESR2       | HLQFN16 | Plastic, thermal enhanced low profile quad flat non-leaded package; 16 terminals; 0.8 mm pitch; 4 mm x 4 mm x 1.45 mm body                               | <u>SOT1688-1(SC)</u> |  |  |

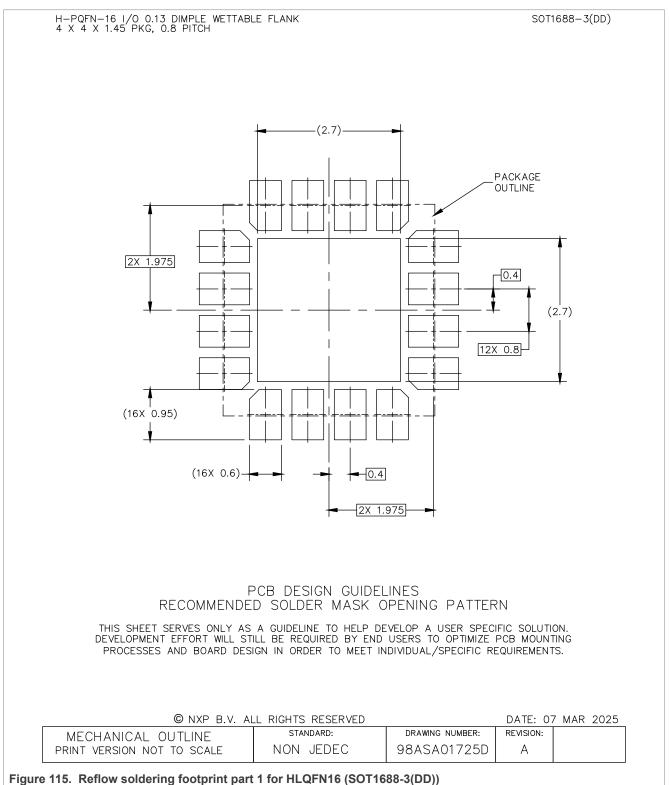

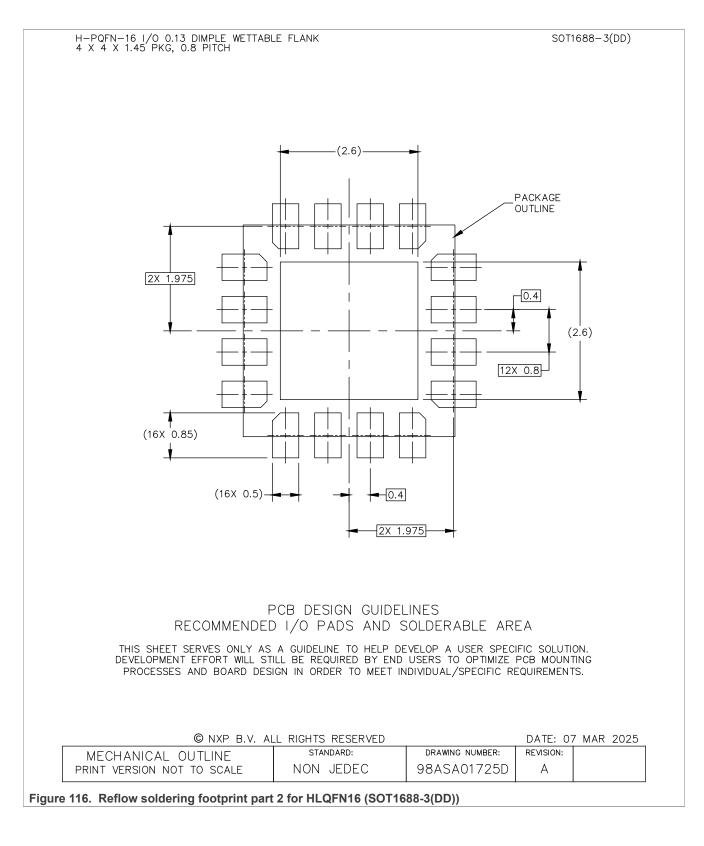

|                      |         | Plastic, thermal enhanced low profile quad flat non-leaded package, dimple deburr wettable flank; 16 terminals; 0.8 mm pitch; 4 mm x 4 mm x 1.45 mm body | <u>SOT1688-3(DD)</u> |  |  |

## 4.1 Ordering options

# Table 2. Ordering optionsDeviceChannel 0

| Device    | Channel 0 |       | Protocol |  |

|-----------|-----------|-------|----------|--|

|           | Axis      | Range |          |  |

| NXLS95220 | Х         | М     | SPI/DSI3 |  |

| NXLS95230 | Х         | н     | SPI/DSI3 |  |

| NXLS95120 | Z         | М     | SPI/DSI3 |  |

| NXLS95130 | Z         | н     | SPI/DSI3 |  |

| NXLS95620 | Y         | М     | SPI/DSI3 |  |

| NXLS95630 | Y         | н     | SPI/DSI3 |  |

| NXLS96220 | Х         | М     | PSI5     |  |

### Single channel inertial sensor

| Device    | Channel 0 |       | Protocol |

|-----------|-----------|-------|----------|

|           | Axis      | Range |          |

| NXLS96230 | X         | Н     | PSI5     |

| NXLS96120 | Z         | M     | PSI5     |

| NXLS96130 | Z         | Н     | PSI5     |

| NXLS96620 | Y         | M     | PSI5     |

| NXLS96630 | Y         | Н     | PSI5     |

## \_

#### Marking 5

#### **Application diagrams** 6

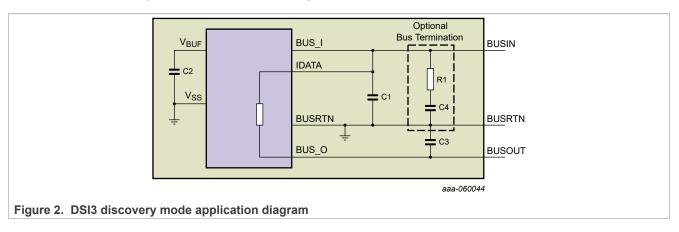

## 6.1 DSI3 application diagrams

### 6.1.1 DSI3 discovery mode application diagram

### Single channel inertial sensor

| Ref<br>Des | Туре               | Typical value description                 | Component value selection and range                                                                                                                                                                                                                                                                    | Comment                                                                                                                                                                                                                |

|------------|--------------------|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R1         | General<br>purpose | 330 Ω, 5 %,<br>200 PPM                    | The system level communication, EMC, and ESD testing determine the optimal value of this component.                                                                                                                                                                                                    | Optional bus termination for high inductance bus<br>wire connections. For optimal EMC performance,<br>this component along with C4 are to be placed as<br>close to the BUS_I and BUSRTN connector pins<br>as possible. |

| C1         | Ceramic            | 220 pF,<br>10 %, 50 V<br>minimum,<br>X7R  | The optimal value of this component should be determined by the system level communication, EMC, and ESD testing.                                                                                                                                                                                      | For optimal EMC performance, this component<br>along with R1 are to be placed as close to the<br>BUS_I and BUSRTN connector pins as possible.                                                                          |

| C2         | Ceramic            | 0.47 μF,<br>10 %, 10 V<br>minimum,<br>X7R | The optimal value of this component should be determined based on the system level micro-cut immunity requirement. To achieve the specified power supply rejection, the minimum value including all tolerances is $0.22 \ \mu$ F. The maximum specified value including all tolerances is $2 \ \mu$ F. | For optimal EMC performance, this component is<br>to be placed as close to the VBUF and BUSRTN<br>pins as possible.                                                                                                    |

| C3         | Ceramic            | 100 pF,<br>10 %, 50 V<br>minimum,<br>X7R  | The optimal value of this component should be determined by the system level communication, EMC, and ESD testing.                                                                                                                                                                                      | For optimal EMC performance, this component<br>is to be placed as close to the BUS_O and<br>BUSRTN connector pins as possible.                                                                                         |

| C4         | Ceramic            | 2.2 nF,<br>10 %, 50 V<br>minimum,<br>X7R  | The optimal value of this component should be determined by the system level communication, EMC, and ESD testing.                                                                                                                                                                                      | Optional bus termination for high inductance bus<br>wire connections. For optimal EMC performance,<br>this component along with R1 are to be placed as<br>close to the BUS_I and BUSRTN connector pins<br>as possible. |

## Table 3. DSI3 discovery mode external component recommendations<sup>[1][2]</sup>

[1] The total bus capacitance must not exceed the values specified in the DSI3<sup>[2]</sup> standard.

[2] The external components are dependent on the bus master and bus impedance and may vary from application to application.

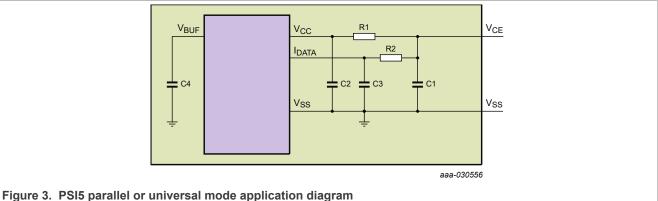

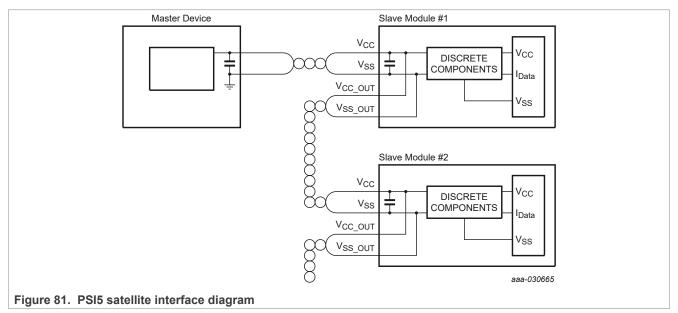

## 6.2 PSI5 application diagrams

### 6.2.1 PSI5 parallel or universal mode application diagram

#### rigure 5. PSI5 parallel of universal mode application diagram

### Table 4. PSI5 parallel or universal mode external component recommendations<sup>[1]</sup>

| Ref<br>Des | Туре               | Description           | Component value selection and range                                                                                                                                                                                    | Purpose                                      |

|------------|--------------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| R1         | General<br>purpose | 82 Ω, 5 %,<br>200 PPM | The optimal value of this component should be determined by the system level communication, EMC, and ESD testing.<br>For proper device function, the minimum value can be $0 \Omega$ . The maximum value is determined | V <sub>CC</sub> filtering and signal damping |

### Single channel inertial sensor

| Ref<br>Des | Туре               | Description                               | Component value selection and range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Purpose                                                                                                                                                                           |

|------------|--------------------|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            |                    |                                           | by the minimum bus voltage provided at the module pin and the minimum operating voltage of the device. To meet the minimum PSI5 operating voltage at the module pin, the maximum resistance including all tolerances is 89.0 $\Omega$ . <sup>[2]</sup>                                                                                                                                                                                                                                                                |                                                                                                                                                                                   |

| R2         | General<br>purpose | 27 Ω, 5 %,<br>200 PPM                     | The optimal value of this component should be determined by the system level communication, EMC, and ESD testing.<br>For proper device function, the minimum value can be 0 $\Omega$ . The maximum value is determined by the minimum bus voltage provided at the module pin. To meet the minimum PSI5 operating voltage at the module pin, the maximum resistance including all tolerances is 66.6 $\Omega$ . If the low response current is used, the maximum resistance including all tolerances is 133 $\Omega$ . | I <sub>DATA</sub> filtering and signal damping                                                                                                                                    |

| C1         | Ceramic            | 2.2 nF, 10<br>%, 50 V<br>minimum,<br>X7R  | The optimal value of this component should be determined by the system level communication, EMC, and ESD testing                                                                                                                                                                                                                                                                                                                                                                                                      | $V_{\rm CC}$ power supply decoupling and signal damping. For optimal EMC performance, this component is to be placed as close to the BUS_I and BUSRTN connector pins as possible. |

| C2         | Ceramic            | 15 nF, 10<br>%, 50 V<br>minimum,<br>X7R   | The optimal value of this component should be determined by the system level communication, EMC, and ESD testing <sup>[3]</sup>                                                                                                                                                                                                                                                                                                                                                                                       | V <sub>CC</sub> power supply decoupling. For optimal EMC performance, this component is to be placed as close to the BUS_I and BUSRTN pins as possible.                           |

| C3         | Ceramic            | 470 pF, 10<br>%, 50 V<br>minimum,<br>X7R  | The optimal value of this component should be determined by the system level communication, EMC, and ESD testing                                                                                                                                                                                                                                                                                                                                                                                                      | I <sub>DATA</sub> Filtering and Signal Damping                                                                                                                                    |

| C4         | Ceramic            | 0.47 µF,<br>10 %, 10 V<br>minimum,<br>X7R | The optimal value of this component should be determined based on the system level micro-cut immunity requirement. To achieve the specified power supply rejection, the minimum value including all tolerances is $0.22 \ \mu\text{F}$ . The maximum specified value including all tolerances is $2 \ \mu\text{F}$ .                                                                                                                                                                                                  | For optimal EMC performance, this component is to be placed as close to the VBUF and BUSRTN pins as possible.                                                                     |

## Table 4. PSI5 parallel or universal mode external component recommendations<sup>[1]</sup>...continued

[1] The total bus capacitance must not exceed the values specified in the PSI5 standard.

[2] R1 must be sized to handle both the programming current at the maximum rated temperature for programming and the operating current at the maximum rated temperature for operation.

[3] If the high baud rate is used, NXP recommends reducing the value of C2. The actual value depends on the bus configuration and number of slaves.

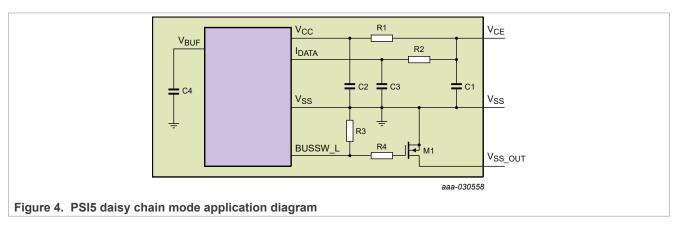

### 6.2.2 PSI5 daisy chain mode application diagram

### Single channel inertial sensor

|            |                     | ,                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                               |

|------------|---------------------|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ref<br>Des | Туре                | Description                               | Component value selection and range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Purpose                                                                                                                                                                                       |

| R1         | General<br>purpose  | 82 Ω, 5 %,<br>200 PPM                     | The optimal value of this component should be<br>determined by the system level communication,<br>EMC, and ESD testing.<br>For proper device function, the minimum<br>value can be 0 Ohms. The maximum value is<br>determined by the minimum bus voltage provided<br>at the module pin and the minimum operating<br>voltage of the device. To meet the minimum<br>PSI5 operating voltage at the module pin, the<br>maximum resistance including all tolerances is                                                                                  | V <sub>CC</sub> filtering and signal damping                                                                                                                                                  |

| R2         | General<br>purpose  | 27 Ω, 5 %,<br>200 PPM                     | 89.0 Ohms.<br>The optimal value of this component should be<br>determined by the system level communication,<br>EMC, and ESD testing.<br>For proper device function, the minimum<br>value can be 0 Ohms. The maximum value<br>is determined by the minimum bus voltage<br>provided at the module pin. To meet the minimum<br>PSI5 operating voltage at the module pin, the<br>maximum resistance including all tolerances is<br>66.6 Ohms. If the low response current is used,<br>the maximum resistance including all tolerances<br>is 133 Ohms. | I <sub>DATA</sub> filtering and signal damping                                                                                                                                                |

| R3         | General<br>purpose  | 20 kΩ, 5 %,<br>200 PPM                    | The optimal value of this component should be determined by the system level communication, EMC, and ESD testing.                                                                                                                                                                                                                                                                                                                                                                                                                                  | Gate resistor for external low side daisy chain<br>FET                                                                                                                                        |

| C1         | Ceramic             | 2.2 nF, 10<br>%, 50 V<br>minimum,<br>X7R  | The optimal value of this component should be determined by the system level communication, EMC, and ESD testing.                                                                                                                                                                                                                                                                                                                                                                                                                                  | V <sub>CC</sub> power supply decoupling and signal<br>damping. For optimal EMC performance, this<br>component is to be placed as close to the BUS_I<br>and BUSRTN connector pins as possible. |

| C2         | Ceramic             | 15 nF, 10<br>%, 50 V<br>minimum,<br>X7R   | The optimal value of this component should be determined by the system level communication, EMC, and ESD testing.                                                                                                                                                                                                                                                                                                                                                                                                                                  | V <sub>CC</sub> power supply decoupling. For optimal EMC performance, this component is to be placed as close to the BUS_I and BUSRTN pins as possible.                                       |

| C3         | Ceramic             | 470 pF, 10<br>%, 50 V<br>minimum,<br>X7R  | The optimal value of this component should be determined by the system level communication, EMC, and ESD testing.                                                                                                                                                                                                                                                                                                                                                                                                                                  | I <sub>DATA</sub> Filtering and Signal Damping                                                                                                                                                |

| C4         | Ceramic             | 0.47 µF,<br>10 %, 10 V<br>minimum,<br>X7R | The optimal value of this component should be determined based on the system level micro-cut immunity requirement. To achieve the specified power supply rejection, the minimum value including all tolerances is $0.22 \ \mu$ F. The maximum specified value including all tolerances is $2 \ \mu$ F.                                                                                                                                                                                                                                             | For optimal EMC performance, this component is to be placed as close to the VBUF and BUSRTN pins as possible.                                                                                 |

| R4         | General<br>purpose  | 100 kΩ, 5 %,<br>200 PPM                   | The optimal value of this component should be determined by the system level communication, EMC, and ESD testing.                                                                                                                                                                                                                                                                                                                                                                                                                                  | Gate pulldown resistor for external low side daisy chain FET                                                                                                                                  |

| M1         | N-Channel<br>MOSFET | NTR4501NT1<br>G, or similar               | The optimal value of this component should be determined by the system level communication, EMC, and ESD testing.                                                                                                                                                                                                                                                                                                                                                                                                                                  | Low side daisy chain transistor                                                                                                                                                               |

# Table 5. PSI5 daisy chain mode external component recommendations

[1] [2]

The total bus capacitance must not exceed the values specified in the PSI5 standard. R1 must be sized to handle both the programming current at the maximum rated temperature for programming and the operating current at the maximum rated temperature for operation. If the high baud rate is used, NXP recommends reducing the value of C2. The actual value depends on the bus configuration and number of slaves.

[3]

Single channel inertial sensor

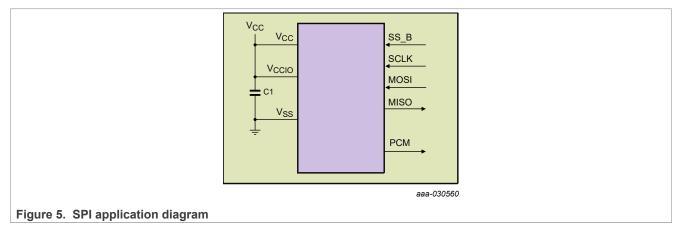

# 6.3 SPI application diagram

#### Table 6. SPI external component recommendations

| Ref Des | Туре    | Typical value description | Comment                                                                                                                                               |

|---------|---------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| C1      | Ceramic | X7R                       | $V_{CC}$ power supply decoupling. For optimal EMC performance, this component is to be placed as close to the $V_{CC}$ and $V_{SS}$ pins as possible. |

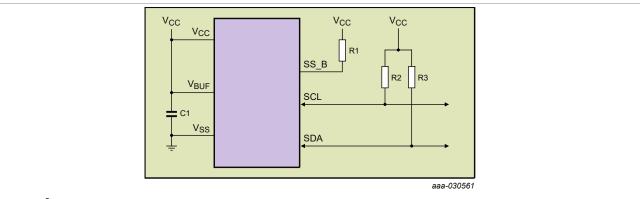

# 6.4 I<sup>2</sup>C application diagram

### Figure 6. I<sup>2</sup>C application diagram

# Table 7. I<sup>2</sup>C external component recommendations

| Ref Des | Туре            | Description                        | Purpose                                         |

|---------|-----------------|------------------------------------|-------------------------------------------------|

| R1      | General purpose | 1000 Ω, 5 %, 200 PPM               | I <sup>2</sup> C selection pin pull-up resistor |

| R2      | General purpose | 1000 Ω, 5 %, 200 PPM               | Serial clock pull-up resistor                   |

| R3      | General purpose | 1000 Ω, 5 %, 200 PPM               | Serial data pull-up resistor                    |

| C1      | Ceramic         | 0.1 μF, 10 %, 10 V Minimum,<br>X7R | V <sub>CC</sub> power supply decoupling         |

Single channel inertial sensor

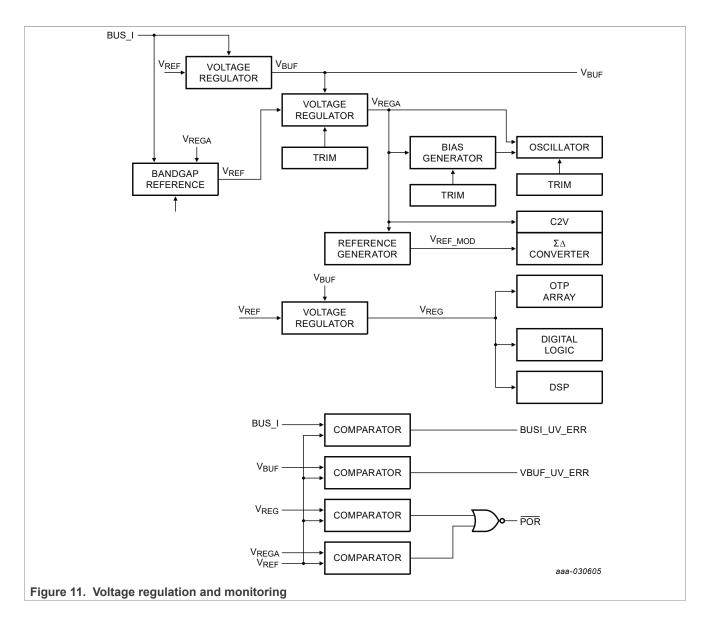

# 7 Block diagram

Single channel inertial sensor

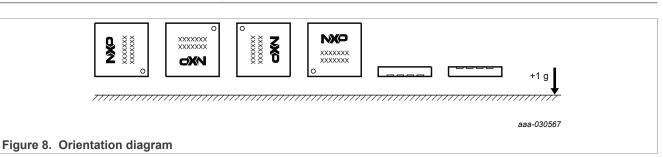

# 8 Device orientation diagrams

Table 8. Single axis device orientation

|   |           | own       | o martin<br>NGC |           |           | []        |

|---|-----------|-----------|-----------------|-----------|-----------|-----------|

| X | Ch0: 0 g  | Ch0: +1 g | Ch0: 0 g        | Ch0: –1 g | Ch0: 0 g  | Ch0: 0 g  |

| Y | Ch0: –1 g | Ch0: 0 g  | Ch0: +1 g       | Ch0: 0 g  | Ch0: 0 g  | Ch0: 0 g  |

| Z | Ch0: 0 g  | Ch0: 0 g  | Ch0: 0 g        | Ch0: 0 g  | Ch0: +1 g | Ch0: –1 g |

# **9 Pinning information**

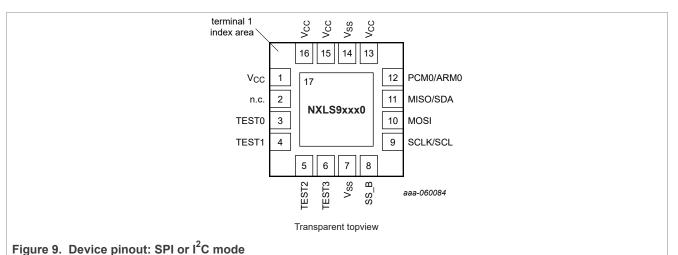

# 9.1 Pinning: SPI or I<sup>2</sup>C mode

# 9.2 Pin description: SPI or I<sup>2</sup>C mode

| Table 9. | Device | pinout: | SPI | or l | l <sup>2</sup> C | mode |

|----------|--------|---------|-----|------|------------------|------|

|----------|--------|---------|-----|------|------------------|------|

| Table J. De | able 5. Device photo. SPT of 1 C mode |            |                                                                                                                                         |  |  |  |

|-------------|---------------------------------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Pin         | Pin Name                              | Definition | Description                                                                                                                             |  |  |  |

| 1           | V <sub>CC</sub>                       | Supply     | NXP recommends that this pin be connected to $V_{\mbox{CC}}.$ Optionally, this pin can be unterminated.                                 |  |  |  |

| 2           | n.c.                                  | No connect | This pin is not connected internally. NXP recommends that these pins be unterminated. Optionally, this pin can be tied to $V_{\rm SS}.$ |  |  |  |

## Single channel inertial sensor

| Pin        | Pin Name        | Definition                        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------------|-----------------|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3, 4, 5, 6 | TEST            | Test Pin                          | NXP recommends that these pins be unterminated. Optionally, this pin can be tied to $V_{\text{SS}}.$                                                                                                                                                                                                                                                                                                                                                                                                           |

| 7, 14      | V <sub>SS</sub> | Supply Return                     | This pin is the supply return node.                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 8          | SS_B            | Slave select                      | In SPI mode, this input pin provides the slave select for the SPI port. An internal pull-up device is connected to this pin.<br>In $I^2C$ mode, this pin must be connected to $V_{BUF}$ with an external pull-up resistor as shown in Figure 6.                                                                                                                                                                                                                                                                |

| 9          | SCLK/SCL        | SPI Clock                         | In SPI mode, this input pin provides the serial clock. An internal pull-down device is connected to this pin.<br>In $I^2C$ mode, this input pin provides the serial clock. This pin must be connected to V <sub>BUF</sub> with an external pull-up resistor as shown in <u>Figure 6</u> .                                                                                                                                                                                                                      |

| 10         | MOSI            | SPI Data In                       | In SPI mode, this pin functions as the serial data input to the SPI port. An internal pull-down device is connected to this pin.<br>In $I^2C$ mode, NXP recommends that this pin be unterminated. Optionally, this pin can be connected to V <sub>SS</sub> .                                                                                                                                                                                                                                                   |

| 11         | MISO/SDA        | SPI Data Out                      | In SPI mode, this pin functions as the serial data output.<br>In I <sup>2</sup> C mode, this pin functions as the serial data input/output. This pin must be<br>connected to $V_{BUF}$ with an external pull-up resistor as shown in Figure 6.                                                                                                                                                                                                                                                                 |

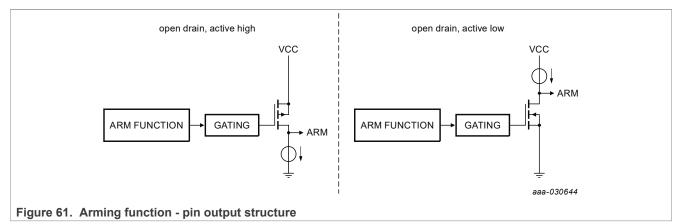

| 12         | PCM0 / ARM0     | Channel 0<br>PCM<br>Channel 0 Arm | <ul> <li>This pin has multiplexed functions:</li> <li>When the channel 0 arming output is selected, the pin can be configured as an open-drain, active low output with a pull-up current; or an open-drain, active high output with a pull-down current.</li> <li>When PCM mode is selected, this pin can be configured as a digital output with PCM signal proportional to the channel 0 sensor data.</li> <li>If unused, or in I<sup>2</sup>C mode, NXP recommends that this pin be unterminated.</li> </ul> |

| 13, 15, 16 | V <sub>CC</sub> | Supply                            | This pin is connected to the supply for the device. An external capacitor must be connected between this pin and $V_{SS}$ as shown in <u>Figure 5</u> and <u>Figure 6</u> .                                                                                                                                                                                                                                                                                                                                    |

| 17         | PAD             | Die Attach Pad                    | This pin is the die attach flag, and must be connected to $V_{SS}$ . See <u>Section 16</u> for die attach pad connection details.                                                                                                                                                                                                                                                                                                                                                                              |

# Table 9. Device pinout: SPI or I<sup>2</sup>C mode...continued

Single channel inertial sensor

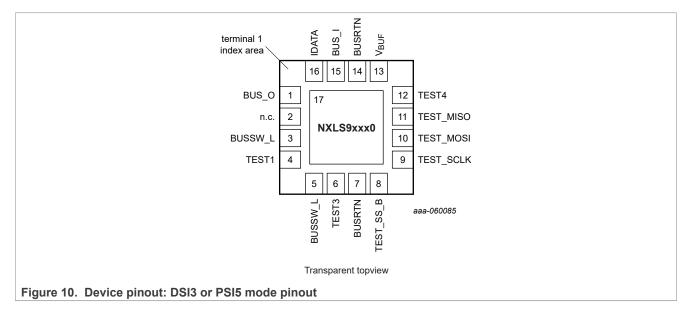

# 9.3 Pinning: DSI3 or PSI5 mode

# 9.4 Pin description: DSI3 or PSI5 mode

Table 10. Device pinout: DSI3 or PSI5 mode pinout

| Pin      | Pin Name               | Definition                    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------|------------------------|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1        | BUS_O                  | Supply Out                    | This pin is connected to the IDATA pin through an internal sense resistor<br>and provides the supply connection to the next slave in a daisy chain<br>configuration.<br>In DSI3 mode, an external capacitor must be connected between this pin and<br>$V_{SS}$ as shown in Figure 2.<br>In PSI5 mode, NXP recommends that this pin be unterminated. Optionally,<br>this pin can be connected to IDATA.                                                                                                         |

| 2        | NC                     | No Connect                    | This pin is not connected internally. NXP recommends that these pins be unterminated. Optionally, this pin can be tied to $V_{\rm SS}$ .                                                                                                                                                                                                                                                                                                                                                                       |

| 4, 6, 12 | TEST                   | Test Pin                      | NXP recommends that these pins be unterminated. Optionally, this pin can be tied to $V_{\text{SS}}.$                                                                                                                                                                                                                                                                                                                                                                                                           |

| 3, 5     | BUSSW_L                | Low Side Bus<br>Switch Driver | In PSI5 daisy chain mode, these pins are connected to the gate of an N-<br>channel FET which connects BUSRTN to the next slave in the daisy chain.<br>An external pulldown resistor is required on the gate of the N-channel FET<br>as shown in Figure 4. Note: both pins provide the identical function. It is<br>necessary to connect only one pin is to the bus switch gate.<br>If unused, or in DSI3 mode, NXP recommends that this pin be unterminated.<br>Optionally, this pin can be tied to $V_{SS}$ . |

| 7, 14    | BUSRTN/V <sub>SS</sub> | Supply Return                 | This pin is the supply return node.                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 8        | TEST_SS_B              | Slave select                  | NXP recommends that this pin be unterminated. Optionally, this pin can be connected to $V_{\mbox{BUF}}.$                                                                                                                                                                                                                                                                                                                                                                                                       |

| 9        | TEST_SCLK              | SPI Clock                     | NXP recommends that this pin be unterminated. Optionally, this pin can be connected to $V_{SS}.$                                                                                                                                                                                                                                                                                                                                                                                                               |

| 10       | TEST_MOSI              | SPI Data In                   | NXP recommends that this pin be unterminated. Optionally, this pin can be connected to $V_{\text{SS}}.$                                                                                                                                                                                                                                                                                                                                                                                                        |

### Single channel inertial sensor

| Pin | Pin Name         | Definition                              | Description                                                                                                                                                                                                                                                                                         |

|-----|------------------|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11  | TEST_MISO        | SPI Data Out                            | This pin must be left unconnected.                                                                                                                                                                                                                                                                  |

| 13  | V <sub>BUF</sub> | Power<br>Supply                         | This pin is connected to a buffer regulator for the internal circuitry. The buffer regulator supplies the internal regulators to provide immunity from EMC and supply dropouts. An external capacitor must be connected between this pin and $V_{SS}$ as shown in Figure 2, Figure 3, and Figure 4. |

| 15  | BUS_I            | Supply and<br>Communication<br>Receiver | This pin is connected to the supply line and supplies power to the device. An external filter must be connected between this pin and BUSRTN as shown in Figure 2, Figure 3, and Figure 4.                                                                                                           |

| 16  | IDATA            | Communication<br>Transmitter            | This pin modulates the response current for DSI3 and PSI5 communication.<br>An external filter must be connected between this pin and BUSRTN as shown<br>in <u>Figure 2</u> , <u>Figure 3</u> , and <u>Figure 4</u> .                                                                               |

| 17  | PAD              | Die Attach Pad                          | This pin is the die attach flag, and must be connected to $V_{SS}$ . See <u>Section 16</u> for die attach pad connection details.                                                                                                                                                                   |

#### Table 10. Device pinout: DSI3 or PSI5 mode pinout...continued

# **10** Electrical characteristics

<u>Section 10.1</u> through <u>Section 10.20</u> contain tables with "Test notes". The note identifiers cross reference to the identifiers and descriptions found in <u>Table 11</u>.

| Table | 11. | Test | notes | legend |

|-------|-----|------|-------|--------|

|-------|-----|------|-------|--------|

| Identifier | Description                                                                                                                                                                                                      |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| *          | Indicates critical characteristic.                                                                                                                                                                               |

| 1          | Parameter tested 100 % at final test. Temperature = -40 °C, 25 °C, and 105 °C, V <sub>BUS_I</sub> = 7 V, Unless otherwise stated                                                                                 |

| 2          | Parameter tested 100 % at final test during safe launch                                                                                                                                                          |

| 3          | Parameter verified by pass/fail testing at final test                                                                                                                                                            |

| 4          | Parameter verified by pass/fail testing at final test during safe launch                                                                                                                                         |

| 5          | Parameter verified by qualification testing                                                                                                                                                                      |

| 6          | Parameter verified by characterization                                                                                                                                                                           |

| 7          | Functionality verified by modeling, simulation and/or design verification.                                                                                                                                       |

| 8          | Circuit integrity assured through IDDQ and scan testing. Timing is determined by internal system clock frequency.                                                                                                |

| 9          | Parameter verified by functional evaluation                                                                                                                                                                      |

| 10         | Thermal resistance provided with device mounted to a 2 layer, 1.6 mm FR4 PCB as documented in AN1902 with 1 signal layer and 1 ground layer.                                                                     |

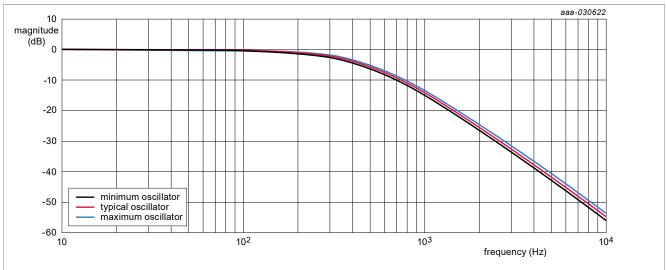

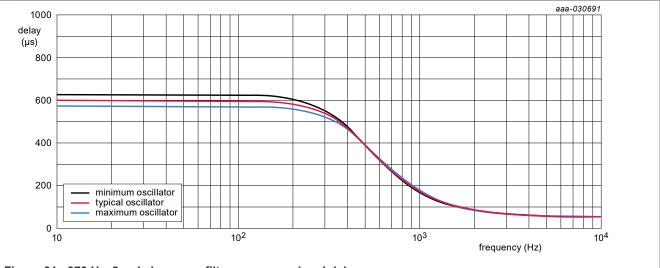

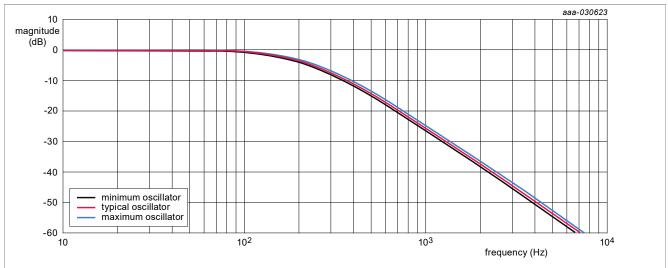

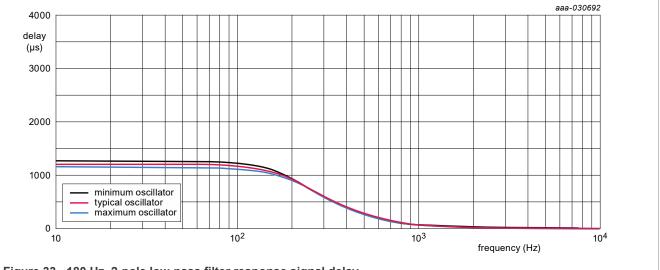

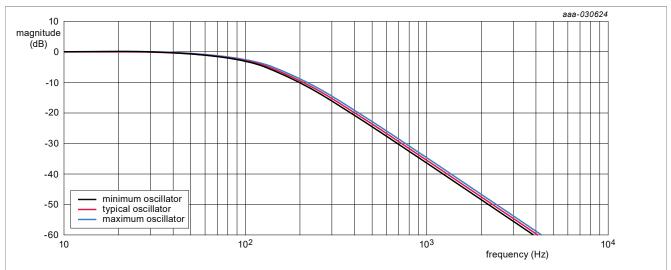

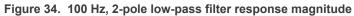

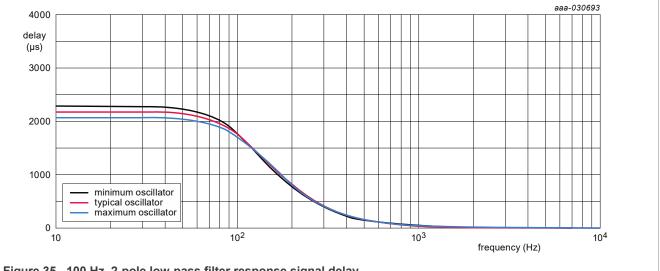

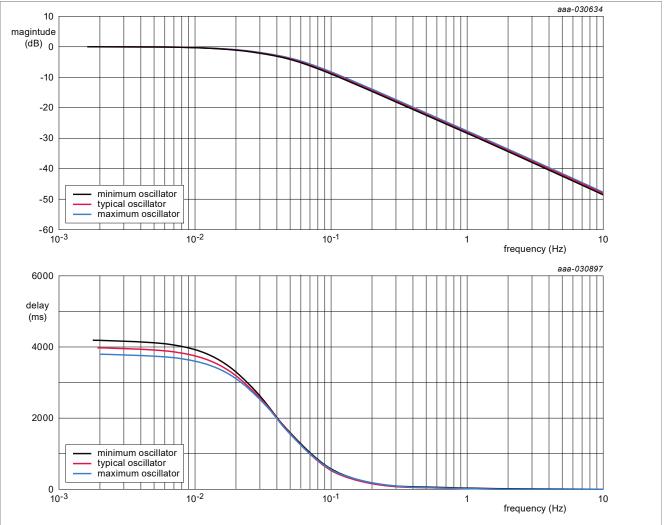

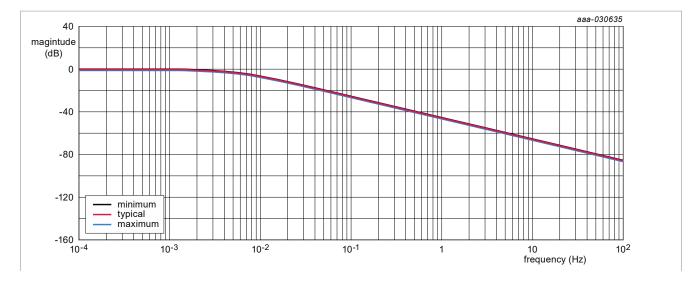

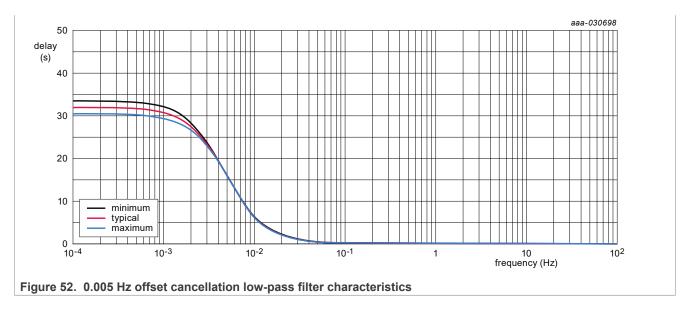

| 11         | Digital low-pass filter characteristics are specified independently and do not include g-cell characteristics.<br>Higher frequency filters will have lower system cut-off frequencies due to the g-cell damping. |

## 10.1 Maximum ratings

Maximum ratings are the extreme limits to which the device can be exposed without permanently damaging it.

| #       | 12. Maximum ratings Rating                                                 | Symbol               | Value                         | Unit | Test         |

|---------|----------------------------------------------------------------------------|----------------------|-------------------------------|------|--------------|

| #       | Raung                                                                      | Symbol               | value                         | Unit | notes        |

| Supply  | voltage (BUS_I/V <sub>CC</sub> , IDATA, BUS_O)                             |                      |                               |      |              |

| 3381    | Reverse Current externally limited to $\leq$ 160 mA, t $\leq$ 100 ms       | BUS_I <sub>REV</sub> | -0.7                          | V    | <u>6</u>     |

| 3383    | Continuous                                                                 | BUS_I <sub>MAX</sub> | +20.0                         | V    | <u>6</u>     |

| 3384    | V <sub>BUF</sub>                                                           | VBUFMAX              | -0.3 to +7.0                  | V    | <u>6</u>     |

| 3385    | SCLK, SS_B, MOSI, MISO (High Z), PCM0/ARM0                                 | VIOMAX               | –0.3 to V <sub>BUF</sub> +0.3 | V    | <u>6</u>     |

| 3386    | BUS_I/V <sub>CC</sub> , IDATA, and BUS_O Continuous Current                | I <sub>SUPMAX</sub>  | 200                           | mA   | <u>6</u>     |

| 3387    | Powered Shock (six sides, 0.5 ms duration)                                 | g <sub>pms</sub>     | ±2000                         | g    | <u>5</u>     |

| 3390    | Unpowered Shock (six sides, 0.5 ms duration)                               | <b>g</b> shock       | ±2000                         | g    | <u>5</u>     |

| 3389    | Powered Shock (six sides, 0.5 ms duration)                                 | g <sub>pms</sub>     | ±4000                         | g    | <u>9</u>     |

| 3388    | Unpowered Shock (six sides, 0.5 ms duration)                               | <b>g</b> shock       | ±4000                         | g    | <u>9</u>     |

| 3391    | Drop Shock (to concrete, tile or steel surface, 10 drops, any orientation) | h <sub>DROP</sub>    | 1.5                           | m    | 5            |

| Electro | ostatic Discharge (per AEC-Q100 <sup>[4]</sup> ), External Pins            |                      |                               |      |              |

| 3392    | BUS_I/V <sub>CC</sub> , IDATA, BUS_O, BUSRTN, HBM (100 pF, 1.5 kΩ)         | V <sub>ESD</sub>     | ±4000                         | V    | <u>5</u>     |

| Electro | ostatic Discharge (per AEC-Q100 <sup>[4]</sup> )                           |                      |                               | I    | 1            |

| 3393    | HBM (100 pF, 1.5 kΩ)                                                       | V <sub>ESD</sub>     | ±2000                         | V    | <u>5</u>     |

| 3395    | CDM (R = 0 Ω)                                                              | V <sub>ESD</sub>     | ±750                          | V    | <u>5</u>     |

| Tempe   | rature Range                                                               | 1                    |                               | 1    |              |

| 3396    | Storage                                                                    | T <sub>stg</sub>     | -55 to +150                   | °C   | <u>5</u>     |

| 3397    | Junction                                                                   | TJ                   | -55 to +150                   | °C   | Z            |

| 3400    | Thermal Resistance                                                         | θ <sub>JA</sub>      | 47                            | °C/W | <u>7, 10</u> |

# 10.2 Operating range - DSI / PSI5

### Table 13. Operating range - DSI / PSI5

| #       | Characteristic                                                                       | Symbol                        | Min                            | Тур  | Max                  | Units  | Test<br>notes  |

|---------|--------------------------------------------------------------------------------------|-------------------------------|--------------------------------|------|----------------------|--------|----------------|

| 3398    | DSI3 Supply Voltage (V <sub>HIGH</sub> ), Measured at BUS_I                          | V <sub>HIGH</sub>             | _                              |      | 20.0                 | V      | <u>5, 6, 7</u> |

| 10468   | DSI3 Supply Voltage (V <sub>LOW</sub> ) Measured at BUS_I                            | V <sub>LOW</sub>              | 4.0                            | _    | _                    | V      | 1              |

| 10467   | PSI5 Supply Voltage (Excluding Sync Pulse)                                           | V <sub>PSI5</sub>             | 4.0                            | —    | 16.5                 | V      | 1              |

| 10466   | Supply Voltage (Undervoltage)                                                        | V <sub>BUS_I_UV</sub>         | V <sub>BUS_</sub><br>I_UV_F    | _    | V <sub>LOW_min</sub> | V      | <u>3, 6</u>    |

| 10472   | Supply Power On Ramp Rate                                                            | V <sub>CC</sub> _<br>RAMP_SAT | 0.00001                        | —    | 10                   | V / µs | <u>6</u>       |

| Progran | ming Voltage (I <sub>PP</sub> $\leq$ 5 mA, 10 °C $\leq$ T <sub>A</sub> $\leq$ 40 °C) |                               |                                |      |                      |        |                |

| 10469   | Applied to BUS_I                                                                     | V <sub>PP</sub>               | 9.0                            | 10.0 | 11.0                 | V      | <u>3, 6</u>    |

| ESD Op  | erating Voltage (No Device Reset, C <sub>BUS_IN</sub> = 220 pF)                      |                               |                                |      | 1                    | 1      | ·              |

| 10470   | Maximum ±15 kV Air Discharge, 330 pF, 2.0 kΩ                                         | V <sub>BUS_I_ESD</sub>        | V <sub>BUS_I_</sub><br>LOW_min | —    | 10.0                 | V      | <u>7, 9</u>    |

### Single channel inertial sensor

#### Table 13. Operating range - DSI / PSI5...continued

| #        | Characteristic                                | Symbol         | Min | Тур | Мах            | Units | Test<br>notes  |

|----------|-----------------------------------------------|----------------|-----|-----|----------------|-------|----------------|

| Operatin | g Temperature Range                           |                | ΤL  |     | T <sub>H</sub> |       |                |

| 10471    | Production Tested Operating Temperature Range | T <sub>A</sub> | -40 | —   | +105           | °C    | 1              |

| 10490    | Guaranteed Operating Temperature Range        | T <sub>A</sub> | -40 | —   | +125           | °C    | <u>5, 6, 7</u> |

# 10.3 Operating range - SPI / I<sup>2</sup>C

## Table 14. Operating range - SPI / I<sup>2</sup>C

| #       | Characteristic                                                                                 | Symbol                        | Min                   | Тур | Мах                          | Units | Test<br>notes  |

|---------|------------------------------------------------------------------------------------------------|-------------------------------|-----------------------|-----|------------------------------|-------|----------------|

| 10501   | Supply Voltage (V <sub>CC</sub> = V <sub>BUF</sub> ) Measured at V <sub>BUF</sub>              | V <sub>CC_BUF</sub>           | —                     | _   | 5.25                         | V     | <u>5, 6, 7</u> |

| 10502   | Supply Voltage (V <sub>CC</sub> = V <sub>BUF</sub> ) Measured at V <sub>BUF</sub> $\therefore$ | V <sub>CC_BUF</sub>           | 3.135                 | _   | -                            | V     | 1              |

| 10504   | Supply Voltage (Undervoltage)                                                                  | V <sub>BUF</sub> _<br>UV_OP   | V <sub>BUF_UV_F</sub> | —   | V <sub>CC</sub> _<br>BUF_min | V     | <u>3, 6</u>    |

| 10509   | Supply Power On Ramp Rate                                                                      | V <sub>CC</sub> _<br>RAMP_SPI | 0.00001               | —   | 10                           | V/µs  | <u>6</u>       |

| Operati | ng Temperature Range                                                                           |                               | TL                    |     | Т <sub>Н</sub>               |       |                |

| 10507   | Production Tested Operating Temperature Range                                                  | T <sub>A</sub>                | -40                   | _   | +105                         | °C    | 1              |

| 10508   | Guaranteed Operating Temperature Range                                                         | T <sub>A</sub>                | -40                   | _   | +125                         | °C    | <u>5, 6, 7</u> |

# 10.4 Electrical characteristics - supply and I/O

#### Table 15. Electrical characteristics - supply and I/O

$V_{BUS\_I\_L\_min} \leq (V_{BUS\_I} - V_{SS}) \leq V_{BUS\_I\_H\_max}, T_L \leq T_A \leq T_H, \Delta T \leq 25 \text{ °C/min, unless otherwise specified}$

| #                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Characteristic                                                                                        |            | Symbol                  | Min                            | Тур                            | Мах                            | Units | Test<br>notes |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|------------|-------------------------|--------------------------------|--------------------------------|--------------------------------|-------|---------------|

| Quiescent Supply Current $10512$ $V_{BUS_{-1}} = 4 V$ , DSI, PSI5         1 $V_{BUS_{-1}} = 10 V$ , DSI, PSI5         1         1 $V_{BUS_{-1}} = 10 V$ , DSI, PSI5         1         1 $V_{BUS_{-1}} = 16.5 V$ , DSI, PSI5         1         1 $V_{BUS_{-1}} = 20 V$ , DSI / PSI5         1         1 $10511$ $V_{BUS_{-1}} = 3.135 V$ , SPI, I <sup>2</sup> C         1         1 $10510$ $V_{BUS_{-1}} = 3.135 V$ , SPI, I <sup>2</sup> C         1         1 $10515$ DSI Low         1         1         1 $10515$ DSI Low         1         1         1 $10519$ DSI High         1         1         1 $10517$ PSI5 Normal         1         1         1 $10517$ PSI5 Low         1         1         1 $10517$ PSI5 Low         1         1         1 $10.77$ PSI5 Low         1         1         1 $10.74$ Regulated Voltage         1         1         1 |                                                                                                       |            | ,                       |                                |                                |                                |       |               |

| 10512                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | V <sub>BUS_I</sub> = 4 V, DSI, PSI5                                                                   | <u>*</u>   | I <sub>q_4_1</sub>      | 4.0                            | _                              | 6.0                            | mA    | 1             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | V <sub>BUS_I</sub> = 10 V, DSI, PSI5                                                                  | <u>*</u>   | I <sub>q_10_1</sub>     | 4.0                            | _                              | 6.0                            | mA    | 1             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | V <sub>BUS_I</sub> = 16.5 V, DSI, PSI5                                                                | *_         | I <sub>q_10_1</sub>     | 4.0                            | —                              | 6.5                            | mA    | 1             |

| 10511                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | V <sub>BUS_I</sub> = 20 V, DSI / PSI5                                                                 | <u>*</u>   | I <sub>q_20_1</sub>     | 4.0                            | _                              | 7.5                            | mA    | 1             |

| 10510                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | V <sub>BUS_I</sub> = 3.135 V, SPI, I <sup>2</sup> C                                                   | *_         | I <sub>q_31_1</sub>     | —                              | —                              | 6.0                            | mA    | <u>3, 6</u>   |

| Respon                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | se Current                                                                                            |            | 1                       | 1                              |                                | 1                              |       |               |

| 10515                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | DSI Low                                                                                               | *_         | I <sub>R_DSI_1</sub>    | l <sub>q</sub> + 10.5          | l <sub>q</sub> + 12.0          | l <sub>q</sub> + 13.5          | mA    | 1             |

| 10519                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | DSI High                                                                                              | <u>*</u>   | I <sub>R_DSI_2</sub>    | I <sub>R_DSI_1</sub><br>+ 10.5 | I <sub>R_DSI_1</sub><br>+ 12.0 | I <sub>R_DSI_1</sub><br>+ 13.5 | mA    | 1             |

| 10518                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | PSI5 Normal                                                                                           | <u>*</u> _ | I <sub>R_PSI5</sub>     | l <sub>q</sub> + 22.0          | l <sub>q</sub> + 26.0          | l <sub>q</sub> + 30.0          | mA    | 1             |

| 10517                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | PSI5 Low                                                                                              | *_         | I <sub>R_PSI5_Low</sub> | l <sub>q</sub> + 11.0          | l <sub>q</sub> + 13.0          | l <sub>q</sub> + 15.0          | mA    | <u>6</u>      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | In-Rush Current (No external Components)                                                              |            | t <sub>INRUSH</sub>     | _                              | -                              | 40                             | mA    | <u>6</u>      |

| Internal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ly Regulated Voltage                                                                                  |            | 1                       | 1                              | 1                              | 1                              | 1     |               |

| 10522                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Internally Regulated Voltage (V <sub>BUF</sub> , V <sub>BUS_I</sub> = 4 V, V <sub>BUS_I</sub> = 20 V) |            | V <sub>BUF</sub>        | 2.85                           | 3.00                           | 3.15                           | V     | 1             |

## Single channel inertial sensor

| #                     | Characteristic                                                      | Symbol                          | Min                         | Тур                        | Max                         | Units | Test<br>notes       |

|-----------------------|---------------------------------------------------------------------|---------------------------------|-----------------------------|----------------------------|-----------------------------|-------|---------------------|

| Low Vol               | tage Detection Threshold                                            | L                               |                             |                            |                             |       |                     |

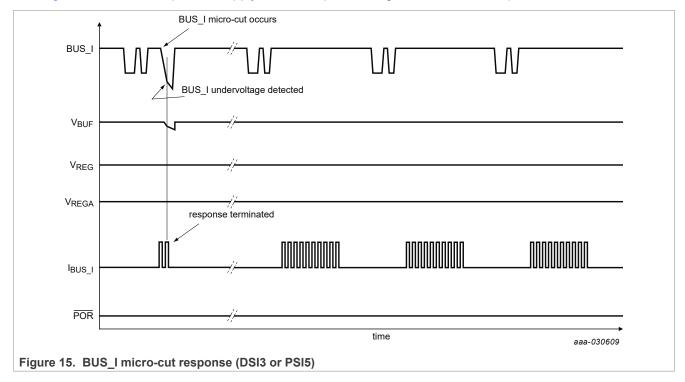

| 10523                 | BUS_I Falling, COMMTYPE = 2, 3, 4, 5, 6, 7                          | * V <sub>BUS_</sub><br>I_UV_F   | 3.85                        | 3.95                       | 4.00                        | V     | <u>3, 6</u>         |

|                       | BUS_I Falling, COMMTYPE = 0, 1                                      | V <sub>BUS_</sub><br>I_UV_01    | 3.31                        | 3.50                       | 3.67                        | V     | <u>6</u>            |

| 10542                 | V <sub>BUF</sub> Falling                                            | · V <sub>BUF_UV_F</sub>         | 2.64                        | 2.74                       | 2.84                        | V     | <u>3, 6</u>         |

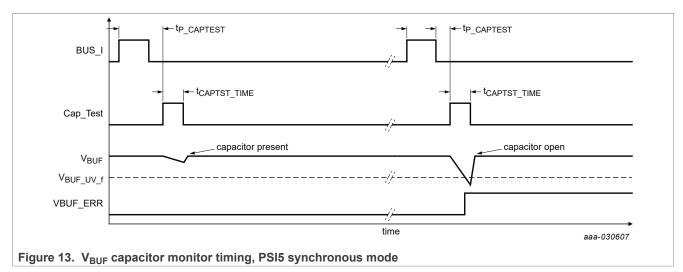

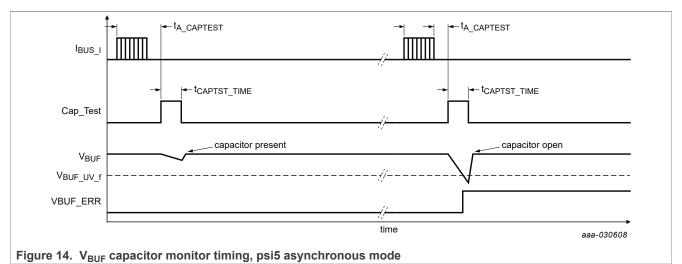

| V <sub>BUF</sub> Ex   | ternal Capacitor                                                    | I                               |                             | 1                          | I                           |       |                     |