Highly configurable 8/4-channel 24/16 bits ±25 V universal input analog front-end with excitation sources

Rev. 5.0 — 17 February 2025

Product data sheet

#### **Document information**

| Information | Content                                                                                                                           |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------|

| Keywords    | NAFE13388, NAFE13188, NAFE13148, NAFE13144, 8/4-channel, analog front-end (AFE), 24-bit, 16-bit ADC resolution, excitation source |

| Abstract    | Highly configurable multichannel precision AFE for industrial applications.                                                       |

# 1 General description

The NAFE13388 is a highly configurable industrial-grade multichannel universal input analog front-end (AFE) family that meets high-precision measurement requirements. The family includes parts that differ for high-speed/low-power, factory-calibrated or not, 24 bits or 16 bits ADC, 8 or 4 channels. See the comparison table for more details. The device integrates low-leakage, high-voltage (HV) fast multiplexers, low-offset and low-drift programmable gain amplifier (PGA) and buffers, high data-rate 24/16-bit sigma-delta analog-to-digital converter (ADC), precise voltage and current excitation source, and low-drift voltage reference. All of the HV analog pins are diode-protected internally for electromagnetic compatibility (EMC) and miswiring scenarios. The NAFE13388 family is equipped with various diagnostic and supplies supervisory circuitry for condition monitoring and anomaly detection. Two precise calibration voltage sources are made available for ease of end-to-end system self-calibration and predictive maintenance.

The NAFE13388 is the superset part that is representative of the whole family. The document refers to this as a generic part. See the dedicated section (number of channels, ADC resolution, calibration) for the detailed information of the specific part .

The NAFE13388 family of products is designed for programmable logic controllers (PLCs), I/O modules, data loggers, instrumentation, and high-precision sensor and data acquisition systems.

# 2 Features and benefits

- · Eight or four configurable HV inputs

- Single-ended or differential, with ranges up to ±25 V

- Independent configurations for voltage, current, resistance, resistance temperature detector (RTD), thermocouple

- Overvoltage protected up to ±36 V for less than one hour

- Programmable gain: x0.2 to x16

- Fast data rates

- 7.5 SPS to 288 kSPS

- Simultaneous 50 Hz/60 Hz line rejection

- ENOB: 17-bit at 72 kSPS

- High accuracy

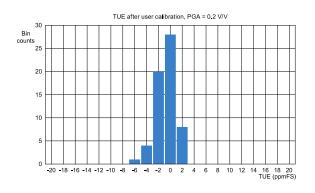

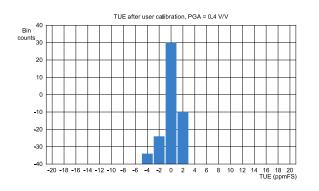

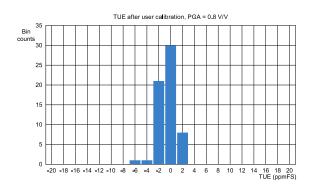

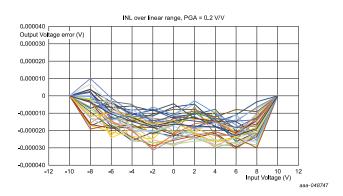

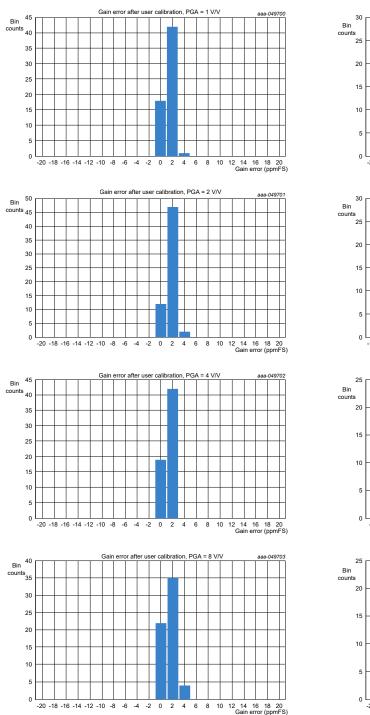

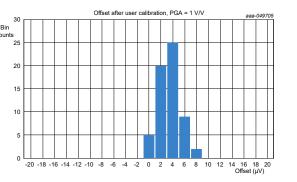

- 0.005 %FS accuracy at room after user calibration

- 0.1 %FS accuracy over -25 ℃ to 105 ℃

- System calibration

- End-to-end calibration with integrated precise voltage sources

- Accurate factory-calibrated products available

- ±3 °C internal temperature sensor

- Precise excitation voltage and current sources

- 0.2% internal oscillator accuracy at room temperature

- Diagnostic system for faults detection and prediction

- CRC error detection

- Ten GPIOs

- 32 MHz SPI interface

- Robust 7.5 kV HBM ESD and IEC61000-4-5 2 kV surge protection

- Power supply: HV: ±7 V to ±24 V, LV: 3.3 V

- 150 mW low power consumption

- Operating temperature range T<sub>A</sub>: -40 ℃ to +125 ℃

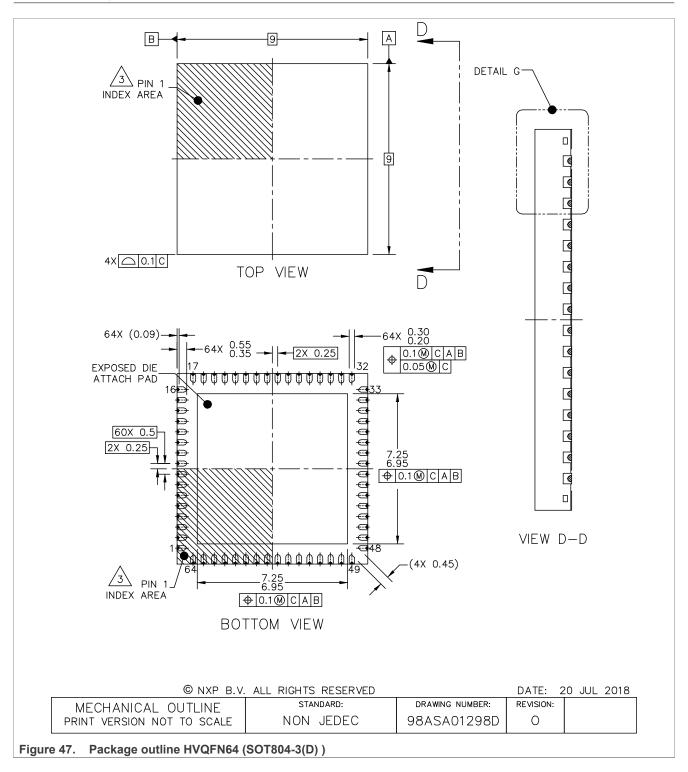

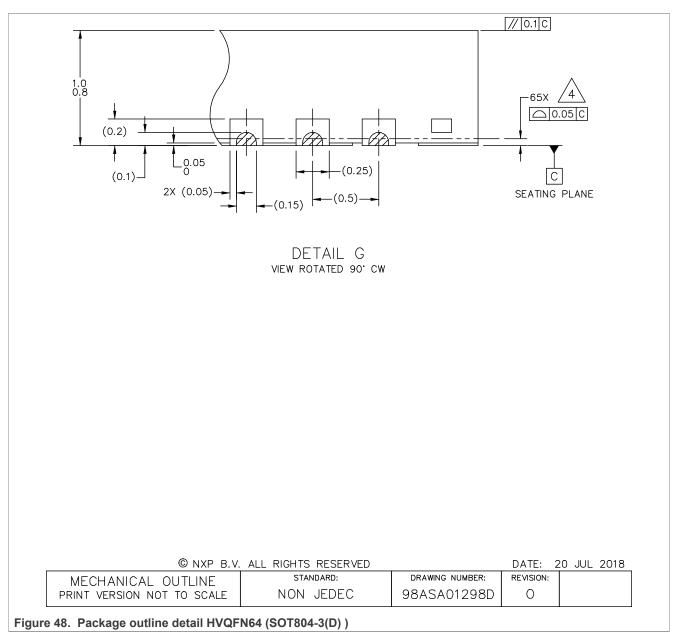

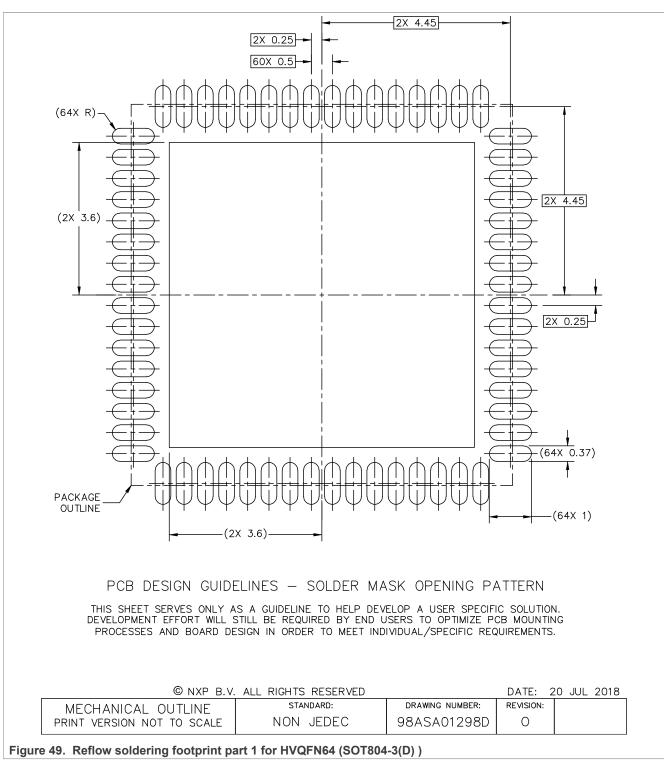

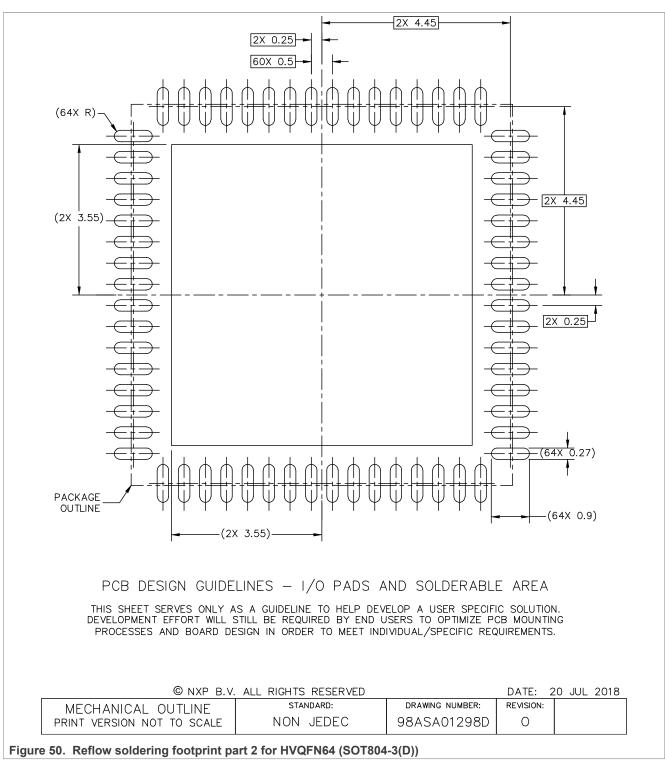

- Package: 64 pin, 9 mm x 9 mm x 0.85 mm HVQFN

Highly configurable 8/4-channel 24/16 bits ±25 V universal input analog front-end with excitation sources

# **3** Applications

- Data acquisition system

- PLC, DCS I/O modules

- Industrial automation and process control

# 4 Ordering information

#### Table 1. Ordering information

| Type number    | Topside mark   | Package | Package                                                                                                                |                                                                     |  |  |  |  |  |  |

|----------------|----------------|---------|------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|--|--|--|--|--|--|

|                |                | Name    | Description                                                                                                            | Version                                                             |  |  |  |  |  |  |

| NAFE13388B40BS | NAFE13388B40BS | HVQFN64 | Plastic, thermal-enhanced very thin quad flatpack; no leads;<br>64 terminals; 0.5 mm pitch; 9 mm x 9 mm x 0.85 mm body | SOT804-3(D) <u>https://</u><br>www.nxp.com/packages/<br>SOT804-3(D) |  |  |  |  |  |  |

| NAFE13188B40BS | NAFE13188B40BS | HVQFN64 | Plastic, thermal-enhanced very thin quad flatpack; no leads;<br>64 terminals; 0.5 mm pitch; 9 mm x 9 mm x 0.85 mm body | SOT804-3(D) <u>https://</u><br>www.nxp.com/packages/<br>SOT804-3(D) |  |  |  |  |  |  |

| NAFE13148B40BS | NAFE13148B40BS | HVQFN64 | Plastic, thermal-enhanced very thin quad flatpack; no leads;<br>64 terminals; 0.5 mm pitch; 9 mm x 9 mm x 0.85 mm body | SOT804-3(D) <u>https://</u><br>www.nxp.com/packages/<br>SOT804-3(D) |  |  |  |  |  |  |

| NAFE13144B40BS | NAFE13144B40BS | HVQFN64 | Plastic, thermal-enhanced very thin quad flatpack; no leads;<br>64 terminals; 0.5 mm pitch; 9 mm x 9 mm x 0.85 mm body | SOT804-3(D) <u>https://</u><br>www.nxp.com/packages/<br>SOT804-3(D) |  |  |  |  |  |  |

| NAFE13184B40BS | NAFE13184B40BS | HVQFN64 | Plastic, thermal-enhanced very thin quad flatpack; no leads;<br>64 terminals; 0.5 mm pitch; 9 mm x 9 mm x 0.85 mm body | SOT804-3(D) <u>https://</u><br>www.nxp.com/packages/<br>SOT804-3(D) |  |  |  |  |  |  |

# 4.1 Ordering options

#### Table 2. Ordering options

| Type number    | Orderable part<br>number | Package | Packing method                                | Minimum order<br>quantity | Temperature            |

|----------------|--------------------------|---------|-----------------------------------------------|---------------------------|------------------------|

|                | NAFE13388B40BSMP         |         | Reel 13" Q2/T1<br>*Standard mark SMD dry pack | 1000                      | TA = -40 °C to +125 °C |

| NAFE13388B40BS | NAFE13388B40BSE          | HVQFN64 | 1 + 1 Tray<br>*Standard mark SMD dry pack     | 260                       | TA = -40 °C to +125 °C |

|                | NAFE13388B40BSK          |         | 5+1 Tray<br>*Standard mark SMD dry pack       | 1300                      | TA = -40 °C to +125 °C |

|                | NAFE13188B40BSMP         |         | Reel 13" Q2/T1<br>*Standard mark SMD dry pack | 1000                      | TA = -40 °C to +125 °C |

| NAFE13188B40BS | NAFE13188B40BSE          | HVQFN64 | 1 + 1 Tray<br>*Standard mark SMD dry pack     | 260                       | TA = -40 °C to +125 °C |

|                | NAFE13188B40BSK          |         | 5+1 Tray<br>*Standard mark SMD dry pack       | 1300                      | TA = -40 °C to +125 °C |

|                | NAFE13148B40BSMP         |         | Reel 13" Q2/T1<br>*Standard mark SMD dry pack | 1000                      | TA = -40 °C to +125 °C |

| NAFE13148B40BS | NAFE13148B40BSE          | HVQFN64 | 1 + 1 Tray<br>*Standard mark SMD dry pack     | 260                       | TA = -40 °C to +125 °C |

|                | NAFE13148B40BSK          |         | 5+1 Tray<br>*Standard mark SMD dry pack       | 1300                      | TA = -40 °C to +125 °C |

|                | NAFE13144B40BSMP         |         | Reel 13" Q2/T1<br>*Standard mark SMD dry pack | 1000                      | TA = -40 °C to +125 °C |

| NAFE13144B40BS | NAFE13144B40BSE          | HVQFN64 | 1 + 1 Tray<br>*Standard mark SMD dry pack     | 260                       | TA = -40 °C to +125 °C |

|                | NAFE13144B40BSK          |         | 5+1 Tray<br>*Standard mark SMD dry pack       | 1300                      | TA = -40 °C to +125 °C |

|                | NAFE13184B40BSMP         |         | Reel 13" Q2/T1<br>*Standard mark SMD dry pack | 1000                      | TA = -40 °C to +125 °C |

| NAFE13184B40BS | NAFE13184B40BSE          | HVQFN64 | 1 + 1 Tray<br>*Standard mark SMD dry pack     | 260                       | TA = -40 °C to +125 °C |

|                | NAFE13184B40BSK          |         | 5+1 Tray<br>*Standard mark SMD dry pack       | 1300                      | TA = -40 °C to +125 °C |

NAFE13388 Product data sheet

## **NXP Semiconductors**

Highly configurable 8/4-channel 24/16 bits ±25 V universal input analog front-end with excitation sources

# 4.2 Product family

The NAFE family is optimized for power and speed, with highly integrated functional features and modes for offloading the host processor to achieve higher performance and low power consumption of overall system.

In addition, the NXP analog input AFE family of products is pin-to-pin, software-compatible, and well-suited in scalable applications of analog I/O modules and data acquisition systems.

<u>Table 3</u> shows the possible features to select for each family member. Contact the NXP factory or an NXP sales representative to get further information and availability of appropriate configurations.

#### Table 3. Part numbers

| Part number    |     | Low-power<br>high-speed | Resolution<br>16-bit/24-bit | #Input | Factory calibrated |

|----------------|-----|-------------------------|-----------------------------|--------|--------------------|

| NAFE13388B40BS | Yes | Low power               | 24                          | 8      | Yes                |

| NAFE73388B40BS | Yes | High speed              | 24                          | 8      | Yes                |

| NAFE13188B40BS | Yes | Low power               | 24                          | 8      | No                 |

| NAFE13184B40BS | Yes | Low power               | 24                          | 4      | No                 |

| NAFE13148B40BS | Yes | Low power               | 16                          | 8      | No                 |

| NAFE13144B40BS | Yes | Low power               | 16                          | 4      | No                 |

# 5 Block diagram

# NXP Semiconductors

# NAFE13388

Highly configurable 8/4-channel 24/16 bits ±25 V universal input analog front-end with excitation sources

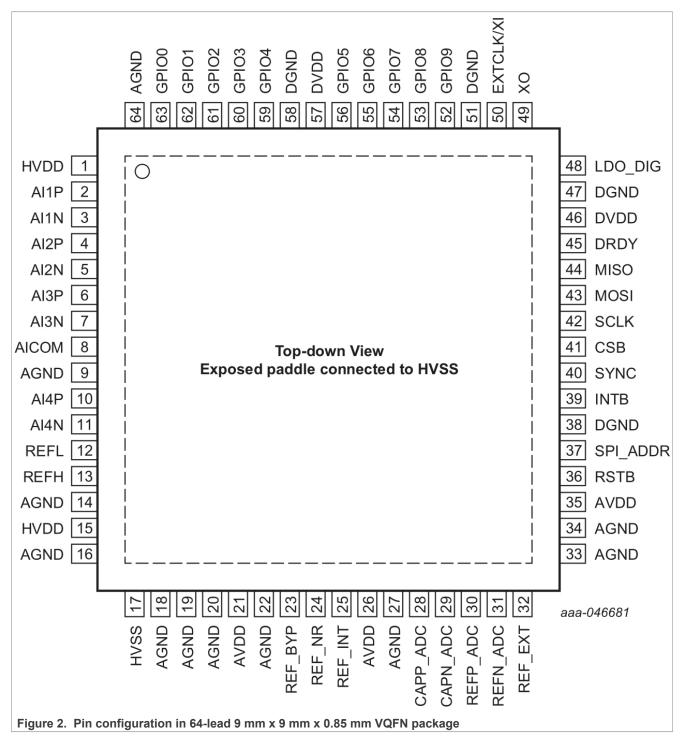

# 6 Pinning information

# 6.1 Pinning

Highly configurable 8/4-channel 24/16 bits ±25 V universal input analog front-end with excitation sources

# 6.2 Pin description

| Pin | Name     | I/O    | Functional description                                                                                                                     |

|-----|----------|--------|--------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | HVDD     | Supply | High-voltage positive supply, 0.1 $\mu$ F    4.7 $\mu$ F to AGND, optional: install 28 V Zener to AGND for protection                      |

| 2   | AI1P     | AI     | Analog Input in series with external 2.5 k $\Omega$ resistor with 1 nF or 10 nF cap to AGND                                                |

| 3   | AI1N     | AI     | Analog Input in series with external 2.5 k $\Omega$ resistor with 1 nF or 10 nF cap to AGND                                                |

| 4   | AI2P     | AI     | Analog Input in series with external 2.5 k $\Omega$ resistor with 1 nF or 10 nF cap to AGND                                                |

| 5   | AI2N     | AI     | Analog Input in series with external 2.5 k $\Omega$ resistor with 1 nF or 10 nF cap to AGND                                                |

| 6   | AI3P     | AI     | Analog Input in series with external 2.5 $k\Omega$ resistor with 1 nF or 10 nF cap to AGND; not used in 4 channel parts. Connect to AGND.  |

| 7   | AI3N     | AI     | Analog Input in series with external 2.5 k $\Omega$ resistor with 1 nF or 10 nF cap to AGND; not used in 4 channel parts. Connect to AGND. |

| 8   | AICOM    | AI     | Analog GND or common input in series with external 2.5 $k\Omega$ resistor with 1 nF or 10 nf cap to AGND                                   |

| 9   | AGND     | Ground | Analog ground                                                                                                                              |

| 10  | AI4P     | AI     | Analog Input in series with external 2.5 k $\Omega$ resistor with 1 nF or 10 nF cap to AGND                                                |

| 11  | AI4N     | AI     | Analog Input in series with external 2.5 k $\Omega$ resistor with 1 nF or 10 nF cap to AGND; not used in 4 channel parts. Connect to AGND. |

| 12  | REFL     | AO     | 0.2 V unbuffered internal voltage source, 10 nF cap to AGND; not used in 4 channel parts. Connect to AGND.                                 |

| 13  | REFH     | AO     | 2.3 V unbuffered internal voltage source, 10 nF cap to AGND                                                                                |

| 14  | AGND     | Ground | Analog ground                                                                                                                              |

| 15  | HVDD     | Supply | High-voltage positive supply, 0.1 μF    4.7 μF cap to AGND                                                                                 |

| 16  | AGND     | Ground | Analog ground                                                                                                                              |

| 17  | HVSS     | Supply | High-voltage negative supply, 0.1 $\mu$ F    4.7 $\mu$ F cap to AGND. (internally shorted to exposed pad) Zene to AGND for protection.     |

| 18  | AGND     | Ground | Analog ground                                                                                                                              |

| 19  | AGND     | Ground | Analog ground                                                                                                                              |

| 20  | AGND     | Ground | Analog ground                                                                                                                              |

| 21  | AVDD     | Supply | 3.3 V analog power supply, 0.1 μF    4.7 μF cap to AGND.                                                                                   |

| 22  | AGND     | Ground | Analog ground                                                                                                                              |

| 23  | REF_BYP  | AO     | Buffered voltage reference bypass, 100 pF (max loading) cap to AGND                                                                        |

| 24  | REF_NR   | AI     | Voltage reference noise reduction, 0.47 µF cap to AGND                                                                                     |

| 25  | REF_INT  | AO     | Internal voltage reference output bypass, 0.47 µF                                                                                          |

| 26  | AVDD     | Supply | 3.3 V analog power supply, 0.1 μF    4.7 μF cap to AGND                                                                                    |

| 27  | AGND     | Ground | Analog ground                                                                                                                              |

| 28  | CAPP_ADC | AO     | ADC buffer positive output, 1 nF C0G cap to CAPN                                                                                           |

| 29  | CAPN_ADC | AO     | ADC buffer negative output, 1 nF C0G cap to CAPP                                                                                           |

| 30  | REFP_ADC | AO     | ADC positive reference bypass, 0.1 µF    1 µF X7R cap to REFN_ADC                                                                          |

| 31  | REFN_ADC | AI     | ADC ground reference, 0.1 µF    1 µF X7R cap to REFP_ADC                                                                                   |

| 32  | REF_EXT  | AI     | External 2.5 V reference voltage Input. 0.1 µF cap to AGND                                                                                 |

| 33  | AGND     | Ground | Analog ground                                                                                                                              |

| 34  | AGND     | Ground | Analog ground                                                                                                                              |

| 35  | AVDD     | Supply | Connect 0.1 µF    4.7 µF cap to AGND (pin-34) close to the AVDD pin                                                                        |

| 36  | RSTB     | DI     | Chip reset, active-low (CMOS push-pull or open drain with internal 100 k $\Omega$ pullup).                                                 |

| 37  | SPI_ADDR | DI     | SPI address 0 (with internal 100 kΩ pulldown).                                                                                             |

| 38  | DGND     | Ground | Digital ground                                                                                                                             |

| 39  | INTB     | DO     | Active low interrupt output (CMOS push-pull or open drain internally pulled up)                                                            |

| 40  | SYNC     | DI     | ADC sync pulse input                                                                                                                       |

Highly configurable 8/4-channel 24/16 bits ±25 V universal input analog front-end with excitation sources

| Pin | Name      | I/O        | Functional description                                                                         |

|-----|-----------|------------|------------------------------------------------------------------------------------------------|

| 41  | CSB       | DI         | Chip select input, active-low (with internal 100 kΩ pullup)                                    |

| 42  | SCLK      | DI         | SPI clock input                                                                                |

| 43  | MOSI      | DI         | SPI data input                                                                                 |

| 44  | MISO      | DO         | SPI data output                                                                                |

| 45  | DRDY      | DO         | ADC data ready output, active-high                                                             |

| 46  | DVDD      | Supply     | 3.3 V digital power supply, 0.1 μF    4.7 μF cap to DGND.                                      |

| 47  | DGND      | Ground     | Digital ground                                                                                 |

| 48  | LDO_DIG   | AO         | Internal 1.8 V LDO bypass, 0.1 μF    4.7 μF uF cap to DGND.                                    |

| 49  | хо        | DI         | 18.432 MHz crystal XOUT with loading cap (< 20 pF). No-connect or float if crystal is not used |

| 50  | EXTCLK/XI | DI         | External clock input or 18.432 MHz crystal XIN with loading cap(< 20 pF)                       |

| 51  | DGND      | Ground     | Digital ground                                                                                 |

| 52  | GPIO9     | DI, DO     | General-purpose digital input/output or system clock output                                    |

| 53  | GPIO8     | DI, DO     | General-purpose digital input/output                                                           |

| 54  | GPIO7     | DI, DO     | General-purpose digital input/output                                                           |

| 55  | GPIO6     | DI, DO     | General-purpose digital input/output                                                           |

| 56  | GPIO5     | DI, DO     | General-purpose digital input/output                                                           |

| 57  | DVDD      | Supply     | 3.3 V digital power supply, 0.1 μF    4.7 μF cap to DGND.                                      |

| 58  | DGND      | Ground     | Digital ground                                                                                 |

| 59  | GPIO4     | DI, DO     | General-purpose digital input/output                                                           |

| 60  | GPIO3     | DI, DO     | General-purpose digital input/output                                                           |

| 61  | GPIO2     | DI, DO     | General-purpose digital input/output                                                           |

| 62  | GPIO1     | DI, DO, AI | General-purpose digital I/O or ADC differential analog input: GPIO0-GPIO1                      |

| 63  | GPIO0     | DI, DO, AI | General-purpose digital I/O or ADC differential analog input: GPIO0-GPIO1                      |

| 64  | AGND      | Ground     | Analog ground                                                                                  |

|     | EP        |            | Exposed pad is connected to HVSS internally. Exposed pad should be tied to HVSS on PCB.        |

# 7 Functional description

# 7.1 Overview

The NAFE13388 is a highly configurable, universal eight/four-input AFE with various integrated diagnostic features. At the HV analog inputs, the low-leakage pins can be configured anywhere from eight single-ended to four differential signals, with external common input AICOM or internal AGND reference. Eight selectable PGA gain settings of 0.2 V/V to 16 V/V provide a wide range of differential input range from ±25 V to ±312.5 mV for variety of applications. In general, all of the HV input characteristics are specified to the linear (nominal) input ranges for all of the channel gain settings, which is 80 % of the full input range. In addition to the differential signals at the PGA output, one auxiliary differential input GPIO0-GPIO1, four low-voltage diagnostic signals are also multiplexed to the ADC: power supplies AVDD, HVDD, HVSS, and an independent coarse voltage reference (REF\_coarse).

The voltage reference (VREF) derived voltage sources REFH and REFL are available through pins for external measurement. These two voltage sources are also connected as inputs to high-voltage multiplexer (HVMUX). They could be used for on-chip self-calibration or self-diagnostic purposes, regardless of the voltage reference sources, which can be either external, internal, or mixed. When supplied with the factory-calibrated coefficients, REFH and REFL facilitate routine calibrations without the need for additional accurate components.

The device includes a configurable voltage or current excitation source. The configurable source provides required voltage or current to sensors, such as RTD.

An independent on-chip temperature sensor is included for continuous die temperature monitoring with a 16-bit readout. This temperature reading is also used to trigger an overtemperature warning at 145 °C, auto-shutdown at 165 °C, or the user-programmable temperature alarm.

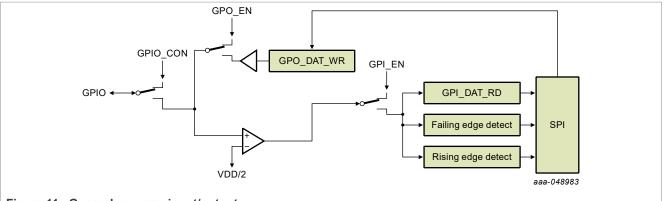

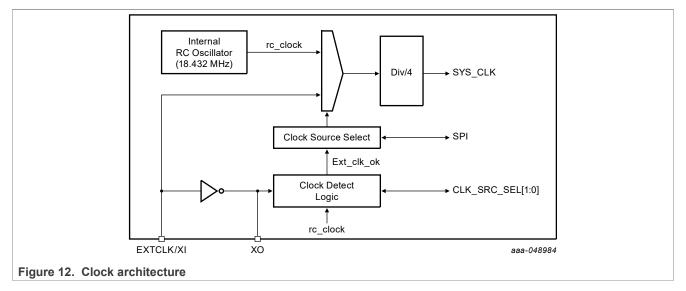

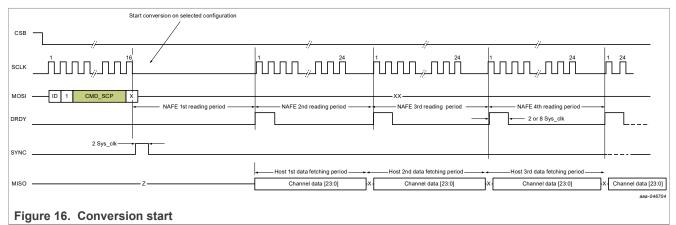

The NAFE13388 comes with ten GPIOs that satisfy most of the needs for monitoring and control in typical applications. The selectable clock sources could be either the internal oscillator or a crystal oscillator, or external clock. In addition, data and conversion synchronization is available via SYNC and DRDY pins, and the last falling edge of the SPI clock.

Following the 24/16-bit  $\Delta\Sigma$  modulator, a multistage digital filter was designed to offer a wide range of data rates with a selectable cascade of SINC filters and the option of Single-Cycle Settling mode or Normal Settling mode. In multichannel, fast-switching applications, the user may trade off speed/accuracy and fine-tune the effective data rate. Simultaneous 50 Hz and 60 Hz line rejection is available at lower data rates.

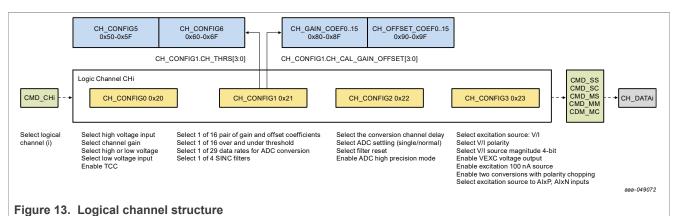

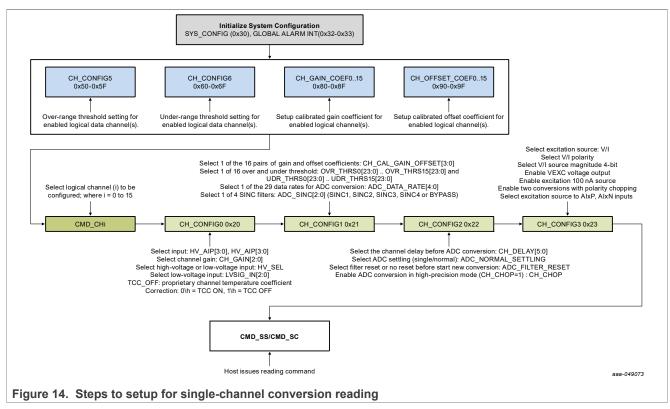

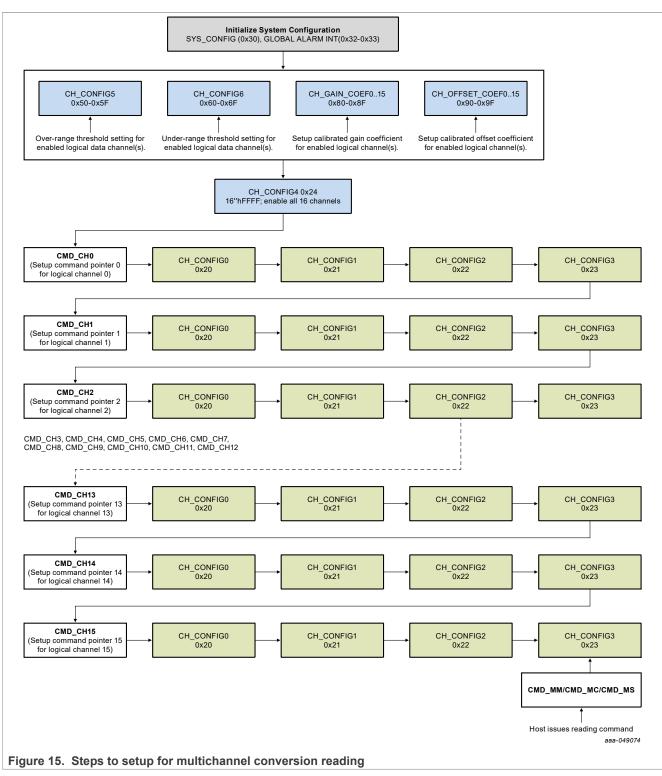

The device includes 16 logical channels that allow saving a set of predefined configurations, including HVMUX inputs, PGA gain, data rate, gain/offset coefficient pairs, voltage/current excitation.

Once these settings have been configured at power up, the host enables the multichannel sequencer to select which logical channels (all or some of them) has to perform the measurement. A data-ready signal is triggered either when each measurement is completed or when all the measurements are completed. This feature saves SPI transactions and allows high data rate input channel scanning at system level.

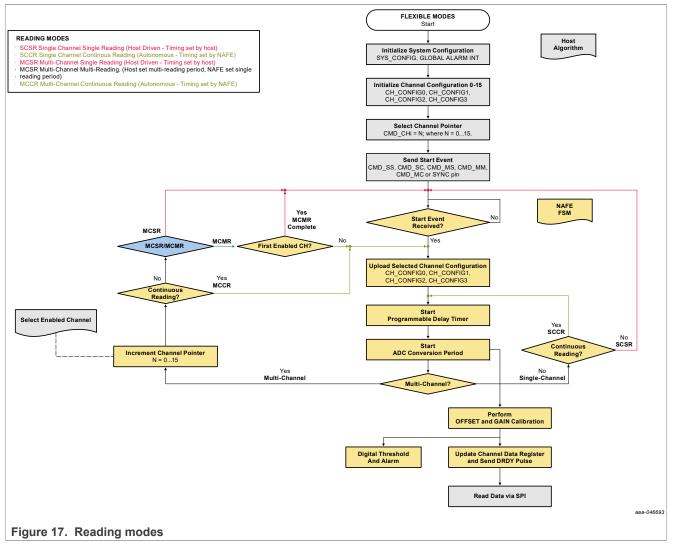

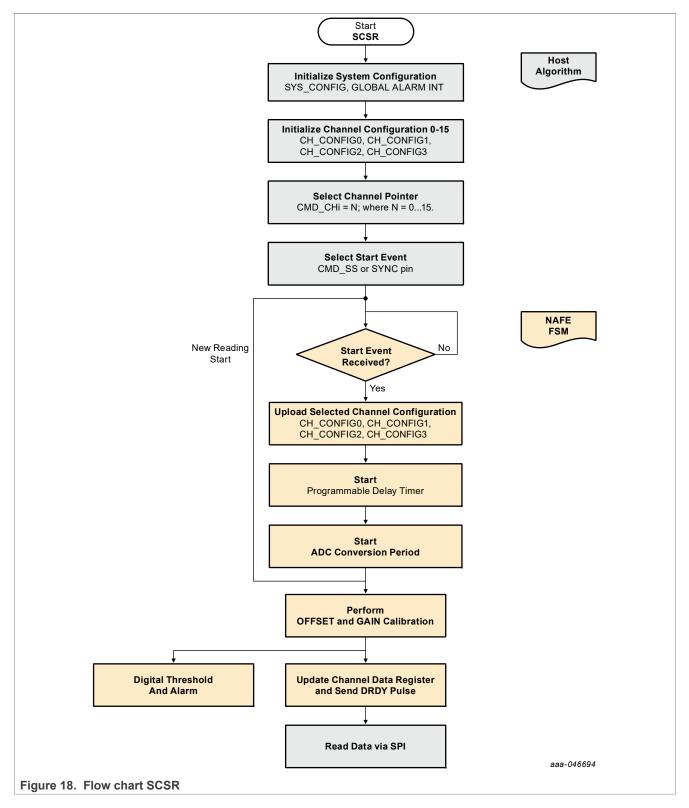

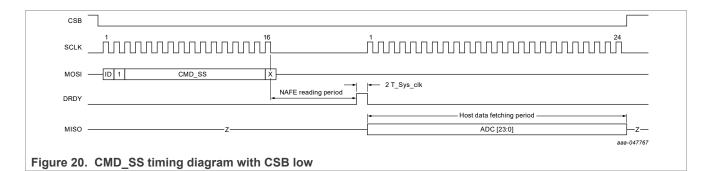

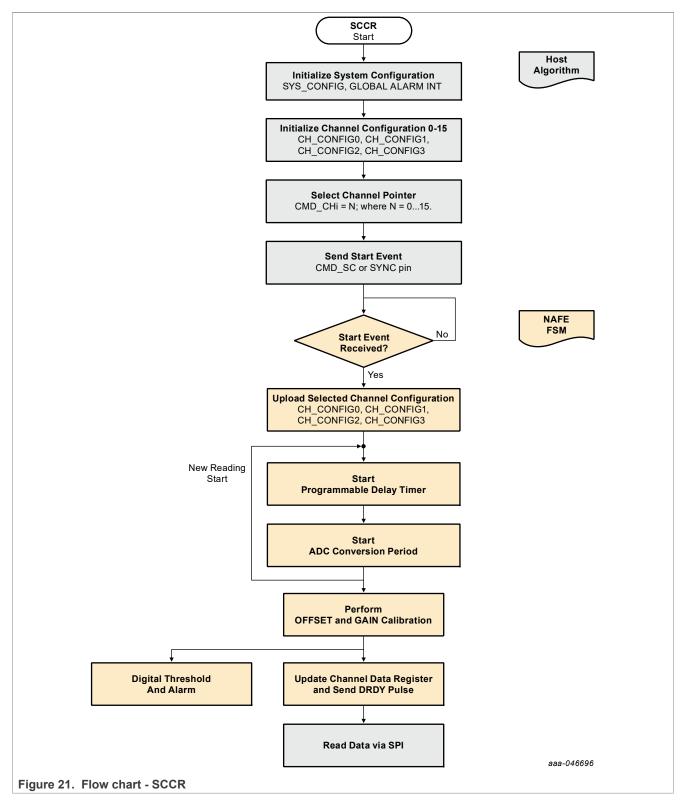

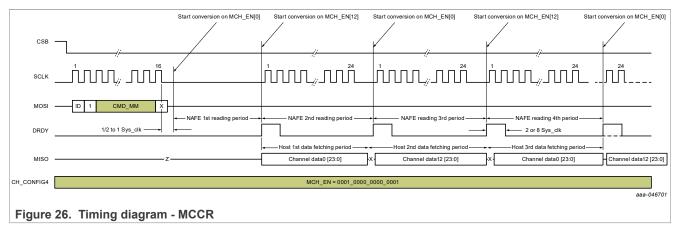

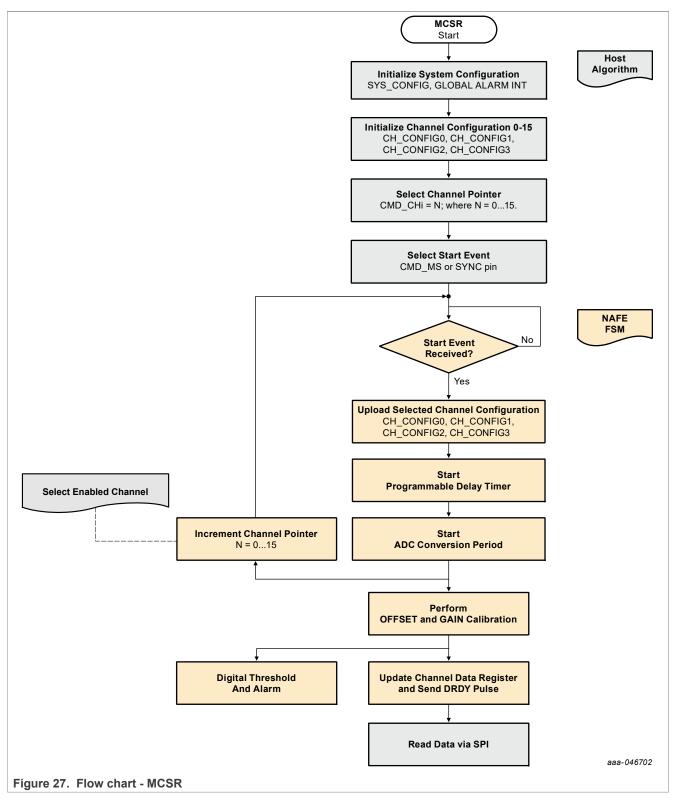

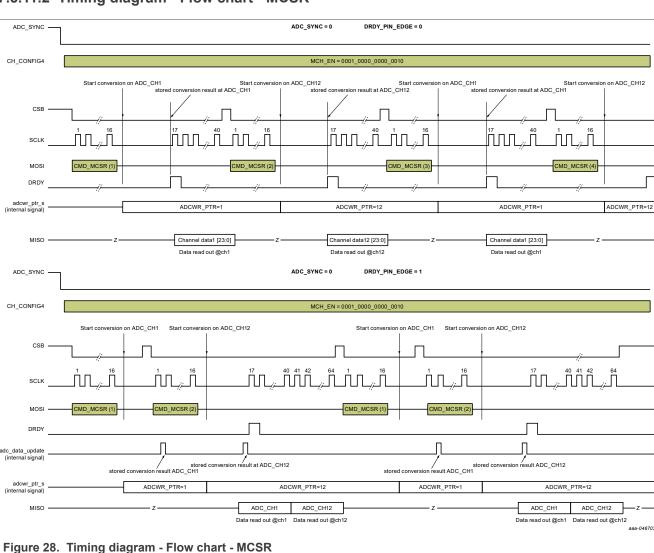

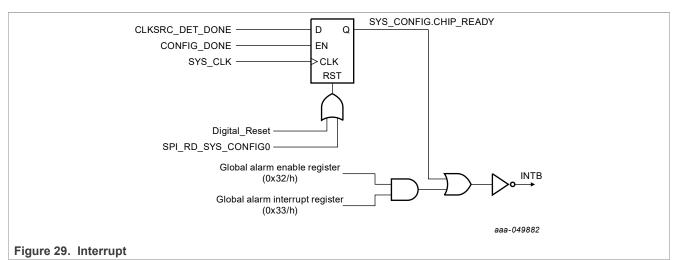

Five efficient reading modes are available for ADC data conversion: single-channel single-reading (SCSR), single-channel continuous-reading (SCCR), multichannel single-reading (MCSR), multichannel multireading (MCMR), and multi-channel continuous-reading (MCCR). The user may issue command CMD\_BURST\_DATA to read back multiple channels data in a single SPI transaction. See <u>Table 19</u> for conversion start commands.

# 7.2 Precise and fast data acquisition

The NAFE13388 is suitable for data acquisition of high-precision and high-speed analog inputs.

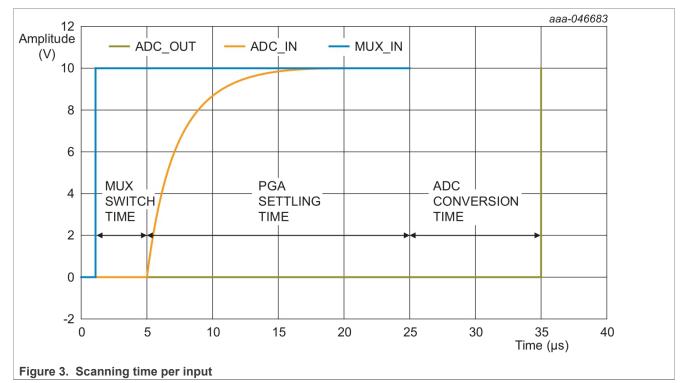

The NAFE13388 integrates an input multiplexer (MUX), high gain bandwidth (GBW) programmable gain amplifier (PGA), and a high-resolution 24/16-bit sigma-delta ADC. The optimized architecture of the MUX, PGA,

and ADC provides fast input-scanning with flexible output data rates, which are comparable with SAR ADC architecture used in fast response-time systems.

Programmable ADC output data rate range:

- 288 ksps to 7.5 sps in Normal Settling mode

- 72 ksps to 1.5 sps in Single-Cycle Settling mode

<u>Figure 3</u> shows the scanning time required when HV MUX switches from one input to another (effectively presenting a step function), and PGA follows to settle with limited bandwidth and the required ADC conversion time at a specified data rate.

## 7.3 Detailed description

This section describes the building blocks integrated in the NAFE13388.

#### 7.3.1 Architecture block diagram

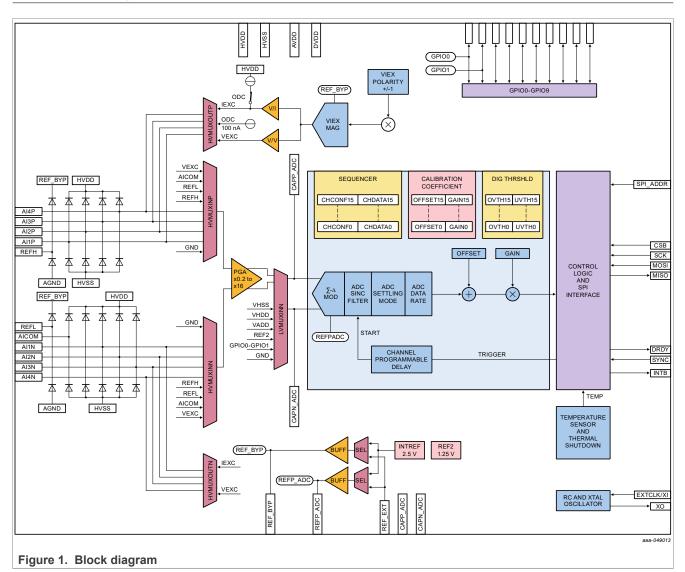

The NAFE13388 can be grouped into eight sections: high-voltage multiplexer, PGA, low-voltage multiplexer, ADC, digital calibration, voltage reference, VIEX (voltage/current excitation), and clock sources as shown in Figure 1.

## 7.3.2 High-voltage multiplexer — HVMUX

The high-voltage analog input section multiplexes externally accessible input and internal inputs.

The external inputs are: AI1P, AI2P, AI3P, AI4P, AI1N, AI2N, AI3N, AI4N, AICOM

- AI1P, AI2P, AI3P, AI4P are connected to the positive high-voltage multiplexer HVMUXINP input.

- AI1N, AI2N, AI3N, AI4N are connected to the negative high-voltage multiplexers HVMUXINN input.

AICOM, REFH, REFL, and AGND (internal ground) are connected to both positive and negative high-voltage input multiplexers HVMUXINP and HVMUXINN, respectively.

### 7.3.2.1 Analog input protection diodes and clamping

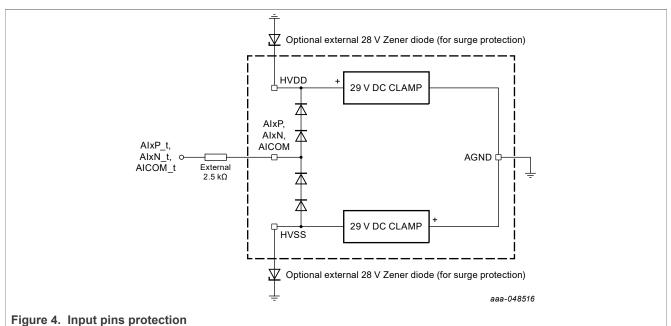

As shown in <u>Figure 4</u>, the external analog input pins of the NAFE are followed by clamping circuits for electrostatic discharge (ESD) and surge protection.

Each HV input pin is equipped with input protection diodes connected to HVDD, HVSS.

It is recommended that an external series 2.5 kOhm resistor with 1 nF or 10 nF capacitor to AGND is installed for each HV input pin for reliability. See <u>Section 11.1</u>.

The integrated clamping circuits, shown in <u>Figure 4</u>, protect the NAFE inputs from possible surge voltage and from ESD events that may occur during the manufacturing process and during printed-circuit board (PCB) assembly.

If an analog input is driven below HVSS, or above HVDD, the internal protection diodes may conduct current. A 2.5 k $\Omega$  or greater external series resistor is required to limit the input current to the specified value.

#### 7.3.2.2 HV input multiplexer - HVMUXIN

The NAFE uses two independent HV input multiplexers to measure the differential, pseudo-differential, and single-ended signal. When the input is used in differential or pseudo-differential mode, the NAFE provides high common-mode rejection.

The differential configuration is obtained by connecting the positive wire of the signal to any of the AIxP inputs and the negative wire of the signal to any of the AIxN inputs and via software configuration selecting the respective inputs of HVMUX.

The pseudo-differential configuration is obtained by connecting the positive wire of signal to any of the AlxP or AlxN inputs and the negative wire of the signal to AICOM input and via software configuration selecting the respective inputs of HVMUX.

The single-ended configuration is achieved by connecting the positive signal to any of the AlxP or AlxN inputs and the negative wire of the signal to AICOM, where AICOM = AGND.

The selected input to positive and negative HVMUX should be configured appropriately to match the physical connections. When CH\_CHOP = 1 is set, two ADC conversions will be performed. Therefore the final ADC output is the average of the difference of these two ADC intermediate outputs. As such, the channel offset is canceled and the effective output data rate is half of the programmed value.

**Note:** The ADC output polarity sign is inverted internally and automatically whenever AlxP input is connected to AICOM or GND while AlxN input is AI1N..AI4N, REFH, REFL.

### 7.3.2.2.1 Analog common input (AICOM)

To ensure precise single-ended measurements, AICOM pin should be connected in series with a 2.5 k $\Omega$  resistor and connected to an external GND reference physically close to the measured positive signal on the printed-circuit board (PCB).

#### 7.3.2.2.2 REFH and REFL

REFH and REFL provide stable and accurate voltage sources derived from VREF\_BYP. REFH and REFL are 92 % and 8 %, of VREF\_BYP, with a nominal value of 2.3 V and 0.2 V, respectively.

REFH and REFL are connected to inputs of both HVMUXINP and HVMUXINN multiplexer.

REFH and REFL could be used for system-level self-calibration on the field, failure prediction, and predictive maintenance. Factory OPT\_COEF1 and OPT\_COEF2 are available for REFH and REFL on optional part numbers.

#### 7.3.2.2.3 Low-leakage circuit

The NAFE13388 provides a high-input impedance of 1 G $\Omega$  and low-input leakage current less than 5 nA at 105 °C. In combination with its low-noise and low-offset drift PGA, the device is well-suited for precision temperature measurement with RTDs and thermocouples.

The NAFE13388 provides a precise programmable current excitation source to enable the measurement of resistance and and external sensors.

#### 7.3.2.3 HV output multiplexer - HVMUXOUT

The AFE uses two independent HV output multiplexers to connect the voltage or current excitation VIEX source to the desired input pin. This enables the device to measure resistance, RTD, to detect open and short circuit at the input, and implement readback monitoring for diagnostic testing.

#### 7.3.3 Programmable gain amplifier

The programmable gain amplifier (PGA) is a low-noise, programmable gain, differential input, differential output amplifier. The PGA operates in Gain or Attenuation mode, depending on the gain selected. Typically, the PGA is programmed to match the input range of the ADC to the full-scale input signal. Available PGA gains are 0.2, 0.4, 0.8, 1, 2, 4, 8,16 V/V.

NAFE13388

### 7.3.3.1 PGA input operating ranges

<u>Table 5</u> shows the HV input nominal ranges, the max and min values, full-scale range, and resolution for the different types of input signals and PGA gain setting.

When overloaded, the PGA output goes to a value close to 0 V. Check the PGA\_OV\_ALRM bit to detect if the PGA is out of range.

#### Table 5. HV input ranges and resolutions

|                  |                  |           | Nom      | inal range valu | es (V)   |          |          |          |  |  |

|------------------|------------------|-----------|----------|-----------------|----------|----------|----------|----------|--|--|

| Туре             | PGA gain setting |           |          |                 |          |          |          |          |  |  |

|                  | 0.2              | 0.4       | 0.8      | 1               | 2        | 4        | 8        | 16       |  |  |

| Bipolar DIFF     | ±20.00000        | ±10.00000 | ±5.00000 | ±4.00000        | ±2.00000 | ±1.00000 | ±0.50000 | ±0.25000 |  |  |

| BipolarSE        | ±10.00000        | ±5.00000  | ±2.50000 | ±2.00000        | ±1.00000 | ±0.50000 | ±0.25000 | ±0.12500 |  |  |

| Unipolar<br>DIFF | ±10.00000        | ±5.00000  | ±2.50000 | ±2.00000        | ±1.00000 | ±0.50000 | ±0.25000 | ±0.12500 |  |  |

| Unipolar SE      | ±10.00000        | ±5.00000  | ±2.50000 | ±2.00000        | ±1.00000 | ±0.50000 | ±0.25000 | ±0.12500 |  |  |

|                  |                  |           | Min      | and max value   | es (V)   |          | ·        |          |  |  |

| Туре             | PGA gain setti   | ng        |          |                 |          |          |          |          |  |  |

|                  | 0.2              | 0.4       | 0.8      | 1               | 2        | 4        | 8        | 16       |  |  |

| Bipolar DIFF     | ±25.00000        | ±12.50000 | ±6.25000 | ±5.00000        | ±2.50000 | ±1.25000 | ±0.62500 | ±0.31250 |  |  |

| BipolarSE        | ±12.50000        | ±6.25000  | ±3.12500 | ±2.50000        | ±1.25000 | ±0.62500 | ±0.31250 | ±0.15625 |  |  |

| Unipolar<br>DIFF | ±12.50000        | ±6.25000  | ±3.12500 | ±2.50000        | ±1.25000 | ±0.62500 | ±0.31250 | ±0.15625 |  |  |

| Unipolar SE      | ±12.50000        | ±6.25000  | ±3.12500 | ±2.50000        | ±1.25000 | ±0.62500 | ±0.31250 | ±0.15625 |  |  |

|                  |                  |           | Fi       | ull range scale | (V)      |          |          |          |  |  |

| Туре             | PGA gain setti   | ng        |          |                 |          |          |          |          |  |  |

|                  | 0.2              | 0.4       | 0.8      | 1               | 2        | 4        | 8        | 16       |  |  |

| Bipolar DIFF     | 50               | 25        | 12.5     | 10              | 5        | 2.5      | 1.25     | 0.625    |  |  |

| BipolarSE        | 25               | 12.5      | 6.25     | 5               | 2.5      | 1.25     | 0.625    | 0.3125   |  |  |

| Unipolar<br>DIFF | 25               | 12.5      | 6.25     | 5               | 2.5      | 1.25     | 0.625    | 0.3125   |  |  |

| Unipolar SE      | 12.5             | 6.25      | 3.125    | 2.5             | 1.25     | 0.625    | 0.3125   | 0.15625  |  |  |

|                  |                  | •         |          | Resolution (V   | )        |          | ·        |          |  |  |

| Туре             | PGA gain setti   | ng        |          |                 |          |          |          |          |  |  |

|                  | 0.2              | 0.4       | 0.8      | 1               | 2        | 4        | 8        | 16       |  |  |

| Bipolar DIFF     | 3.0E-6           | 1.5E-6    | 745.1E-9 | 596.0E-9        | 298.0E-9 | 149.0E-9 | 74.5E-9  | 37.3E-9  |  |  |

| BipolarSE        | 3.0E-6           | 1.5E-6    | 745.1E-9 | 596.0E-9        | 298.0E-9 | 149.0E-9 | 74.5E-9  | 37.3E-9  |  |  |

| Unipolar<br>DIFF | 3.0E-6           | 1.5E-6    | 745.1E-9 | 596.0E-9        | 298.0E-9 | 149.0E-9 | 74.5E-9  | 37.3E-9  |  |  |

| Unipolar SE      | 3.0E-6           | 1.5E-6    | 745.1E-9 | 596.0E-9        | 298.0E-9 | 149.0E-9 | 74.5E-9  | 37.3E-9  |  |  |

Highly configurable 8/4-channel 24/16 bits ±25 V universal input analog front-end with excitation sources

### 7.3.3.2 PGA input common mode ranges

PGA input common mode voltage range depends on PGA gain.

For cases with fully differential input voltages, the maximum allowable input common mode voltage can be calculated as:

If

$$V_{in+} = VCM + \frac{V_{DIFF}}{2}$$

and  $V_{in-} = VCM - \frac{V_{DIFF}}{2}$

Ther

$$VCM_{max} = A \cdot \left( V_{REF} - CH_{GAIN} \cdot \frac{V_{DIFF}}{2} \right)$$

Where, A = 1 for  $CH_{GAIN} = 1$ , 2, 4, 8, 16.

$$A = 5$$

for  $CH_{GAIN} = 0.2$ , 0.4, 0.8.

And  $V_{REF} = 2.5 V$  with internal reference voltage.

### 7.3.4 Low-voltage multiplexer - LVMUX

The internal node voltages (scaled HVDD and HVSS, AVDD, VREF\_Coarse, GPIO0-GPIO1) and PGA outputs are routed to the ADC input via a low-voltage multiplexer controlled by register bit HVSEL.

**Note:** The associated HV\_AIP and HV\_AIN setting for each LVSIG\_IN signal selection in <u>Table 6</u>. For example, LVSIG\_IN = 3 (VADD), the setting for CH\_CONFIG0 is 0xCC07 when CH\_GAIN = 0 and TCC\_OFF = 1.

| HV_AIP | HV_AIN | CH_GAIN | HVSEL | LVSIG_IN         | TCC_OFF |

|--------|--------|---------|-------|------------------|---------|

| 9      | 9      | Х       | 0     | 0:REF/2 vs REF/2 | Х       |

| A      | A      | Х       | 0     | 1:GPIO0 vs GPIO1 | Х       |

| В      | В      | Х       | 0     | 2:REF_Coarse     | X       |

| С      | С      | Х       | 0     | 3:AVDD           | Х       |

| D      | D      | Х       | 0     | 4:HVDD           | X       |

| E      | E      | Х       | 0     | 5:REF2           | X       |

Table 6. CONFIG0 Setting for using LVMUX signals

## 7.3.5 Analog-to-digital converter

## 7.3.5.1 ADC buffer

The ADC buffer is used to drive the sampling circuit of the ADC, where its differential output pins, CAPP and CAPN, are to be loaded with external COG type capacitor.

## 7.3.5.2 Sigma-delta ADC

The ADC is based on sigma-delta architecture that provides low-noise and high-speed acquisition in Single-Channel and Multichannel mode. The sigma-delta architecture includes a sigma-delta modulator followed by a configurable digital filter.

The ADC modulator is a third-order  $\Sigma\Delta$  modulator. The modulator samples the analog input voltage at a high-sample rate (fMOD = fsys\_clk / 2) and converts the analog input to a bit stream that is processed by the following digital filter.

## **NXP Semiconductors**

# NAFE13388

Highly configurable 8/4-channel 24/16 bits ±25 V universal input analog front-end with excitation sources

The digital filter processes the modulator output data to produce the high-resolution conversion result. The digital filter filters and decimates the data. Software selection of a certain digital filter depends on the trade-off between resolution, data rate, and line-cycle rejection acceptable in a system.

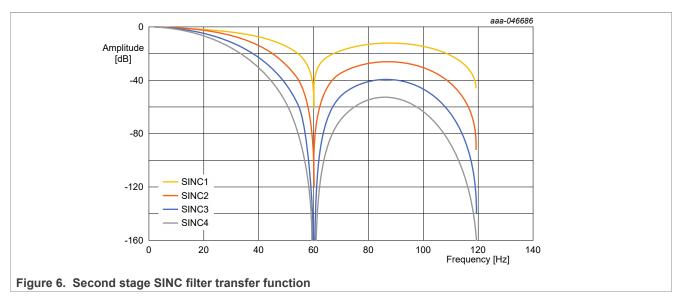

The ADC digital filter consists of two SINC filter stages. The first stage is a variable decimation SINC4 filter followed by the second stage variable-decimation, variable-order SINC filters. The optimized high-speed SINC4 filter averages and down-samples the modulator data to produce high-speed data rates from 288 ksps to 6 ksps.

The low-speed digital filter performs additional filtering and decimation to produce data rates of 4.5 ksps to 7.5 sps. The low-speed stage is a programmable-order SINC filter as SINC1, SINC2, SINC3, SINC4.

The data rate is programmed by the CH\_CONFIG1.ADC\_DATA\_RATE bits.

The digital filters are controlled by CH\_CONFIG1.ADC\_SINC bits.

**Note:** SINCx filter has settling time of x clock cycles, where x is the order. To manage the SINC filter settling, the NAFE13388 offers two different Conversion modes.

The Single-Cycle Settling mode is suggested for a multichannel system to avoid the settling error. The Normal Settling mode is suggested for single channel to get a faster data rate or lower noise.

#### 7.3.5.3 Frequency response

The low-pass filtering effect of the SINC filters sets the overall frequency response of the ADC.

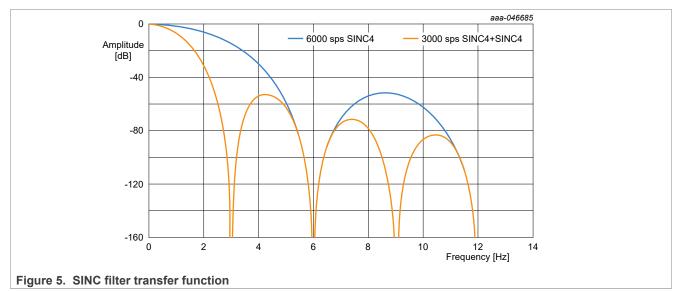

In Normal Settling mode, the frequency response of data rates, 6000 sps to 288000 sps, is determined by the transfer function of the first stage SINC4 filter. The frequency response of data rates, 7.5 sps to 4500 sps, is the product of the transfer function of the first digital filter stage (SINC4) and the selected digital filter of the second stage (SINC1, SINC2, SINC3, SINC4).

<u>Figure 5</u> shows an example of filter response for data rate 6000 sps with first stage SINC4 filter; and for data rate 3000 sps with second stage SINC4 filter.

Highly configurable 8/4-channel 24/16 bits ±25 V universal input analog front-end with excitation sources

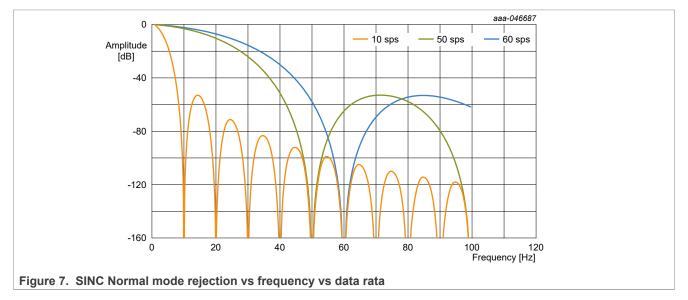

### 7.3.5.4 50 Hz/60 Hz Normal mode noise rejection

The NAFE13388 features a digital filter that provides a 50 Hz and 60 Hz Normal mode rejection (NMR).

Figure 7 shows the SINC4 filter NMR at the data rate of 10 sps, 50 sps, and 60 sps.

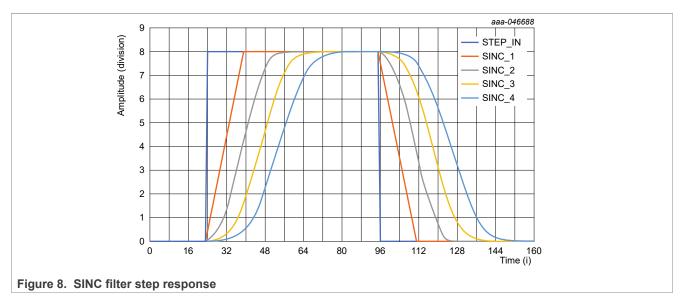

#### 7.3.5.5 Step response

The NAFE13388 could be configured for the following settling mode:

- Normal settling: Fits better for single-channel reading, providing lower noise measurements.

- Single-cycle settling: Fits better for multichannel reading, providing settled output.

<u>Figure 8</u> shows the relative settling time of the digital filter for the normal settling for different orders of SINC filter.

Highly configurable 8/4-channel 24/16 bits ±25 V universal input analog front-end with excitation sources

### 7.3.5.5.1 Normal settling vs. single-cycle settling

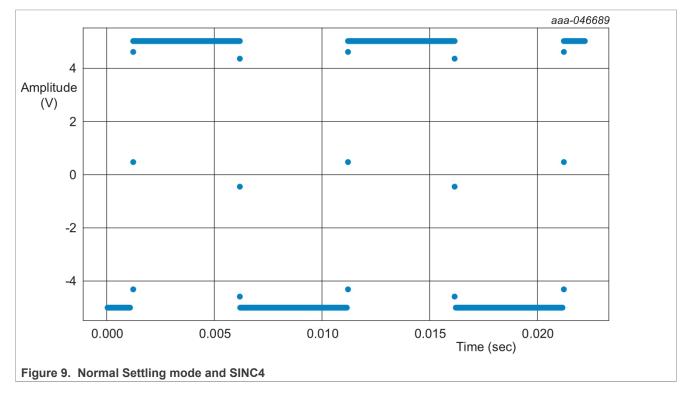

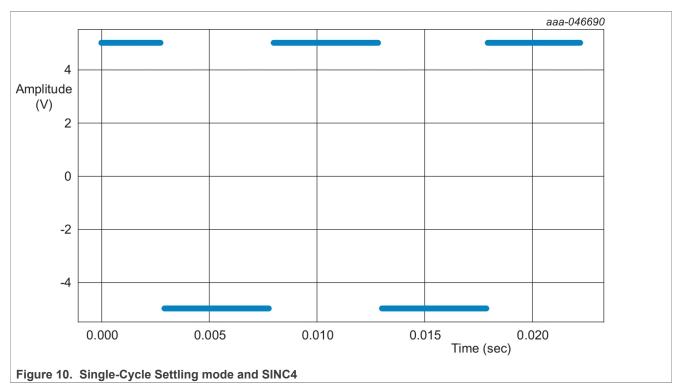

<u>Figure 9</u> shows a 100 Hz digitized square wave sampled at 36 ksps. The digital filter is SINC4 and the settling mode is set to normal. During the square wave transition from low to high, the output takes four samples to settle.

Instead, <u>Figure 10</u> shows a 100 Hz digitized square wave with Settling mode set to single-cycle. The waveform is sampled at 9 ksps and the digital filter is SINC4. In Single-Cycle Settling mode, during the square wave transition from low to high, the output takes one sample to settle.

NAFE13388 Product data sheet

Highly configurable 8/4-channel 24/16 bits ±25 V universal input analog front-end with excitation sources

## 7.3.5.6 ADC data rate

Table 7 shows the programmable data rates for different SINC digital filters and Settling modes.

A total of 29 programmable data rates is available. The rates are set by channel-based CH CONFIG1 register bits ADC\_DATA\_RATE[4:0]. The highest data rate codes (DRO = 0..11) are with second-stage SINC filter bypassed, ADC SINC[2:0]=0. Moreover, data rates with Single-Cycle Settling modes are four times slower with respect to Normal Settling mode, CH\_CONFIG2 register bit ADC\_NORMAL\_SETTLING = 1. The final effective data rate, in Single-Cycle Settling mode, could be further reduced by CH DELAY[5:0]. The details are described in Section 7.5.3.3.

Although all conversions are from the 24-bit ADC, the data may be read out in 24-bit or 16-bit format by setting ADC DATA OUT 16BIT bit in SYS CONFIG0 register.

|          |     |        | r               | Normal settling | g               |                 |       |

|----------|-----|--------|-----------------|-----------------|-----------------|-----------------|-------|

| DRO code | OSR | SINC4  | SINC4+<br>SINC1 | SINC4+<br>SINC2 | SINC4+<br>SINC2 | SINC4+<br>SINC4 | SINC4 |

| 0        | 8   | 288000 |                 |                 |                 |                 | 72000 |

| 1        | 12  | 192000 |                 |                 |                 |                 | 48000 |

| Table 7. | C | Data rate | (system | clock: | 4.608 | MHz) |

|----------|---|-----------|---------|--------|-------|------|

|          |   |           |         |        |       |      |

|          |     | Ŭ      |                 |                 |                 |                 |       | , , , , , , , , , , , , , , , , , , , |                 |                 |                 |  |

|----------|-----|--------|-----------------|-----------------|-----------------|-----------------|-------|---------------------------------------|-----------------|-----------------|-----------------|--|

| DRO code | OSR | SINC4  | SINC4+<br>SINC1 | SINC4+<br>SINC2 | SINC4+<br>SINC2 | SINC4+<br>SINC4 | SINC4 | SINC4+<br>SINC1                       | SINC4+<br>SINC2 | SINC4+<br>SINC2 | SINC4+<br>SINC4 |  |

| 0        | 8   | 288000 |                 |                 |                 |                 | 72000 |                                       |                 |                 |                 |  |

| 1        | 12  | 192000 |                 |                 |                 |                 | 48000 |                                       |                 |                 |                 |  |

| 2        | 16  | 144000 |                 |                 |                 |                 | 36000 |                                       |                 |                 |                 |  |

| 3        | 24  | 96000  |                 |                 |                 |                 | 24000 |                                       |                 |                 |                 |  |

| 4        | 32  | 72000  |                 |                 |                 |                 | 18000 |                                       |                 |                 |                 |  |

| 5        | 48  | 48000  |                 |                 |                 |                 | 12000 |                                       |                 |                 |                 |  |

| 6        | 64  | 36000  |                 |                 |                 |                 | 9000  |                                       |                 |                 |                 |  |

| 7        | 96  | 24000  |                 |                 |                 |                 | 6000  |                                       |                 |                 |                 |  |

| 8        | 128 | 18000  |                 |                 |                 |                 | 4500  |                                       |                 |                 |                 |  |

| 9        | 192 | 12000  |                 |                 |                 |                 | 3000  |                                       |                 |                 |                 |  |

| 10       | 256 | 9000   |                 |                 |                 |                 | 2250  |                                       |                 |                 |                 |  |

Single-cycle settling

|    | - Data Fato | (- <b>)</b> |         | •       |         |         |      |         |         |         |        |

|----|-------------|-------------|---------|---------|---------|---------|------|---------|---------|---------|--------|

| 11 | 384         | 6000        |         |         |         |         | 1500 |         |         |         |        |

| 12 | 512         |             | 4500.00 | 4500.00 | 4500.00 | 4500.00 |      | 2250.00 | 1500.00 | 1125.00 | 900.00 |

| 13 | 768         |             | 3000.00 | 3000.00 | 3000.00 | 3000.00 |      | 1500.00 | 1000.00 | 750.00  | 600.00 |

| 14 | 1024        |             | 2250.00 | 2250.00 | 2250.00 | 2250.00 |      | 1125.00 | 750.00  | 562.50  | 450.00 |

| 15 | 2048        |             | 1125.00 | 1125.00 | 1125.00 | 1125.00 |      | 562.50  | 375.00  | 281.25  | 225.00 |

| 16 | 4096        |             | 562.50  | 562.50  | 562.50  | 562.50  |      | 281.25  | 187.50  | 140.63  | 112.50 |

| 17 | 5760        |             | 400.00  | 400.00  | 400.00  | 400.00  |      | 200.00  | 133.33  | 100.00  | 80.00  |

| 18 | 7680        |             | 300.00  | 300.00  | 300.00  | 300.00  |      | 150.00  | 100.00  | 75.00   | 60.00  |

| 19 | 11520       |             | 200.00  | 200.00  | 200.00  | 200.00  |      | 100.00  | 66.67   | 50.00   | 40.00  |

| 20 | 23040       |             | 100.00  | 100.00  | 100.00  | 100.00  |      | 50.00   | 33.33   | 25.00   | 20.00  |

| 21 | 38400       |             | 60.00   | 60.00   | 60.00   | 60.00   |      | 30.00   | 20.00   | 15.00   | 12.00  |

| 22 | 46080       |             | 50.00   | 50.00   | 50.00   | 50.00   |      | 25.00   | 16.67   | 12.50   | 10.00  |

| 23 | 76800       |             | 30.00   | 30.00   | 30.00   | 30.00   |      | 15.00   | 10.00   | 7.50    | 6.00   |

| 24 | 92160       |             | 25.00   | 25.00   | 25.00   | 25.00   |      | 12.50   | 8.33    | 6.25    | 5.00   |

| 25 | 115200      |             | 20.00   | 20.00   | 20.00   | 20.00   |      | 10.00   | 6.67    | 5.00    | 4.00   |

| 26 | 153600      |             | 15.00   | 15.00   | 15.00   | 15.00   |      | 7.50    | 5.00    | 3.75    | 3.00   |

| 27 | 230400      |             | 10.00   | 10.00   | 10.00   | 10.00   |      | 5.00    | 3.33    | 2.50    | 2.00   |

| 28 | 307200      |             | 7.50    | 7.50    | 7.50    | 7.50    |      | 3.75    | 2.50    | 1.88    | 1.50   |

Table 7. Data rate (system clock: 4.608 MHz)...continued

The highest data rate is achieved with the lowest OSR, SINC4 only in Normal Settling mode.

#### 7.3.5.7 Noise performance vs data rate

The NAFE13388 noise performance depends on the device configuration: data rate, PGA gain, digital filter order, and Settling mode configuration. Two settings that affect noise performance are data rate and PGA gain. Decreasing the data rate results in a proportional decrease of total noise because the equivalent noise bandwidth of the digital filter is reduced proportionally with the data rate. Increasing the gain reduces input referred noise of the NAFE13388 because the noise of the PGA is lower than the noise of the ADC. Noise performance also depends on the shape of the digital filter because the order of the digital filter decreases the equivalent noise bandwidth, which results in lower noise.

The table below lists the typical noise performance of gain equal to 0.2 to 16 V/V (corresponding input full-scale ranges of  $\pm 25$  V to  $\pm 0.3125$  V) as input-referred values.

The noise performance data are in units of µVRMS (RMS = root mean square) under the conditions listed.

The data shown in the noise performance tables represent typical performance in normal settling at TA = 25 °C and internal 2.5 V reference voltage. The noise data are acquired with inputs shorted and is based on continuous ADC readings for a period of ten seconds or 1024 samples, whichever occurs first. Repeated noise measurements may yield higher or lower noise performance results because of the statistical nature of the noise.

The following tables in this section report the noise performance versus data rate and PGA gain setting.

Effective number of bits (ENOB) is calculated from the RMS noise applying the following formula:

ENOB = MIN(LOG(Full\_Scale\_Range / Noise\_RMS, 2), 24)

Full Scale Range =  $\frac{10}{PGAGAIN}$

Highly configurable 8/4-channel 24/16 bits ±25 V universal input analog front-end with excitation sources

# 7.3.5.7.1 Noise 24-bit option

#### Table 8. Noise µVrms (24-bit)

| Code |        |        | Estimate noise (uVrms) vs. gain setting |         |        |        |        |        |       |        |

|------|--------|--------|-----------------------------------------|---------|--------|--------|--------|--------|-------|--------|

|      | rate   | OSR    | 0.2                                     | 0.4     | 0.8    | 1      | 2      | 4      | 8     | 16     |

| 0    | 288000 | 8      | 27946.8                                 | 13973.4 | 6986.7 | 5589.4 | 2794.7 | 1397.4 | 698.7 | 349.45 |

| 1    | 192000 | 12     | 7546.0                                  | 3773.0  | 1886.5 | 1509.2 | 754.6  | 377.4  | 188.8 | 94.62  |

| 2    | 144000 | 16     | 2984.2                                  | 1492.1  | 746.1  | 596.9  | 298.5  | 149.3  | 74.9  | 37.85  |

| 3    | 96000  | 24     | 818.1                                   | 409.1   | 204.6  | 163.7  | 82.0   | 41.2   | 21.1  | 11.50  |

| 4    | 72000  | 32     | 343.5                                   | 171.8   | 86.0   | 68.8   | 34.6   | 17.8   | 9.7   | 6.26   |

| 5    | 48000  | 48     | 137.2                                   | 68.7    | 34.5   | 27.7   | 14.2   | 7.8    | 5.1   | 4.09   |

| 6    | 36000  | 64     | 98.8                                    | 49.5    | 24.9   | 20.0   | 10.4   | 5.9    | 4.1   | 3.45   |

| 7    | 24000  | 96     | 76.3                                    | 38.2    | 19.2   | 15.5   | 8.1    | 4.6    | 3.2   | 2.80   |

| 8    | 18000  | 128    | 65.7                                    | 32.9    | 16.6   | 13.3   | 7.0    | 4.0    | 2.8   | 2.42   |

| 9    | 12000  | 192    | 53.6                                    | 26.8    | 13.5   | 10.9   | 5.7    | 3.3    | 2.3   | 1.98   |

| 10   | 9000   | 256    | 46.4                                    | 23.2    | 11.7   | 9.4    | 4.9    | 2.8    | 2.0   | 1.71   |

| 11   | 6000   | 384    | 37.9                                    | 19.0    | 9.6    | 7.7    | 4.0    | 2.3    | 1.6   | 1.40   |

| 12   | 4500   | 512    | 32.8                                    | 16.4    | 8.3    | 6.7    | 3.5    | 2.0    | 1.4   | 1.21   |

| 13   | 3000   | 768    | 26.8                                    | 13.4    | 6.8    | 5.4    | 2.8    | 1.6    | 1.1   | 0.99   |

| 14   | 2250   | 1024   | 23.2                                    | 11.6    | 5.9    | 4.7    | 2.5    | 1.4    | 1.0   | 0.86   |

| 15   | 1125   | 2048   | 16.4                                    | 8.2     | 4.1    | 3.3    | 1.7    | 1.0    | 0.7   | 0.61   |

| 16   | 562.5  | 4096   | 11.6                                    | 5.8     | 2.9    | 2.4    | 1.2    | 0.7    | 0.5   | 0.43   |

| 17   | 400    | 5760   | 9.8                                     | 4.9     | 2.5    | 2.0    | 1.0    | 0.6    | 0.4   | 0.36   |

| 18   | 300    | 7680   | 8.5                                     | 4.3     | 2.2    | 1.7    | 0.9    | 0.5    | 0.4   | 0.31   |

| 19   | 200    | 11520  | 7.0                                     | 3.5     | 1.8    | 1.4    | 0.7    | 0.4    | 0.3   | 0.26   |

| 20   | 100    | 23040  | 5.0                                     | 2.5     | 1.3    | 1.0    | 0.5    | 0.3    | 0.2   | 0.18   |

| 21   | 60     | 38400  | 3.9                                     | 2.0     | 1.0    | 0.8    | 0.4    | 0.2    | 0.2   | 0.14   |

| 22   | 50     | 46080  | 3.6                                     | 1.8     | 0.9    | 0.7    | 0.4    | 0.2    | 0.2   | 0.13   |

| 23   | 30     | 76800  | 2.9                                     | 1.4     | 0.7    | 0.6    | 0.3    | 0.2    | 0.1   | 0.10   |

| 24   | 25     | 92160  | 2.7                                     | 1.3     | 0.7    | 0.5    | 0.3    | 0.2    | 0.1   | 0.09   |

| 25   | 20     | 115200 | 2.4                                     | 1.2     | 0.6    | 0.5    | 0.3    | 0.1    | 0.1   | 0.08   |

| 26   | 15     | 153600 | 2.2                                     | 1.1     | 0.5    | 0.4    | 0.2    | 0.1    | 0.1   | 0.07   |

| 27   | 10     | 230400 | 1.9                                     | 0.9     | 0.5    | 0.4    | 0.2    | 0.1    | 0.1   | 0.06   |

| 28   | 7.5    | 307200 | 1.7                                     | 0.9     | 0.4    | 0.3    | 0.2    | 0.1    | 0.1   | 0.05   |

Highly configurable 8/4-channel 24/16 bits ±25 V universal input analog front-end with excitation sources

# 7.3.5.7.2 ENOB 24-bit option

### Table 9. ENOB 24-bit option

| Code |        |        | Estimate ENOB vs. gain setting |      |      |      |      |      |      |      |

|------|--------|--------|--------------------------------|------|------|------|------|------|------|------|

|      | rate   | OSR    | 0.2                            | 0.4  | 0.8  | 1    | 2    | 4    | 8    | 16   |

| 0    | 288000 | 8      | 10.8                           | 10.8 | 10.8 | 10.8 | 10.8 | 10.8 | 10.8 | 10.8 |

| 1    | 192000 | 12     | 12.7                           | 12.7 | 12.7 | 12.7 | 12.7 | 12.7 | 12.7 | 12.7 |

| 2    | 144000 | 16     | 14.0                           | 14.0 | 14.0 | 14.0 | 14.0 | 14.0 | 14.0 | 14.0 |

| 3    | 96000  | 24     | 15.9                           | 15.9 | 15.9 | 15.9 | 15.9 | 15.9 | 15.8 | 15.6 |

| 4    | 72000  | 32     | 17.1                           | 17.1 | 17.1 | 17.1 | 17.1 | 17.1 | 16.9 | 16.4 |

| 5    | 48000  | 48     | 18.4                           | 18.4 | 18.4 | 18.4 | 18.4 | 18.2 | 17.7 | 16.9 |

| 6    | 36000  | 64     | 18.9                           | 18.9 | 18.9 | 18.9 | 18.8 | 18.6 | 18.0 | 17.2 |

| 7    | 24000  | 96     | 19.3                           | 19.3 | 19.3 | 19.2 | 19.2 | 18.9 | 18.3 | 17.5 |

| 8    | 18000  | 128    | 19.5                           | 19.5 | 19.5 | 19.5 | 19.4 | 19.1 | 18.5 | 17.7 |

| 9    | 12000  | 192    | 19.8                           | 19.8 | 19.8 | 19.8 | 19.7 | 19.4 | 18.8 | 18.0 |

| 10   | 9000   | 256    | 20.0                           | 20.0 | 20.0 | 20.0 | 19.9 | 19.6 | 19.0 | 18.2 |

| 11   | 6000   | 384    | 20.3                           | 20.3 | 20.3 | 20.3 | 20.2 | 19.9 | 19.3 | 18.5 |

| 12   | 4500   | 512    | 20.5                           | 20.5 | 20.5 | 20.5 | 20.4 | 20.1 | 19.5 | 18.7 |

| 13   | 3000   | 768    | 20.8                           | 20.8 | 20.8 | 20.7 | 20.7 | 20.4 | 19.8 | 19.0 |

| 14   | 2250   | 1024   | 21.0                           | 21.0 | 21.0 | 21.0 | 20.9 | 20.6 | 20.0 | 19.2 |

| 15   | 1125   | 2048   | 21.5                           | 21.5 | 21.5 | 21.5 | 21.4 | 21.1 | 20.5 | 19.7 |

| 16   | 562.5  | 4096   | 22.0                           | 22.0 | 22.0 | 22.0 | 21.9 | 21.6 | 21.0 | 20.2 |

| 17   | 400    | 5760   | 22.2                           | 22.2 | 22.2 | 22.2 | 22.1 | 21.8 | 21.3 | 20.4 |

| 18   | 300    | 7680   | 22.4                           | 22.4 | 22.4 | 22.4 | 22.3 | 22.1 | 21.5 | 20.6 |

| 19   | 200    | 11520  | 22.7                           | 22.7 | 22.7 | 22.7 | 22.6 | 22.3 | 21.8 | 20.9 |

| 20   | 100    | 23040  | 23.2                           | 23.2 | 23.2 | 23.2 | 23.1 | 22.8 | 22.3 | 21.4 |

| 21   | 60     | 38400  | 23.2                           | 23.2 | 23.2 | 23.2 | 23.1 | 22.8 | 22.3 | 21.4 |

| 22   | 50     | 46080  | 23.7                           | 23.7 | 23.7 | 23.6 | 23.6 | 23.3 | 22.8 | 21.9 |

| 23   | 30     | 76800  | 24.0                           | 24.0 | 24.0 | 24.0 | 23.9 | 23.7 | 23.1 | 22.3 |

| 24   | 25     | 92160  | 24.0                           | 24.0 | 24.0 | 24.0 | 24.0 | 23.8 | 23.2 | 22.4 |

| 25   | 20     | 115200 | 24.0                           | 24.0 | 24.0 | 24.0 | 24.0 | 23.9 | 23.4 | 22.6 |

| 26   | 15     | 153600 | 24.0                           | 24.0 | 24.0 | 24.0 | 24.0 | 24.0 | 23.6 | 22.8 |

| 27   | 10     | 230400 | 24.0                           | 24.0 | 24.0 | 24.0 | 24.0 | 24.0 | 23.9 | 23.1 |

| 28   | 7.5    | 307200 | 24.0                           | 24.0 | 24.0 | 24.0 | 24.0 | 24.0 | 24.0 | 23.9 |

Highly configurable 8/4-channel 24/16 bits ±25 V universal input analog front-end with excitation sources

# 7.3.5.7.3 Noise 16-bit option

#### Table 10. Noise 16-bit option

| Code |        |         | Estimate Noise(µVrms) vs PGA gain setting |         |        |        |        |        |       |        |  |

|------|--------|---------|-------------------------------------------|---------|--------|--------|--------|--------|-------|--------|--|

|      | rate   | OSR     | 0.2                                       | 0.4     | 0.8    | 1      | 2      | 4      | 8     | 16     |  |

| 0    | 288000 | 8       | 27948.3                                   | 13974.1 | 6987.1 | 5589.7 | 2794.9 | 1397.5 | 698.8 | 349.54 |  |

| 1    | 19200  | 12      | 7551.2                                    | 3775.6  | 1887.8 | 1510.3 | 755.2  | 377.7  | 189.0 | 94.85  |  |

| 2    | 14400  | 16      | 2997.3                                    | 1498.7  | 749.4  | 599.5  | 299.8  | 150.1  | 75.4  | 38.32  |  |

| 3    | 96000  | 24      | 864.1                                     | 432.1   | 216.1  | 172.9  | 86.7   | 43.7   | 22.6  | 12.64  |  |

| 4    | 72000  | 32      | 441.7                                     | 220.9   | 110.6  | 88.5   | 44.5   | 22.8   | 12.4  | 7.93   |  |

| 5    | 48000  | 48      | 309.0                                     | 154.5   | 77.4   | 62.0   | 31.2   | 16.1   | 9.0   | 6.04   |  |

| 6    | 36000  | 64      | 293.6                                     | 146.8   | 73.5   | 58.8   | 29.6   | 15.2   | 8.4   | 5.45   |  |

| 7    | 24000  | 96      | 286.4                                     | 143.2   | 71.7   | 57.4   | 28.8   | 14.7   | 7.9   | 4.86   |  |

| 8    | 18000  | 128     | 283.6                                     | 141.8   | 71.0   | 56.8   | 28.5   | 14.5   | 7.6   | 4.55   |  |

| 9    | 24000  | 192     | 280.8                                     | 140.4   | 70.2   | 56.2   | 28.2   | 14.2   | 7.4   | 4.21   |  |

| 10   | 9000   | 256     | 279.5                                     | 139.7   | 69.9   | 55.9   | 28.0   | 14.1   | 7.3   | 4.03   |  |

| 11   | 6000   | 384     | 278.1                                     | 139.1   | 69.5   | 55.6   | 27.9   | 14.0   | 7.1   | 3.84   |  |

| 12   | 4500   | 512     | 277.4                                     | 138.7   | 69.4   | 55.5   | 27.8   | 13.9   | 7.1   | 3.75   |  |

| 13   | 2250   | 1024    | 276.3                                     | 138.2   | 69.1   | 55.3   | 27.7   | 13.9   | 7.0   | 3.60   |  |

| 14   | 1125   | 2048    | 275.8                                     | 137.9   | 69.0   | 55.2   | 27.6   | 13.8   | 6.9   | 3.52   |  |

| 15   | 562.5  | 4096    | 275.6                                     | 137.8   | 68.9   | 55.1   | 27.6   | 13.8   | 6.9   | 3.48   |  |

| 16   | 300    | 7680    | 275.4                                     | 137.7   | 68.9   | 55.1   | 27.5   | 13.8   | 6.9   | 3.46   |  |

| 17   | 225    | 10240   | 275.4                                     | 137.7   | 68.9   | 55.1   | 27.5   | 13.8   | 6.9   | 3.46   |  |

| 18   | 150    | 15360   | 275.4                                     | 137.7   | 68.8   | 55.1   | 27.5   | 13.8   | 6.9   | 3.45   |  |

| 19   | 100    | 23040   | 275.3                                     | 137.7   | 68.8   | 55.1   | 27.5   | 13.8   | 6.9   | 3.45   |  |

| 20   | 50     | 46080   | 275.3                                     | 137.7   | 68.8   | 55.1   | 27.5   | 13.8   | 6.9   | 3.44   |  |

| 21   | 30     | 76800   | 275.3                                     | 137.7   | 68.8   | 55.1   | 27.5   | 13.8   | 6.9   | 3.44   |  |

| 22   | 25     | 92160   | 275.3                                     | 137.7   | 68.8   | 55.1   | 27.5   | 13.8   | 6.9   | 3.44   |  |

| 23   | 15     | 153600  | 275.3                                     | 137.7   | 68.8   | 55.1   | 27.5   | 13.8   | 6.9   | 3.44   |  |

| 24   | 12.5   | 184320  | 275.3                                     | 137.7   | 68.8   | 55.1   | 27.5   | 13.8   | 6.9   | 3.44   |  |

| 25   | 10     | 230400  | 275.3                                     | 137.7   | 68.8   | 55.1   | 27.5   | 13.8   | 6.9   | 3.44   |  |

| 26   | 5      | 460800  | 275.3                                     | 137.7   | 68.8   | 55.1   | 27.5   | 13.8   | 6.9   | 3.44   |  |

| 27   | 2.5    | 921600  | 275.3                                     | 137.7   | 68.8   | 55.1   | 27.5   | 13.8   | 6.9   | 3.44   |  |

| 28   | 1.25   | 1843200 | 275.3                                     | 137.7   | 68.8   | 55.1   | 27.5   | 13.8   | 6.9   | 3.44   |  |

Highly configurable 8/4-channel 24/16 bits ±25 V universal input analog front-end with excitation sources

## 7.3.5.7.4 ENOB 16-bit option

| Code | Data   | 2,304,000 | Estimate ENOB vs gain setting |      |      |      |      |      |      |      |

|------|--------|-----------|-------------------------------|------|------|------|------|------|------|------|

|      | rate   | OSR       | 0.2                           | 0.4  | 0.8  | 1    | 2    | 4    | 8    | 16   |

| 0    | 288000 | 8         | 10.8                          | 10.8 | 10.8 | 10.8 | 10.8 | 10.8 | 10.8 | 10.8 |

| 1    | 19200  | 12        | 12.7                          | 12.7 | 12.7 | 12.7 | 12.7 | 12.7 | 12.7 | 12.7 |

| 2    | 14400  | 16        | 14.0                          | 14.0 | 14.0 | 14.0 | 14.0 | 14.0 | 14.0 | 14.0 |

| 3    | 96000  | 24        | 15.8                          | 15.8 | 15.8 | 15.8 | 15.8 | 15.8 | 15.8 | 15.6 |

| 4    | 72000  | 32        | 16.0                          | 16.0 | 16.0 | 16.0 | 16.0 | 16.0 | 16.0 | 16.0 |

| 5    | 48000  | 48        | 16.0                          | 16.0 | 16.0 | 16.0 | 16.0 | 16.0 | 16.0 | 16.0 |

| 6    | 36000  | 64        | 16.0                          | 16.0 | 16.0 | 16.0 | 16.0 | 16.0 | 16.0 | 16.0 |

| 7    | 24000  | 96        | 16.0                          | 16.0 | 16.0 | 16.0 | 16.0 | 16.0 | 16.0 | 16.0 |

| 8    | 18000  | 128       | 16.0                          | 16.0 | 16.0 | 16.0 | 16.0 | 16.0 | 16.0 | 16.0 |

| 9    | 24000  | 192       | 16.0                          | 16.0 | 16.0 | 16.0 | 16.0 | 16.0 | 16.0 | 16.0 |

| 10   | 9000   | 256       | 16.0                          | 16.0 | 16.0 | 16.0 | 16.0 | 16.0 | 16.0 | 16.0 |

| 11   | 6000   | 384       | 16.0                          | 16.0 | 16.0 | 16.0 | 16.0 | 16.0 | 16.0 | 16.0 |

| 12   | 4500   | 512       | 16.0                          | 16.0 | 16.0 | 16.0 | 16.0 | 16.0 | 16.0 | 16.0 |

| 13   | 2250   | 1024      | 16.0                          | 16.0 | 16.0 | 16.0 | 16.0 | 16.0 | 16.0 | 16.0 |

| 14   | 1125   | 2048      | 16.0                          | 16.0 | 16.0 | 16.0 | 16.0 | 16.0 | 16.0 | 16.0 |

| 15   | 562.5  | 4096      | 16.0                          | 16.0 | 16.0 | 16.0 | 16.0 | 16.0 | 16.0 | 16.0 |

| 16   | 300    | 7680      | 16.0                          | 16.0 | 16.0 | 16.0 | 16.0 | 16.0 | 16.0 | 16.0 |

| 17   | 225    | 10240     | 16.0                          | 16.0 | 16.0 | 16.0 | 16.0 | 16.0 | 16.0 | 16.0 |

| 18   | 150    | 15360     | 16.0                          | 16.0 | 16.0 | 16.0 | 16.0 | 16.0 | 16.0 | 16.0 |

| 19   | 100    | 23040     | 16.0                          | 16.0 | 16.0 | 16.0 | 16.0 | 16.0 | 16.0 | 16.0 |

| 20   | 50     | 46080     | 16.0                          | 16.0 | 16.0 | 16.0 | 16.0 | 16.0 | 16.0 | 16.0 |

| 21   | 30     | 76800     | 16.0                          | 16.0 | 16.0 | 16.0 | 16.0 | 16.0 | 16.0 | 16.0 |

| 22   | 25     | 92160     | 16.0                          | 16.0 | 16.0 | 16.0 | 16.0 | 16.0 | 16.0 | 16.0 |

| 23   | 15     | 153600    | 16.0                          | 16.0 | 16.0 | 16.0 | 16.0 | 16.0 | 16.0 | 16.0 |

| 24   | 12.5   | 184320    | 16.0                          | 16.0 | 16.0 | 16.0 | 16.0 | 16.0 | 16.0 | 16.0 |

| 25   | 10     | 230400    | 16.0                          | 16.0 | 16.0 | 16.0 | 16.0 | 16.0 | 16.0 | 16.0 |

| 26   | 5      | 460800    | 16.0                          | 16.0 | 16.0 | 16.0 | 16.0 | 16.0 | 16.0 | 16.0 |

| 27   | 2.5    | 921600    | 16.0                          | 16.0 | 16.0 | 16.0 | 16.0 | 16.0 | 16.0 | 16.0 |

| 28   | 1.25   | 1843200   | 16.0                          | 16.0 | 16.0 | 16.0 | 16.0 | 16.0 | 16.0 | 16.0 |

# 7.3.6 Gain and offset calibration

All NAFE family products include 46 user-accessible calibration coefficient registers divided into three groups:

- Gain: GAIN\_COEF0[23:0] to GAIN\_COEF15[23:0]

- Offset: OFFSET\_COEF0[23:0] to OFFSET\_COEF15[23:0]

#### • Optional: OPT\_COEF0[23:0] to OPT\_COEF15[23:0]

To reduce the calibration error, the bit-width of gain, offset, and self-calibration coefficient registers are 24-bit wide, the same as main ADC.

The above user-calibration coefficients can be read and written by the user. During device power up or reset, the factory calibrated coefficients stored in NVM are loaded into the preset registers, if available. The user may overwrite with different calibration coefficients as needed.

In general, there are three categories of calibration coefficients:

- System offset and gain calibration coefficients for voltage or current input

- · System offset and gain calibration coefficients for resistance and RTD input

- Self-calibration values

- 2.5 V VREF

- 2.3 V REFH and 0.2 V REFL

These features enable accurate dynamic self-calibration without external voltage sources and advanced predictive maintenance.

<u>Table 12</u> describes the calibration gain/offset coefficient pair, addressable by coefficient pointer CH\_CONFIG1.CH\_CAL\_GAIN\_OFFSET.

| Pointer | Gain register     | ADDR \h | Offset register     | ADDR \h | NVM stored coefficient and setting      |

|---------|-------------------|---------|---------------------|---------|-----------------------------------------|

| 0       | GAIN_COEF0[23:0]  | 80      | OFFSET_COEF0[23:0]  | 90      | Gain = 0.2 V/V, single-ended Alxx-AlCOM |

| 1       | GAIN_COEF1[23:0]  | 81      | OFFSET_COEF1[23:0]  | 91      | Gain = 0.4 V/V, single-ended Alxx-AlCOM |

| 2       | GAIN_COEF2[23:0]  | 82      | OFFSET_COEF2[23:0]  | 92      | Gain = 0.8 V/V, single-ended Alxx-AlCOM |

| 3       | GAIN_COEF3[23:0]  | 83      | OFFSET_COEF3[23:0]  | 93      | Gain = 1 V/V, single-ended Alxx-AICOM   |

| 4       | GAIN_COEF4[23:0]  | 84      | OFFSET_COEF4[23:0]  | 94      | Gain = 2 V/V, single-ended Alxx-AICOM   |

| 5       | GAIN_COEF5[23:0]  | 85      | OFFSET_COEF5[23:0]  | 95      | Gain = 4 V/V, single-ended Alxx-AICOM   |

| 6       | GAIN_COEF6[23:0]  | 86      | OFFSET_COEF6[23:0]  | 96      | Gain = 8 V/V, single-ended Alxx-AICOM   |

| 7       | GAIN_COEF7[23:0]  | 87      | OFFSET_COEF7[23:0]  | 97      | Gain = 16 V/V, single-ended Alxx-AICOM  |

| 8       | GAIN_COEF8[23:0]  | 88      | OFFSET_COEF8[23:0]  | 98      | -                                       |

| 9       | GAIN_COEF9[23:0]  | 89      | OFFSET_COEF9[23:0]  | 99      | -                                       |

| 10      | GAIN_COEF10[23:0] | 8A      | OFFSET_COEF10[23:0] | 9A      | -                                       |

| 11      | GAIN_COEF11[23:0] | 8B      | OFFSET_COEF11[23:0] | 9B      | -                                       |

| 12      | GAIN_COEF12[23:0] | 8C      | OFFSET_COEF12[23:0] | 9C      | -                                       |

| 13      | GAIN_COEF13[23:0] | 8D      | OFFSET_COEF13[23:0] | 9D      | -                                       |

| 14      | GAIN_COEF14[23:0] | 8E      | OFFSET_COEF14[23:0] | 9E      | -                                       |

| 15      | GAIN_COEF15[23:0] | 8F      | OFFSET_COEF15[23:0] | 9F      | -                                       |

Table 12. System gain and offset calibration registers

#### Table 13. Optional and RTD calibrated coefficients register

| CAL REGISTER    | NVM stored parameter | Nominal value | Stored format | Setting description                                                                     |

|-----------------|----------------------|---------------|---------------|-----------------------------------------------------------------------------------------|

| OPT_COEF0[23:0] | VREFP_ADC            | 2.496 V       | (VREF/5)*2^24 | Factory measured voltage across pins<br>REFP_ADC - REFN_ADC                             |

| OPT_COEF1[23:0] | REFH - GND           | 2.29632 V     | (REFH/5)*2^24 | ADC converted voltage after factory CAL.<br>gain = 0.8 V/V, TCC_OFF = 1, CH_CHOP<br>= 1 |

| OPT_COEF2[23:0] | REFL - GND           | 0.19968 V     | (REFL/5)*2^24 | ADC converted voltage after factory CAL.<br>gain = 16 V/V, TCC_OFF = 1, CH_CHOP =<br>1. |

NAFE13388

Product data sheet

| CAL REGISTER     | NVM stored parameter | Nominal value | Stored format | Setting description                                                                |

|------------------|----------------------|---------------|---------------|------------------------------------------------------------------------------------|

| OPT_COEF3[23:0]  | RTD_OFFSET1          | 0             |               | Factory CAL coefficient for gain = 16 V/V,<br>VIEX_VI = 1, VIEX_MAG = 9\d (250 uA) |

| OPT_COEF4[23:0]  | RTD_GAIN1            | 1             | G = 2^24/4    | Factory CAL coefficient for gain = 16 V/V,<br>VIEX_VI = 1, VIEX_MAG = 9\d (250 uA) |

| OPT_COEF5[23:0]  | RTD_OFFSET2          | 0             |               | Factory CAL coefficient for gain = 8 V/V,<br>VIEX_VI = 1, VIEX_MAG = 11\d (500 uA) |

| OPT_COEF6[23:0]  | RTD_GAIN2            | 1             | G = 2^24/4    | Factory CAL coefficient for gain = 8 V/V,<br>VIEX_VI = 1, VIEX_MAG = 11\d (500 uA) |

| OPT_COEF7[23:0]  | RTD_OFFSET3          | 0             |               | Factory CAL coefficient for gain = 4 V/V,<br>VIEX_VI = 1, VIEX_MAG = 13\d (1 mA)   |

| OPT_COEF8[23:0]  | RTD_GAIN3            | 1             | G = 2^24/4    | Factory CAL coefficient for gain = 4 V/V,<br>VIEX_VI = 1, VIEX_MAG = 13\d (1 mA)   |

| OPT_COEF9[23:0]  | RTD_OFFSET4          | 0             |               | Factory CAL coefficient for gain = 0.8 V/V,<br>VIEX_VI = 1, VIEX_MAG = 13\d (1 mA) |

| OPT_COEF10[23:0] | RTD_GAIN4            | 1             | G = 2^24/4    | Factory CAL coefficient for gain =0 .8 V/V,<br>VIEX_VI = 1, VIEX_MAG = 13\d (1 mA) |

| OPT_COEF11[23:0] |                      |               |               |                                                                                    |

| OPT_COEF12[23:0] |                      |               |               |                                                                                    |

| OPT_COEF13[23:0] |                      |               |               |                                                                                    |

| OPT_COEF14[23:0] |                      |               |               |                                                                                    |

| OPT_COEF15[23:0] |                      |               |               |                                                                                    |

Table 13. Optional and RTD calibrated coefficients register...continued

Note: Units used in nominal value: voltage (V), gain (V/V), offset (V)

## 7.3.6.1 Gain and offset calibration coefficients

The NAFE product family includes 16 pairs of offset and gain calibration registers and internal adder and multiplier for offset and gain compensation.

Offset calibration registers are 24-bit wide. Their values are in two's complement format with a minimum negative value equal to 80\_0000\h and a maximum positive value equal to 7F\_FFF\h. A register value of 00\_0000\h has no offset correction.

$$Offset = \left(\frac{10}{2^{24}}\right) \cdot \frac{1}{GAIN} \cdot \left(mod\left(hex2dec(COEF) + 2^{23}, 2^{24}\right) - 2^{23}\right)$$

Gain calibration registers are 24-bit wide. Their values are straight binary format. The registers map a gain range from 0 to 3.99999976158142. The unity gain value is 40\_0000\h. <u>Table 14</u> shows the full range of gain factor correction.

$$Gain = \frac{COEF}{2^{22}}$$

The NAFE13388 output equation with internal digital calibration is as follows:

$$AFE_{OUT} = (ADCOUT - CAL_OFFSET) \cdot CAL_GAIN$$

Table 14. Gain calibration coefficient and factor

| Gain calibration<br>coefficient (Hexadecimal) | Gain calibration coefficient (Decimal) | Gain calibration factor<br>= Gain_coeff./(2^22) |

|-----------------------------------------------|----------------------------------------|-------------------------------------------------|

| FFFFF                                         | 16777215                               | 3.999998                                        |

| 800000                                        | 8388608                                | 2.000000                                        |

| 400001                                        | 4194305                                | 1.000002                                        |

| Gain calibration<br>coefficient (Hexadecimal) | Gain calibration coefficient (Decimal) | Gain calibration factor<br>= Gain_coeff./(2^22) |

|-----------------------------------------------|----------------------------------------|-------------------------------------------------|

| 400000                                        | 4194304                                | 1.000000                                        |

| 3FFFFF                                        | 4194303                                | 0.9999998                                       |

| 200000                                        | 2097152                                | 0.5000000                                       |

| 000000                                        | 0                                      | 0.000000                                        |

#### Table 14. Gain calibration coefficient and factor...continued

#### Table 15. Offset calibration coefficient and factor

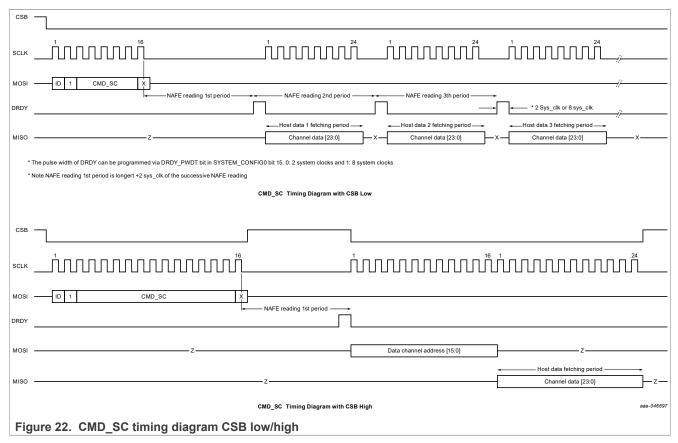

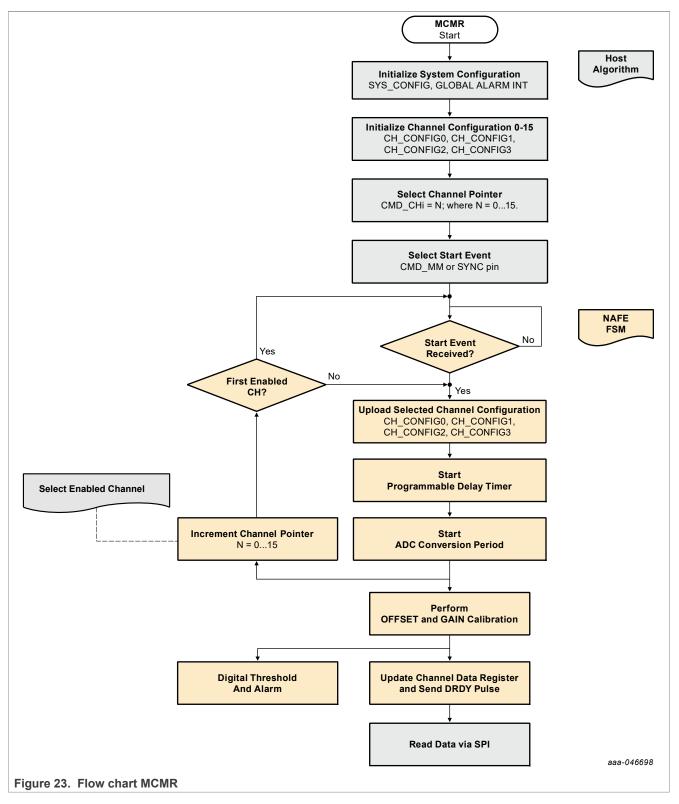

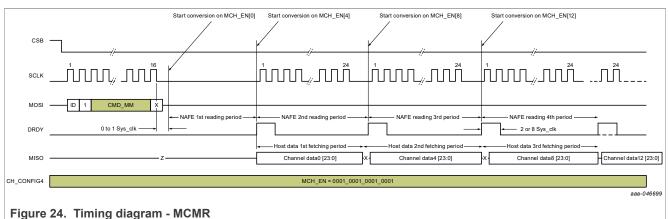

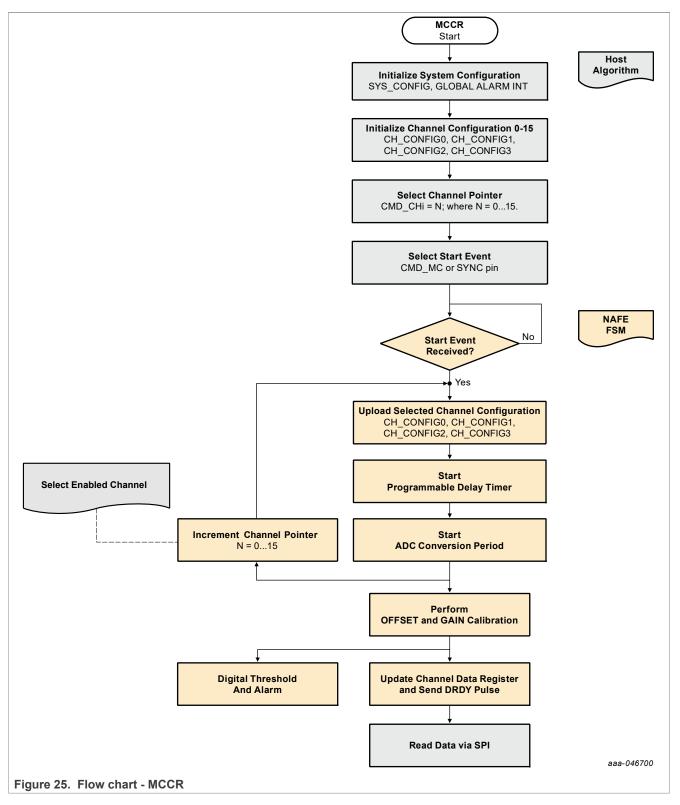

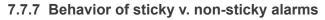

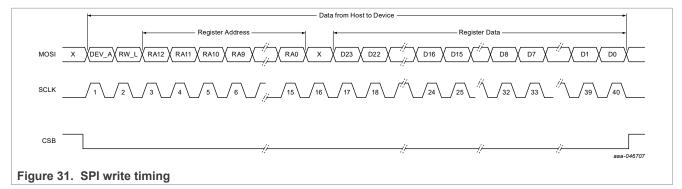

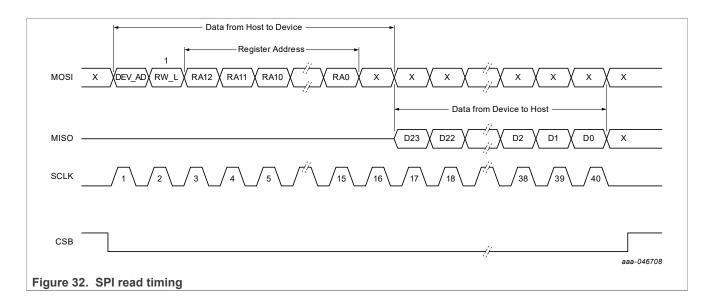

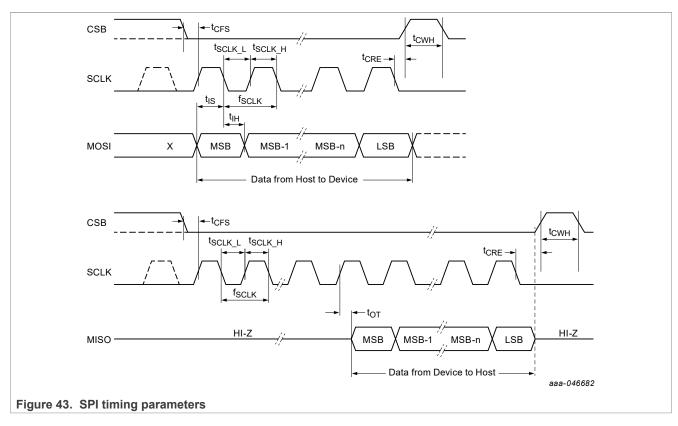

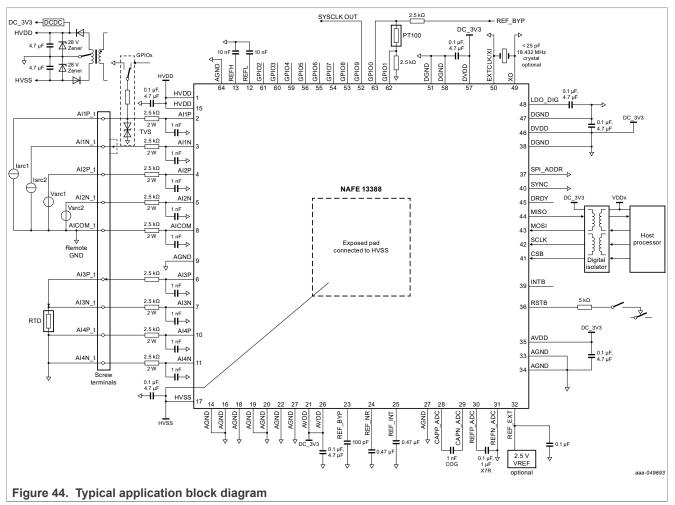

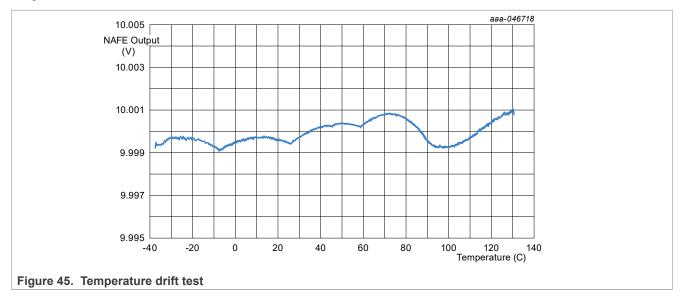

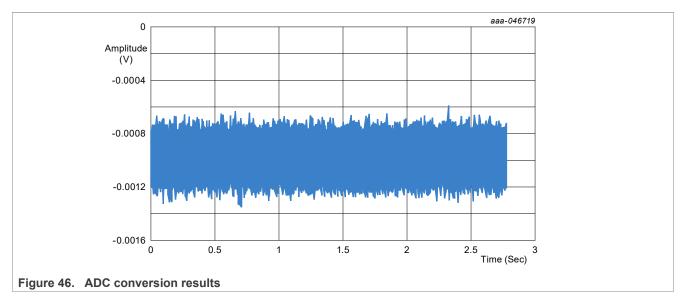

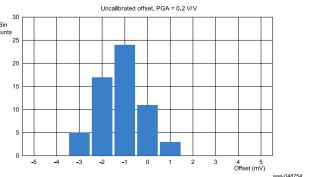

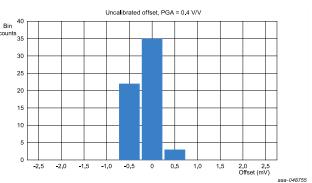

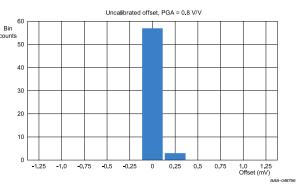

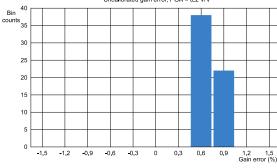

| Offset calibration coefficient (Hexadecimal) | Offset calibration coefficient (Decimal) | Offset calibration PGA = 0.2 (V) |