# **GD3160**

# Advanced IGBT/SiC gate driver

Rev. 14.0 — 10 December 2024

Product data sheet

# 1 General description

The GD3160 is an advanced, single-channel gate driver for IGBTs and SiC power devices. Integrated Galvanic isolation and low on-resistance drive transistors provide high charging and discharging current, low dynamic saturation voltage and rail-to-rail gate voltage control.

Current and temperature sense minimizes IGBT/SiC stress during faults. Accurate and configurable undervoltage lockout (UVLO) provides protection while ensuring sufficient gate-drive voltage headroom.

The GD3160 autonomously manages severe faults and reports faults and status via INTB and/or INTA pins and an SPI interface. It is capable of directly driving gates of most IGBTs and SiC MOSFETs. Self test, control, and protection functions are included for design of high-reliability systems (ASIL C/D). The GD3160 meets the stringent requirements of automotive applications and is fully AEC-Q100 grade 1 qualified.

Advanced IGBT/SiC gate driver

### 2 Features and benefits

This section summarizes the key features, safety features, and regulatory approvals for the GD3160.

### 2.1 Key features

- Integrated Galvanic signal isolation (up to 8 kV)

- High gate current integrated: 15 A source/sink capable

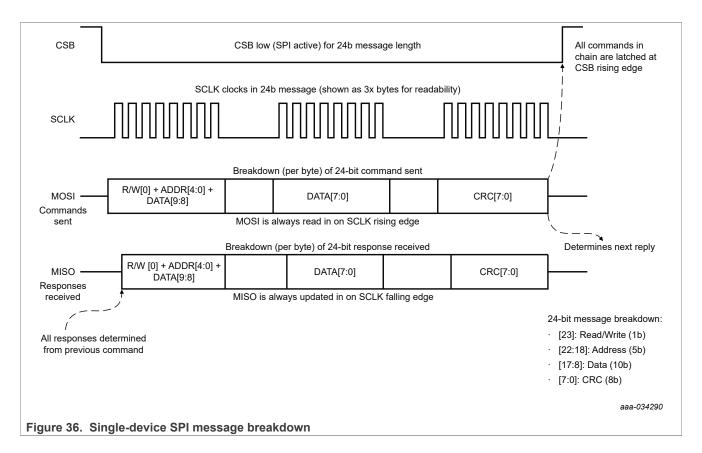

- · SPI interface for safety monitoring, configuration, and diagnostic reporting

- · Supports high switching frequencies: PWM up to 100 kHz

- Fail-safe state management from LV and HV domain for user-selectable safe state

- · Programmable gate voltage regulator

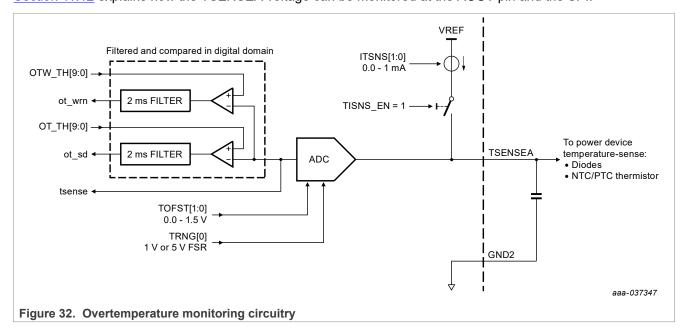

- Temperature sense compatible with diode-based temperature sensors, NTC and PTC thermistors

- · Configurable desaturation and current sense optimized for protecting SiC and IGBTs

- · Integrated soft shutdown, two-level turn-off, optimized for unique gate drive requirements of SiC

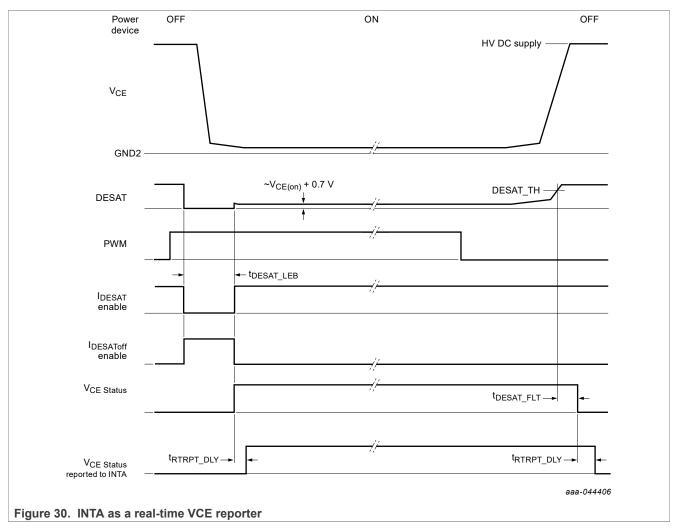

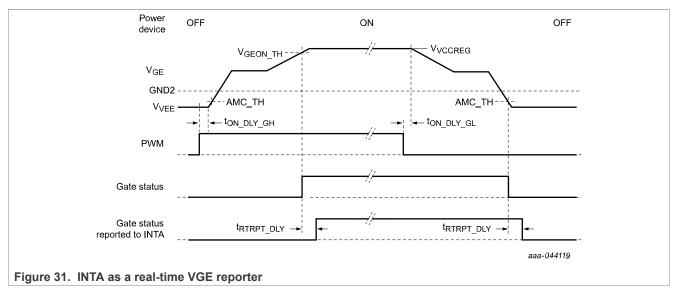

- Real-time VCE and VGE reporting via INTA pin

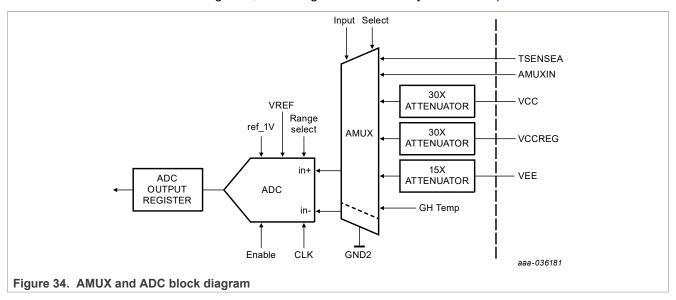

- Integrated ADC for monitoring parameters from HV domain

- CMTI > 100 V/ns

- Compatible with 200 to 1700 V IGBT/SiC, power range > 125 kW

- Operating temperature range -40 to 125 °C

- Available in 5.0 or 3.3 V logic interface variants

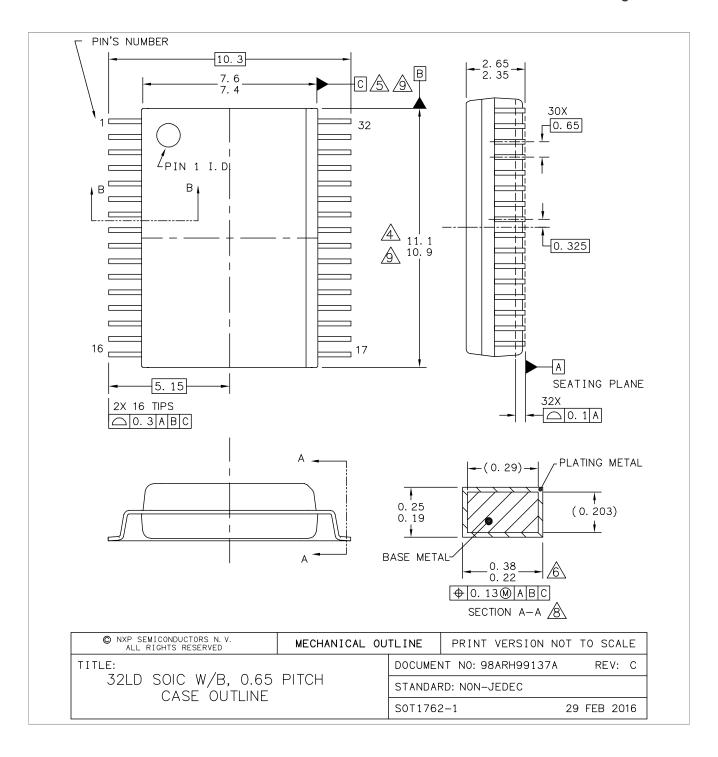

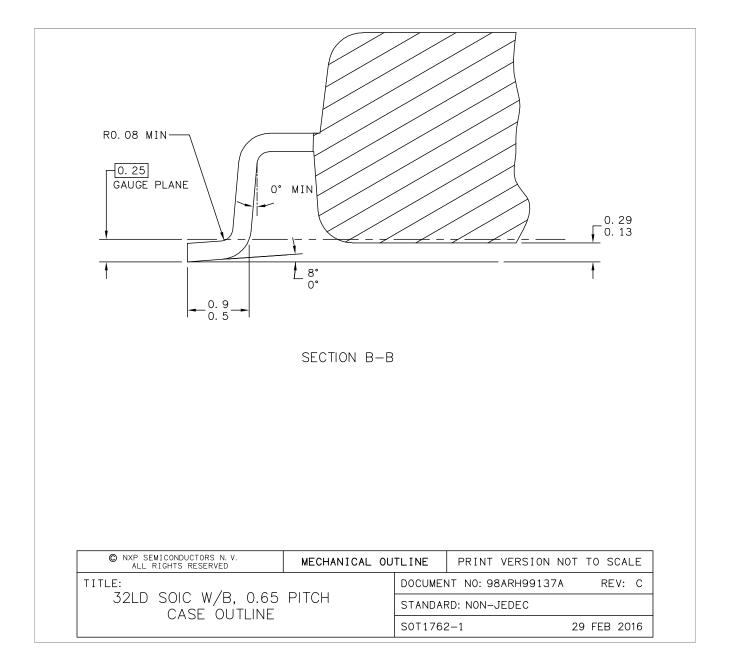

- Small package footprint (10 mm x 11 mm) 32-pin SOIC

### 2.2 Safety features

- Certified compliant with ISO 26262, supporting ASIL D level functional safety

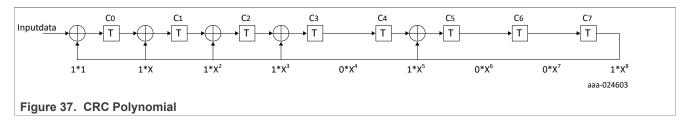

- · Error checking of SPI and configuration data with 8-bit CRC

- Autonomously manages severe faults and reports status via configurable INTB and/or INTA pins, and SPI interface

- · Current, DESAT, and temperature sense inputs and ADC reporting for IGBT/SiC monitoring and protection

- · Interrupt pins (INTA and INTB) for fast response to faults

- · Built-in self-check of all analog and digital circuits

- Continuous watchdog of communications across isolation barrier

- · Deadtime enforcement

- · Over- and undervoltage supervision of all power supplies on both low- and high-voltage sides

- · Dedicated fail-safe state management pins on both low- and high-voltage sides

- · VGE real-time cycle-by-cycle monitoring

#### 2.3 Safety and regulatory approvals

- Reinforced isolation per DIN V VDE V 0884-10

- Withstand 5000 V rms (1 minute) isolation per UL 1577

- · AEC-Q100 grade 1 automotive qualified

Advanced IGBT/SiC gate driver

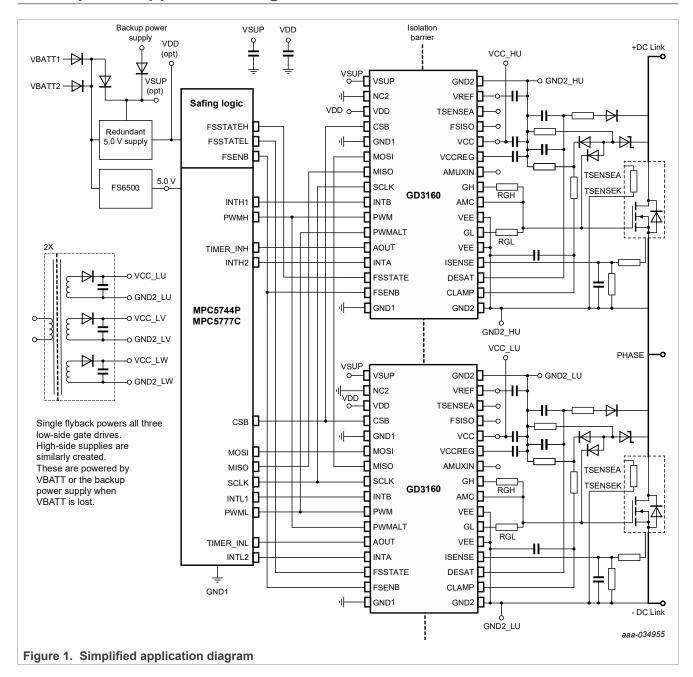

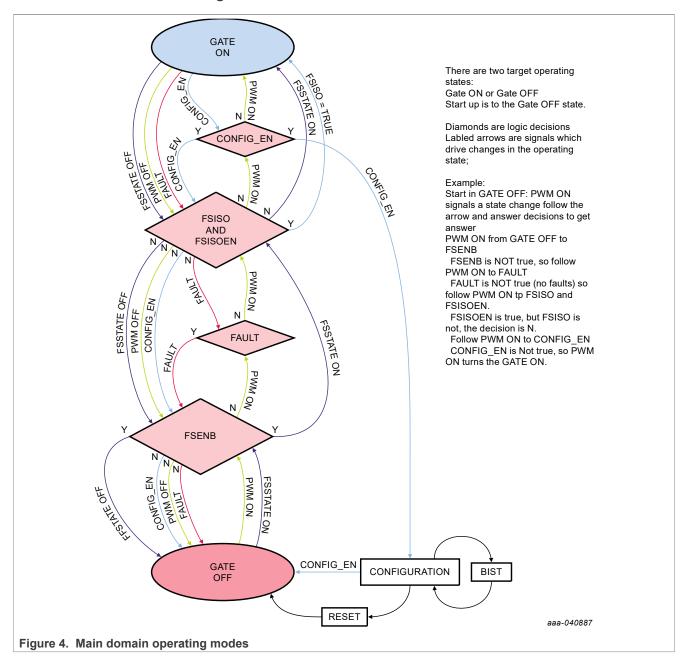

# 3 Simplified application diagram

Advanced IGBT/SiC gate driver

# 4 Applications

- · SiC gate driver

- · IGBT gate driver

- DC/DC power converter

- · Automotive traction inverter

## Advanced IGBT/SiC gate driver

# **Ordering information**

Table 1. Orderable part variations

| Part number <sup>[1]</sup> | VDD   | External clearance and creepage distance [2] | Material<br>(isolation)<br>group <sup>[3]</sup> | FSISO option (Gate state when FSISO is activated) | Temperature (T <sub>J</sub> ) | Package                |

|----------------------------|-------|----------------------------------------------|-------------------------------------------------|---------------------------------------------------|-------------------------------|------------------------|

| MGD3160AM515EK             | 5.0 V | > 7.72 mm                                    | II                                              | Gate ON                                           |                               |                        |

| MGD3160AM518EK             | 5.0 V | > 8.0 mm                                     | I                                               | Gate ON                                           | 1                             |                        |

| MGD3160AM535EK             | 5.0 V | > 7.72 mm                                    | II                                              | Gate 3-STATE                                      | 1                             |                        |

| MGD3160AM538EK             | 5.0 V | > 8.0 mm                                     | I                                               | Gate 3-STATE                                      | 40 °C to 150 °C               | 32-pin wide body SOIC, |

| MGD3160AM315EK             | 3.3 V | > 7.72 mm                                    | II                                              | Gate ON                                           | -40 C to 150 C                | 0.65 mm pitch          |

| MGD3160AM318EK             | 3.3V  | > 8.0 mm                                     | I                                               | Gate ON                                           | 1                             |                        |

| MGD3160AM335EK             | 3.3 V | > 7.72 mm                                    | II                                              | Gate 3-STATE                                      | 1                             |                        |

| MGD3160AM338EK             | 3.3 V | > 8.0 mm                                     | I                                               | Gate 3-STATE                                      | 1                             |                        |

To order parts in tape and reel, add the R2 suffix to the part number. To order parts in tray packing, add the T suffix to the part number. per IEC 60950-1 Tables 2K and 2N per IEC 60664-1 [1] [2] [3]

### Advanced IGBT/SiC gate driver

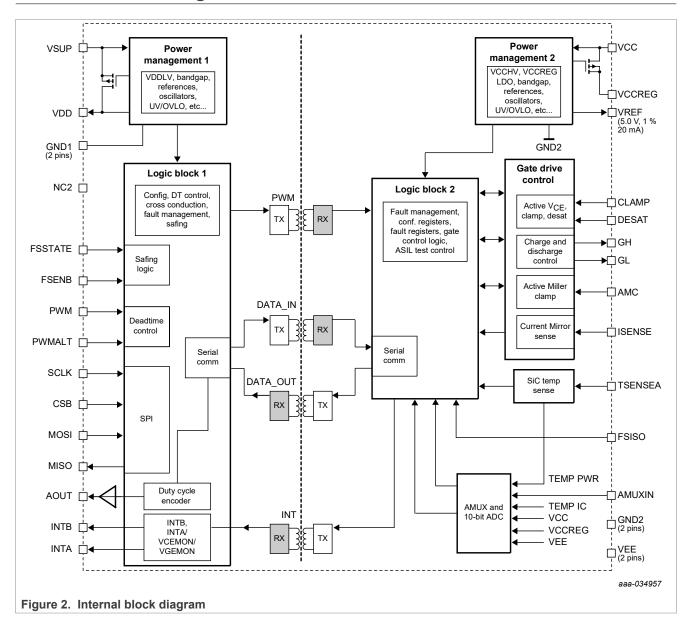

# 6 Internal block diagram

Advanced IGBT/SiC gate driver

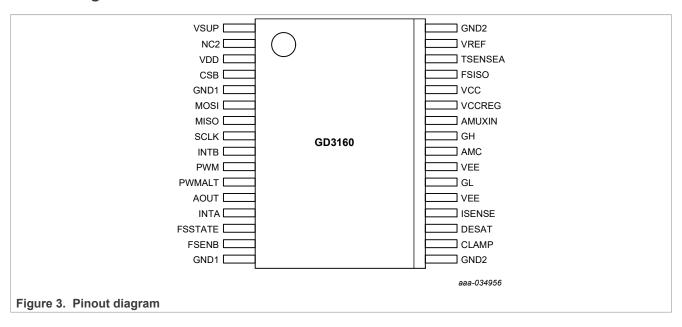

# 7 Pinning information

## 7.1 Pinning

## 7.2 Pin description

Table 2. Pin definitions

| Pin number       | Pin name       | Pin type               | Definition                                                     | Comments                                                                                                                                                                                                           |

|------------------|----------------|------------------------|----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pins 1 to 16 (lo | w-voltage, non | -isolated pins)        |                                                                |                                                                                                                                                                                                                    |

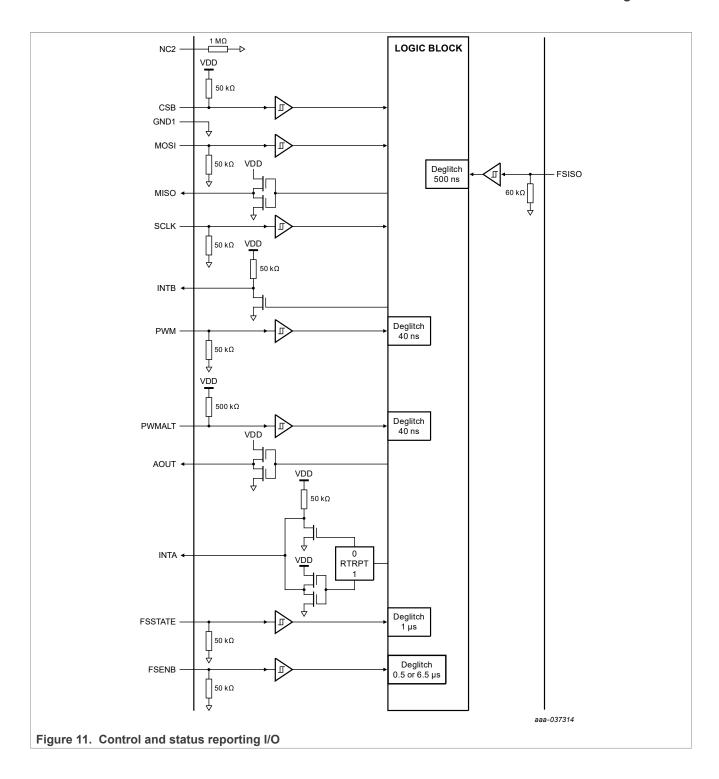

| 1                | VSUP           | Input/power            | Primary power supply for non-isolated low-voltage (LV) domain. | Main supply input is compatible with 12 V automotive battery range/transients, referenced to GND1. VSUP may either be (1) driven by 12V, or (2) tied to VDD and powered by an external, post-regulated 5 V supply. |

| 2                | NC2            | No connect             | No connection.                                                 | NC2 must be connected to GND1.                                                                                                                                                                                     |

| 3                | VDD            | Input-output/<br>power | Power supply for non-<br>isolated low-voltage<br>(LV) logic.   | Main supply for logic on LV domain, referenced to GND1. VDD may either be (1) regulated internally to 3.3 V or 5.0 V from VSUP, or (2) tied to VSUP and powered by an external, post-regulated 5 V supply.         |

| 4                | CSB            | Input/digital          | SPI chip select.                                               | Active low CSB activates SPI link and framing.                                                                                                                                                                     |

| 5, 16            | GND1           | Ground 1               | Ground for non-<br>isolated (LV) domain<br>power and logic.    | Redundant GND1 pins provide ground reference for all non-isolated low-voltage (LV) domain signals. Isolated from all circuitry referenced to GND2.                                                                 |

| 6                | MOSI           | Input/digital          | SPI MOSI pin.                                                  | Input data for GD3160 SPI. MOSI data latches on rising edge of SCLK, MSB first. Internal passive pulldown to GND1.                                                                                                 |

| 7                | MISO           | Output/digital         | SPI MISO pin.                                                  | Data output for GD3160 SPI. GD3160 outputs MISO on falling edge of SCLK, MSB first.                                                                                                                                |

| 8                | SCLK           | Input/digital          | SPI clock.                                                     | GD3160 acknowledges SPI clock only when CSB is low. Internal passive pulldown to GND1.                                                                                                                             |

| 9                | INTB           | Output/Dgital          | Interrupt/Fault status output.                                 | INTB reports fault with active low (logic 0 reports fault). Internal passive pullup to VDD.                                                                                                                        |

| 10               | PWM            | Input/digital          | PWM control command for gate output.                           | Logic high turns on power device gate. PWM pin is ignored during fail-safe, configuration, BIST, reset, and most fault modes. Internal passive pull down to GND1.                                                  |

| 11               | PWMALT         | Input/digital          | Complementary PWM command for gate output.                     | Complementary PWMALT enforces deadtime constraint and prevents accidental shoot-through condition. Connect to GND1 if unused. Internal passive pull up to VDD.                                                     |

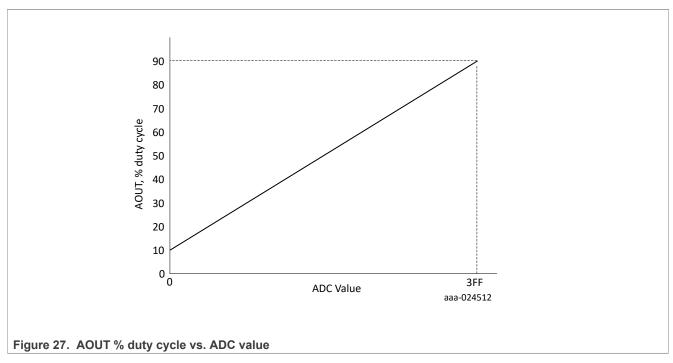

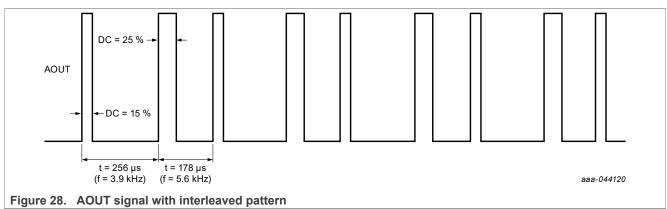

| 12               | AOUT           | Output/analog          | Duty-cycle encoded output of isolated ADC.                     | 5.0 V, 3.9 kHz (or multiplexed with 5.6 kHz) readout is configurable by SPI. Pin left open if unused.                                                                                                              |

GD3160

All information provided in this document is subject to legal disclaimers.

© 2024 NXP B.V. All rights reserved.

# Advanced IGBT/SiC gate driver

Table 2. Pin definitions...continued

| Pin number       | Pin name          | Pin type                | Definition                                                                      | Comments                                                                                                                                                                                                                                     |

|------------------|-------------------|-------------------------|---------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 13               | INTA              | Output/digital          | Interrupt/fault status/<br>monitor.                                             | Output pin reports fault via active pulldown interrupt, or reports VCE or VGE state via logic high/low. Pullup pin to VDD with a 50 k $\Omega$ resistor or left open if unused.                                                              |

| 14               | FSSTATE           | Input/digital           | Fail-safe gate state control pin.                                               | Gate output control pin. Connect to GND1 if unused. Internal passive pulldown to GND1.                                                                                                                                                       |

| 15               | FSENB             | Input/digital           | Fail-safe mode enable pin.                                                      | Active-low pin enabling Fail-Safe mode (FSSTATE controls gate). Internal passive pulldown to GND1. Connect to VDD if unused.                                                                                                                 |

| Pins 17 to 32 (I | high-voltage, iso | plated pins)            |                                                                                 |                                                                                                                                                                                                                                              |

| 17, 32           | GND2              | Ground 2                | Ground for isolated (HV) domain power, analog, and logic.                       | Redundant GND2 pins provide ground reference for all isolated high-voltage (HV) domain. Isolated from all circuitry referenced to GND1. Connect to power device emitter/source.                                                              |

| 18               | CLAMP             | Input/analog            | Sense terminal for<br>VCE/VDS overvoltage<br>during turn-off.                   | CLAMP detects Zener breakdown current and increase gate drive impedance and employ soft shutdown for turn-off. Connect to VEE if unused.                                                                                                     |

| 19               | DESAT             | Input-output/<br>analog | Drive/sense terminal for VCE/VDS desaturation condition.                        | Connected to GND2 if unused.                                                                                                                                                                                                                 |

| 20               | ISENSE            | Input/analog            | Current sense feedback pin.                                                     | Resistive network converts current mirror into readable voltage signal on ISENSE. Connect to GND2 if unused.                                                                                                                                 |

| 21, 23           | VEE               | Input/power             | Negative gate supply voltage.                                                   | VEE is the negative voltage on the isolated domain, and is referenced to GND2. Connect to GND2 if a negative supply is not used.                                                                                                             |

| 22               | GL                | Output/analog           | Pulldown pin for output gate turn-off/discharge event.                          | GL pin pulls gate to VEE.                                                                                                                                                                                                                    |

| 24               | AMC               | Input-output/<br>analog | Direct connect to gate for gate voltage sense and active Miller clamp function. | AMC provides low-impedance holdoff (active Miller clamp) and senses VGE/VGS for reporting and diagnostics.                                                                                                                                   |

| 25               | GH                | Output/analog           | Pullup pin for output gate turn-on event.                                       | GH pin pulls gate to VCCREG.                                                                                                                                                                                                                 |

| 26               | AMUXIN            | Input/analog            | General-purpose input for isolated ADC.                                         | One of many SPI-selectable inputs for the isolated ADC. Connect to GND2 if unused.                                                                                                                                                           |

| 27               | VCCREG            | Output/power            | Internally-regulated positive gate supply.                                      | Programmable gate supply derived from VCC, referenced to GND2. Connect to VCC if unused.                                                                                                                                                     |

| 28               | VCC               | Input/power             | Positive voltage supply for isolated domain circuitry.                          | Referenced to GND2.                                                                                                                                                                                                                          |

| 29               | FSISO             | Input/digital           | HV domain pin to enable the Fail-safe state.                                    | Active-high disables PWM, FSSTATE, and, according to the part number, turns on gate (MGD3160AM515EK, MGD3160AM315EK, MGD3160 AM518EK or MGD3160AM318EK) or 3-states GATE (MGD3160AM535EK, MGD3160AM335EK, MGD3160AM538EK).                   |

| 30               | TSENSEA           | Input/analog            | Anode of temp sense diode/NTC of the power module.                              | TSENSEA reads back voltage from temperature sense element, and is referenced to GND2. Includes possible current driver for temp sense network. The temperature sense network cathode should be connected to GND2. Connect to VREF if unused. |

| 31               | VREF              | Output/power            | Internally regulated reference voltage for HV domain analog, ADC, and logic.    | Output for an internally generated 5.0 V, 20 mA regulator. Referenced to GND2.                                                                                                                                                               |

Advanced IGBT/SiC gate driver

## **Product characteristics**

### 8.1 Range of functionality

Table 3. Range of functionality

All voltages referenced to GND1 (LV domain) or GND2 (HV domain). Currents are positive into and negative out of the specified pins.

| Symbol                                 | Description (rating)                                                                                                                |      | Min           | Max    | Unit |

|----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|------|---------------|--------|------|

| TJ                                     | Operating junction temperature                                                                                                      |      | -40           | 150    | °C   |

| f <sub>PWM</sub>                       | PWM switching frequency                                                                                                             |      | 0             | 100    | kHz  |

| V <sub>VEE</sub>                       | High-voltage domain negative supply voltage                                                                                         | [1]  | -10           | 0.3    | V    |

| VSUP not connec                        | ted to VDD                                                                                                                          |      |               | •      |      |

| V <sub>VSUP</sub>                      | Low-voltage domain supply voltage, full performance (MGD3160AM515EK, MGD3160AM535EK, MGD3160AM518EK or MGD3160AM538EK 5.0 V option) | [2]  | 6             | 32     | V    |

|                                        | Low-voltage domain supply voltage, full performance (MGD3160AM315EK, MGD3160AM335EK, MGD3160AM318EK or MGD3160AM338EK 3.3 V option) | [2]  | 4.5           | 32     | V    |

| V <sub>VSUP_JS</sub>                   | Low-voltage domain jump start voltage, 1 minute at 25 °C                                                                            | [3]  | _             | 28     | V    |

| V <sub>VSUP_LD</sub>                   | Low-voltage domain load dump voltage, 400 ms at 25 °C                                                                               | [4]  | _             | 40     | V    |

|                                        | Note: Load dump voltage test according to ISO16750-2 Test B                                                                         |      |               |        |      |

| VSUP connected                         | to VDD (MGD3160AM515EK, MGD3160AM535EK, MGD3160AM518EK or MGD3160                                                                   | 0AM5 | 38EK, 5.0 V o | ption) |      |

| V <sub>VDD</sub> , V <sub>VSUP</sub>   | Low-voltage domain supply voltage                                                                                                   | [5]  | 4.75          | 5.25   | V    |

| VCC not connecte                       | ed to VCCREG                                                                                                                        |      |               |        |      |

| V <sub>VCC</sub>                       | High-voltage domain positive supply voltage                                                                                         | [1]  | _             | 25     | V    |

| V <sub>VCCREG</sub>                    | High-voltage domain post regulated supply voltage                                                                                   | [1]  | 9.3           | _      | V    |

| VCC connected to                       | VCCREG                                                                                                                              |      |               |        | -    |

| V <sub>VCC</sub> , V <sub>VCCREG</sub> | High-voltage domain positive supply voltage                                                                                         | [1]  | 9.3           | 25     | V    |

|                                        | l .                                                                                                                                 |      |               |        |      |

- Ref = GND2

- Ref = GND1, VDD generated internally

- [1] [2] [3] [4] [5] Jump start test according to ISO16750-2

- Load dump voltage test according to ISO16750-2 Test B

- Ref = GND1, VDD and VSUP connected, VDD generated externally

### 8.2 Absolute maximum ratings

All voltages are referenced to GND1 or GND2. Currents are positive into and negative out of the specified pins. Exceeding these ratings may cause malfunction or permanent device damage.

Table 4. Absolute maximum ratings

All voltages referenced to GND1 (LV domain) or GND2 (HV domain). Currents are positive into and negative out of the specified pins.

| Symbol               | Description (Rating)                                       | Min  | Max | Unit |

|----------------------|------------------------------------------------------------|------|-----|------|

| Power suppli         | es and current references                                  | •    |     |      |

| V <sub>VSUP</sub>    | Low-voltage domain supply voltage [1]                      | -0.3 | 40  | V    |

| V <sub>VDD3p3</sub>  | Low-voltage domain logic supply voltage, 3.3 V version [1] | -0.3 | 6.0 | V    |

| V <sub>VDD5</sub>    | Low-voltage domain logic supply voltage, 5.0 V version [1] | -0.3 | 6.0 | V    |

| V <sub>VCC</sub>     | High-voltage domain positive supply voltage [2]            | -0.3 | 25  | V    |

| V <sub>VEE</sub>     | High-voltage domain negative supply voltage [2]            | -12  | 0.3 | V    |

| V <sub>VCC-VEE</sub> | High-voltage domain positive/negative supply               | -0.3 | 37  | V    |

| V <sub>VCCREG</sub>  | High-voltage domain post regulated supply voltage [2]      | -0.3 | 25  | V    |

GD3160

## Advanced IGBT/SiC gate driver

Table 4. Absolute maximum ratings...continued

All voltages referenced to GND1 (LV domain) or GND2 (HV domain). Currents are positive into and negative out of the specified pins.

| Symbol                  | Description (Rating)                                                   |          | Min       | Max                         | Unit     |

|-------------------------|------------------------------------------------------------------------|----------|-----------|-----------------------------|----------|

| VCCREG                  | VCCREG output current                                                  |          |           | -100                        | mA       |

| / <sub>VREF</sub>       | VREF voltage                                                           | [2]      | -0.3      | 6.0                         | V        |

| VREF                    | VREF output current                                                    |          | _         | -20                         | mA       |

| ogic pins               |                                                                        |          |           |                             |          |

| V <sub>IN</sub>         | Logic input pin voltage (FSSTATE, FSENB, PWM, PWMALT, SCLK, CSB, MOSI) | [1]      | -0.3      | 18                          | V        |

| V <sub>OUT</sub>        | Logic output pin voltage (MISO, INTB, INTA, AOUT)                      | [1]      | -0.3      | V <sub>VDD</sub> + 0.3 V    | V        |

| V <sub>INTB</sub>       | INTB voltage                                                           | [1]      | -0.3      | 6.3                         | V        |

| V <sub>FSISO</sub>      | Logic input pin voltage (FSISO)                                        | [2]      | -0.3      | 6.3                         | V        |

|                         | Gate drive outpu                                                       | ıt stage |           |                             |          |

| V <sub>GH</sub>         | GH voltage                                                             | [2]      | VEE - 0.3 | V <sub>VCCREG</sub> + 0.3 V | V        |

| V <sub>GL</sub>         | GL voltage                                                             | [2]      | VEE - 0.3 | V <sub>VCCREG</sub> + 0.3 V | V        |

| V <sub>AMC</sub>        | AMC voltage                                                            | [2]      | VEE - 0.3 | V <sub>VCCREG</sub> + 0.3 V | V        |

| I <sub>SOURCEMAX</sub>  | GH max. source current                                                 | [3]      |           | -15                         | Α        |

| I <sub>SINKMAX</sub>    | GL, AMC max. sink current                                              | [3]      | _         | 15                          | A        |

| V <sub>CLAMP</sub>      | CLAMP voltage                                                          | [2]      | VEE - 0.3 | V <sub>VCC</sub> + 0.3 V    | V        |

| V <sub>DESAT</sub>      | DESAT voltage                                                          | [2]      | -0.3      | V <sub>VCC</sub> + 0.3 V    | V        |

| Temperature             |                                                                        |          |           | V00 1 1                     |          |

| V <sub>TSENSEA</sub>    | TSENSEA voltage                                                        | [2]      | -0.3      | 6.0                         | V        |

| Interrupt pin:          | <u> </u>                                                               |          |           |                             |          |

| I <sub>INTA</sub>       | Open drain DC output current                                           | [4]      | _         | -20                         | mA       |

| I <sub>INTB</sub>       | Open drain DC output current                                           | [4]      | _         | -20                         | mA       |

| ISENSE sens             |                                                                        |          |           | -                           |          |

| V <sub>ISENSE</sub>     | ISENSE voltage                                                         | [2]      | -2.0      | V <sub>VCC</sub> + 0.3 V    | V        |

| AMUXIN pin <sup>[</sup> |                                                                        |          |           | 7 700 010 7                 | <u> </u> |

| V <sub>AMUXIN</sub>     | AMUXIN voltage                                                         | [2]      | -0.3      | 6.0                         | V        |

| ESD ratings             | / Wie / Wie Vollage                                                    |          | 0.0       | 0.0                         | •        |

|                         | ESD voltage (HBM)                                                      | [6]      |           |                             | kV       |

| $V_{ESDHBM}$            | All pins                                                               |          | -2.0      | 2.0                         | ΚV       |

|                         | ESD voltage (CDM)                                                      | [7]      |           |                             | V        |

| V <sub>ESDCDM</sub>     | Corner pins                                                            |          | -750      | 750                         |          |

|                         | Other pins                                                             |          | -500      | 500                         |          |

| V                       | ESD voltage (module level)                                             | [8]      |           |                             | kV       |

| V <sub>ESDModule</sub>  | VSUP, GND1, GND2 pins                                                  |          | -8.0      | 8.0                         |          |

| Immunity                |                                                                        |          |           |                             |          |

| dV <sub>ISO</sub> /dt   | Common mode transient immunity                                         | [9]      | _         | 100                         | V/ns     |

| PWM freque              | ncy                                                                    |          |           |                             |          |

| f <sub>PWMMAX</sub>     | Maximum switching frequency                                            |          | _         | 100                         | kHz      |

Ref = GND1

Ref = GND2

<sup>50 %, 100</sup> nF, 10 kHz V<sub>INTB</sub>, V<sub>INTA</sub> < 1.0 V

<sup>[1]</sup> [2] [3] [4]

### Advanced IGBT/SiC gate driver

ADC performance is guaranteed by design up to 500 µA injected current on AMUXIN pin.

Human Body Model (HBM) at device level

ANSI/ESDA/JEDEC JS-001: 2010 Model HBM (human body model)

Electrostatic Discharge (ESD) Sensitivity Testing Human Body Model (HBM)

Test points: pin to GND1 and pin to GND2

Charged Device Model (CDM)

ANSI/ESD S5.3.1-2009

ESD Association Standard for Electrostatic Discharge Sensitivity Testing - Charged Device Model (CDM) - Component Level

**Module Level ESD Tests**

ISO 10605:2008/Cor. 1:2010(E)

Road vehicles - Test methods for electrical disturbances from electrostatic discharge

Pulse width = 10 ns

#### 8.3 Thermal characteristics

#### Table 5. Thermal ratings

Exceeding these ratings may cause a malfunction or permanent damage to the device.

| Symbol              | Description (rating)                                  | Min | Max | Unit |

|---------------------|-------------------------------------------------------|-----|-----|------|

| Thermal ratings     |                                                       |     |     |      |

| T <sub>J</sub>      | Operating junction temperature                        | -40 | 150 | °C   |

| T <sub>STG</sub>    | Storage temperature                                   | -65 | 150 | °C   |

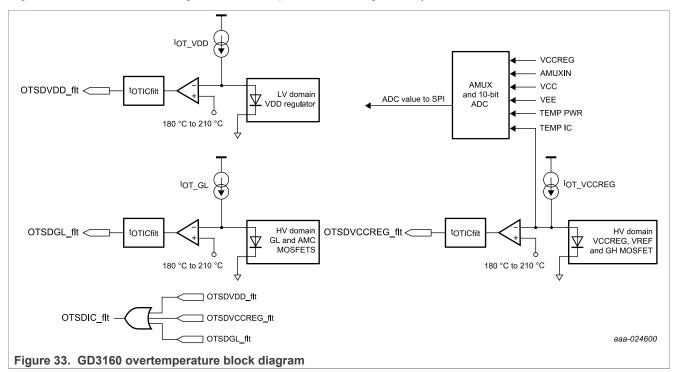

| T <sub>OTSDth</sub> | Overtemperature shutdown threshold of IC              | 180 | 210 | °C   |

| T <sub>PPRT</sub>   | Peak package reflow temperature during reflow [1] [2] | _   | 260 | °C   |

| MSL                 | Moisture Sensitivity Level                            | _   | 3   | _    |

NXP's Package Reflow capability meets Pb-free requirements for JEDEC standard J-STD-020C. For Peak Package Reflow Temperature and Moisture Sensitivity Levels (MSL), contact NXP.

Table 6. Thermal resistance characteristics

| Symbol                   | Description (rating)                           | Min | Max | Unit |

|--------------------------|------------------------------------------------|-----|-----|------|

| Thermal resistance ratin | gs                                             |     |     |      |

| $R_{\theta JA}$          | Junction-to-Ambient thermal resistance [1] [2] | _   | 51  | °C/W |

| $R_{\theta JB}$          | Junction-to-Board thermal resistance [3]       | _   | 34  | °C/W |

Per EIA/JESD51-2A Integrated Circuits Thermal Test Method Environmental Conditions - Natural Convection (Still Air) Per EIA/JESD51-7 High Effective Thermal Conductivity Test Board for Leaded Surface Mount Packages

Pin soldering temperature limit is for 10 seconds maximum duration. Not designed for immersion soldering. Exceeding these limits may cause malfunction or permanent damage to the device.

JEDEC high-K thermal test board without thermal attachment.

### Advanced IGBT/SiC gate driver

# 8.4 Isolation and safety related specifications

Table 7. Insulation specifications

| Symbol      | Description (Rating)                                 |      | Value    | Unit     |

|-------------|------------------------------------------------------|------|----------|----------|

| MGD3160AM51 | 5EK, MGD3160AM535EK, MGD3160AM315EK and MGD3160AM33  | 35EK |          | <u> </u> |

| CLR         | External clearance distance                          | [1]  | > 7.72   | mm       |

| CPG         | External creepage distance                           | [2]  | > 7.72   | mm       |

| DTI         | Internal clearance (Gap) distance through insulation |      | > 80     | μm       |

| СТІ         | Comparative tracking index                           | [3]  | > 400    | V        |

| $M_{Group}$ | Material (isolation) group                           | [4]  | II       | _        |

|             | Installation classification                          | [5]  |          |          |

| IEC150      | Mains voltage ≤ 150 V <sub>RMS</sub>                 |      | I to IV  |          |

| IEC300      | Mains voltage ≤ 300 V <sub>RMS</sub>                 |      | I to III | _        |

| IEC600      | Mains voltage ≤ 600 V <sub>RMS</sub>                 |      | I to II  |          |

| MGD3160AM51 | 8EK, MGD3160AM538EK, MGD3160AM318EK and MGD3160AM33  | 88EK |          | <u>'</u> |

| CLR         | External clearance distance                          | [1]  | > 8.00   | mm       |

| CPG         | External creepage distance                           | [2]  | > 8.00   | mm       |

| DTI         | Internal clearance (Gap) distance through insulation |      | > 80     | μm       |

| CTI         | Comparative tracking index                           | [3]  | > 600    | V        |

| $M_{Group}$ | Material (isolation) group                           | [4]  | 1        | _        |

|             | Installation classification                          | [5]  |          |          |

| IEC150      | Mains voltage ≤ 150 V <sub>RMS</sub>                 |      | I to IV  |          |

| IEC300      | Mains voltage ≤ 300 V <sub>RMS</sub>                 |      | I to III | _        |

| IEC600      | Mains voltage ≤ 600 V <sub>RMS</sub>                 |      | I to II  |          |

per IEC 60950-1 Table 2K

Table 8. DIN V VDE 0884-10 (VDE V 0884-10) insulation characteristics

| Symbol             | Description (Rating)                                              |     | Value             | Units            |

|--------------------|-------------------------------------------------------------------|-----|-------------------|------------------|

| CCLASS             | Climatic classification                                           |     | 40/125/21         | _                |

| PDEGREE            | Pollution degree                                                  |     | 2                 | _                |

| V <sub>IORM</sub>  | Maximum repetitive peak isolation voltage                         |     | 1500              | $V_{pk}$         |

| V <sub>IOWM</sub>  | Maximum working isolation voltage                                 |     | 1060              | V <sub>RMS</sub> |

| V <sub>IOTM</sub>  | Maximum transient isolation voltage                               | [1] | 4000              | $V_{pk}$         |

| V <sub>IOTM</sub>  | Maximum transient isolation voltage                               | [2] | 8000              | $V_{pk}$         |

| V <sub>IOSM</sub>  | Maximum surge isolation voltage                                   | [3] | 10000             | $V_{pk}$         |

| V <sub>PD(m)</sub> | Input to output test voltage 100 % test method B1                 | [4] | 2812              | $V_{pk}$         |

|                    | Input to output test voltage type test method A                   | [5] | 2400              | $V_{pk}$         |

|                    | Input to output test voltage type test subgroups 1 to 3           | [6] | 1800              | $V_{pk}$         |

| C <sub>IO</sub>    | Barrier capacitance, input to output                              |     | < 3               | pF               |

| R <sub>IO</sub>    | Insulation resistance at T <sub>s</sub> , V <sub>IO</sub> = 500 V |     | > 10 <sup>9</sup> | Ω                |

| T <sub>S</sub>     | Maximum junction temperature                                      |     | 150               | °C               |

| Ps                 | Safe total dissipated power                                       |     | 0.38              | W                |

| V <sub>ISO</sub>   | Withstand isolation voltage (1 minute)                            | [7] | 5000              | V <sub>RMS</sub> |

For part numbers MGD3160AM515EK, MGD3160AM535EK, MGD3160AM315EK, and MGD3160AM335EK

per IEC 60950-1 Table 2N

<sup>[1]</sup> [2] [3] [4] [5] per DIN IEC 112/VDE 0303 Part 1

per IEC 60664-1 per IEC 60664-1 Table F.1

For part numbers MGD3160AM518EK, MGD3160AM538EK, MGD3160AM318EK, and MGD3160AM338EK

### Advanced IGBT/SiC gate driver

```

[3] per IEC 60065, 1.2 μ/50 μs waveform

[4] V<sub>ini</sub> = V<sub>IOTM</sub>, t<sub>ini</sub> = 1 s

V<sub>PD(m)</sub> = V<sub>IORM</sub> x 1.875, t<sub>m</sub> = 1 s, Partial discharge < 5pC</li>

[5] V<sub>ini</sub> = V<sub>IOTM</sub>, t<sub>ini</sub> = 60 s

V<sub>PD(m)</sub> = V<sub>IORM</sub> x 1.6, t<sub>m</sub> = 10 s, Partial discharge < 5pC</li>

[7] V<sub>TEST</sub> = V<sub>ISO</sub> = 5000 V<sub>RMS</sub>, t = 60 s (NXP qualification)

V<sub>TEST</sub> = 2500 V<sub>RMS</sub>(4243Vpk), t = 1 s (100 % production) (MGD3160AM515EK, MGD3160AM535EK, MGD3160AM315EK and MGD3160AM335EK)

V<sub>TEST</sub> = 5000 V<sub>RMS</sub>(8500Vpk), t = 1 s (100 % production) (MGD3160AM518EK, MGD3160AM538EK, MGD3160AM318EK and MGD3160AM338EK)

```

The GD3160 uses the same isolation technology as GD3100, but device certification and manufacturing certification are still pending until the device goes into production for the component programs listed in <u>Table 9</u>.

Table 9. Regulatory information

| Standard    | Approval                                                                         |

|-------------|----------------------------------------------------------------------------------|

| UL 1577     | Certified 5.0 kV rms for 1 min single protection, 5.0 kV rms.                    |

| VDE 0884-10 | Tested in accordance with DIN V VDE V 0884-10 reinforced isolation, 1.5 kV peak. |

Advanced IGBT/SiC gate driver

## 9 Electrical characteristics

### 9.1 Power management

#### Table 10. Power management electrical characteristics

VDD, VCC, VCCREG, VEE in regulation,  $T_J$  = -40 to 150 °C, unless otherwise specified. All voltages referenced to GND1 or GND2. Currents are positive into and negative out of the specified pins.

| Symbol                      | Parameter                                                                               |     | Min   | Тур  | Max  | Unit |

|-----------------------------|-----------------------------------------------------------------------------------------|-----|-------|------|------|------|

| Voltage supplies an         | d references - low-voltage domain. Voltages reference to GND1                           |     |       |      |      |      |

| I <sub>VSUP</sub>           | VSUP quiescent current                                                                  | [1] | _     | 5    | 8    | mA   |

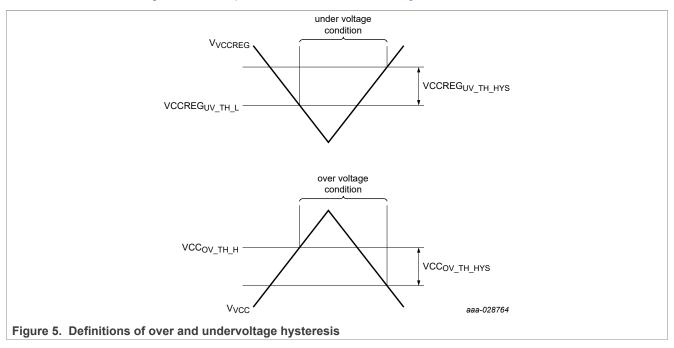

| VSUP <sub>OV_TH_H</sub>     | VSUP overvoltage threshold (rising)                                                     |     | 28    | _    | 32.0 | V    |

| VSUP <sub>OV_TH_HYS</sub>   | VSUP overvoltage threshold hysteresis                                                   |     | 0.25  | _    | 0.75 | V    |

| VSUP <sub>UV_TH_L</sub>     | VSUP undervoltage threshold (falling)                                                   | [2] | 5.5   | _    | 6.5  | V    |

| VSUP <sub>UV_TH_HYS</sub>   | VSUP undervoltage threshold hysteresis                                                  |     | 0.05  | _    | 0.25 | V    |

| VSUP <sub>POR_FALLING</sub> | Low-voltage domain POR condition (falling), POR when VSUP < VSUP <sub>POR_FALLING</sub> | [3] | 2     | _    | _    | V    |

| VSUP <sub>POR_RISING</sub>  | Low-voltage domain POR clear (rising), POR clear when VSUP > VSUP <sub>POR_RISING</sub> | [3] | _     | _    | 3.75 | V    |

| t <sub>VSUP_FILT</sub>      | VSUP over/under voltage fault filter time                                               |     | 32    | 40   | 48   | μs   |

| t <sub>VDD_FLT_FILT</sub>   | VDD over/under voltage fault filter time                                                |     | 16    | 20   | 24   | μs   |

| GD3160 with 3.3 V V         | /DD                                                                                     |     |       |      |      |      |

| V <sub>VDD3p3</sub>         | Output of VDD regulator when powered by VSUP                                            |     | 3.20  | 3.30 | 3.40 | V    |

| VDD <sub>OV_TH_H3p3</sub>   | VDD overvoltage threshold (rising)                                                      |     | 3.60  | 3.75 | 3.90 | V    |

| VDD <sub>OV_TH_HYS3p3</sub> | VDD overvoltage threshold hysteresis                                                    |     | 0.075 | 0.15 | 0.20 | V    |

| VDD <sub>UV_TH_L3p3</sub>   | VDD undervoltage threshold (falling)                                                    |     | 2.56  | 2.73 | 2.92 | V    |

| VDD <sub>UV_TH_HYS3p3</sub> | VDD undervoltage threshold hysteresis                                                   |     | 0.075 | 0.15 | 0.20 | V    |

| GD3160 with 5.0 V V         | /DD <sup>[4]</sup>                                                                      |     |       |      |      |      |

| V <sub>VDD5</sub>           | Output of VDD regulator when powered by VSUP                                            |     | 4.85  | 5.00 | 5.15 | V    |

| VDD <sub>OV_TH_H5</sub>     | VDD overvoltage threshold (rising)                                                      |     | 5.35  | 5.55 | 5.77 | V    |

| VDD <sub>OV_TH_HYS5</sub>   | VDD overvoltage threshold hysteresis                                                    |     | 0.075 | 0.15 | 0.20 | V    |

| VDD <sub>UV_TH_L5</sub>     | VDD undervoltage threshold (falling)                                                    |     | 4.12  | 4.30 | 4.48 | V    |

| VDD <sub>UV_TH_HYS5</sub>   | VDD undervoltage threshold hysteresis                                                   |     | 0.075 | 0.15 | 0.20 | V    |

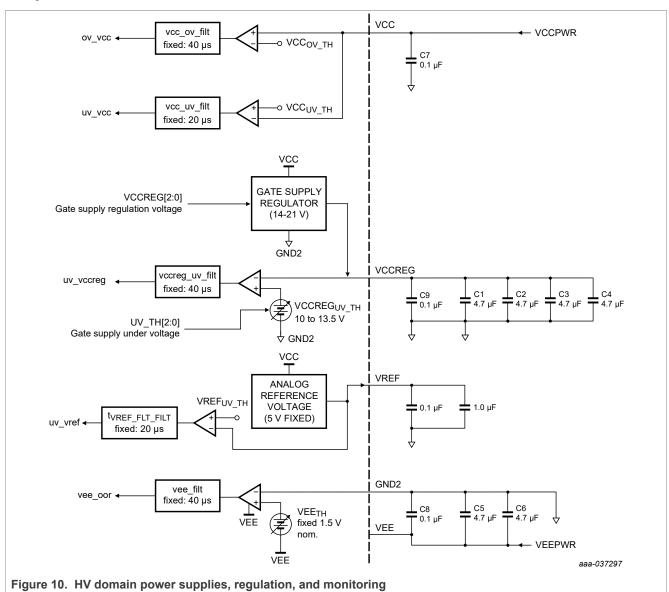

| Voltage supplies ar         | nd references - high-voltage domain. Voltages referenced to GND2                        |     |       |      |      |      |

| VCC <sub>OV_TH_H</sub>      | VCC overvoltage threshold (rising edge)                                                 |     | 23.0  | _    | 25.0 | V    |

| VCC <sub>OV_TH_HYS</sub>    | VCC overvoltage threshold hysteresis                                                    |     | 0.25  | _    | 0.90 | V    |

| t <sub>VCC_OV_FILT</sub>    | VCC overvoltage fault filter time                                                       |     | 32    | 40   | 48   | μs   |

| VCC <sub>UV_TH_L</sub>      | VCC undervoltage threshold (falling edge)                                               |     | 5.5   | _    | 6.5  | V    |

| VCC <sub>UV_TH_HYS</sub>    | VCC undervoltage threshold hysteresis                                                   |     | 0.10  | 0.15 | 0.25 | V    |

| VVCC <sub>POR_FALLING</sub> | High-voltage domain POR condition (falling) POR when VCC < VCC <sub>POR_FALLING</sub>   | [3] | 2     | _    | _    | V    |

| VVCC <sub>POR_RISING</sub>  | High-voltage domain POR clear (rising) ,POR clear when VCC > VCCPOR_RISING              | [3] | _     | _    | 3.75 | V    |

| t <sub>VCC_UV_FILT</sub>    | VCC undervoltage fault filter time                                                      |     | 16    | 20   | 24   | μs   |

| I <sub>VCC</sub>            | VCC quiescent current                                                                   | [5] | 6     | 7.5  | 11   | mA   |

### Advanced IGBT/SiC gate driver

Table 10. Power management electrical characteristics...continued

VDD, VCC, VCCREG, VEE in regulation,  $T_J = -40$  to 150 °C, unless otherwise specified. All voltages referenced to GND1 or GND2. Currents are positive into and negative out of the specified pins.

| Symbol                                                                                                                                                                    | Parameter                                                             | Min    | Тур    | Max   | Unit |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|--------|--------|-------|------|

|                                                                                                                                                                           | VCCREG regulated output voltage, VCCREG[2:0] = '000' (VCC > 15.0 V)   | 13.75  | 14     | 14.28 | V    |

|                                                                                                                                                                           | VCCREG regulated output voltage, VCCREG[2:0] = '001' (VCC > 16.0 V)   | 14.72  | 15     | 15.28 | V    |

|                                                                                                                                                                           | VCCREG regulated output voltage, VCCREG[2:0] = '010' (VCC > 17.0 V)   | 15.7   | 16     | 16.3  | ٧    |

| VCCREGOUT  VCCREGOUT  VCCREGUV_TH_LYS  tvccreg_flt_filt  Vvref  Vvref_tvar  VREFUV_TH_LYS  tvref_flt_filt  Ivee  VEEOOR_TH  tvee_flt_filt  Current limits and r  Ivdd_lim | VCCREG regulated output voltage, VCCREG[2:0] = '011' (VCC > 18.0 V)   | 16.67  | 17     | 17.33 | V    |

| VCCREGOUT                                                                                                                                                                 | VCCREG regulated output voltage, VCCREG[2:0] = '100' (VCC > 19.0 V)   | 17.64  | 18     | 18.36 | V    |

|                                                                                                                                                                           | VCCREG regulated output voltage, VCCREG[2:0] = '101' (VCC > 20.0 V)   | 18.62  | 19     | 19.38 | V    |

|                                                                                                                                                                           | VCCREG regulated output voltage, VCCREG[2:0] = '110' (VCC > 21.0 V)   | 19.6   | 20     | 20.4  | V    |

| Symbol  VCCREGOUT  VCCREGOUT  VCCREGUV_TH_L  VCCREG_IT_FILT  VVREF  VVREF_TVAR  VREF_UV_TH_L  VREF_UV_TH_L  VREF_UV_TH_L  VEE  VEEOOR_TH  Current limits and recommended. | VCCREG regulated output voltage, VCCREG[2:0] = '111' (VCC > 22.0 V)   | 20.57  | 21     | 21.43 | V    |

| VCCREG <sub>DO</sub>                                                                                                                                                      | VCCREG dropout voltage [6]                                            | _      | _      | 0.5   | V    |

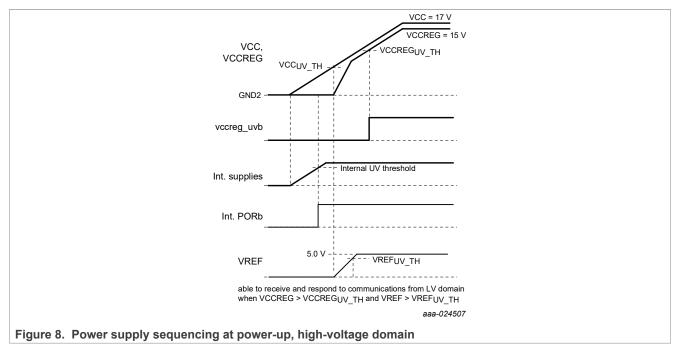

|                                                                                                                                                                           | VCCREG undervoltage threshold (falling edge), UV_TH = '000'           | 9.50   | 10.00  | 10.50 | V    |

|                                                                                                                                                                           | VCCREG undervoltage threshold (falling edge), UV_TH = '001'           | 9.98   | 10.50  | 11.03 | V    |

|                                                                                                                                                                           | VCCREG undervoltage threshold (falling edge), UV_TH = '010'           | 10.45  | 11.00  | 11.55 | V    |

| VOODEO                                                                                                                                                                    | VCCREG undervoltage threshold (falling edge), UV_TH = '011' (default) | 10.93  | 11.50  | 12.08 | V    |

| VCCREG <sub>UV_TH_L</sub>                                                                                                                                                 | VCCREG undervoltage threshold (falling edge), UV_TH = '100'           | 11.40  | 12.00  | 12.60 | V    |

|                                                                                                                                                                           | VCCREG undervoltage threshold (falling edge), UV_TH = '101'           | 11.88  | 12.50  | 13.13 | V    |

|                                                                                                                                                                           | VCCREG undervoltage threshold (falling edge), UV_TH = '110'           | 12.35  | 13.00  | 13.65 | V    |

|                                                                                                                                                                           | VCCREG undervoltage threshold (falling edge), UV_TH = '111'           | 12.83  | 13.50  | 14.18 | V    |

| VCCREG <sub>UV_TH_HYS</sub>                                                                                                                                               | VCCREG undervoltage threshold hysteresis                              | 0.05   | 0.15   | 0.230 | V    |

| t <sub>VCCREG_FLT_FILT</sub>                                                                                                                                              | VCCREG undervoltage fault filter time                                 | 32     | 40     | 48    | μs   |

| $V_{VREF}$                                                                                                                                                                | VREF regulated voltage [7]                                            | 4.938  | 5.00   | 5.079 | V    |

| V <sub>VREF_TVAR</sub>                                                                                                                                                    | VREF variation with temperature [8] [3]                               | -15    | _      | 15    | mV   |

| VREF <sub>UV_TH_L</sub>                                                                                                                                                   | VREF undervoltage threshold (falling)                                 | 4.12   | 4.30   | 4.49  | V    |

| VREF <sub>UV_TH_HYS</sub>                                                                                                                                                 | VREF undervoltage threshold hysteresis                                | 0.10   | 0.15   | 0.225 | ٧    |

| t <sub>VREF_FLT_FILT</sub>                                                                                                                                                | VREF UV fault filter time                                             | 16     | 20     | 24    | μs   |

| I <sub>VEE</sub>                                                                                                                                                          | VEE quiescent current [9]                                             | -0.850 | -0.045 | -0.2  | mA   |

| VEE <sub>OOR_TH</sub>                                                                                                                                                     | VEE out of range                                                      | -2.0   | -1.5   | -1.0  | V    |

|                                                                                                                                                                           | VEE out of range fault filter time                                    | 32     | 40     | 48    | μs   |

| Current limits and re                                                                                                                                                     | ferences                                                              |        |        |       |      |

| I <sub>VDD_LIM</sub>                                                                                                                                                      | Current limit of VDD regulator                                        | -60    | -30    | -20   | mA   |

| I <sub>VREF_LIM</sub>                                                                                                                                                     | Current limit of VREF regulator                                       | -60    | _      | -20   | mA   |

| I <sub>VCCREG_LIM</sub>                                                                                                                                                   | Current limit of VCCREG regulator                                     | -1500  | -1100  | -800  | mA   |

- VSUP = 14 V, IGBT off

- [1] [2] [3] [4] [5] [6] Valid for MGD3160AM5xxEK only (VDD option = 5 V)

- Guaranteed by design

- When VDD is externally supplied, the applied voltage must be 4.75 to 5.25 V. VCC = 17 V, I<sub>VREF</sub> = 0 mA, IGBT off

- VCC = 17 V,  $I_{VREF}$  = 0 mA, IGB1 on VCC < 15 V,  $I_{VCCREG}$  = 100 mA VCCREG > VCCREGUV\_TH,  $I_{VREF}$  = 0 to 20 mA  $I_{VCCREG}$  = 0 to 150 °C,  $I_{VREF}$  = 1.0 mA VEE = -8.0 V,  $I_{VREF}$  = 0 mA, IGB1 off [7]

- [8]

### 9.2 Digital inputs and outputs

Table 11 and Table 12 specify characteristics of the low-voltage digital I/O pins. Table 13 specifies the FSISO digital input pin on the high-voltage (HV) domain.

## Advanced IGBT/SiC gate driver

Table 11. Low-voltage digital I/O electrical characteristics

VDD, VCC, VCCREG, VEE in regulation,  $T_J$  = -40 °C to +150 °C, unless otherwise specified. All voltages referenced to GND1. Currents are positive into and negative out of the specified pins.

| Symbol                  | Parameter                                                                                  |         | Min        | Тур        | Max        | Unit |

|-------------------------|--------------------------------------------------------------------------------------------|---------|------------|------------|------------|------|

| V <sub>INL</sub>        | Logic low input voltage                                                                    | [1]     | _          | _          | 0.30 x VDD | V    |

| V <sub>INH</sub>        | Logic high input voltage                                                                   | [1]     | 0.70 x VDD | _          | _          | V    |

| V <sub>INhys</sub>      | Input voltage threshold hysteresis                                                         | [1]     | 0.20 x VDD | 0.25 x VDD | 0.30 x VDD | V    |

| INPU <sub>LK</sub>      | Input leakage for pins with pullup resistor pins: CSB, PWMALT                              | [2] [3] | _          | _          | 4.0        | μA   |

| INPD <sub>LK</sub>      | Input leakage for pins with pulldown resistor pins: MOSI, SCLK, PWM, FSSTATE, FSENB, FSISO | [3] [4] | -1.0       | _          | _          | μA   |

| C <sub>IN</sub>         | Input capacitance, logic pins                                                              | [3]     | _          | _          | 10         | pF   |

| V <sub>OL</sub>         | Logic low output voltage                                                                   | [5]     | _          | _          | 0.2 x VDD  | V    |

| V <sub>OLINT</sub>      | Logic low output voltage for open-drain interrupts                                         | [6]     | _          | _          | 0.2 x VDD  | V    |

| V <sub>OH</sub>         | Logic high output voltage                                                                  | [7]     | 0.8 x VDD  | _          | _          | V    |

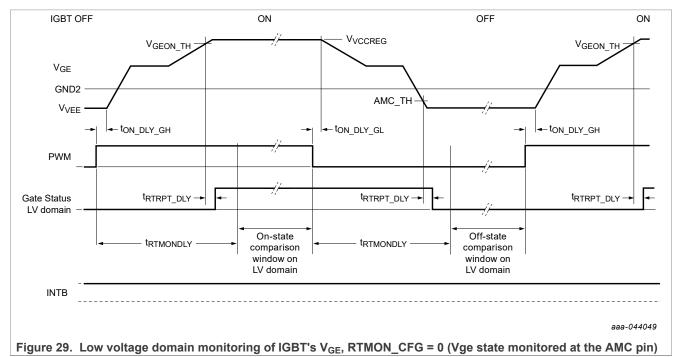

| t <sub>RTRPT_DLY</sub>  | Real time reporting delay                                                                  |         | 200        | 220        | 240        | ns   |

| t <sub>MIN</sub>        | Input pulse deglitch                                                                       | [8]     | 34         | _          | 67         | ns   |

| t <sub>fltdly</sub>     | Event detection delay to INTA or INTB low                                                  |         | _          | 1.28       | 1.6        | μs   |

| t <sub>onmin</sub>      | Minimum on pulse width (PWM)                                                               | [9]     | _          | _          | 220        | ns   |

| t <sub>offmin</sub>     | Minimum off pulse width (PWM)                                                              | [9]     | _          | _          | 220        | ns   |

| R <sub>PU</sub>         | Pullup resistor for CSB, INTB, INTA                                                        |         | 30         | 50         | 75         | kΩ   |

| R <sub>PU_PWMALT</sub>  | Pullup resistor for PWMALT                                                                 |         | 300        | 500        | 750        | kΩ   |

| R <sub>PD</sub>         | Pulldown resistor FSSTATE, FSENB, PWM, SCLK, MOSI                                          |         | 30         | 50         | 75         | kΩ   |

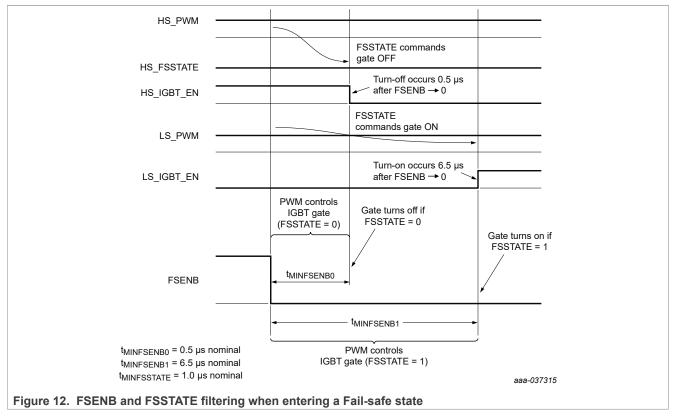

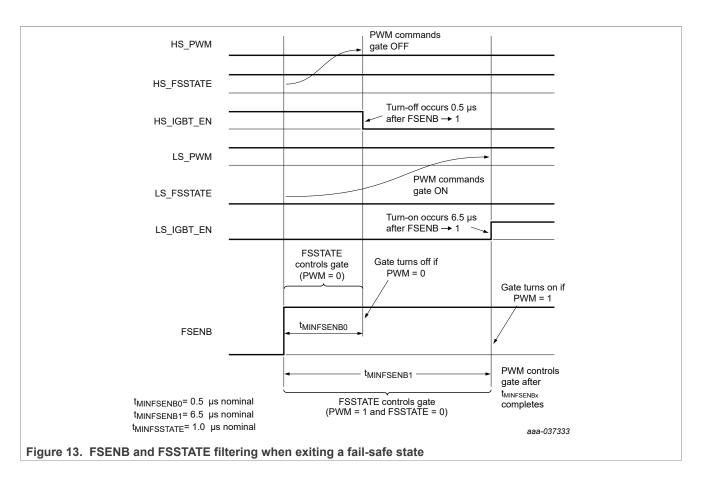

| t <sub>MINFSSTATE</sub> | FSSTATE input pulse deglitch                                                               |         | 931        | 1000       | 1071       | ns   |

| t <sub>MINFSENB0</sub>  | FSENB input pulse deglitch (FSSTATE = 0 or PWM = 0)                                        |         | 0.465      | 0.5        | 0.536      | μs   |

| t <sub>MINFSENB1</sub>  | FSENB input pulse deglitch (FSSTATE = 1 or PWM = 1)                                        |         | 5.995      | 6.5        | 7.025      | μs   |

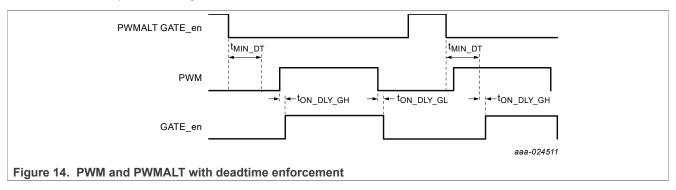

|                         | PWM deadtime, DEADT = '0000'                                                               |         | 0.081      | 0.1        | 0.198      | μs   |

|                         | PWM deadtime, DEADT = '0001'                                                               |         | 0.12       | 0.14       | 0.239      | μs   |

|                         | PWM deadtime, DEADT = '0010'                                                               |         | 0.217      | 0.24       | 0.342      | μs   |

|                         | PWM deadtime, DEADT = '0011'                                                               |         | 0.372      | 0.4        | 0.507      | μs   |

|                         | PWM deadtime, DEADT = '0100'                                                               |         | 0.508      | 0.54       | 0.651      | μs   |

|                         | PWM deadtime, DEADT = '0101'                                                               |         | 0.741      | 0.78       | 0.898      | μs   |

|                         | PWM deadtime, DEADT = '0110'                                                               |         | 0.993      | 1.04       | 1.166      | μs   |

| t <sub>MIN DT</sub>     | PWM deadtime, DEADT = '0111'                                                               |         | 1.226      | 1.28       | 1.413      | μs   |

| $(TIME_2 = 1)^{[10]}$   | PWM deadtime, DEADT = '1000'                                                               |         | 1.478      | 1.54       | 1.681      | μs   |

|                         | PWM deadtime, DEADT = '1001'                                                               |         | 1.711      | 1.78       | 1.928      | μs   |

|                         | PWM deadtime, DEADT = '1010'                                                               |         | 1.963      | 2.04       | 2.196      | μs   |

|                         | PWM deadtime, DEADT = '1011'                                                               |         | 2.196      | 2.28       | 2.443      | μs   |

|                         | PWM deadtime, DEADT = '1100'                                                               |         | 2.448      | 2.54       | 2.711      | μs   |

|                         | PWM deadtime, DEADT = '1101'                                                               |         | 2.681      | 2.78       | 2.958      | μs   |

|                         | PWM deadtime, DEADT = '1110'                                                               |         | 2.933      | 3.04       | 3.226      | μs   |

|                         | PWM deadtime, DEADT = '1111' (default)                                                     |         | 3.132      | 3.28       | 3.406      | μs   |

### Advanced IGBT/SiC gate driver

Table 11. Low-voltage digital I/O electrical characteristics...continued

$VDD,\ VCC,\ VCCREG,\ VEE\ in\ regulation,\ T_J = -40\ ^{\circ}C\ to\ +150\ ^{\circ}C,\ unless\ otherwise\ specified.\ All\ voltages\ referenced\ to\ GND1.\ Currents\ are$ positive into and negative out of the specified pins.

| Symbol              | Parameter                     | Min   | Тур  | Max   | Unit |

|---------------------|-------------------------------|-------|------|-------|------|

|                     | PWM deadtime, DEADT = '0000', | 0.128 | 0.16 | 0.329 | μs   |

|                     | PWM deadtime, DEADT = '0001'  | 0.206 | 0.24 | 0.411 | μs   |

|                     | PWM deadtime, DEADT = '0010'  | 0.4   | 0.44 | 0.617 | μs   |

|                     | PWM deadtime, DEADT = '0011'  | 0.71  | 0.76 | 0.947 | μs   |

|                     | PWM deadtime, DEADT = '0100'  | 0.982 | 1.04 | 1.235 | μs   |

|                     | PWM deadtime, DEADT = '0101'  | 1.448 | 1.52 | 1.729 | μs   |

|                     | PWM deadtime, DEADT = '0110'  | 1.952 | 2.04 | 2.265 | μs   |

| t <sub>MIN_DT</sub> | PWM deadtime, DEADT = '0111'  | 2.418 | 2.52 | 2.759 | μs   |

| $(TIME_2 = 0)$      | PWM deadtime, DEADT = '1000'  | 2.922 | 3.04 | 3.295 | μs   |

|                     | PWM deadtime, DEADT = '1001'  | 3.388 | 3.52 | 3.789 | μs   |

|                     | PWM deadtime, DEADT = '1010'  | 3.892 | 4.04 | 4.325 | μs   |

|                     | PWM deadtime, DEADT = '1011'  | 4.358 | 4.52 | 4.819 | μs   |

|                     | PWM deadtime, DEADT = '1100'  | 4.862 | 5.04 | 5.355 | μs   |

|                     | PWM deadtime, DEADT = '1101'  | 5.328 | 5.52 | 5.849 | μs   |

|                     | PWM deadtime, DEADT = '1110'  | 5.832 | 6.04 | 6.385 | μs   |

|                     | PWM deadtime, DEADT = '1111'  | 6.298 | 6.52 | 6.879 | μs   |

- Pins: FSSTATE, FSENB, PWM, PWMALT, SCLK, CSB, MOSI [1]

- [2] [3] [4] [5] [6] CSB, PWMALT connected to VDD

- Guaranteed by design

- MOSI, SCLK, PWM, FSSTATE, FSENB connected to GND1; FSISO connected to GND2 Pins: MISO, AOUT, INTA (when RTRPT = 1), I = 3.0 mA

- Pins: INTB, INTA (when RTRPT = 0), I = 10 mA

- [7] [8] Pins: MISO, AOUT, INTA (when RTRPT = 1), I = -2.0 mA

- Pins: PWM, PWMALT

- C<sub>Load</sub> = 2 nF, guaranteed by design

- [10] TIME\_2\_is Timer scaling bit of MODE1 register

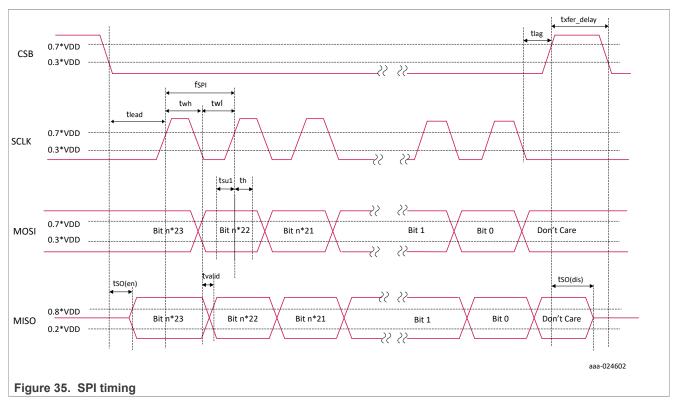

Table 12. SPI timing

VDD, VCC, VCCREG, VEE in regulation,  $T_J = -40$  to +150 °C, unless otherwise specified. All voltages referenced to GND1. Currents are positive into and negative out of the specified pins.

| Symbol               | Parameter                                                        |         | I   | Limit value | 9   | Unit |

|----------------------|------------------------------------------------------------------|---------|-----|-------------|-----|------|

| Symbol               | Parameter                                                        |         | Min | Тур         | Max | Unit |

| f <sub>SPI</sub>     | Frequency of SPI operation                                       | [1] [2] | _   | _           | 10  | MHz  |

| t <sub>lead</sub>    | Falling edge of CSB to rising edge of SCLK (required setup time) | [2]     | 50  | _           | _   | ns   |

| t <sub>lag</sub>     | Falling edge of SCLK to rising edge of CSB (required setup time) | [2]     | 50  | _           | _   | ns   |

| t <sub>wh</sub>      | High time of SCLK                                                | [2]     | 45  | _           | _   | ns   |

| t <sub>wl</sub>      | Low time of SCLK                                                 | [2]     | 45  | _           | _   | ns   |

| t <sub>su1</sub>     | MOSI to rising edge of SCLK (required setup time)                | [2]     | 15  | _           | _   | ns   |

| t <sub>h</sub>       | MOSI to rising edge of SCLK (required hold time)                 | [2]     | 15  | _           | _   | ns   |

| t <sub>SO(en)</sub>  | Time from falling edge of CSB to MISO low impedance              | [2]     | _   | _           | 30  | ns   |

| t <sub>SO(dis)</sub> | Time from Rising Edge of CSB to MISO high Impedance              | [2]     | _   | _           | 30  | ns   |

| t <sub>valid</sub>   | Time from falling edge of SCLK to MISO data valid                | [3] [2] | _   | _           | 30  | ns   |

GD3160

### Advanced IGBT/SiC gate driver

Table 12. SPI timing...continued

VDD, VCC, VCCREG, VEE in regulation,  $T_J = -40$  to +150 °C, unless otherwise specified. All voltages referenced to GND1. Currents are positive into and negative out of the specified pins.

| Symbol                  | Parameter                | ı   | imit value | •   | Unit  |

|-------------------------|--------------------------|-----|------------|-----|-------|

|                         | raianietei               | Min | Тур        | Max | Oilit |

| t <sub>xfer_delay</sub> | Minimum message deadtime | 19  | _          | _   | μs    |

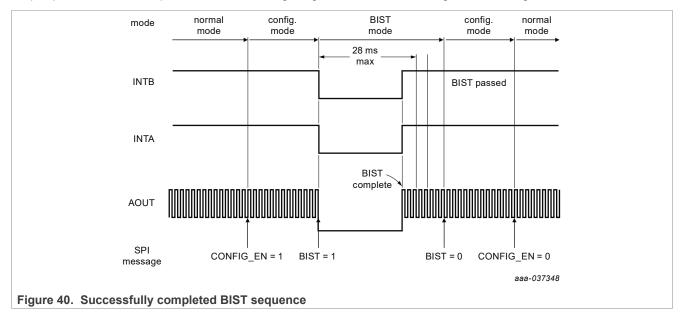

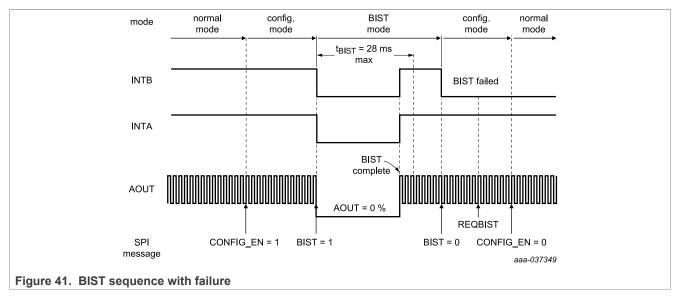

| t <sub>BIST</sub>       | BIST duration            | _   | _          | 28  | ms    |

#### Table 13. FSISO pin electrical characteristics

VCC, VCCREG in regulation, T<sub>J</sub> = -40 °C to +150 °C, unless otherwise specified. All voltages referenced to GND2. Currents are positive into and negative out of the specified pins.

| Symbol                | Parameter                                    | Min         | Тур         | Max         | Unit |

|-----------------------|----------------------------------------------|-------------|-------------|-------------|------|

| V <sub>FSISOL</sub>   | FSISO logic low input voltage [1]            | _           | _           | 0.3 x VREF  | V    |

| V <sub>FSISOH</sub>   | FSISO logic high input voltage [1]           | 0.7 x VREF  | _           | 1.05 x VREF | V    |

| V <sub>FSISOhys</sub> | FSISO input voltage threshold hysteresis [1] | 0.20 x VREF | 0.25 x VREF | 0.32 x VREF | V    |

| C <sub>FSISOIN</sub>  | FSISO input capacitance [2]                  | _           | _           | 10          | pF   |

| R <sub>FSISOPD</sub>  | FSISO pulldown resistor                      | 30          | 60          | 100         | kΩ   |

| t <sub>FSISOMIN</sub> | FSISO input pulse deglitch                   | 500         | 750         | 1100        | ns   |

Reference = GND2

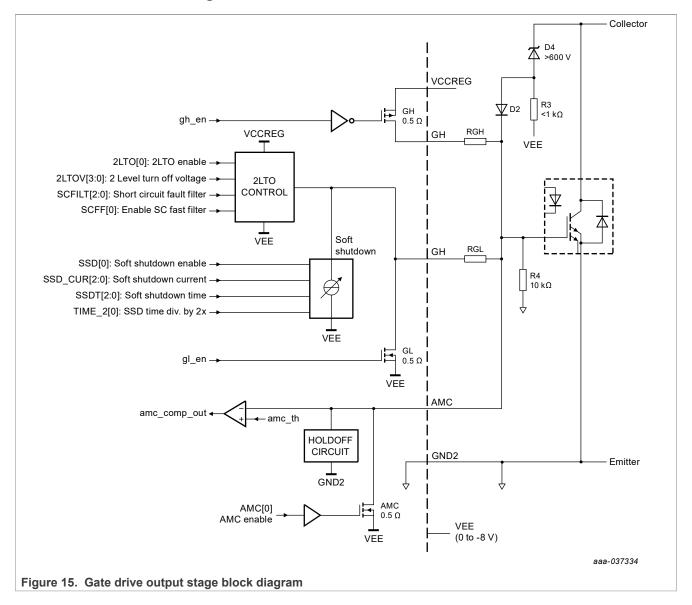

## 9.3 Gate drive outputs

#### Table 14. Gate drive output stage electrical characteristics

VDD, VCC, VCCREG, VEE in regulation, T<sub>J</sub> = −40 to 150 °C, unless otherwise specified. All voltages referenced to GND2. Currents are positive into and negative out of the specified pins.

| Symbol                 | Parameter                                         |     | Min  | Тур  | Max | Unit |

|------------------------|---------------------------------------------------|-----|------|------|-----|------|

| Static electrica       | l ratings                                         |     |      |      |     |      |

| RDSON <sub>GH</sub>    | Gate drive pullup transistor GH on-resistance     | [1] | _    | _    | 800 | mΩ   |

| RDSON <sub>GL</sub>    | Gate drive pulldown transistor GL on-resistance   | [1] | _    | _    | 500 | mΩ   |

| RDSON <sub>AMC</sub>   | Gate drive pulldown transistor AMC on-resistance  | [1] | _    | _    | 500 | mΩ   |

| I <sub>DSS_GH</sub>    | Gate drive pullup transistor saturation current   | [2] | 14.0 | 19.0 | _   | Α    |

| I <sub>DSS_GL</sub>    | Gate drive pulldown transistor saturation current | [3] | 14.0 | 19.0 | _   | Α    |

| I <sub>DSS_AMC</sub>   | Active Miller clamp transistor saturation current | [3] | 14.0 | 19.0 | _   | Α    |

| I <sub>LEAKGH</sub>    | GH leakage current                                | [2] | -10  | _    | _   | μA   |

| I <sub>LEAKGL</sub>    | GL leakage current                                | [3] | _    | _    | 150 | μA   |

| I <sub>LEAKAMC</sub>   | AMC leakage current                               | [4] | _    | _    | 30  | μA   |

| Switching and          | delay timing                                      |     |      |      |     |      |

| t <sub>ON_DLY_GH</sub> | PWM to GH turn-on delay                           | [5] | 75   | _    | 125 | ns   |

| t <sub>ON_GH</sub>     | PWM to GH turn on time                            | [6] | 100  | _    | 150 | ns   |

| t <sub>ON_DLY_GL</sub> | PWM to GL turn on delay                           | [7] | 75   | _    | 125 | ns   |

| t <sub>ON_GL</sub>     | PWM to GL turn on time                            | [8] | 100  | _    | 150 | ns   |

| t                      | PWM to output pulse delay distortion              | [9] |      |      |     | ns   |

| t <sub>pd_dist</sub>   | ton_dly_gh = ton_dly_gl                           |     | -32  | _    | 32  | 113  |

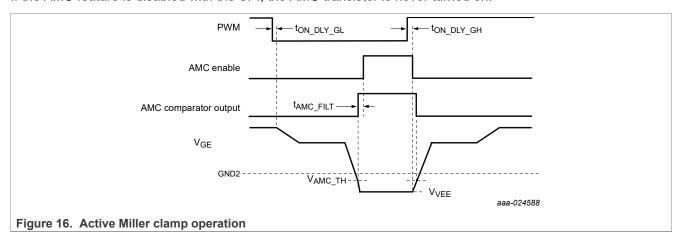

| t <sub>AMC_FILT</sub>  | AMC turn on filter time                           |     | 170  | 180  | 220 | ns   |

GD3160

All information provided in this document is subject to legal disclaimers.

© 2024 NXP B.V. All rights reserved.

T<sub>SPI</sub> = 1/f<sub>SPI</sub> Guaranteed by design

$<sup>0.2 \</sup>text{ x V}_{DD} \le \text{MISO} \le 0.8 \text{ x V}_{DD}, \text{ CL} = 50 \text{ pF}$

Guaranteed by design

## Advanced IGBT/SiC gate driver

Table 14. Gate drive output stage electrical characteristics...continued

VDD, VCC, VCCREG, VEE in regulation,  $T_J$  = -40 to 150 °C, unless otherwise specified. All voltages referenced to GND2. Currents are positive into and negative out of the specified pins.

| Symbol                | Parameter                                                 |      | Min  | Тур  | Max  | Unit |

|-----------------------|-----------------------------------------------------------|------|------|------|------|------|

| Gate voltage mor      | nitor                                                     |      |      |      |      |      |

| V <sub>GEON_TH</sub>  | V <sub>GE</sub> monitor threshold high                    | [10] | -2.3 | -2.0 | -1.7 | V    |

| V <sub>AMC_TH</sub>   | Active Miller clamp threshold voltage (referenced to VEE) | [11] | 1.7  | _    | 2.3  | V    |

| V <sub>GOFF</sub>     | Unpowered gate clamp voltage of holdoff circuit           | [12] | _    | _    | 3.0  | V    |

|                       | PWM monitor delay time, RTMONDLY = '0000'                 |      | _    | _    | _    | ns   |

|                       | PWM monitor delay time, RTMONDLY = '0001'                 |      | _    | _    | _    | ns   |

|                       | PWM monitor delay time, RTMONDLY = '0010'                 |      | 383  | 400  | 512  | ns   |

|                       | PWM monitor delay time, RTMONDLY = '0011'                 |      | 577  | 600  | 718  | ns   |

|                       | PWM monitor delay time, RTMONDLY = '0100'                 |      | 771  | 800  | 924  | ns   |

|                       | PWM monitor delay time, RTMONDLY = '0101'                 |      | 965  | 1000 | 1130 | ns   |

|                       | PWM monitor delay time, RTMONDLY = '0110'                 |      | 1159 | 1200 | 1336 | ns   |

| t <sub>RTMONDLY</sub> | PWM monitor delay time, RTMONDLY = '0111'                 |      | 1353 | 1400 | 1542 | ns   |

| $(TIME_2 = 1)^{[13]}$ | PWM monitor delay time, RTMONDLY = '1000'                 |      | 1547 | 1600 | 1748 | ns   |

|                       | PWM monitor delay time, RTMONDLY = '1001'                 |      | 1741 | 1800 | 1954 | ns   |

|                       | PWM monitor delay time, RTMONDLY = '1010' (default)       |      | 1935 | 2000 | 2160 | ns   |

|                       | PWM monitor delay time, RTMONDLY = '1011'                 |      | 2323 | 2400 | 2572 | ns   |

|                       | PWM monitor delay time, RTMONDLY = '1100'                 |      | 2711 | 2800 | 2984 | ns   |

|                       | PWM monitor delay time, RTMONDLY = '1101'                 |      | 3099 | 3200 | 3396 | ns   |

|                       | PWM monitor delay time, RTMONDLY = '1110'                 |      | 3487 | 3600 | 3808 | ns   |

|                       | PWM monitor delay time, RTMONDLY = '1111'                 |      | 3875 | 4000 | 4220 | ns   |

|                       | PWM monitor delay time, RTMONDLY = '0000'                 |      | _    | _    | _    | ns   |

|                       | PWM monitor delay time, RTMONDLY = '0001'                 |      | 378  | 400  | 464  | ns   |

|                       | PWM monitor delay time, RTMONDLY = '0010'                 |      | 766  | 800  | 1024 | ns   |