# Converting Projects for ColdFire V1 to CodeWarrior Microcontrollers 6.3

This document contains following topics:

- Terms and Abbreviations

- Libraries

- Access Include Paths D:\Projects

- Librarian

- Parameter Calling Convention

- Assembly Function Declarations and Definitions

- EWL Memory Allocation Scheme

- Additional Information

## **Terms and Abbreviations**

The following terms and abbreviations are used in this document:

- MSL Main Standard Libraries

- EWL Embedded Warrior Libraries

- MCU 6.2 Refers to CodeWarrior Development Studio for Microcontrollers, Version 6.2

- MCU 6.3 Refers to CodeWarrior Development Studio for Microcontrollers, Version 6.3

## Libraries

Embedded Warrior Libraries (EWL) introduces a new library set aiming at reducing the memory footprint taken by IO operations and introduces a simpler memory allocator. The IO operations are divided in three categories: printing, scanning and file operations.

The printing and scanning formatters for EWL are grouped in an effort to provide only the support required for the application:

```

int - integer and string processing

int_FP - integer, string and floating point

int_LL - integer (including long long) and string

int_FP_LL - all but wide chars

c9x - all including wide char

```

The buffered IO can be replaced by raw IO, this works solely when printf and scanf are used to perform IO, all buffering is bypassed and writing direct to the device is used. EWL libraries contain prebuilt versions for all formatters and IO modes. Selecting a model combination enables correct compiling and linking. The EWL layout for ColdFire is built per core architecture. It is composed of:

```

libm.a - math support (c9x or not)

libc.a - non c9x std C libs

libc99.a - c9x libs

librt.a - runtime libraries

libc++.a - non-c9x matching c++ libraries

libstdc++.a - c9x/c++ compliant libs

fp coldfire.a - FPU emulation libraries

```

Selecting an EWL model for the libraries frees the user from adding libraries to the project, the linker will determine from the settings the correct library set, these settings are: processor, pid/pic, hard/soft FPU. The process of selecting a model is explained in the Librarian section below. Although the library names are known to the toolset their location is not.

## **Access Include Paths D:\Projects**

The "System Access Paths" point to code in MSL. These have to be changed to point to EWL. The new system access paths are (compiler relative & recursive).

```

{Compiler}\ColdFire_Support\ewl\EWL_C

{Compiler}\ColdFire_Support\ewl\EWL_C++

{Compiler}\ColdFire_Support\ewl\EWL_Runtime

{Compiler}\ColdFire_Support\ewl\lib

```

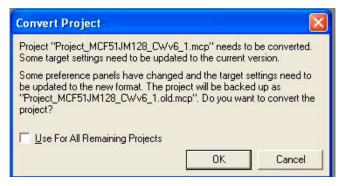

**NOTE** These access path changes are done automatically during Project conversion by the IDE, when opening a project that was built using MCU 6.2.

Figure 1.1 Converter Message

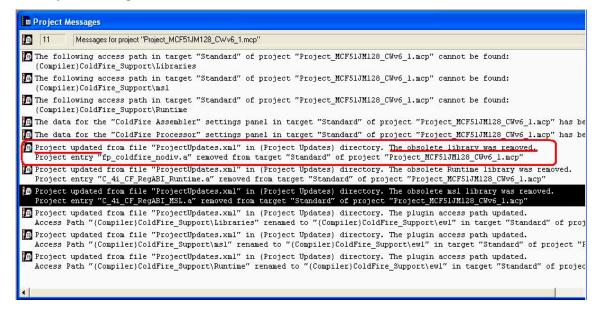

**NOTE** When opening a MCU 6.2 project, with target CF v1, using MCU 6.3 after conversion there are some messages that the obsolete library was removed.

Figure 1.2 Project Messages

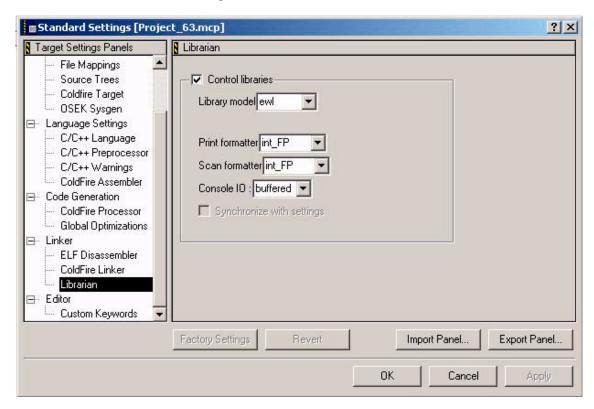

## Librarian

The Librarian panel allows the user to select a "Library model" from a pre-defined list of available models. The lists of available models are:

```

"ewl"

"ewl_c++"

"c9x"

```

"c9x\_c++"

The "ewl" and "ewl\_c++" have a smaller memory footprint, while the "c9x" and "c9x\_c++" models are fully C99 compliant. The "ewl' and "ewl\_c++" models have relevant sub-models that allow the user to pick the desired print and scan formatters and the desired IO scheme. The "c9x" and "c9x\_c++" models do not have sub-models.

Figure 1.3 Console External RAM Settings - Librarian

For the print and scan sub-models the available choices and the functionality that they cover are listed in the "Libraries" section above.

When choosing the "c9x" or the "c9x\_c++" models, the sub-model drop-downs are disabled, as they do not apply to these models.

The "Control libraries" check-box, determines whether or not the EWL mechanism of library selection will be used by the build tools (compiler and linker). When this check-box is not selected, the user has to manually add the required library files to the project.

The user can select the relevant library files by choosing the correct architecture (CF v1) and whether or not FPU and PIC/PID is used.

**NOTE** When opening a MCU 6.2 project, with target CF v1, using MCU 6.3 the converter, chooses the "ewl" model with the print and scan formatter set to "int FP" and "Console IO" set to "buffered".

# **Parameter Calling Convention**

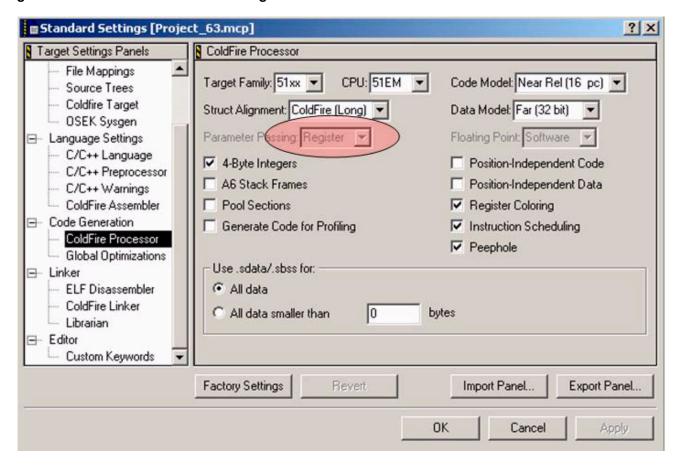

The parameter passing affects space and time performance. The best performance for both occurs when selecting the register passing ABI. The default parameter passing convention is Register, and it can not be changed from the "ColdFire Processor" panel.

Figure 1.4 Console External RAM Settings - ColdFire Processor

**NOTE** When using the MCU 6.3 product the "Parameter Passing" drop down, in the "ColdFire Processor" panel is disabled and fixed to "Register".

Other calling conventions are available through one of the following methods:

}

# **Assembly Function Declarations and Definitions**

For all functions in the application that are pure assembly functions, the function definition and declaration(s) should contain a "declspec" qualifier that defines the parameter passing convention. For example,

```

asm void __declspec(register_abi) TrapHandler_printf(void) Without this declspec, following warning appears.

```

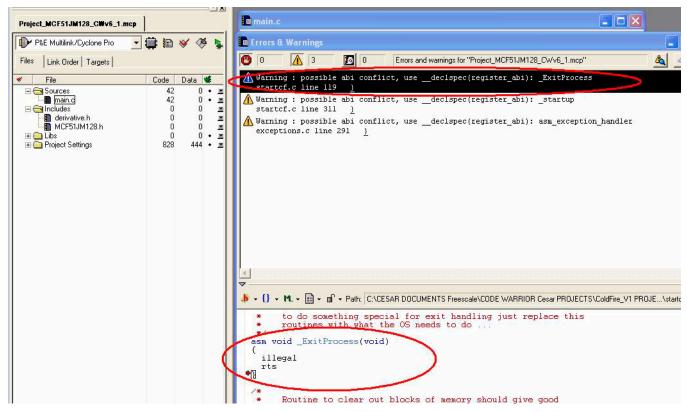

**WARNING!** "possible abi conflict, use \_\_declspec(register\_abi):" generated by the compiler for all such assembly only functions.

Figure 1.5 Asm function warning if the declaration (definition) doesn't contain "declspec" qualifier

Please note while converting CF v1 projects for MCU 6.2 to MCU 6.3 the user has to modify their code such that the assembly functions contain the "\_\_\_declspec" qualifier. Also if the function contains code that assumes a different calling convention, and is called from a "C" function, for example,

```

asm void mcf5xxx_wr_vbr(unsigned long) { /* Set VBR */

move.14(SP),D0

movec d0,VBR

nop

rts

}

```

The code should be modified to use the "Register" parameter passing convention. In this example, the line move. 14 (SP), D0 must be removed.

# **EWL Memory Allocation Scheme**

EWL supports an improved memory allocation scheme. The memory allocation scheme in EWL requires the following symbols to be defined in the LCF file: \_\_\_mem\_limit and \_\_\_stack\_safety. \_\_stack\_safety is the size of the cushion between the stack and the heap.

# **Technical Note**

**TN270**

In the example below, it is set to 16 bytes, which is typical.

These symbols can be added to the LCF file right after the definition of \_\_\_\_HEAP\_END.

## **Additional Information**

See the CodeWarrior Development Studio for Microcontroller Architectures 6.3 Release Notes and documentation for more information.

Visit http://www.freescale.com/support for additional assistance.

#### How to Reach Us:

#### Home Page:

www.freescale.com

#### E-mail:

support@freescale.com

### **USA/Europe or Locations Not Listed:**

Freescale Semiconductor Technical Information Center, CH370 1300 N. Alma School Road Chandler, Arizona 85224 +1-800-521-6274 or +1-480-768-2130 support@freescale.com

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) support@freescale.com

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064, Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor Hong Kong Ltd. Technical Information Center 2 Dai King Street Tai Po Industrial Estate Tai Po, N.T., Hong Kong +800 2666 8080 support.asia@freescale.com

## For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center P.O. Box 5405

Denver, Colorado 80217

1-800-521-6274 or 303-675-2140

Fax: 303-675-2150

LDCForFreescaleSemiconductor@hibbertgroup.com

Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale, the Freescale logo, CodeWarrior and ColdFire are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. Flexis and Processor Expert are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners.

© 2010 Freescale Semiconductor, Inc. All rights reserved.

Document Number: TN270 Rev. B