# **AN5238**

# FS6500 and FS4500 safe system basis chip hardware design and product guidelines

Rev. 10 — 27 August 2024

**Application note**

### **Document information**

| Information | Content                                                                                                                                                                             |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Keywords    | FS6500, FS4500, ASIL B, ASIL D, CAN FD, LIN                                                                                                                                         |

| Abstract    | This application note provides design guidelines for integrating the FS6500 and FS4500 system basis chip (SBC) family of devices into automotive and industrial electronic systems. |

FS6500 and FS4500 safe system basis chip hardware design and product guidelines

# 1 Introduction

This application note provides design guidelines for integrating the FS6500 and FS4500 system basis chip (SBC) family of devices into automotive and industrial electronic systems. It shows how to optimize PCB layouts and gives recommendations regarding external components.

To minimize the EMC impact from embedded DC/DC converters, pay attention to PCB component routing when designing with the FS6500 and FS4500.

FS6500 and FS4500 safe system basis chip hardware design and product guidelines

### 2 Overview

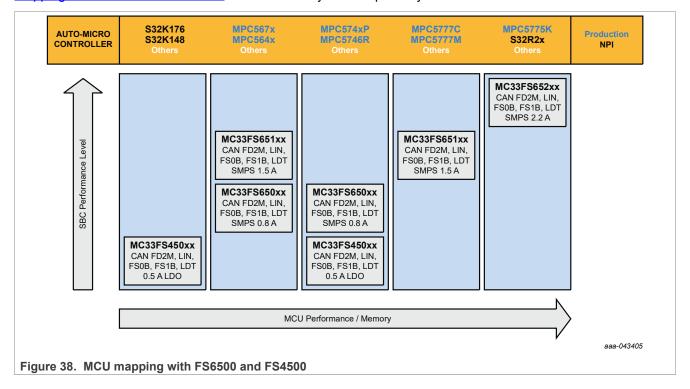

The FS6500 and FS4500 are multi-output power supply integrated circuits dedicated to the automotive market. They simplify system implementation by providing ISO 26262 system solutions, documentation and an optimized MCU interface enabling customers to minimize the cost and complexity of their designs. The FS6500 and FS4500 integrated EMC and ESD protections also facilitate less complex system designs with increased functional reliability.

NXP analog ICs are manufactured using the SMARTMOS process, a combinational BiCMOS manufacturing flow integrating precision analog, power functions, and dense CMOS logic together on a single cost-effective die.

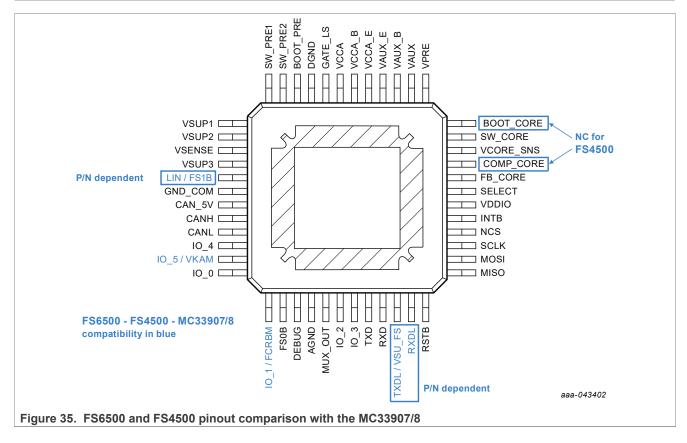

This application note applies to all FS6500 and FS4500 part numbers in both versions ASIL D and ASIL B. LIN and FS1B functions are exclusive. The differentiation is made by part numbers. When LIN is available, FS1B is not, and vice versa. Other exceptions are specifically indicated. Compared to ASILD, ASIL B parts feature a simple Watchdog and do not provide LBIST or FCCU monitoring.

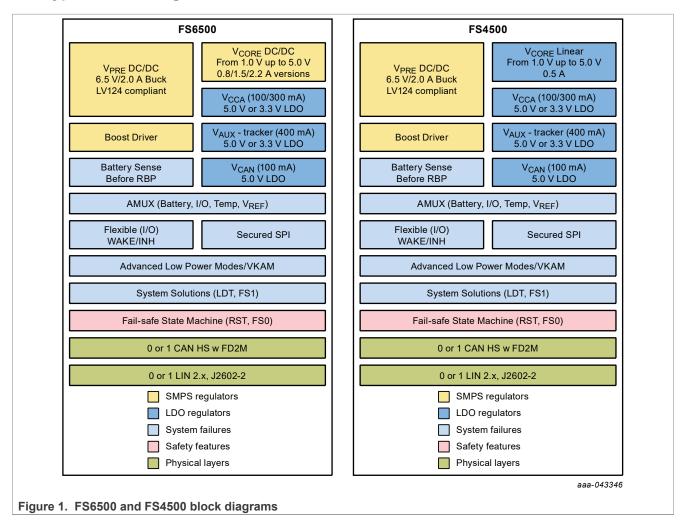

# 2.1 Typical block diagram

### FS6500 and FS4500 safe system basis chip hardware design and product guidelines

# 2.1.1 Key features

- Flexible DC/DC buck pre-regulator with optional boost to fit with LV124

- Ultra low-voltage operation down to 2.7 V

- Scalable family of products supporting a wide range of MCU and power segmentation architectures

- Pin to pin compatible, backward compatible with MC33907/8 at the iso function

- SMPS core supply, from 1.0 V to 5.0 V, delivering up to 2.2 A on FS6500 series

- Linear core supply, from 1.0 V to 5.0 V, delivering up to 0.5 A on FS4500 series

- · Analog multiplexer and battery sensing

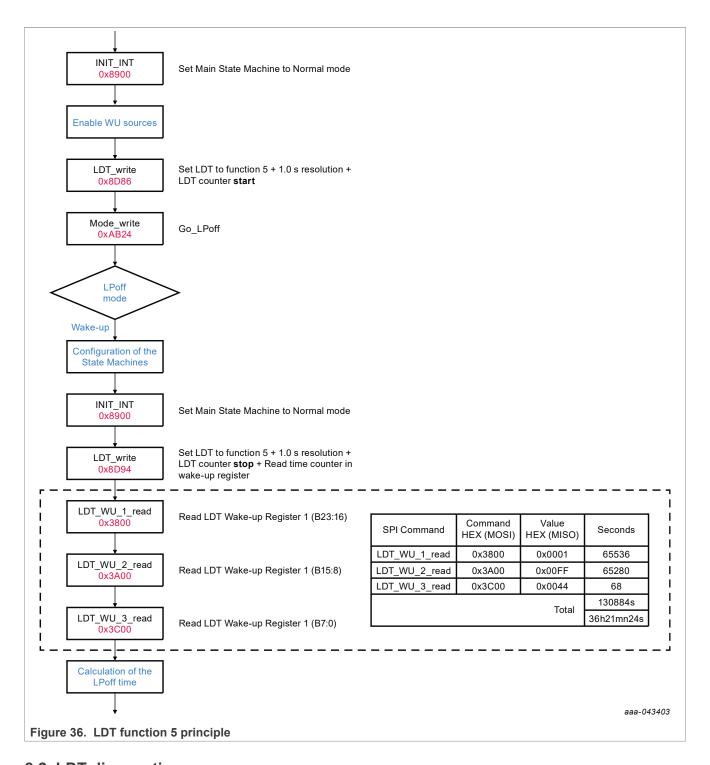

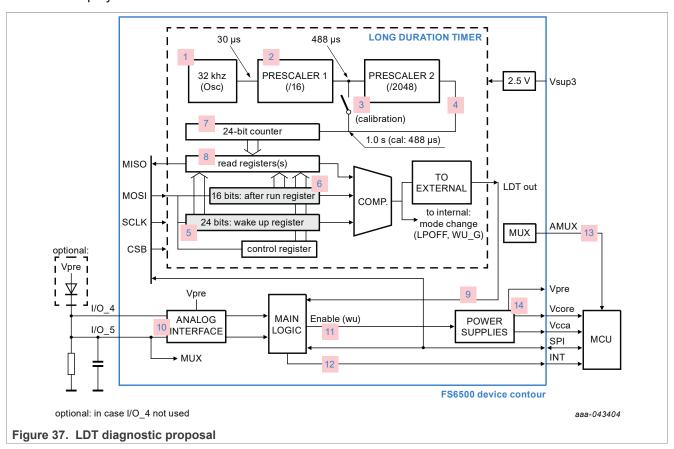

- Long duration timer available in normal and low-power modes (1.0 s resolution)

- Low-power mode 32 μA

- · Multiple wake-up sources in low-power mode: CAN, LIN, IOs, LDT

- · Secured SPI interface

- Robust CANFD (2.0 Mbit/s) and LIN physical layers with superior EMI/ESD performance

- Independent fail-safe state machine monitoring safety critical parameters and supporting functional safety standards

- Fail-silent safety strategy allowing fail-safe state without reset assertion

- Two fail-safe outputs with configurable timings between FS0B and FS1B

- · Fit for ASIL D and ASIL B safety requirements

# 2.1.2 Typical applications

- · Electrical power steering, engine/battery management

- Active suspension, gear box, transmission

- EV, HEV, inverter, ADAS

- Automation (PLC, robotics), medical (infusion pump, stairs)

- Building control (lift), transportation (military, mobile machine)

### 2.1.3 Part number selector guide

### 2.1.3.1 Part number breakdown for ASIL D parts

### MC35FS c 5 x y z AE/R2 (Automotive) - Grade 0

Table 1. Part number breakdown – ASIL D parts

| Code | Option   | Variable                  | Description    |

|------|----------|---------------------------|----------------|

| С    | 4 series | Linear                    |                |

| C    | 6 series | V <sub>CORE</sub> Type    | DCDC           |

| х    | 0        | V <sub>CORE</sub> Current | 0.5 A or 0.8 A |

| ^    | 1        | V CORE Current            | 1.5 A          |

|      | 0        | _                         | None           |

| .,   | 1        |                           | FS1B           |

| У    | 2        |                           | LDT            |

|      | 3        |                           | FS1B and LDT   |

| z    | N        | Physical Interface        | None           |

| 2    | С        | Physical Interface        | CAN FD         |

# FS6500 and FS4500 safe system basis chip hardware design and product guidelines

Table 1. Part number breakdown - ASIL D parts...continued

| Code       | Option                                                                      | Variable | Description |  |

|------------|-----------------------------------------------------------------------------|----------|-------------|--|

| Note: Refe | Note: Refer to the data sheet for the exact list of part numbers available. |          |             |  |

FS6500 and FS4500 safe system basis chip hardware design and product guidelines

# MC33FS <u>c</u> 5 <u>x y z</u> AE/R2 (Automotive) – Grade 1

Table 2. Part number breakdown – ASIL D parts

| Code       | Option              | Variable                                        | Description                      |

|------------|---------------------|-------------------------------------------------|----------------------------------|

|            | 4 series            | V Type                                          | Linear                           |

| С          | 6 series            | V <sub>CORE</sub> Type                          | DCDC                             |

|            | 0                   |                                                 | 0.5 A for FS45<br>0.8 A for FS65 |

| x          | 1                   | V <sub>CORE</sub> Current                       | 1.5 A                            |

|            | 2                   |                                                 | 2.2 A                            |

|            | 0                   |                                                 | None                             |

|            | 1                   | Functions I                                     | FS1B                             |

| У          | 2                   |                                                 | LDT                              |

|            | 3                   |                                                 | FS1B and LDT                     |

|            | 4                   |                                                 | LDT and VKAM ON by default       |

|            | N                   |                                                 | None                             |

| z          | С                   | Physical Interface                              | CAN                              |

|            | L                   |                                                 | CAN and LIN                      |

| Note: Refe | er to the data shee | t for the exact list of part numbers available. |                                  |

FS6500 and FS4500 safe system basis chip hardware design and product guidelines

# 2.1.3.2 Part number breakdown for ASIL B parts

### MC35FS c 5 x y z AE/R2 (Automotive) - Grade 0

Table 3. Part number breakdown - ASIL B parts

| Code | Option   | Variable                  | Description                                                              |

|------|----------|---------------------------|--------------------------------------------------------------------------|

| _    | 4 series | V Time                    | Linear                                                                   |

| С    | 6 series | V <sub>CORE</sub> Type    | Linear  DCDC  0.5 A or 0.8 A  1.5 A  None  FS1B  LDT  FS1B and LDT  None |

|      | 0        | V Command                 | 0.5 A or 0.8 A                                                           |

| X    | 1        | V <sub>CORE</sub> Current | 1.5 A                                                                    |

|      | 6 FS1B   |                           | None                                                                     |

|      |          | FS1B                      |                                                                          |

| У    | 7        | Functions                 | LDT                                                                      |

|      | 8        |                           | FS1B and LDT                                                             |

| _    | N        | Dhusian Intenton          | None                                                                     |

| Z    | С        | Physical Interface        |                                                                          |

### MC33FS c 5 x y z AE/R2 (Automotive) - Grade 1

Table 4. Part number breakdown - ASIL B parts

| Code       | Option              | Variable                                         | Description    |

|------------|---------------------|--------------------------------------------------|----------------|

|            | 4 series            | V Type                                           | Linear         |

| С          | 6 series            | - V <sub>CORE</sub> Type                         | DCDC           |

|            | 0                   |                                                  | 0.5 A or 0.8 A |

| x          | 1                   | V <sub>CORE</sub> Current                        | 1.5 A          |

|            | 2                   |                                                  | 2.2 A          |

|            | 5                   |                                                  | None           |

|            | 6                   | Functions                                        | FS1B           |

| У          | 7                   | FUNCTIONS                                        | LDT            |

|            | 8                   |                                                  | FS1B and LDT   |

|            | N                   |                                                  | None           |

| _          | С                   | Dhysical Interface                               | CAN FD         |

| Z          | K                   | Physical Interface                               | LIN only       |

|            | L                   |                                                  | CAN FD and LIN |

| Note: Refe | er to the data shee | et for the exact list of part numbers available. |                |

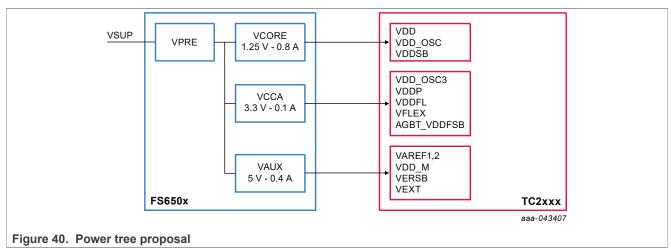

# 2.2 Voltage regulators

# 2.2.1 V<sub>PRE</sub> voltage pre-regulator (SMPS)

$V_{PRE}$  is a flexible switched-mode power supply working in PWM at a fixed 440 kHz frequency.  $V_{PRE}$  is a current mode controlled SMPS, with a fully integrated compensation network.  $V_{PRE}$  can be configured in two topologies:

AN5238

All information provided in this document is subject to legal disclaimers.

© 2024 NXP B.V. All rights reserved.

### FS6500 and FS4500 safe system basis chip hardware design and product guidelines

non-inverting buck-boost or standard buck configuration. The output voltage is regulated at 6.5 V with 2.0 A current capability.  $V_{PRE}$  keeps power dissipation down and eliminates the need for bulky heat sinks compared to linear regulators for a wide input supply range from 2.7 V to 36 V.

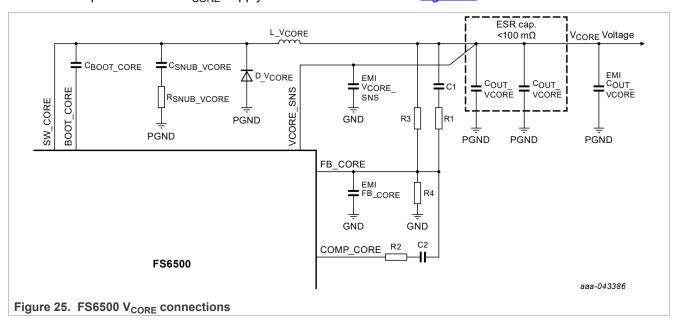

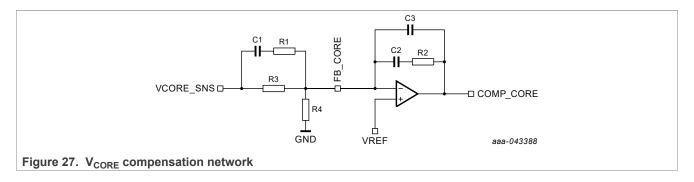

### 2.2.2 FS6500 V<sub>CORE</sub> voltage regulator (SMPS)

FS6500  $V_{CORE}$  is a step-down switched-mode converter working in PWM at a fixed 2.4 MHz frequency dedicated to supplying the MCU core.  $V_{CORE}$  is a voltage mode controlled SMPS, with an external compensation network. The output voltage can be configured in a 1.0 V to 5.0 V range, with an external resistor bridge (a maximum of 1.0 % accuracy resistors are recommended) connected between  $V_{CORE}$  and the FB\_CORE pin. The  $V_{CORE}$  output voltage accuracy is  $\pm 2.0$  % (excluding external resistor accuracy) with a 0.8 A current capability for the FS650x family, 1.5 A for the FS651x family and 2.2 A for the FS652x family.

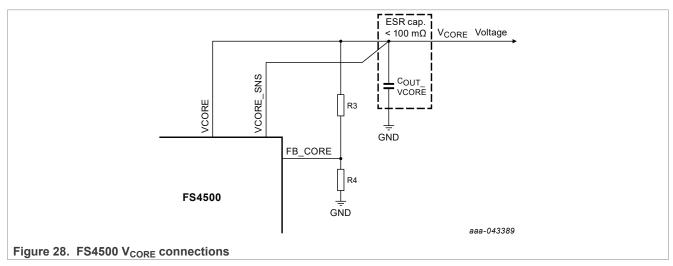

### 2.2.3 FS4500 V<sub>CORE</sub> voltage regulator (linear)

FS4500  $V_{CORE}$  is a linear voltage regulator dedicated to supplying the MCU core. The output voltage can be configured in a 1.0 V to 5.0 V range, with an external resistor bridge (a maximum of 1.0 % accuracy resistors are recommended) connected between  $V_{CORE}$  and the FB\_CORE pin. The  $V_{CORE}$  output voltage accuracy is  $\pm 2.0$  % (excluding external resistor accuracy) with a 0.5 A current capability for the FS450x family.

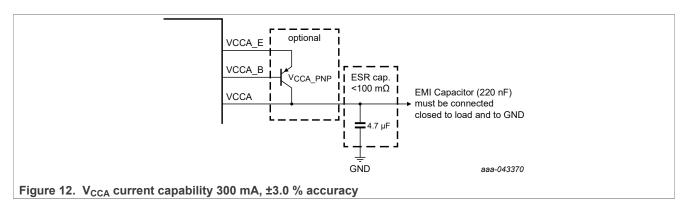

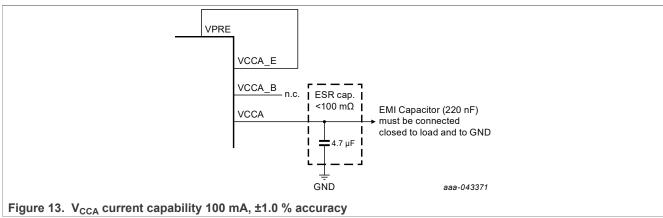

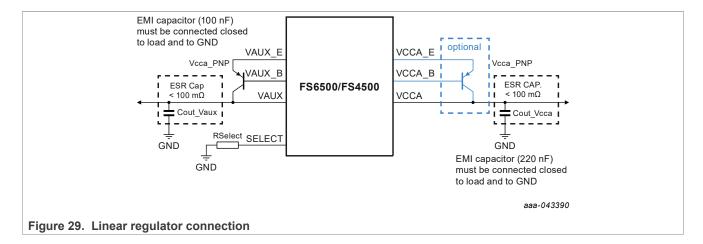

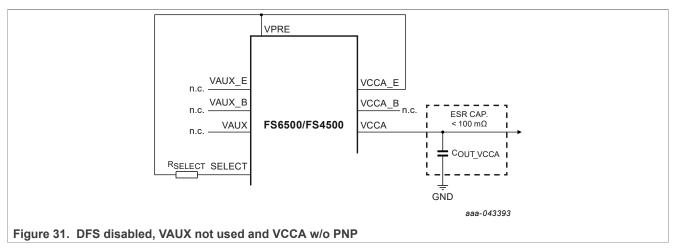

# 2.2.4 V<sub>CCA</sub> voltage regulator (LDO)

$V_{CCA}$  is a linear voltage regulator mainly dedicated to supplying the MCU I/Os, especially the ADC reference voltage. The output voltage is selectable at 5.0 V or 3.3 V, thanks to a resistor value connected to the SELECT pin. The  $V_{CCA}$  output voltage accuracy is  $\pm 1.0\%$  with an output current capability of 100 mA. An external PNP transistor can be used to boost the current capability up to 300 mA with a  $\pm 3.0\%$  output voltage accuracy.

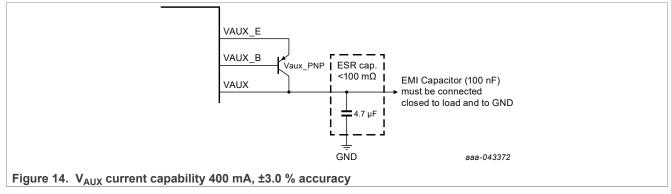

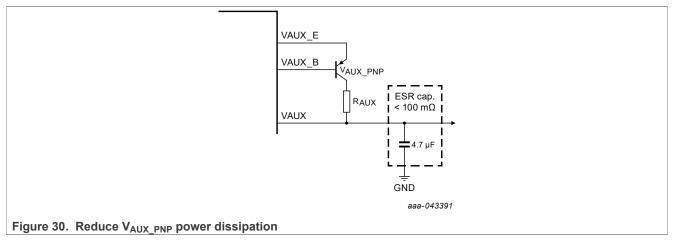

### 2.2.5 V<sub>AUX</sub> voltage regulator (LDO)

$V_{AUX}$  is an auxiliary voltage regulator mainly dedicated to suppling additional devices in the ECU, additional MCU I/Os, or sensors outside the ECU. The external PNP is mandatory.  $V_{AUX}$  is protected against short to battery for up to 40 V. The output voltage is selectable at 5.0 V or 3.3 V, due to the resistor value connected to the SELECT pin.  $V_{AUX}$  output voltage accuracy is  $\pm 3.0$  % with an output current capability of 400 mA.  $V_{AUX}$  can be configured as a tracker of  $V_{CCA}$  with a  $\pm 15$  mV accuracy, when  $V_{AUX}$  is supplying a sensor and  $V_{CCA}$  the reference of the ADC, converting the sensor data to do ratio metric conversions.

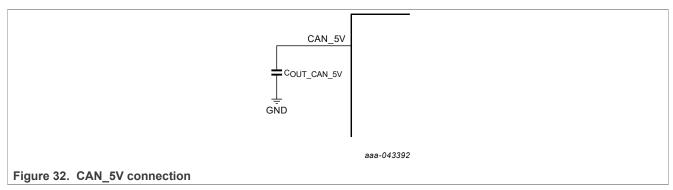

### 2.2.6 CAN\_5V voltage regulator

CAN\_5V is a linear voltage regulator dedicated to the embedded CAN FD interface. If the internal CAN transceiver is not used in the application, the CAN\_5V regulator can be used to supply an external standalone CAN or FLEX-RAY transceiver.

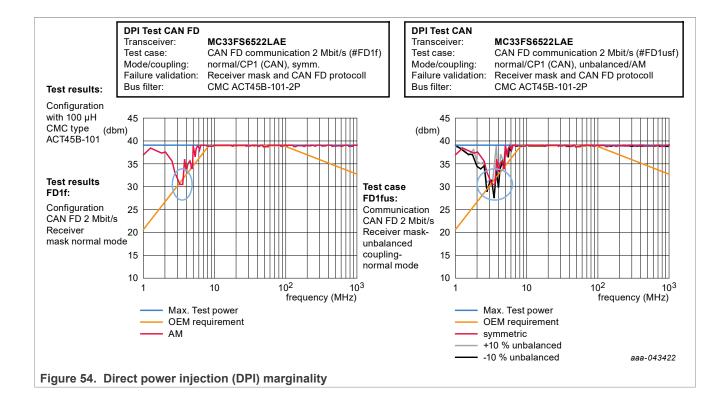

### 2.3 Built-in CAN FD transceiver

The built-in CAN FD interface meets the ISO11898-2 and -5 standards with flexible data standard at 2.0 Mbit/s. Local and bus failure diagnostics, protection, and fail-safe operation modes are provided. The CAN FD exhibits wake-up capability with a very low-current consumption. Refer to the data sheet to know which part number has CAN FD active.

### 2.4 Built-in LIN transceiver

The built-in LIN interface is compatible with the LIN protocol specification 2.0, 2.1, 2.2, and SAEJ2602-2. Local and bus failure diagnostics, protection, and fail-safe operation modes are provided. The LIN exhibits wake-

AN5238

FS6500 and FS4500 safe system basis chip hardware design and product guidelines

up capability with a very low-current consumption. Refer to the data sheet to know which part number has LIN active.

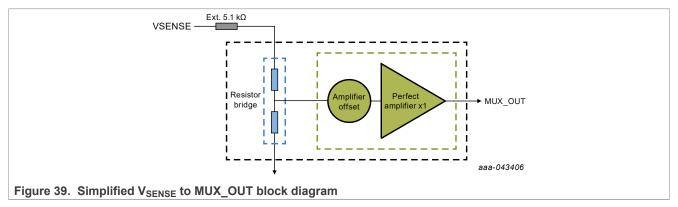

# 2.5 Analog multiplexer

The analog multiplexer allows multiplexing of the following voltages to be output from the FS6500 and FS4500 and connected to one of the MCU ADC channels. The MCU can use the information for monitoring purposes (refer to the data sheet for more details).

- 2.5 V internal reference voltage with a ±1.0 % accuracy

- · Battery sense

- Analog inputs IO\_0 and IO\_5

- Die temperature T(°C) = (V<sub>AMUX</sub> V<sub>AMUX</sub> <sub>TP</sub>) / V<sub>AMUX</sub> <sub>TP</sub> <sub>CO</sub> + 165

A serial resistor can be added to filter the MUX\_out pin before the MCU ADC input. This resistor is not mandatory, and depends on the application need and PCB layout performances. If a resistor is added, the MUX out time constant is longer.

# 2.6 Configurable I/Os

The FS6500 and FS4500 includes five multi-purpose I/Os.

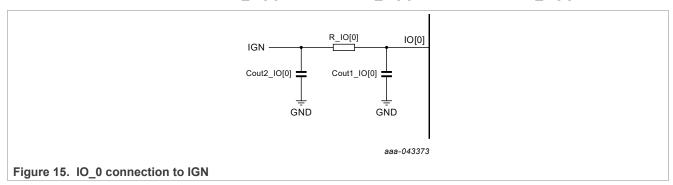

IO\_0 and IO\_4 are global pins and can be connected outside the ECU. They are load dump proof and robust against ISO 7637-2:2011 pulses with a serial resistor and a capacitor to limit the current and the negative voltage during the high transient pulse on the line.

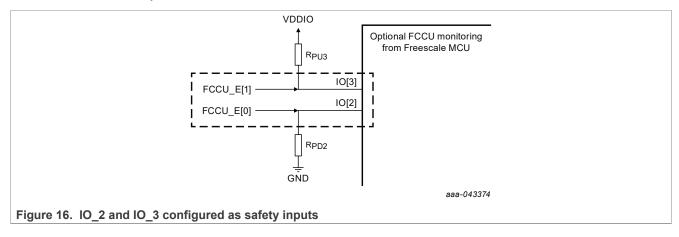

IO 2/3 are local pins and must be connected inside the ECU.

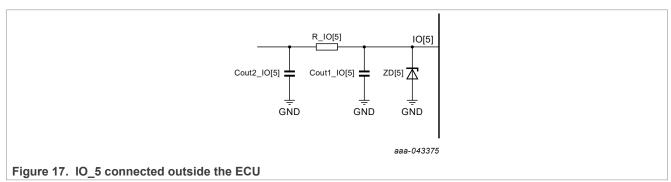

$IO\_5$  is shared with  $V_{KAM}$  output regulator and consequently rated at 20 V maximum. A zener diode in addition to a serial resistor is required if this IO is connected outside the ECU to be robust against load dump and ISO 7637-2:2011 pulses.

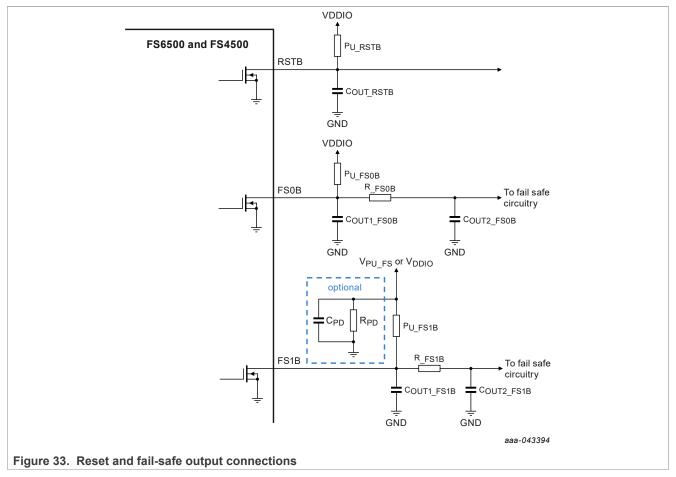

### 2.7 Safety outputs

The FS6500 and FS4500 has two safety outputs FS0B and FS1B. The FS0B pin is intended to take remedial action (disable actuators) after any critical fault detection within the system fault interval time (FTTI). The FS1B pin follows the activation of FS0B with a configurable delay or for a configurable duration. Both safety outputs are active low. Refer to the safety manual for more details on the safety implementation.

### 2.8 Fail-safe machine

To fulfill the safety-critical applications, a dedicated fail-safe machine (FSM) is provided. The FSM is composed of three main sub-blocks:

- Voltage supervisors

- · Fail-safe output driver (FSO)

- Built-in self test (BIST)

The FSM is independent from the rest of the circuitry to avoid common cause failure. The FSM has its own voltage regulators (analog and digital), dedicated bandgap, and oscillator. This block is physically independent from the rest of the circuitry by doing dedicated layout placement and trench isolation.

FS6500 and FS4500 safe system basis chip hardware design and product guidelines

# 2.9 Watchdog

According to the data sheet chapter 6.5.2.1, WD\_ANSWER = NOT(WD\_LFSR x 4 + 6 - 4) /4. In order to correctly calculate the WD\_ANSWER, based on the WD\_LFSR, the MCU shall use unsigned integer operation on minimum 16 bits register. Note: this applies only to ASIL D. For ASIL B, a simple watchdog is implemented.

### 2.10 Low-power mode OFF

Before going to LPOFF, it is recommended to read the IO\_INPUT register and verify IO\_0 state. With default IO\_0 wake-up configuration (rising edge or high level), IO\_0 must be at a low level before sending the LPOFF SPI command. Otherwise, the device goes to LPOFF and immediately wakes up by the IO\_0 high level state.

In low-power mode OFF (LPOFF), all the voltage regulators are turned off, except VKAM, if VKAM was ON before going to LPOFF. The MCU connected to  $V_{CORE}$  is not supplied. The FS6500 and FS4500 configuration monitors external events to wake-up and leave the LPOFF mode. Wake-up events can be generated via the CAN FD interface, LIN interface, I/O inputs, or long duration timer. A wake-up event triggers the regulators to turn on.

After wake-up from LPOFF, it is recommended to read the fault error counter and decrement it to an appropriate value by several consecutive good watchdog refreshes before a reset request by the SPI. The number of watchdogs needed (N) depends on the fault error counter value (FLT\_ERR\_2:0) and the WD refresh counter (WD\_RFR\_2:0) setup during INIT phase. N = FLT\_ERR\_2:0 x (WD\_RFR\_2:0 + 1) to decrement the counter to "0".

### 2.11 MCU programming

### 2.11.1 At customer assembly line

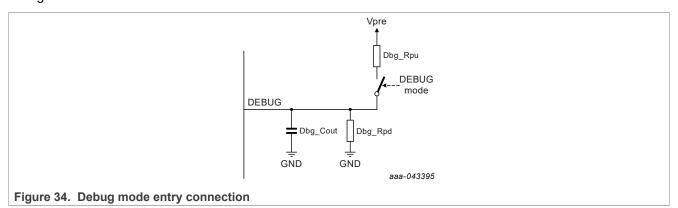

After PCB assembly, the first time the MCU is powered, the flash memory of the MCU is empty and must be programmed. To facilitate the programming, it is recommended to use the debug mode of the device applying the correct voltage at DEBUG pin as explained in <u>Section 6.8. FS6500 and FS4500 Debug pin, page 34</u>. In debug mode, the CAN transceiver is in normal mode by default, ready to transmit and receive data, and the watchdog timeout is disabled by default, preventing to refresh good watchdog periodically. When the programming is complete, send the device to LPOFF\_Auto\_WU to restart the MCU from a power on reset and execute the software.

### 2.11.2 In-vehicle programming

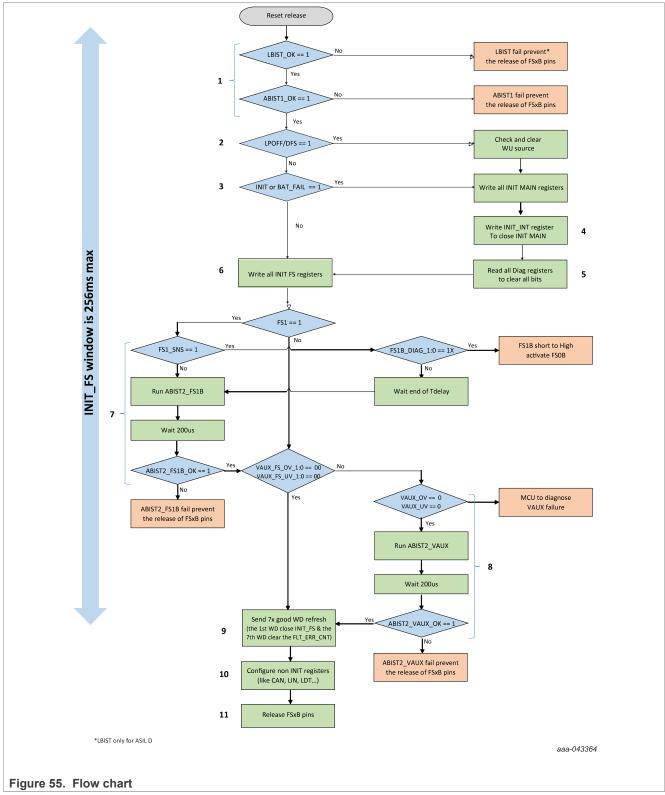

For in-vehicle programming at the garage, if the debug mode cannot be used, the watchdog refresh can be disabled during INIT\_FS state of the fail-safe logic to allow programming without taking care of the watchdog refresh. INIT\_FS can be entered by a reset request with RSTB\_REQ bit in SF\_OUTPUT\_REQUEST register. It is also recommended to disable the FCCU monitoring to avoid unexpected FCCU error detection during the programming by setting IO\_23\_FS bit at '0' in INIT\_FSSM register. The watchdog disable is effective when the INIT\_FS is closed and requires at least one good watchdog refresh within the 256 ms of the INIT\_FS timeout.

When the programming is complete, reset the MCU by a reset request with RSTB\_REQ bit in SF\_OUTPUT\_REQUEST register to execute the new software and enable the watchdog again or send the device to LPOFF\_Auto\_WU to restart the MCU from a power on reset and execute the new software.

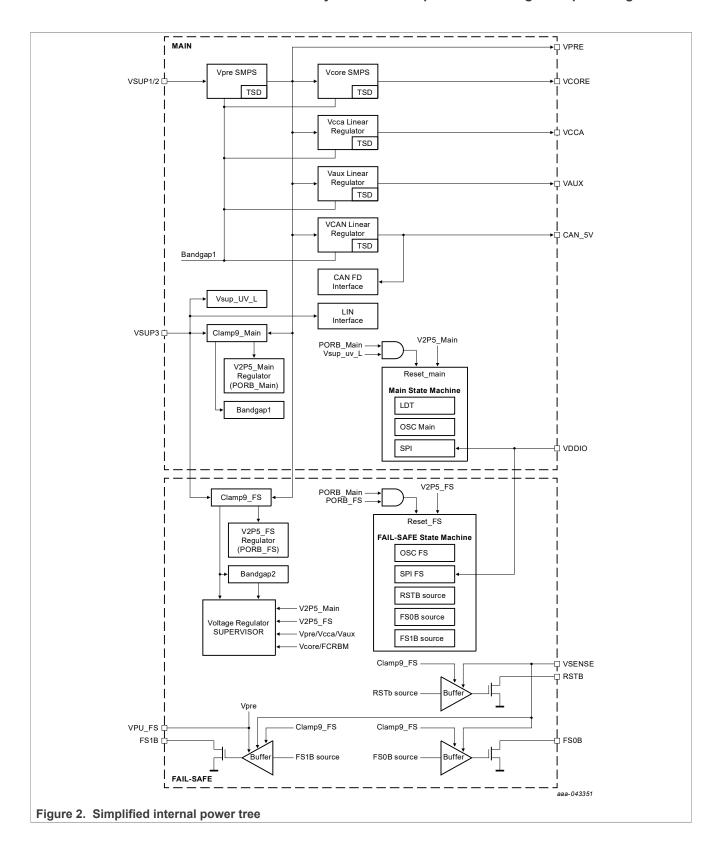

### 2.12 Simplified internal power tree

<u>Figure 2</u> describes a simplified internal power tree to help understand basic concept between main part of the device and fail-safe part of the device.

# FS6500 and FS4500 safe system basis chip hardware design and product guidelines

FS6500 and FS4500 safe system basis chip hardware design and product guidelines

# 3 Known device behaviors

Table 5. Known behavior summary and workaround

| Event                                                                            | Behavior                                                                                                                                                                                                         | AN Section   | Workaround                                                                                               |

|----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|----------------------------------------------------------------------------------------------------------|

| LPOFF current spikes                                                             | Two current spikes could be observed after several minutes in LPOFF mode                                                                                                                                         | Section 3.1  | NA                                                                                                       |

| LPOFF current excursion                                                          | Temporary excursion in the LPOFF quiescent current                                                                                                                                                               | Section 3.2  | Mask INTB interrupt generation to remove this excursion.                                                 |

| FS1b time delay                                                                  | tDELAY or tDUR time is not respected in specific configuration                                                                                                                                                   | Section 3.3  | NA                                                                                                       |

| No wake up by CAN                                                                | Part numbers without FS1B will not wake up by can if FS1B_CAN_IMPACT=1                                                                                                                                           | Section 3.4  | Configure FS1B_CAN_IMPACT=0 in INIT_<br>FAULT register for part numbers without<br>FS1B.                 |

| Unexpected OV/UV after wake up from LPOFF.                                       | In case of wake up from LPOFF with a residual voltage on VPRE<3.4 V, VPRE_OV, VCORE_FB_OV, VCCA_OV, VAUX_OV, VSNS_UV flags can unexpectedly reported                                                             | Section 3.5  | Read Diagnostic registers twice after wake up from LPOFF to filter unexpected flags.                     |

| Unexpected CAN_5V Ilim flag                                                      | If CAN TXD traffic is present when CAN_<br>MODE bit is configured from sleep to normal<br>mode, ILIM_CAN bit can be unexpectedly<br>reported                                                                     | Section 3.6  | Configure CAN_MODE in normal mode before starting a transmission on CAN TXD.                             |

| FS1B backup delay automatically triggered                                        | FS1B backup delay is triggered When VSUP is removed or when device goes to LPOFF mode                                                                                                                            | Section 3.7  | Removing Cpd and Rpd in Vpu_fs Pin.                                                                      |

| Unexpected FS1B release                                                          | FS1B glitch happens ~12 s after device power-<br>up, results in FS1B being released gradually<br>when FS1B is pulled up to VDDIO and FS1B_<br>DLY_REQ=1 (S1 open), even when there is no<br>FS1B release command | Section 3.8  | Pull up FS1B to VPU_FS or set FS1B_DLY_<br>REQ=0 before FS1B release when FS1B is<br>pulled up to VDDIO. |

| CANH_BATT,CANH_GND,<br>CANL_BATT,CANL_GND didn't<br>report as expected           | When CAN BUS is shorted to GND/battery, CANH_BATT,CANH_GND,CANL_BATT happen, diagnose bits did not report as expected.                                                                                           | Section 3.9  |                                                                                                          |

| ISO 7637-2 Pulse 2a (+112<br>V max) test fail when Pi filter<br>inductor >2.2 µH | When Pi filter inductor > 2.2 μH, it is possible that Vcore_UV, Vcca_UV, Vaux_UV reported when ISO 7637-2 pulse 2 a was injected.                                                                                | Section 3.10 | Select Pi filter inductor value ≤ 2.2 µH.                                                                |

| VAUX short to VBAT at start-up                                                   | When powering-up, if VAUX is shorted to VBAT, the RSTB pin is kept low until the short-circuit is removed, preventing application to run.                                                                        | Section 3.11 | Use dual common anode switching diode as protection                                                      |

| VAUX 3.3 V tracker regulating at 5<br>V during LBIST after wake-up               | V <sub>AUX</sub> starts up at 5.0 V after wake-up from LPOFF/DFS during LBIST execution (~12 ms) before regulating to 3.3 V when V <sub>AUX</sub> = V <sub>CCA</sub> = 3.3 V and VAUX tracker mode is enabled.   | Section 3.12 | Disable VAUX tracker mode or use an external tracker LDO if 3.3 V tracker function is a must.            |

| VAUX 3.3 V tracker oscillation at light load                                     | V <sub>AUX</sub> oscillates between 3.3 V and 5 V after LBIST execution preventing RSTB release at light load.                                                                                                   | Section 3.13 | Disable VAUX tracker mode or use an external tracker LDO if 3.3 V tracker function is a must.            |

| Fault error counter behavior when ABIST1 fails                                   | Fault error counter value will be stuck at '2' and will not be incremented when RSTB or FS0B is asserted LOW when ABIST1 fails.                                                                                  | Section 3.14 | Send 'LPOFF_AUTO_WU' SPI commands when ABIST1 failure is detected.                                       |

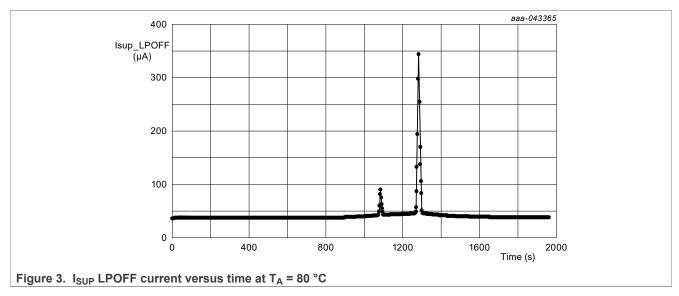

# 3.1 LPOFF current spikes

The current consumption on  $V_{SUP}$  in LPOFF mode is specified in the data sheet at 60  $\mu$ A maximum at  $T_A$  = 80  $^{\circ}$ C. However, two current spikes could be observed after several minutes.

Measurements taken with KITFS6523CAEEVM at  $T_A$  = 80 °C in Figure 3 indicates :

- first spike at 90 µA after 17 minutes during 18 seconds

- second spike at 350 μA after 21 minutes during 30 seconds

### FS6500 and FS4500 safe system basis chip hardware design and product guidelines

The origin of these current spikes in LPOFF mode are due to VPRE bootstrap capacitor discharge. When the device goes in LPOFF, the bootstrap capacitor is discharged through leakages. It can take a long time to discharge at room temperature and it is accelerated by hot temperature. This time depends also on device manufacturing process and PCB parasitic. The current spike levels and timings measured on KITFS6523CAEEVM are for information only. It might differ at customer application.

During capacitor discharge some elements in the bootstrap circuitry are activated, consuming current from V<sub>SUP</sub> and finally discharging the capacitor. It is a single event. When the bootstrap capacitor is fully discharge after these two current spikes, no more variation of the LPOFF guiescent current is visible.

### 3.2 LPOFF current excursion

A temporary excursion in the LPOFF quiescent current can be observed in the specific conditions described in the following list:

- ISUP\_LPOFF current =  $32 \mu A$  (typ.) when the device enters in LPOFF with VSUP < 7.7 V or VSUP > 8.3 V. When the device is in LPOFF, then ISUP\_LPOFF current does not change with VSUP voltage.

- ISUP\_LPOFF current = 1.7 mA (typ.) when the device enters in LPOFF with VSUP between 7.7 V and 8.3 V. When the device is in LPOFF, if VSUP moves < 7.7 V or > 8.3 V, then ISUP\_LPOFF current goes back to 32 μA and does not change anymore with VSUP voltage.

- To trigger the ISUP\_LPOFF excursion behavior, it is mandatory to enter in LPOFF with VSUP between 7.7 V and 8.3 V and to stay in this VSUP range.

This behavior is not temperature dependent and is visible on all the parts. This LPOFF current excursion can be removed if the INTB interrupt generation is masked with INT\_INH\_ALL bit in INIT\_INT register.

### 3.3 FS1b time delay

The activation of FS1B follows the activation of FS0B with a configurable delay (tDELAY) or a configurable duration (tDUR).

In specific configurations FS1b will be activated after a specific time mentioned in the following table.

### FS6500 and FS4500 safe system basis chip hardware design and product guidelines

Table 6. FS1b Activation time

| FS1b configuration | INIT_SF_<br>IMPACT register   | Deep<br>FailSafe | INIT_FS closing condition<br>after RSTb assertion | FS1b                                                               |

|--------------------|-------------------------------|------------------|---------------------------------------------------|--------------------------------------------------------------------|

|                    |                               |                  | Good WD                                           | Asserted after tDELAY config                                       |

|                    |                               | disable          | time out (256 ms)                                 | Asserted after 4.7 s                                               |

| tDELAY config      | RSTB and FS0b                 |                  | wrong WD sent after 37 ms                         | Asserted after 4.7 s                                               |

| 12 331g            | asserted low                  | enable           | Time out or wrong WD                              | Asserted after 4.7 s deep failsafe when fault_err_ count=max value |

|                    | RSTB and FS0b<br>asserted low |                  | Good WD                                           | Released after tDUR config                                         |

|                    |                               |                  | time out (256ms)                                  | Released after 4.7 s                                               |

| tDUR config        |                               |                  | wrong WD after 37 ms                              | Released after 4.7 s                                               |

|                    |                               | enable           | Time out or wrong WD                              | Never released deep failsafe when fault_err_count = max value      |

### 3.4 No wake up by CAN

Part numbers without FS1B will not wake up by CAN if FS1B\_CAN\_IMPACT=1. It is recommended to configure FS1B\_CAN\_IMPACT=0 in INIT\_FAULT register to keep the CAN wake up capability.

# 3.5 Unexpected OV/UV when returning from low power off mode

In case of wake up from LPOFF with a residual voltage on VPRE (Vpre < 3.4 V), VPRE OV, VCORE FB OV, VAUX OV, VCCA OV and VSNS UV flags can unexpectedly be set to 1.

It is recommended to read Diagnostic registers twice after wake up from LPOFF to filter unexpected flags. In case of true failure, the flags will remain visible at the second reading.

### 3.6 Unexpected CAN 5V Ilim flag

If CAN TXD traffic is present when CAN\_MODE bit is configured from sleep to normal mode, ILIM\_CAN bit in DIAG\_VSUP\_VCAN can be unexpectedly reported.

Configure the CAN\_MODE bit before starting a transmission on CAN TXD.

### 3.7 FS1B backup delay automatically triggered

This behavior happens when FS1B is configured in delay mode and pulled up to Vpu\_fs. When Vsup is removed or when the device goes to LPOFF Mode, all fail safe registers are reset to their default values. FS1B\_DLY\_REQ bit in SF\_OUTPUT\_REQUEST register will be set to 1: Request FS1B assertion with Tdelay controlled by the backup delay (open S1). As a result, FS1B backup delay is triggered if Rpd and Cpd are connected to the Vpu\_fs pin.

If FS1B is high when Vsup is removed or when device goes to LPOFF Mode, FS1B is asserted low with a delay after FS0B is activated. The delay time is defined by Rpd and Cpd in Vpu\_fs pin. If FS1B is low when Vsup is removed or when device goes to LPOFF Mode, FS1B goes high as soon as Vsup < Vsup\_UV\_L (Buck-Boost Mode), Vsup < Vsup\_UV\_L\_B (Buck Mode) or FS65 enters LPOFF mode. Then, FS1B return to low when Vpu\_fs voltage drops to 3.2 V (typ). The duration of FS1B high is defined by Rpd and Cpd value in Vpu\_fs pin.

FS6500 and FS4500 safe system basis chip hardware design and product guidelines

The workaround is to remove Cpd and Rpd from the Vpu\_fs pin if the triggered FS1B backup delay function is not expected when Vsup is removed or when device goes to LPOFF Mode in the application.

### 3.8 Unexpected FS1B release

This behavior happens when FS1B is pulled up to VDDIO and FS1B\_DLY\_REQ=1 (S1 open). An FS1B glitch happens ~12 s after the device powers up, resulting in FS1B being released gradually, even if there is no FS1B release command.

To prevent this behavior, pull FS1B up to Vpu\_fs. Pulling up FS1B to Vpu\_fs avoids the common cause failure when both FS0B and FS1B are pulled up to VDDIO. If the application requires that FS1B be pulled up to VDDIO, the FS1B\_DLY\_REQ bit in the SF\_OUTPUT\_REQUEST register must be set to 0 (Close S1) before the FS1B glitch happens.

# 3.9 CANH BATT, CANH GND, CANL BATT, CANL GND didn't report as expected

CANL\_GND/CANH\_BATT did not report in some cases when a CAN BUS short to GND/battery occurs, because the voltage in the CANL/CANH pin did not reach the CANL\_GND/CANH\_BATT detection threshold. First, CANL short to GND is detected when CANL< 0.5 V, 500 ns after TXD is activated low, and five consecutive times have elapsed. 0.5 V is not the detection threshold. Different parts have different thresholds, but the max threshold < 0.5 V. CANH short to battery is detected when CANH > 5.2 V, 500 ns after TXD is activated low, and five consecutive times have elapsed. 5.2 V is not the detection threshold. Different parts have different thresholds, but the min threshold > 5.2 V. In another side, the injected position CANL short to GND/CANH short to battery impacts the diagnostic bits report due to a voltage drop between the injected point and the CANL/CANH pins.

CANL\_BATT/CANH\_GND did not report in some cases when a CAN BUS short to battery/GND occurs, because ICANL or ICANH did not reach the CANL\_BATT/CANH\_GND detection threshold. First, CANL short to battery and CANH short to GND are detected when ICANL or ICANH > 75 mA (typ), 500 ns after TXD is activated low, and five consecutive times have elapsed. 75 mA is the typical threshold. Different parts have different thresholds, varying from 40 mA to 100 mA. In another side, there is usually a common choke in the CAN BUS to filter noise. This component prevents ICANL or ICANH from reaching the diagnostic threshold when a CAN BUS short to battery/GND happens.

### 3.10 ISO 7637-2 Pulse 2a (+112 V max) test fails when Pi filter inductor > 2.2 µH

The FS45/FS65 may report a Vcore\_UV, Vaux\_UV, Vcca\_UV when injectingISO 7637-2 Pulse 2a(+112 V max) with Pi filter inductors with values greater than recommended ( > 2.2  $\mu$ H). Pi filters with higher values cause voltage gaps between Vsup1/2 and Vsup3 when the battery voltage oscillates. The FS45/FS65 data sheet says that "All VSUPS (VSUP1/2/3) must be connected to the same supply". A 1  $\mu$ H Pi filter inductor is recommended in the FS65 application schematic and the inductor value must not exceed 2.2  $\mu$ H. To improve EMC performance for the whole board, add another inductor with a higher inductance (for a change) before the FS65.

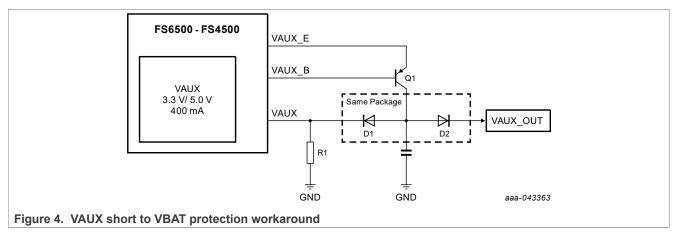

### 3.11 VAUX short to VBAT at start-up

When the FS65-FS45 is powering-up while VAUX output is shorted to the battery voltage (VBAT), the RSTB pin is kept low, preventing the application from running. The only way to release RSTB, is to eliminate the short circuit. However, if the short circuit occurs after the FS65-FS45 is already awake and configured, the device reaction depends on the INIT\_VAUX\_OVUV\_Impact register settings. Also, if VAUX is shorted to ground, this event will not occur since VAUX\_FS\_UV\_1:0 default setting is "VAUX\_UV does have an impact on FS0B only".

When the product goes in LPOFF, its current configuration is lost, which means the default configuration will be taken into account when waking up again. In the default configuration, VAUX is configured as "safety critical" so

FS6500 and FS4500 safe system basis chip hardware design and product guidelines

an OV (e.g. short to battery) triggers a RESET and keeps the safety pins asserted. After 8.0 s, the FS65-FS45 goes into DFS (Deep Fail-Safe) if enabled, or LPOFF.

<u>Figure 4</u> shows a workaround for RSTB being held low because the VAUX output is shorted to battery voltage during power-up. This workaround uses a dual common anode switching diode as protection.

The same forward voltage for both diodes is achieved by keeping the dual common anode switching diodes in the same package with the same thermal coupling for both diodes (optimum would be on the same die) and by using the R1 pull-down resistor to balance the VAUX load current between the diodes.

This workaround is well fitted for light load currents on VAUX (e.g. ILOAD < ~50 mA). For higher current levels, R1 would have to dissipate too much power and VAUX accuracy would be impacted.

# 3.12 VAUX 3.3 V tracker regulating at 5 V during LBIST after wake-up

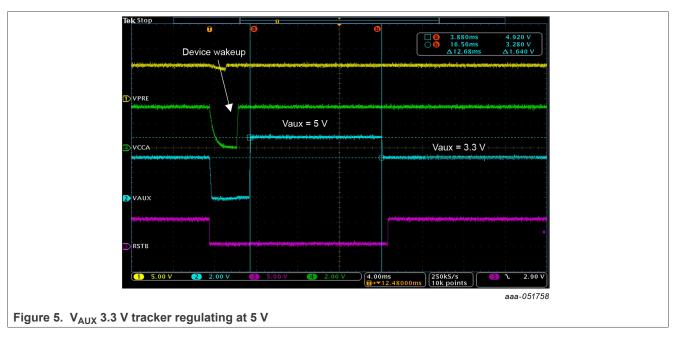

When the device wakes up from LPOFF or DFS mode,  $V_{AUX}$  delivers 5.0 V during LBIST execution (~12 ms) before regulating to 3.3 V when  $V_{AUX} = V_{CCA} = 3.3$  V and VAUX tracker mode is enabled. See <u>Figure 5</u>.

The root cause is that the VAUX 3.3 V configuration is masked by the digital block if VAUX\_TRK\_EN = 1 when the device wakes up from LPOFF mode. Since the VAUX feedback resistor divider default configuration is

AN5238

FS6500 and FS4500 safe system basis chip hardware design and product guidelines

5.0 V,  $V_{AUX}$  starts up and remains at 5 V until the tracker mode is engaged when ABIST1 starts (after LBIST execution). After LBIST execution,  $V_{AUX}$  starts to track the  $V_{CCA}$  output voltage and regulates at 3.3 V.

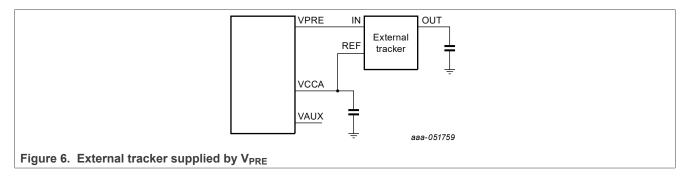

The workaround is to disable VAUX tracker mode when  $V_{AUX}$  and  $V_{CCA}$  are configured at 3.3 V.  $V_{AUX}$  will regulate at 3.3 V after wake-up from LPOFF/DFS mode. If  $V_{AUX}$  3.3 V tracker mode is a must, the customer is advised to use an external tracker LDO; the tracker LDO can be supplied by  $V_{PRE}$  with reference from  $V_{CCA}$  for tracking (see Figure 6).

### 3.13 VAUX 3.3 V tracker oscillation at light load

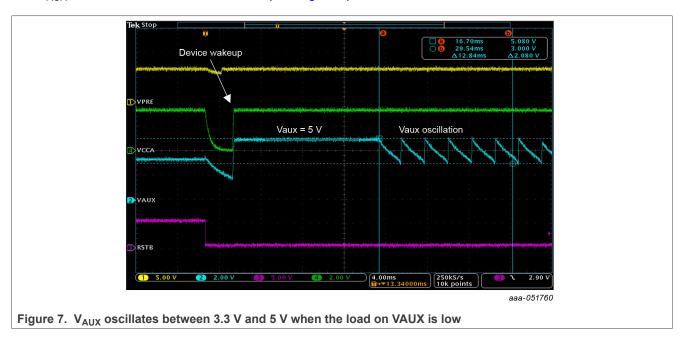

When there is a light load at the VAUX output, V<sub>AUX</sub> will oscillate between 3.3 V and 5 V after the transition from 5 V to 3.3 V, preventing pin RSTB being released.

The root cause is that the  $V_{AUX}$  transition time from 5 V to 3.3 V is greater than the  $V_{AUX}$  overvoltage filtering time ( $V_{AUX}_{OV}$ ) when there is a light load on VAUX. As a result,  $V_{AUX}$  UV and OV events are triggered cyclically and  $V_{AUX}$  oscillates between 3.3 V and 5 V (see Figure 7).

The workaround is the same as suggested for VAUX 3.3 V tracker regulating at 5 V in <u>Section 3.12</u>. Disable VAUX tracker mode or add an external tracker LDO.

FS6500 and FS4500 safe system basis chip hardware design and product guidelines

### 3.14 Fault error counter behavior when ABIST1 fails

The fault error counter value is '1' by default after device POR or wake-up from LPOFF mode. However, the fault error counter value will be stuck at '2' and will not increase when RSTB or FS0B is asserted if ABIST1 has failed.

The workaround is to send an 'LPOFF\_AUTO\_WU = 1' command via SPI if an ABIST1 failure is reported after device power-up. Fail-safe digital will be reset, ABIST1 will be executed again and ABIST1 will pass if faults are removed.

FS6500 and FS4500 safe system basis chip hardware design and product guidelines

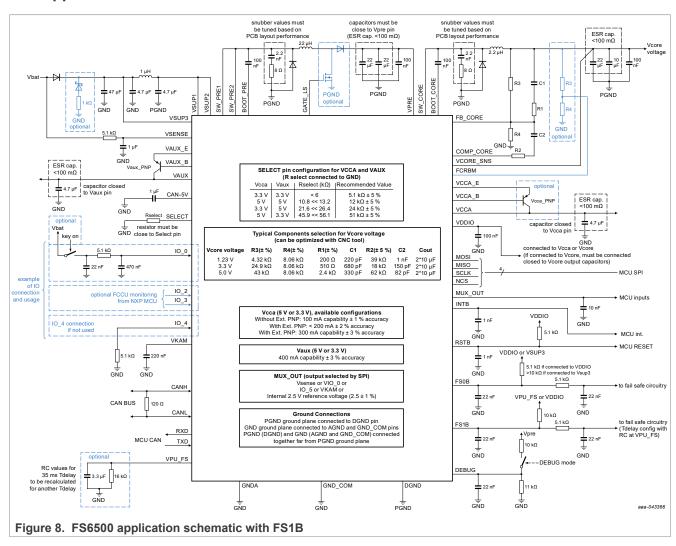

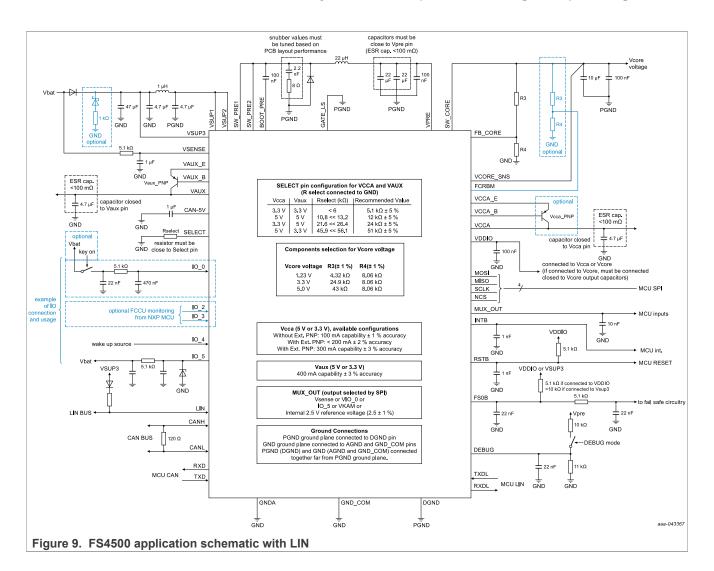

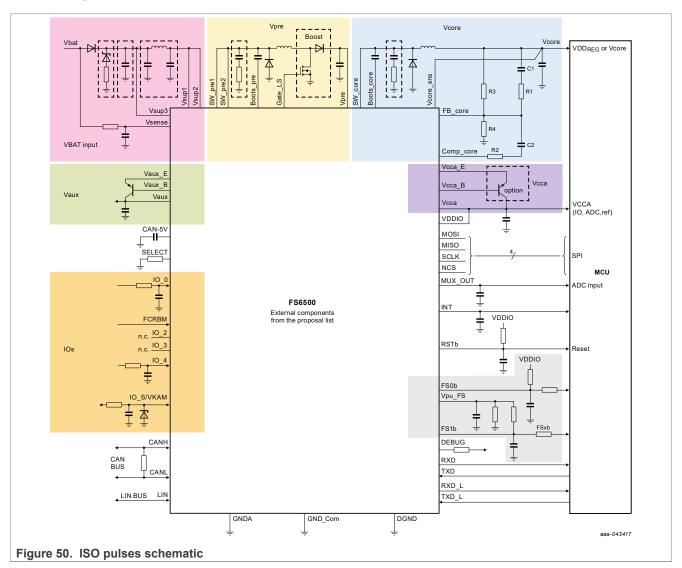

# 4 Application schematic and unused pins configuration

# 4.1 Application schematic

### FS6500 and FS4500 safe system basis chip hardware design and product guidelines

# 4.2 Connection of unused pins

### Connection of unused pins

| Pins                                                                                                                                                                                           | Name    | Туре     | Connection if not used                  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|----------|-----------------------------------------|

| 1                                                                                                                                                                                              | VSUP1   | A_IN     | Connection mandatory                    |

| 2                                                                                                                                                                                              | VSUP2   | A_IN     | Connection mandatory                    |

| 3                                                                                                                                                                                              | VSESNSE | A_IN     | Connection mandatory                    |

| 4                                                                                                                                                                                              | VSUP3   | A_IN     | Connection mandatory                    |

|                                                                                                                                                                                                | LIN     | A_IN/OUT | Open                                    |

| 5                                                                                                                                                                                              | or FS1B | D_OUT    | Open - 4.0 MΩ internal pull-down to GND |

| LIN and FS1B functions are exclusive. The differentiation is made by part numbers. When LIN FS1B is not, and vice versa. If neither LIN, nor FS1B functions are used, this pin must be left of |         |          |                                         |

| 6                                                                                                                                                                                              | GND_COM | GROUND   | Connection mandatory                    |

| 7                                                                                                                                                                                              | CAN_5V  | A_OUT    | Connection mandatory                    |

AN5238

# FS6500 and FS4500 safe system basis chip hardware design and product guidelines

| Pins     | Name                                                                                   | Туре                       | Connection if not used                                                                              |

|----------|----------------------------------------------------------------------------------------|----------------------------|-----------------------------------------------------------------------------------------------------|

| 8        | CANH                                                                                   | A_IN/OUT                   | Open                                                                                                |

| 9        | CANL                                                                                   | A_IN/OUT                   | Open                                                                                                |

| 10       | IO_4                                                                                   | D_IN<br>A_OUT              | External 5.1 kΩ pull-down to GND                                                                    |

| 11       | IO_5/VKAM                                                                              | A_IN<br>D_IN<br>A_OUT      | External pull down to GND                                                                           |

|          | VKAM can be enabled or disabled by defau                                               | ult at power-up. The diffe | rentiation is made by part numbers.                                                                 |

| 12       | IO_0                                                                                   | A_IN<br>D_IN               | External pull down to GND (DEEP fail-<br>safe should be disabled - SELECT pin<br>connected to VPRE) |

| 13       | FCRBM                                                                                  | A_IN                       | Connection mandatory (to the middle point of the redundant resistor bridge or to FB_CORE directly)  |

| 14       | FS0B                                                                                   | D_OUT                      | Open - 4.0 M $\Omega$ internal pull-down to GND                                                     |

| 15       | DEBUG                                                                                  | D_IN                       | Connection mandatory (to GND in application run mode)                                               |

| 16       | AGND                                                                                   | GROUND                     | Connection mandatory                                                                                |

| 17       | MUX_OUT                                                                                | A_OUT                      | Open                                                                                                |

| 18<br>19 | IO_2:3                                                                                 | D_IN                       | External pull down to GND/Open                                                                      |

| 20       | TXD                                                                                    | D_IN                       | Open - 33 kΩ internal pull up to VDDIO                                                              |

| 21       | RXD                                                                                    | D_OUT                      | Open - push pull structure                                                                          |

|          | TXDL                                                                                   | D_IN                       | Open - 33 kΩ internal pull up to VDDIO                                                              |

| 22       | or VPU_FS                                                                              | A_OUT                      | Open                                                                                                |

|          | LIN and FS1B functions are exclusive. The FS1B is not, and vice versa. If neither LIN, |                            |                                                                                                     |

| 23       | RXDL                                                                                   | D_OUT                      | Open - push pull structure                                                                          |

| 24       | RSTB                                                                                   | D_OUT                      | Connection mandatory                                                                                |

| 25       | MISO                                                                                   | D_OUT                      | Connection mandatory                                                                                |

| 26       | MOSI                                                                                   | D_IN                       | Connection mandatory                                                                                |

| 27       | SCLK                                                                                   | D_IN                       | Connection mandatory                                                                                |

| 28       | NCS                                                                                    | D_IN                       | Connection mandatory                                                                                |

| 29       | INTB                                                                                   | D_OUT                      | Open - 10 kΩ internal pull up to VDDIO                                                              |

| 30       | VDDIO                                                                                  | A_IN                       | Connection mandatory                                                                                |

| 31       | SELECT                                                                                 | D_IN                       | Connection mandatory                                                                                |

| 32       | FB_CORE                                                                                | A_IN                       | Connection mandatory                                                                                |

| 33       | COMP_CORE                                                                              | A_OUT                      | Connection mandatory                                                                                |

| 34       | VCORE_SNS                                                                              | A_IN                       | Connection mandatory                                                                                |

# FS6500 and FS4500 safe system basis chip hardware design and product guidelines

| Pins | Name      | Туре     | Connection if not used |

|------|-----------|----------|------------------------|

| 35   | SW_CORE   | A_OUT    | Connection mandatory   |

| 33   | or VCORE  | A_OUT    | Connection mandatory   |

| 36   | BOOT_CORE | A_IN/OUT | Connection mandatory   |

| 37   | VPRE      | A_IN     | Connection mandatory   |

| 38   | VAUX      | A_OUT    | Open                   |

| 39   | VAUX_B    | A_OUT    | Open                   |

| 40   | VAUX_E    | A_OUT    | Open                   |

| 41   | VCCA_E    | A_OUT    | Connection mandatory   |

| 42   | VCCA_B    | A_OUT    | Open                   |

| 43   | VCCA      | A_OUT    | Connection mandatory   |

| 44   | GATE_LS   | A_OUT    | Connection mandatory   |

| 45   | DGND      | GROUND   | Connection mandatory   |

| 46   | BOOT_PRE  | A_IN/OUT | Connection mandatory   |

| 47   | SW_PRE2   | A_OUT    | Connection mandatory   |

| 48   | SW_PRE1   | A_OUT    | Connection mandatory   |

FS6500 and FS4500 safe system basis chip hardware design and product guidelines

# 5 Optional configurations

According to customer application needs, optional configurations for the FS6500 and FS4500 are described in the following sections.

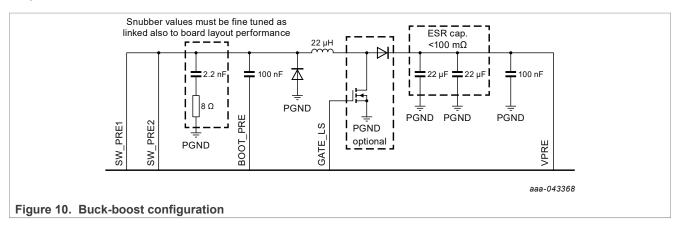

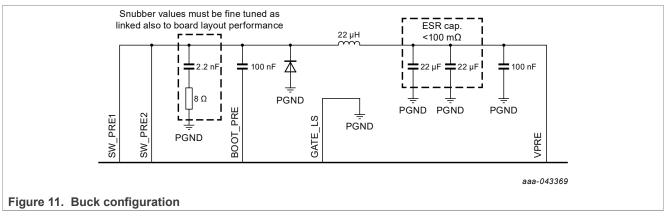

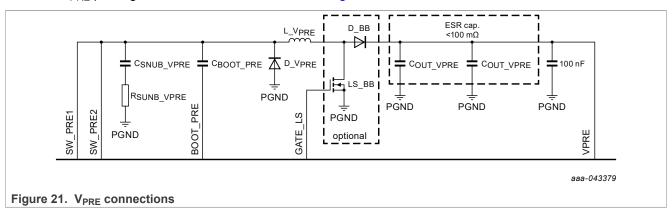

# 5.1 Pre-regulator, buck or buck-boost configuration

Two topologies are available on the FS6500 and FS4500 for the  $V_{PRE}$  pre-regulator. The FS6500 and FS4500 can be configured in buck only or buck-boost converter mode according to the GATE\_LS pin connection. The detection is done automatically during the startup sequence, from power on reset or after each wake-up from LPOFF.

In buck-only configuration, the external low-side MOS and the diode are removed, and the Gate\_LS pin must be connected to ground (PGND or GND).

# 5.2 V<sub>CCA</sub>, current capability

To increase the current capability from 100 mA to 300 mA on the  $V_{CCA}$  linear regulator, an external PNP transistor must be connected. Using an external PNP increases the current capability and reduces the accuracy from  $\pm 1.0$  % at 100 mA to  $\pm 3.0$  % at 300 mA.

### FS6500 and FS4500 safe system basis chip hardware design and product guidelines

When no external PNP is connected to  $V_{CCA}$ , the VCCA\_E pin must be connected to the VPRE pin.

# 5.3 V<sub>AUX</sub>

Depending on application needs, the auxiliary regulator can be used. Figure 10 shows the correct connections of  $V_{AUX}$  with the mandatory external PNP.

When  $V_{AUX}$  is not used, VAUX\_E, VAUX\_B and Vaux pins must be left open. In this situation, VAUX\_UV flag is set and cannot be cleared. This is an expected behavior since VAUX is not starting in this situation. As a consequence, VOTHERS\_G bit is also set and cannot be cleared since VOTHERS\_G = ILIM\_CCA or TWARN\_CCA or TSD\_CCA or ILIM\_CCA\_OFF or VCCA\_UV or VCCA\_OV or ILIM\_AUX or TSD\_AUX or ILIM\_AUX\_OFF or VAUX\_OV or VAUX\_UV or ILIM\_CAN\_or VCAN\_UV or VCAN\_OV or TSD\_CAN.

FS6500 and FS4500 safe system basis chip hardware design and product guidelines

# 5.4 Feedback Core Resistor Bridge Monitoring (FCRBM)

When the application targets the ISO 26262 ASIL D or ASIL B safety level, it is recommended to monitor the  $V_{CORE}$  output voltage through FCRBM. In that case, a second resistor bridge is needed, which is a duplication of the R3/R4 external resistor bridge used to create  $V_{CORE}$  from FB\_CORE. Refer to the safety manual for more information. If the second resistor bridge (R3b/R4b) is not mounted, FCRBM must be connected directly to FB\_CORE to satisfy FB\_CORE = FCRBM in all conditions.

# 5.5 IO\_0 ignition connection

In automotive applications, it is recommended to connect IO\_0 to the ignition to be able to recover from deep fail-safe state by a key OFF, key ON action. IO\_0 is a global pin and can be connected outside the ECU. It is load dump proof and robust against ISO 7637-2:2011 pulses with a serial resistor R\_IO[0] and a capacitor Cout1\_IO[0] to limit the current and the negative voltage during the high transient pulse on the line. It is robust against ESD GUN test up to ±8.0 kV, with a filtering capacitor Cout2\_IO[0].

Cout1\_IO[0] must be placed close to the device pin and Cout2\_IO[0] must be placed close to the module connector. Recommended values are R\_IO[0] = 5.1 k $\Omega$ , Cout1\_IO[0] = 470 nF, and Cout2\_IO[0] = 22 nF.

### 5.6 IO 2 and IO 3, FCCU monitoring for ASIL D only

IO\_2 and IO\_3 can be configured as safety inputs to allow monitoring of the NXP microcontroller FCCU output pins FCCU\_E[0] and FCCU\_E[1]. IO\_2 should be connected to FCCU\_EF[0] and IO\_3 to FCCU\_E[1]. A 5.1 k $\Omega$  pull-up resistor must be connected to IO\_3/FCCU\_E[1] and a 10 k $\Omega$  pull-down resistor to IO\_2/FCCU\_E[0]. Bi-stable protocol only from MCU is supported. If not used, IO\_2 and IO\_3 can be left open or pulled down to GND. Refer to the safety manual for more information.

FS6500 and FS4500 safe system basis chip hardware design and product guidelines

# 5.7 IO\_5 connected outside the ECU

If IO\_5 is connected outside the ECU, a zener diode ZD[5], in addition to a serial resistor R\_IO[5] and a capacitor Cout1\_IO[5], is required to limit the current and the negative voltage during the high transient pulse on the line. It is robust against an ESD GUN test up to ±8.0 kV, with the filtering capacitor Cout2\_IO[5]. Cout1\_IO[0] must be placed close to the device pin and Cout2\_IO[0] must be placed close to the module connector.

Table 7. IO 5 component list

| Component   | Value  | Reference/manufacturer proposal                 | Ground connection |

|-------------|--------|-------------------------------------------------|-------------------|

| Cout1_IO[5] | 470 nF |                                                 |                   |

| Cout2_IO[5] | 22 nF  |                                                 | GND               |

| ZD[5]       |        | BZT52H-C20/NXP<br>MMSZ5250BT1G/ON Semiconductor | GND               |

| R_IO[5]     | 5.1 kΩ |                                                 |                   |

# **5.8 VKAM**

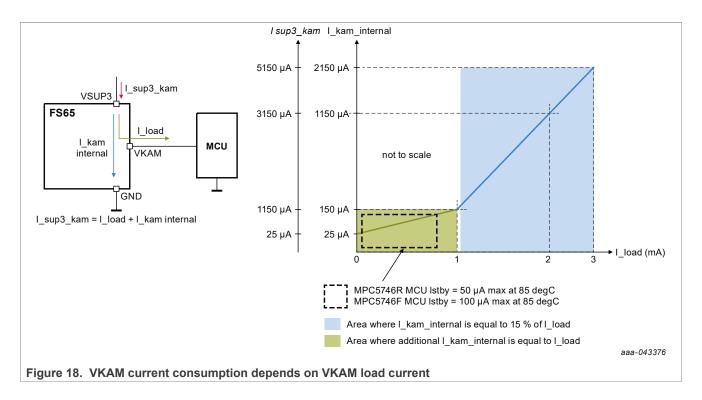

VKAM is a keep alive memory supply, available in LPOFF to supply the static RAM of the MCU (usually named VSTBY at MCU side), but it can also be used for other use cases where VKAM would fit. It provides a 3.3 V supply with 3.0 mA maximum current capability and requires an external capacitor between 100 nF and 1.0 µF to work properly. A 220 nF output capacitor is recommended. VKAM is ON by default in part numbers FS65x4.VKAM is OFF by default in other part numbers, and can be turned ON by the SPI. VKAM current consumption depends on the VKAM current load. This dependence is shown in Figure 14 to illustrate the data sheet parametric performances.

### FS6500 and FS4500 safe system basis chip hardware design and product guidelines

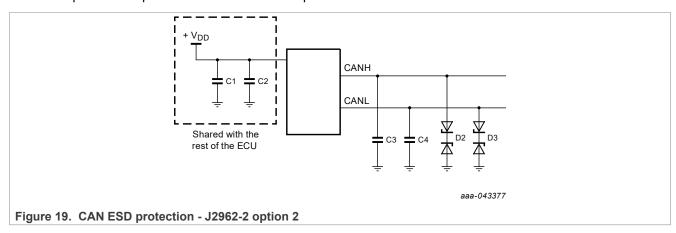

# 5.9 CAN ESD protection

CAN ESD protection option 2 is recommended to pass J2962-2 certification for the American market.

Table 8. CAN ESD protection component list

| Option No.                                                      | Component name | Label  | Value                                 |  |  |

|-----------------------------------------------------------------|----------------|--------|---------------------------------------|--|--|

| 2                                                               | Capacitor      | C3, C4 | 82 pF, 100 V ±5 % <sup>(1)</sup>      |  |  |

|                                                                 | Zener          | D2, D3 | NXP PESD1CAN, (in same SOT23 package) |  |  |

| Note 1. Over the entire voltage and temperature operating range |                |        |                                       |  |  |

FS6500 and FS4500 safe system basis chip hardware design and product guidelines

# 6 FS6500 and FS4500 external components

This section is based on <u>Figure 4</u> and <u>Figure 5</u>, and details how to select the external components. It also proposes some references and tolerances needed to ensure optimal performance of the system. All the recommended components are based on NXP use case validations.

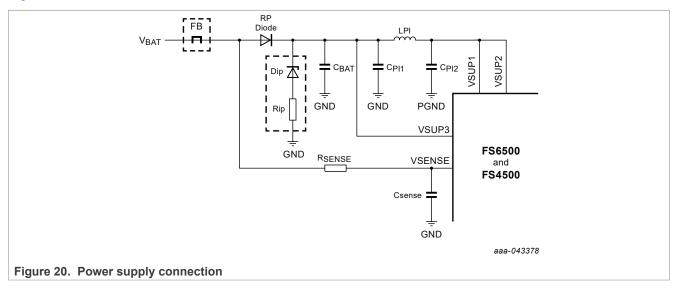

## 6.1 FS6500 and FS4500 power supply

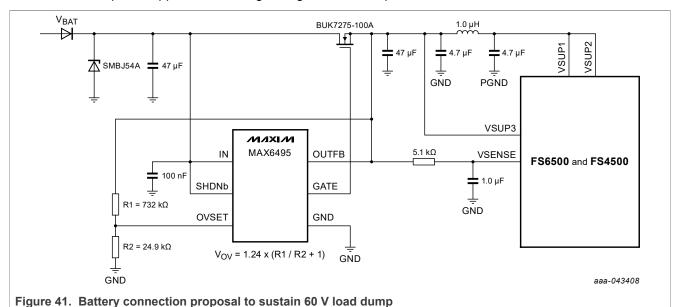

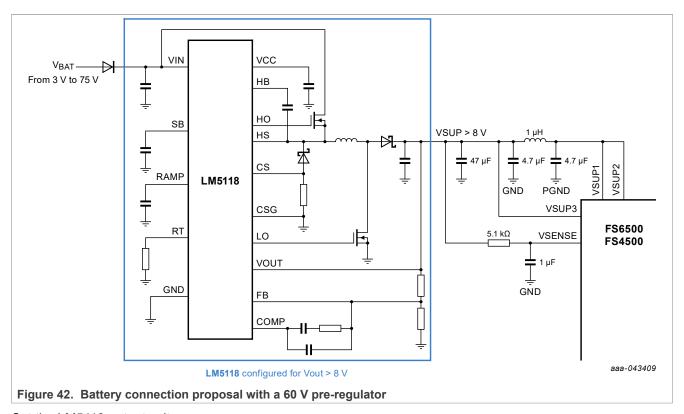

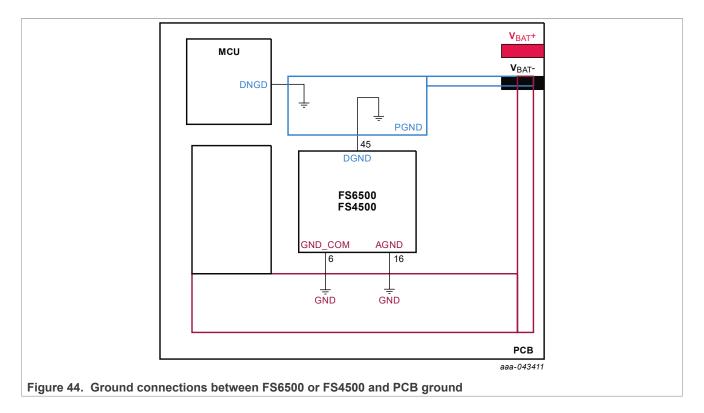

Power to the FS6500 and FS4500 is provided by the VSUP1, VSUP2, and VSUP3 supply pins. An external reverse battery protection diode must be connected between the VBAT external battery input and the capacitor input filter.

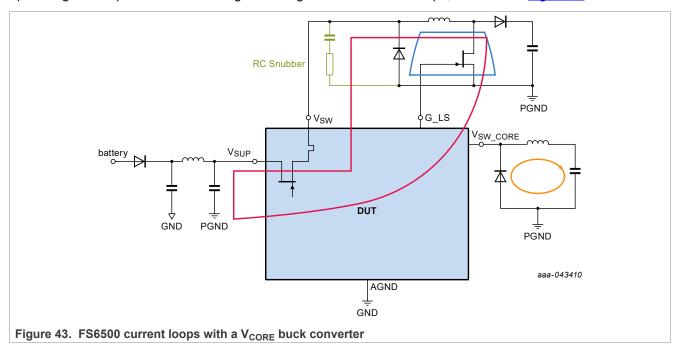

A PI filter is implemented to avoid current switching noises coming from DC/DC converters to be propagated to  $V_{BAT}$  and  $V_{SUP3}$  supplies. For that reason, VSUP3 must be connected before the PI filter to deliver a clean supply to the FS6500 and FS4500, de-correlated from the VSUP1 and VSUP2 dedicated to the VPRE SMPS pre-regulator.

The  $C_{BAT}$  capacitor between the VBAT and VSUP pins must be greater than 47  $\mu$ F, to limit the slew rate on VSUP pins, in case of high transients. The resistor connected to VSENSE is mandatory to limit the current at the pin, in case of high transients (positive and negative).

If the application has to sustain ISO pulses on VBAT in LPOFF mode, the connection of a an external zener diode ( $D_{IP}$ ) and a serial resistor to ground ( $R_{IP}$ ) is needed to discharge the  $C_{BAT}$  capacitor.

If the application has to pass J2962 certification for American automotive market, a ferrite bead (FB) on the  $V_{BAT}$  line is recommended to pass the radiated emission test. The FS6500 and FS4500 power connection is shown in Figure 16.

The PI filter has a resonance frequency at

$$f_res = \frac{1}{2\pi \times \sqrt{LPI \cdot CPI}}$$

with a filtering slope at -40 dB per decade.

The  $V_{PRE}$  pre-regulator is the main contributor to the noise reported to  $V_{BAT}$ . The resonance frequency of the PI filter must be f\_res <  $V_{PRE}$  switching frequency (f\_res <  $F_{SWPRE}$  < 440 kHz). LPI = 1.0  $\mu$ H and CPI = 4.7  $\mu$ F,

AN5238

FS6500 and FS4500 safe system basis chip hardware design and product guidelines

giving a resonance frequency f\_res = 73 kHz. The resonance frequency of the PI filter can be adjusted at the application level to improve EMC performances.

Table 9. Power supply component list

| Component          | Value      | Reference/manufacturer proposal                                                                                                                               | Ground connection |

|--------------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| FB                 |            | MPZ1608S101ATAH0/TDK                                                                                                                                          |                   |

| RP Diode           |            | PMEG10030ELP/NXP ( $I_F$ = 3 A, $V_R$ = 100 V)<br>PMEG10020ELR/NXP ( $I_F$ = 2A, $V_R$ = 100 V)<br>SBRS81100T3G/On Semiconductor ( $I_F$ = 2A, $V_R$ = 100 V) |                   |

| Dip                | Zener 30 V | BZX384C/NXP                                                                                                                                                   |                   |

| R <sub>IP</sub>    | 1.0 kΩ     |                                                                                                                                                               | GND               |

| C <sub>BAT</sub>   | 47 μF      | EMVH500ADA470MJA0G/NIPPON CHEMI-CON CORPORATION                                                                                                               | GND               |

| CPI1               | 4.7 µF     | GCM32ER71H475K/Murata                                                                                                                                         | GND               |

| LPI                | 1 μH       | B82472G6102M000/TDK-EPCOS                                                                                                                                     |                   |

| CPI2               | 4.7 µF     | GCM32ER71H475K/Murata                                                                                                                                         | PGND              |

| R <sub>SENSE</sub> | 5.1 ΚΩ     |                                                                                                                                                               |                   |

| C <sub>SENSE</sub> | 1.0 µF     | CGA5L3X7R1H105K/Murata                                                                                                                                        | GND               |

# 6.2 FS6500 and FS4500 V<sub>PRE</sub> pre-regulator

The V<sub>PRE</sub> pre-regulator delivers a 6.5 V typical output voltage.

- In buck only configuration, the Gate LS pin must be tied to PGND or GND.

- In buck-boost configuration, an external logic level MOSFET (N-type) must be connected to the Gate\_LS pin and an additional diode is needed, as shown in <a href="Figure 6">Figure 6</a>.

The two  $C_{OUT\_VPRE}$  capacitors in parallel can be replaced by one 47  $\mu F$  capacitor, but with always ESR < 100  $m\Omega$ . The  $V_{PRE}$  pre-regulator connections are shown in Figure 17.

# 6.2.1 V<sub>PRE</sub> main characteristics

- V<sub>SUPMAX</sub> = 36 V

- V<sub>SUPMIN</sub> = 2.7 V

- V<sub>PRE</sub> = 6.5 V

- V<sub>PRE MAXRATING</sub> = 8.0 V

AN5238

All information provided in this document is subject to legal disclaimers

© 2024 NXP B.V. All rights reserved.

### FS6500 and FS4500 safe system basis chip hardware design and product guidelines

- I<sub>PREMAX</sub> = 2.0 A

- I<sub>PREMIN</sub> = 0.3 A (in boost mode when V<sub>SUP</sub> < 4.0 V)</li>

- F<sub>SWPRE</sub> = 440 kHz

### 6.2.2 L\_V<sub>PRE</sub> calculation

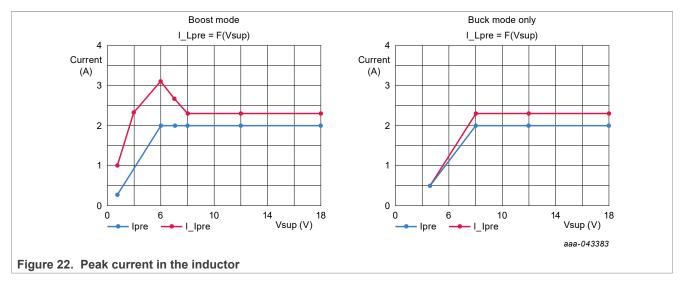

- Inductor current ripple: I<sub>RIP</sub> = K x I<sub>PREMAX</sub> = 0.6 A with K = 0.3 (30% of I<sub>PRE</sub>)

- Buck configuration:

$$LVpre = \frac{(Vpre \times (Vsupmax - Vpre))}{K \times Vsupmax \times Ipremax \times Fswpre}$$

· Boost configuration:

$$LVpre = \frac{(Vsupmin^2 \times (Vpre-Vsupmin))}{K \times Vpre^2 \times Ipremin \times Fswpre}$$

- From calculation,  $L_V_{PRE}$  = 20.6  $\mu H$  in buck mode and  $L_V_{PRE}$  = 16.6  $\mu H$  in boost mode

- From normalized value, recommended L\_V<sub>PRE</sub> = 22 μH

- The current discharge slope in the inductor is:

$$\frac{-Vpre}{LVpre}$$

with  $V_{PRE}$  = 6.5 V and  $L_{V_{PRE}}$  = 22  $\mu$ H,  $I_{SLOPE}$  = -300 mA/ $\mu$ s.

V<sub>PRE</sub> is a current mode controlled SMPS with a -500 mA/µs internal slope compensation to avoid subharmonic oscillations when the duty cycle is > 50%. A minimum L\_V<sub>PRE</sub> must be chosen to maintain the current discharge slope in the inductor lower than the internal slope compensation.

# 6.2.3 L\_V<sub>PRE</sub> selection

- · Must be shielded inductor

- Inductor value: 22 µH

# FS6500 and FS4500 safe system basis chip hardware design and product guidelines

- · Buck mode only:

- rated current: I<sub>R</sub> > I<sub>PREMAX</sub> > 2.0 A

- saturation current:  $I_{SAT} > I_R + (I_{RIP}/2) > 2.3 A$

- Buck/boost mode (80 % efficiency considered in boost mode):

- rated current: I<sub>R</sub> > I<sub>SUP</sub> > 2.7 A

- saturation current:  $I_{SAT} > I_{SUP} + (I_{RIP}/2) > 3.1 A$

- Serial resistance: DCR < 100 mΩ</li>

# 6.2.4 D\_V<sub>PRE</sub> selection

- · Schottky diode is recommended

- lower forward voltage drop (V<sub>F</sub>) reduces power dissipation

- lower parasitic capacitor improves EMC performance

- Reverse voltage: V<sub>R</sub> ≥ V<sub>SUPMAX</sub> ≥ 36 V

- Average rectified forward current: I<sub>F</sub> > I<sub>PREMAX</sub> + (I<sub>RIP</sub> /2) > 2.3 A

- Power dissipation: P<sub>D</sub> = V<sub>F</sub> x I<sub>F</sub>

### 6.2.5 LS\_BB selection

- Must be logic level N-type MOSFET

- Low R<sub>DS(on)</sub> reduces conduction losses

- Drain source voltage:  $V_{DS} > V_{PRE\_MAXRATING} + V_{F(D\_BB)} > \sim 9.0 \text{ V}$

- Drain current: I<sub>DS</sub> > I<sub>PREMAX</sub> + (I<sub>RIP</sub> /2) > 2.3 A

- · Gate source capacitance:

$$Cgs = \frac{(Iboost \times Trise)}{Vpre}$$

With  $I_{BOOST}$  = 300 mA and  $t_{RISE}$  = 30 ns,  $C_{GS}$  = 1.5 nF.

FS6500 and FS4500 safe system basis chip hardware design and product guidelines

# 6.2.6 D\_BB selection

- · Schottky diode is recommended

- lower forward voltage drop (V<sub>F</sub>) reduces power dissipation

- lower parasitic capacitor improves EMC performance

- Reverse voltage: V<sub>R</sub> ≥ V<sub>PRE MAXRATING</sub> ≥ 8.0 V

- Average rectified forward current: I<sub>F</sub> > I<sub>PREMAX</sub> + (I<sub>RIP</sub> /2) > 2.3 A

- Power dissipation: P<sub>D</sub> = V<sub>F</sub> x I<sub>F</sub>

### 6.2.7 Output capacitors

- Minimum 40  $\mu$ F ceramic capacitor(s) with low ESR << 100 m $\Omega$  is recommended

- The ESR of the output capacitor is one of the main contributor to the output voltage ripple. The ripple generated by the ESR is proportional to its value (ESR \* I<sub>RIP</sub>). A high ripple can disturb the regulation loop.

- · Low ESR capacitors reduce the ripple, avoid instability and lower EMI.

### 6.2.8 Snubber

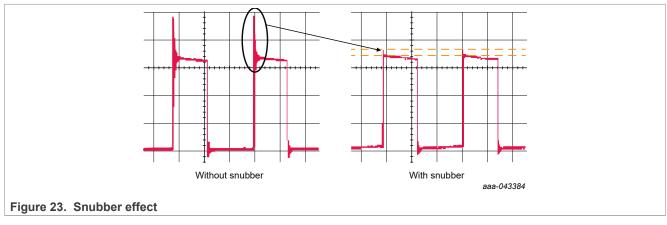

In asynchronous SMPS, a freewheeling diode is used to discharge the inductor (during recirculation phase). When this diode is turned OFF (corresponding to when the MOS is turned ON), some oscillations happen due to the leakage inductance and output capacitance of the diode plus the PCB layout parasitic. A RC snubber in parallel to the diode dampens these oscillations and lower EMI. The snubber improves EMI but impact efficiency lowering the turn ON and OFF switching times. Its implementation is a compromise between EMI performance and Efficiency. The damping effect of a well designed snubber is shown in Figure 19.

is the oscillation frequency where L<sub>P</sub> and C<sub>P</sub> are the parasitic inductor/capacitor mainly depending on the diode and the PCB layout.

$$Fring = \frac{1}{2\pi \times \sqrt{Lp \times Cp}}$$

- A good starting point to design the snubber is to take:

- C<sub>P</sub> = diode output capacitance from diode data sheet

- $-C_{SNUB} = 5 \times C_{P}$

- Calculate Lp from Fring measured by oscilloscope

\_

FS6500 and FS4500 safe system basis chip hardware design and product guidelines

$$Rsnub = 1 / 2 \times \sqrt{(Lp) / (Cp)}$$

Try the snubber calculated values or try the values provided for V<sub>PRE</sub> and V<sub>CORE</sub> in this application note and adjust them experimentally to compensate the PCB layout parasitic.

# 6.2.9 V<sub>PRE</sub> RC snubber

- RC snubber in parallel to the freewheeling diode D\_V<sub>PRE</sub> is recommended to dampen the voltage ringing at the SW\_PRE pin and reduce high frequency emissions.

- C<sub>SNUB\_VPRE</sub> and R<sub>SNUB\_VPRE</sub> values must be tuned according to board and layout performance to take into account parasitic inductance/capacitance.

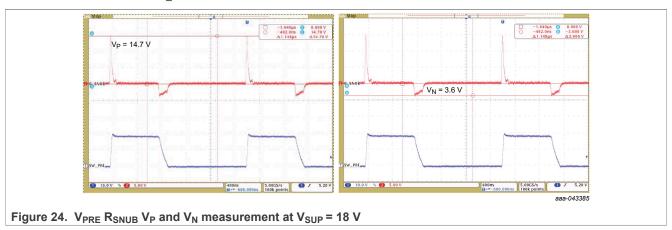

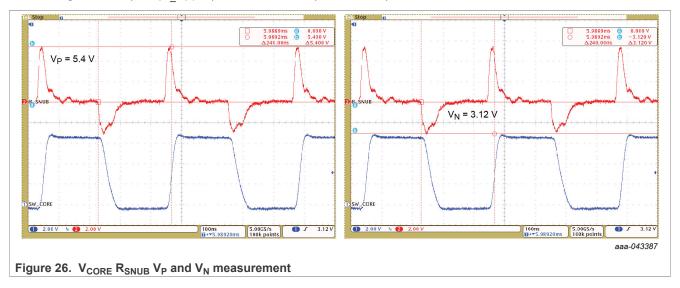

- The current pike in R<sub>SNUB\_VPRE</sub> at each V<sub>PRE</sub> cycle is important. R<sub>SNUB\_VPRE</sub> resistor must be at least a 1/4 W resistor type for V<sub>SUPMAX</sub> = 18 V. P(R<sub>SNUB\_VPRE</sub>) = 1/2 \* C<sub>SNUB\_VPRE</sub> \* (V<sub>P</sub><sup>2</sup> + V<sub>N</sub><sup>2</sup>) \* F<sub>SW</sub> where V<sub>P</sub> and V<sub>N</sub> are the voltage levels (positive and negative) measured at the resistor R<sub>SNUB\_VPRE</sub> (see <u>Figure 20</u>).

- From Figure 20, P(R<sub>SNUB VPRE</sub>) = 1/2 \* 4.7 nF \* (14.7<sup>2</sup> + 3.6<sup>2</sup>) \* 440 kHz = 0.237 W.

### 6.2.10 Continuous mode

- V<sub>PRE</sub> must work in continuous mode (current in the inductor always > 0) to provide a good load transient response and good EMC performance. V<sub>PRE</sub> is continuous when I<sub>PRE</sub> > 180 mA (for a 22 μH inductor).

- $I_{PRE} = I_{CCA} + I_{AUX} + I_{CAN} + (I_{CORE} * V_{CORE} / V_{PRE} / V_{CORE\_EFF})$  where  $V_{CORE\_EFF}$  is  $V_{CORE}$  efficiency (~85 % at 3.3 V and ~70 % at 1.2 V)

### 6.2.11 Component list proposal

Table 10. V<sub>PRE</sub> supply component list

| Component              | Value  | Reference/manufacturer proposal                                                                                                                                                                                                | Ground connection |

|------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| C <sub>SNUB_VPRE</sub> | 2.2 nF | Snubber component values to be adjusted at PCB level                                                                                                                                                                           |                   |

| R <sub>SNUB_VPRE</sub> | 8.0 Ω  | Shubber component values to be adjusted at FOB level                                                                                                                                                                           | PGND              |

| C <sub>BOOT_PRE</sub>  | 100 nF | CGA2B3X7R1H104K050BB/TDK                                                                                                                                                                                                       |                   |

| D_V <sub>PRE</sub>     |        | - PMEG4020EP/NXP ( $I_F$ = 2.0 A, $V_R$ = 40 V)<br>- PMEG4030EP/NXP ( $I_F$ = 3.0 A, $V_R$ = 40 V)<br>- SS24T3G/On Semiconductor ( $I_F$ = 2.0 A, $V_R$ = 40 V)<br>- MBRS340T3/ON Semiconductor ( $I_F$ = 3.0 A, $V_R$ = 40 V) | PGND              |

### FS6500 and FS4500 safe system basis chip hardware design and product guidelines

Table 10. V<sub>PRE</sub> supply component list...continued

| Component             | Value          | Reference/manufacturer proposal                                                                                                                                                                                                | Ground connection |

|-----------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| L_V <sub>PRE</sub>    | 22 µH          | - B82464G4223M/TDK-EPCOS ( $I_R$ = 2.25 A, $I_{SAT}$ = 2.5 A)<br>- MSS1278-223MLB/COILCRAFT ( $I_R$ = 4.0 A, $I_{SAT}$ = 6.0 A)                                                                                                |                   |

| LS_BB                 |                | - BUK9M24-60E/NXP<br>- BUK9832-55A/NXP                                                                                                                                                                                         | PGND              |

| D_BB                  |                | - PMEG4020EP/NXP ( $I_F$ = 2.0 A, $V_R$ = 40 V)<br>- PMEG4030EP/NXP ( $I_F$ = 3.0 A, $V_R$ = 40 V)<br>- SS24T3G/On Semiconductor ( $I_F$ = 2.0 A, $V_R$ = 40 V)<br>- MBRS340T3/ON Semiconductor ( $I_F$ = 3.0 A, $V_R$ = 40 V) |                   |

| C <sub>OUT_VPRE</sub> | 10 μF<br>22 μF | Ceramic capacitor ESR < 100 mΩ - 4x CGA6M3X7R1C106K/TDK - 2x GCM32ER71C226ME19/MURATA                                                                                                                                          | PGND              |

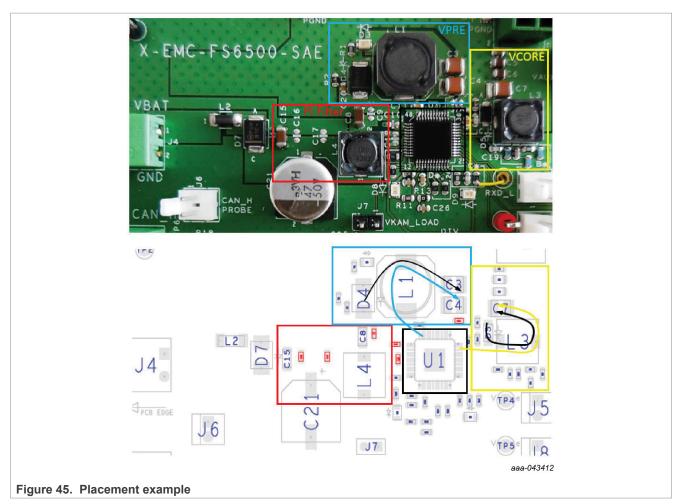

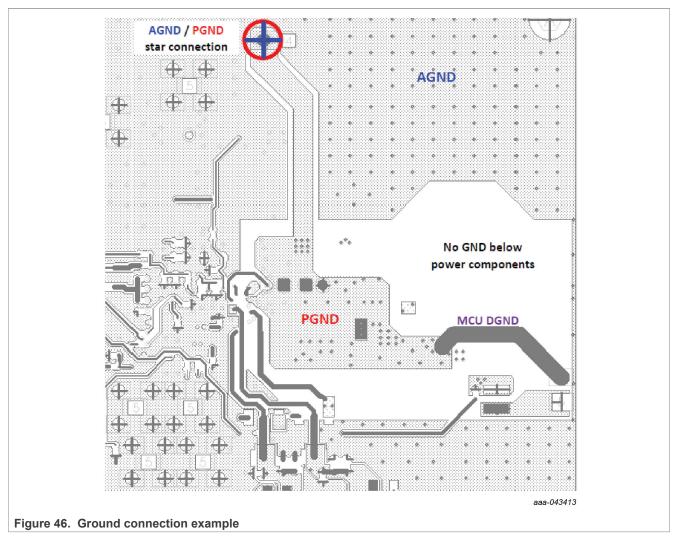

# 6.3 FS6500 V<sub>CORE</sub> supply regulator