## **NXP Semiconductors**

**Application Note**

### Document Number: AN5108 Rev. 1.0, 7/2016

## **Clock calibration**

for the dual SOIC 24 V high-side switch family

## 1 Introduction

This application note describes the clock calibration and how to use a reference time slot of the MC06XS4200, MC10XS4200, MC20XS4200, MC20XS4200, and MC50XS4200 devices. These intelligent high-side switches are designed to be used in 24 V systems such as trucks, busses, and special engines. They can be used in some industrial and 12 V applications as well. The low  $R_{\text{DS(on)}}$  channels can control incandescent lamps, LEDs, solenoids, or DC motors. Control, device configuration, and diagnostics are performed through a 16-bit SPI interface, allowing easy integration into existing applications. For a complete feature description, refer to the individual data sheets.

#### **Contents**

| 1 | Introduction               | . 1 |

|---|----------------------------|-----|

| 2 | Internal clock calibration | . 2 |

| 3 | Timing specification       | . 3 |

| 4 | Reference documents        | . 4 |

| 5 | Revision history           | Ę   |

### 2 Internal clock calibration

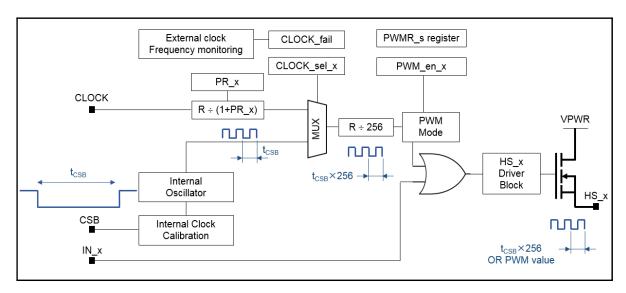

Each channel has a fully independent PWM module activated by setting PWM\_en\_s. It modulates an internal or external clock signal. Setting Clock\_int\_s = 1 (bit D6 of the OCR\_s register) activates the internal clock, and setting Clock\_int\_s = 0 activates the external clock. By using a reference time slot (usually available from an external microcontroller), the period of each of the internal PWM clocks can be changed or calibrated.

Calibration of the default period =  $1/f_{PWM(0)}$  reduces its maximum variation from about  $\pm 30\%$  to  $\pm 10\%$ . The programming procedure is as follows:

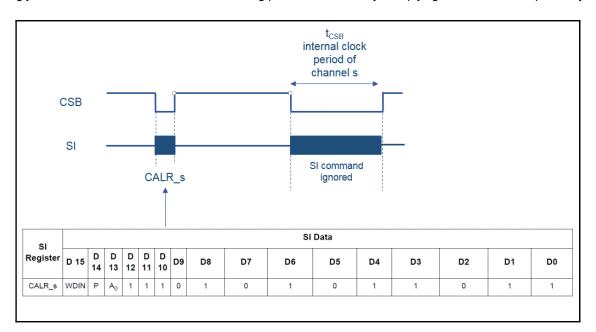

- · Initialization by sending a dedicated word to the SI-CALR register.

- Next, the device sets the new value of the switching period in two steps. First it measures the time elapsed between the first falling

edge on the CSB pin and the next rising edge on the CSB pin (t<sub>CSB</sub>). Then it changes the value of the internal clock period

accordingly. The actual value of the channel's switching period is obtained by multiplying the internal clock period by 256.

Figure 1. Clock calibration sequence

Figure 2. Internal and external clock operation

Clock calibration, Rev. 1.0

## 3 Timing specification

The timing specification related to clock calibration is detailed in Table 5. of each device datasheet. See Reference documents.

Table 1. Calibration timing specification

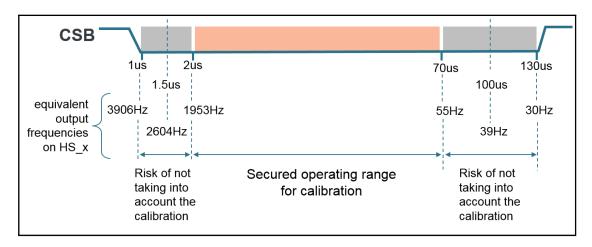

| Minimum required low time during calibration of the internal clock through CSB | t <sub>CSB(MIN)</sub> | 1.0 | 1.5 | 2.0 | μs |

|--------------------------------------------------------------------------------|-----------------------|-----|-----|-----|----|

| Maximum allowed low time during calibration of the internal clock through CSB  | $t_{CSB(MAX)}$        | 70  | 100 | 130 | μs |

<u>Figure 3</u> provides a description of specified timings converted to frequencies, as well as frequency ranges where the frequency target is preferred.

Figure 3. Calibration timing specification

When the duration of the negative CSB pulse is outside a predefined time slot (from  $t_{CSB(MIN)}$ ) to  $t_{CSB(MAX)}$ ), the calibration event is ignored and the internal clock frequency remains unchanged. If the value ( $t_{PWM(0)}$ ) has not been previously calibrated, it remains at its default level.

## 4 Reference documents

### Table 2. AN5108 reference documents

| Description           | URL                                                           |

|-----------------------|---------------------------------------------------------------|

| MC06XS4200 Data Sheet | http://www.nxp.com/files/analog/doc/data_sheet/MC06XS4200.pdf |

| MC10XS4200 Data Sheet | http://www.nxp.com/files/analog/doc/data_sheet/MC10XS4200.pdf |

| MC20XS4200 Data Sheet | http://www.nxp.com/files/analog/doc/data_sheet/MC20XS4200.pdf |

| MC22XS4200 Data Sheet | http://www.nxp.com/files/analog/doc/data_sheet/MC22XS4200.pdf |

| MC50XS4200 Data Sheet | http://www.nxp.com/files/analog/doc/data_sheet/MC50XS4200.pdf |

# 5 Revision history

| Revision | Date   | Description of changes                 |

|----------|--------|----------------------------------------|

| 1.0      | 4/2015 | Initial release                        |

| 1.0      | 7/2016 | Updated to NXP document form and style |

#### How to Reach Us:

Home Page: NXP.com

Web Support:

http://www.nxp.com/support

Information in this document is provided solely to enable system and software implementers to use NXP products. There are no expressed or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document. NXP reserves the right to make changes without further notice to any products herein.

NXP makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does NXP assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation, consequential or incidental damages. "Typical" parameters that may be provided in NXP data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must be validated for each customer application by the customer's technical experts. NXP does not convey any license under its patent rights nor the rights of others. NXP sells products pursuant to standard terms and conditions of sale, which can be found at the following address:

http://www.nxp.com/terms-of-use.html.

NXP, the NXP logo, Freescale, the Freescale logo, and SMARTMOS are trademarks of NXP B.V. All other product or service names are the property of their respective owners. All rights reserved.

© 2016 NXP B.V.

Document Number: AN5108

Rev. 1.0 7/2016