# Freescale Semiconductor

**Application Note**

Document Number: AN4688

Rev. A, 01/2013

# Sampling Audio with ADC on Kinetis KwikStik

ADC, DMA and LCD demo using Processor Expert and Peripheral Initialization Components.

.

Periodical sampling of analog signal is a common task required in many microcontroller (MCU) applications. The Kinetis MCUs provide analog to digital converters (ADCs) with hardware sample triggering that can be easily leveraged for this task. This application note describes the design of an application that uses Processor Expert to configure the ADC and other peripherals to perform periodic sampling of an analog signal obtained from a microphone on a KwikStik device. Its on-board matrix LCD presents the sampled data as a waveform. The source code of the example is available in the archive file AN4688SW.zip.

This note assumes the use of CodeWarrior for MCUs v10.3 or later.

### Contents

| 1 | Introduction             |    |

|---|--------------------------|----|

| 2 | Hardware                 | 2  |

|   | Description of Operation |    |

|   | Development tools        |    |

|   | Components configuration |    |

|   | Source Code              |    |

| 7 | Conclusion               | 13 |

|   | Revision History         |    |

### 1 Introduction

Processor Expert is a rapid application development tool that provides a quick way to setup initialization and runtime control of a Freescale MCU and its on-chip peripheral devices. Peripheral Initialization components go a step further by providing pre-configured drivers for these peripheral devices. The Code Warrior for MCUs v10.x tools and Microcontrollers Driver Suite provide support for the Kinetis MCUs.

### 2 Hardware

The example project uses a Kinetis KwikStik. It is a development board used to evaluate, develop, and debug software written for Kinetis MCUs.

The KwikStik board features:

- ➤ 32-bit K40X256 MCU that contains 256KB flash memory and 256KB FlexMemory

- ➤ LCD screen with 306 segments

- ➤ 3.5 mm audio output jack and two micro USB connectors

- Omni-directional microphone and a buzzer

- On-board J-Link USB programmer

- > Infrared communications

- ➤ Micro SD card slot.

- Capacitive touch sensing interface

- ➤ General purpose Tower plug-in (TWRPI) socket

- ➤ Manganese lithium rechargeable battery

Detailed information on the KwikStik board and Kinetis K40 MCU are available at: http://www.freescale.com/kwikstik.

# 3 Description of Operation

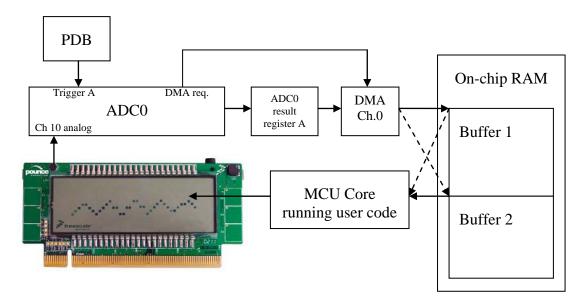

The demo application repeatedly samples a single ADC channel at a given frequency and stores the data to a memory buffer via an enhanced Direct Memory Access (eDMA) module.

ADC conversions are triggered with pulses provided continuously by the Programmable Delay Block (PDB) peripheral. After each conversion, the ADC raises a DMA request and the eDMA transfers the data from the sample register to the memory buffer. The benefit of this approach is that the CPU core is not involved with the sequence of operations: it is free to perform other tasks rather than handling an ADC sample stream.

The example code uses a double buffering technique, which means that as one half of the buffer fills with ADC values, the application code processes the accumulated data in other half. When one half the buffer fills with new samples, an interrupt informs the MCU that the buffer end has been reached. Incoming data samples are then transferred to the other half of the buffer, while the application code

Sampling Audio with ADC on Kinetis KwikStik

2

starts processing the newly-filled half of the buffer. The application code reads the sampled values and displays them as a waveform.

Figure 1 shows the basic signal and data flow in the demo application.

Figure 1. Block Diagram of Signal and Data Flow

# 4 Development tools

The demo application is created using Processor Expert, a rapid application design tool. Processor Expert enables the quick design and implementation of a microcontroller application. The application is built using Processor Expert's Embedded Components. These components are building blocks that generate source code files that contain the initialization and driver code for the selected MCU and its on-chip peripherals.

For the Kinetis K40 platform, there are the following types of Embedded Components available:

- ➤ **Peripheral Initialization Components** These components generate the initialization code for a peripheral. The interface of these components gives a user access to all possible features that can be initialized. By pointing and clicking, you can active specific peripheral features and configure them.

- ➤ **Logical Device Drivers** (**LDD**) These components provide basic initialization code and drivers for runtime use of the peripherals.

To achieve maximum throughput of the ADC data flow, the application's Peripheral Initialization Components are used to configure ADC, eDMA and PDB. Peripheral Initialization components are used because the required access to certain low-level hardware specific features is not available in LDD components.

Processor Expert is available as a plug-in for CodeWarrior for MCUs or within the standalone Microcontroller Driver Suite. For the compilation and debugging of the demo, CodeWarrior for MCUs v10.2 was used.

For more details on the development tools, see the website <a href="http://www.freescale.com">http://www.freescale.com</a>.

# 5 Components configuration

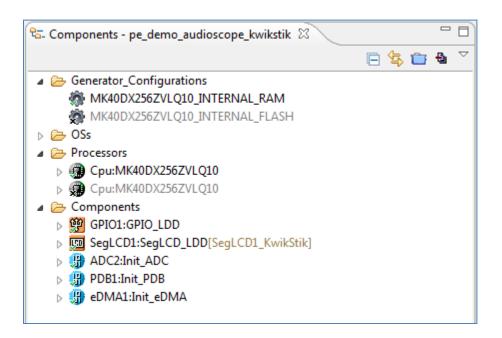

Table 1show the components used in the example application project.

| Embedded Component    | Task                                                           |

|-----------------------|----------------------------------------------------------------|

| CPU (MK40DX256ZVLQ10) | Configures basic settings of K40 MCU on the KwikStik board     |

| GPIO_LDD              | Provides driver for a digital pin for testing purposes         |

| SegLCD_LDD            | Provides a simple LCD driver for the display on the KwikStik   |

| Init_ADC              | Provides ADC (Analog to Digital Converter) initialization code |

| Init_PDB              | Provides PDB (Programmable Delay Block) initialization code    |

| Init_eDMA             | Provides eDMA (Direct Memory Access) initialization code       |

Table 1. Summary of components used in the example application

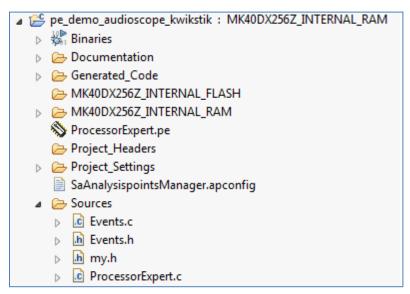

Figure 2 presents the **CodeWarrior Projects** view of the example program in CodeWarrior for MCUs v10.2. It shows the source files and the various Processor Expert components used to implement the functions of the example program.

Figure 2. CodeWarrior Project Structure of Application Using Processor Expert

Figure 3. Processor Expert components used if the project

The following subsections describe important settings of the individual components. You can view complete settings of in the Processor Expert Component Inspector after opening the project and selecting the component.

**Note**: To access component settings in the **CodeWarrior Project** view, click on the ProcessorExpert.pe object in the **CodeWarrior Projects** view in the project. Then select the component in the **Components** view and see the settings in Inspector view. For more information on how to change these settings, refer to the Processor Expert User Guide.

### 5.1 CPU

The CPU component configures the MCU to use the external 50MHz crystal on the KwikStik board. The core clock is initialized to run at 100MHz.

### 5.2 GPIO\_LDD

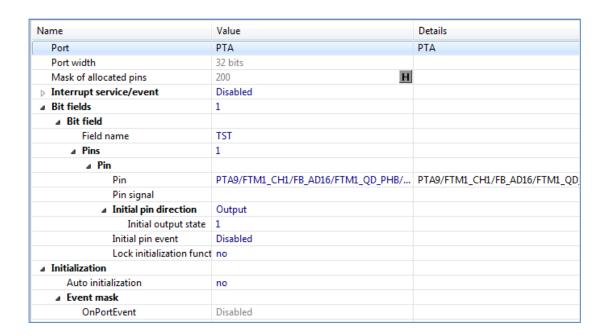

The GPIO\_LDD component provides a driver code for the PTA9 pin. This pin is accessible on the KwikStik Tower connector and is used for debugging and test purposes (for example, measuring the sampling frequency).

Figure 4. GPIO\_LDD settings in Component Inspector

### 5.3 Init PDB

The Init\_PDB component initializes and configures the PDB. The PDB provides controllable delays from either an internal or external trigger, or a programmable interval tick. These can be used as hardware trigger inputs for the ADCs and/or generate the interval triggers to DACs.

In this example application, the *PDB channel 0* is configured by Init\_PDB component with the following settings:

- Prescaler and Divider are set to 1 so the counter input frequency is 50MHz.

- $\triangleright$  The counter modulus is set to 6250, which makes the period in 125 μ<u>S</u>. This value is equal to sampling frequency 8 kHz.

- Enabled *Continuous mode* means that the counter will continue running in a loop once it's started.

- ➤ Input trigger select is set to *PDB\_SWTRIG* which means that PDB is triggered (started) by software only. The PDB starts to provide trigger pulses to ADC after the PDB1\_Init() function is called in main().

- ➤ Only *trigger A* of the *ADC0* is *enabled* and no delay is configured for it (delay with value 0).

Figure 5 shows the Component Inspector interface for the PDB, and how the settings are described appear in it.

| Name                   | Value          | Details    |

|------------------------|----------------|------------|

| Device                 | PDB0           | PDB0       |

|                        |                |            |

| Clock gate             | Enabled        |            |

|                        |                |            |

| Prescaler              | divide by 1    |            |

| Divider                | divide by 1    |            |

| Counter frequency      | 50000.0000 kHz |            |

| Modulus                | 6250 E         |            |

| Counter period         | 125.000 us     |            |

| Continuous mode enable | Continuous     |            |

| Interrupt delay value  | 0              |            |

| Interrupt delay        | 0.000 us       |            |

| Load Mode              | Immediate      |            |

|                        |                |            |

|                        |                |            |

|                        |                |            |

|                        |                |            |

| Trigger A enable       | Enabled        |            |

| Output select A        | Delay only     |            |

| Back to Back           | Disabled       |            |

| Trigger delay A val    | 0              |            |

| Trigger A delay        | 0.000 us       |            |

|                        |                |            |

|                        |                |            |

| Channel for DAC        |                |            |

| ▶ Pulse outs           |                |            |

|                        |                |            |

| Input trigger select   | PDB_SWTRIG     | PDB_SWTRIG |

|                        |                |            |

| △ Initialization       |                |            |

| Load OK                | yes            |            |

| Enable PDB             | yes            |            |

| Call Init method       | no             |            |

Figure 5. Init\_PDB settings in Component Inspector

### 5.4 Init ADC

The MCU features a 16-bit analog-to-digital converter (ADC). It uses a successive approximation conversion algorithm and supports up to four pairs of differential and 24 single-ended inputs. It offers a hardware average function, selectable hardware conversion trigger, selectable voltage reference and many other advanced features.

In the example application the Init\_ADC component is configured to initialize the ADC converter (ADC0) the following way:

- Result data format is 16-bit unsigned.

- Conversion mode is *Single*. (That is, every single measurement is started by a trigger pulse).

- ADC clock is set to use the *Bus clock* with Prescaler of 8. The resulting conversion time is 16.9 μs.

- Conversion trigger is hardware (HW).

- ➤ HW average is *Enabled* with HW average length 4 samples.

- > Channel 10 single input is *enabled*. This channel input is connected to on-board microphone.

- ➤ Trigger A is *enabled*. Trigger A source is set to *PDB0\_CH0\_TriggerA*.

- > Interrupt request is *Disabled*.

- > DMA request is Enabled.

- ➤ Initial channel select for trigger A is *Channel 10*. This channel is connected to the on-board microphone.

| Name                                 | Value                         | Details            |

|--------------------------------------|-------------------------------|--------------------|

| Device                               | ADC0                          | ADC0               |

| Settings                             |                               |                    |

| Clock gate                           | Enabled                       |                    |

|                                      |                               |                    |

| Input clock select                   | Bus clock                     |                    |

| Prescaler                            | 8                             |                    |

| Frequency                            | 6250 kHz                      |                    |

| High-speed conversion                | Disabled                      |                    |

| Asynchro clock output                | Disabled                      |                    |

| Long sample time                     | Disabled                      |                    |

| Long sample time length              | 20 ADCK cycles                |                    |

| Conversion mode                      | Single                        |                    |

| Result data format                   | 16-bit right                  |                    |

| Low power mode                       | Disabled                      |                    |

| Conversion trigger                   | HW                            |                    |

|                                      |                               |                    |

| HW average                           | Enabled                       |                    |

| HW average length                    | 4 samples                     |                    |

| Single conversion time - Single-en   | •                             | 59.172 kHz         |

| Single conversion time - Differentia |                               | 44.131 kHz         |

| Additional conversion time - Single  |                               | 62,500 kHz         |

| Additional conversion time - Differ  |                               | 45.956 kHz         |

| ■ Compare settings                   |                               |                    |

| Compare                              | Disabled                      |                    |

| Compare value 1                      | 0 0                           |                    |

| Compare value 2                      | 0 <b>D</b>                    |                    |

| Relation of the CV1 to CV2           | Less than or equal            |                    |

| Compare function                     | Result < CV1                  |                    |

| Offset                               | 4 <b>D</b>                    |                    |

| Voltage reference                    | Default pin pair              |                    |

| Pins/Signals                         | o circuit piii puii           |                    |

| Channel 0                            | Disabled                      |                    |

| Channel 1                            | Disabled                      |                    |

| Chameri                              | :                             |                    |

| △ Channel 10                         | :<br>Enabled                  |                    |

| Channel 10 single input              | PTA7/FTM0_CH4/FB              | DTA7/ETMA CHA/EE   |

| b Channel 11                         | Disabled                      | PTA//FTIVIO_CH4/FE |

| > Channel 11                         | Disabled                      |                    |

| 4 Tringer A                          | Enabled                       |                    |

|                                      |                               | DDD0 CH0 Triage4   |

| Trigger A source                     | PDB0_CH0_TriggerA<br>Disabled | PDB0_CH0_TriggerA  |

| Interrupts/DMA                       | Disabled                      |                    |

|                                      | Disabled                      |                    |

| Interrupt request                    | Disabled                      |                    |

|                                      | 0 (Highest)                   |                    |

|                                      | ADCinterrupt                  |                    |

| Conversion complete A interrupt      | Enabled                       |                    |

| Conversion complete B interrupt      | Disabled                      |                    |

| DMA request                          | Enabled                       |                    |

| Initialization                       |                               |                    |

| △ ADC part triggered by trigger A    | CI 140                        |                    |

| Initial channel select A             | Channel 10                    |                    |

| Differential mode A                  | Disabled                      |                    |

| ■ ADC part triggered by trigger B    |                               |                    |

|                                      | ADC disabled                  |                    |

| Differential mode B                  | Disabled                      |                    |

| Call Init method                     | no                            |                    |

Figure 6. Init\_ADC settings in Component Inspector

Sampling Audio with ADC on Kinetis KwikStik

## 5.5 Init\_eDMA

The enhanced direct memory access (eDMA) controller can perform complex data transfers with minimal intervention from a host.

In this application the eDMA is used to transfer the results of the ADC conversion to a location in the memory buffer. Individual transfers are triggered by a DMA request signal from the ADC.

In the example application the *Init\_eDMA* component is configured to initialized eDMA the following way:

- Clock gate for DMA and DMA multiplexor are *Enabled*.

- ➤ Channel 0 is *initialized* with the following values:

- o DMA source muxing is *Enabled* and channel source is *ADCO*.

- o Data source is set to address of ADCO Result register A: (uint32\_t)&ADCO\_RA. Address offset is 0, the values is still read from the same register.

- O Data destination is initially set to the beginning of the array & Masured Values and Address offset is 2 (to increment address with 2 byte after transfer.

- o Block length is set to 2, as 16-bits (2 bytes) are transferred.

- o Major iteration count is set to 40. This is the length of one half of the buffer.

- o Transfer complete interrupt is *Enabled*.

- o Error interrupt is *Enabled*.

- The interrupts have assigned ISR names: Transfer Done 0 ISR Name:

DMA\_ADC\_DoneInterrupt

- Error ISR Name : *DMA error*

| NI                             | W-L                | D-t-1   |

|--------------------------------|--------------------|---------|

| Name                           | Value              | Details |

| Device                         | DMA                | DMA     |

|                                |                    |         |

| Clock gate for DMA             | Enabled            |         |

| Clock gate for DMA multiplexor | Enabled            |         |

| :                              |                    |         |

|                                |                    |         |

|                                | Initialize         | ADC0    |

|                                |                    |         |

| Auto disable external reque    | Disabled           |         |

| Preemption                     | Disabled           |         |

| Preempt ability                | Enabled            |         |

| Channel arbitration priority   |                    |         |

| Bandwidth control              | No stalls          |         |

| ■ DMA source muxing            |                    |         |

| Channel                        | Enabled            |         |

| Channel trigger                | Disabled           |         |

| Channel source                 | ADC0               |         |

| △ Data source                  |                    |         |

| External object declarati      | / :                |         |

| Address                        | (uint32_t)&ADC0_RA |         |

| Transfer size                  | 16-bit             |         |

| Address offset                 | 0 <b>D</b>         |         |

| Address adjustment             | 0 <b>D</b>         |         |

| Address modulo                 | Buffer disabled    |         |

| Minor loop maping              | Disabled           |         |

| Block length                   | 2 <b>D</b>         |         |

| △ Minor linking                | Disabled           |         |

| Major iteration count          | 40 <b>D</b>        |         |

| Major linking                  | Disabled           |         |

| Major link channel number      |                    |         |

| Scatter/gather processing      | Disabled           |         |

| △ Interrupts                   |                    |         |

| △ Transfer done                | B: 11 1            |         |

| Half transfer interrupt        | Disabled           |         |

| Transfer complete inter        | Enabled            |         |

| ⊿ Error                        | Enabled            |         |

| Error interrupt  • Pins        | Enabled            |         |

| → Pins  ⊿ Initialization       |                    |         |

| External request               | Enabled            |         |

| Start transfer                 | no                 |         |

| ✓ Interrupts                   | 110                |         |

| △ Transfer done 0              |                    |         |

| Interrupt request              | Enabled            |         |

| Interrupt priority             | 0 (Highest)        |         |

| ISR Name                       | DMA_ADC_DoneInte   |         |

| :                              | one intern         |         |

| △ Error                        |                    |         |

| Interrupt request              | Enabled            |         |

| Interrupt request              | 0 (Highest)        |         |

| ISR Name                       | DMA_error          |         |

| △ Initialization               | DIMA_CHO!          |         |

| Call Init method               | no                 |         |

Figure 7. Init\_ADC settings in Component Inspector

Sampling Audio with ADC on Kinetis KwikStik

### 6 Source Code

The archive AN4688SW.zip includes the full commented source code of the demo application.

The code generated by Processor Expert for individual components can be found in the folder *Generated code*. This folder is visible in Figure 2. The hand-written modules and modules intended for manual modification are placed in the *Sources* folder. What follows is a brief summary of the source files in the Sources folder:

▶ ProcessorExpert.c – This is the main Processor Expert module that contains the application code. The module supplies all of the component header files and header files required to define the information required by Processor Expert and any variables definitions. It also defines the ShowData() helper functions that display the data, and the main() function. The main() function first calls all of the individual initialization functions of the various components. After that, it spins in an endless loop where the data are displayed. For better visibility on the LCD screen, a delay is provided by displaying the contents of every tenth buffer.

```

for(;;) {

// check if DMA cycle is finished

if (Measured) {

cntr++;

// display only time after time

if (cntr > 10) {

// display data

ShowData();

cntr = 0;

}

// reset flag

Measured = FALSE;

}

}

```

> Events.c - This file contains the interrupt handler for the DMA interrupt that is invoked when the DMA buffer fulfills up:

```

PE_ISR(DMA_ADC_DoneInterrupt)

{

// Clear all DMA interrupt flags

DMA_CINT = 0x40;

// switch bufstart to other part of buffer

BufStart = ADC_BUFFER_SIZE - BufStart;

// reset destination address

DMA_TCD0_DADDR = (uint32_t)&(MeasuredValues[BufStart]);

// toggle pin

GPIO1_ToggleFieldBits(GPIOPtr, TST,1);

// toggle flag

Measured = TRUE;

}

```

There is also very simple handler for the DMA error interrupt that doesn't do any specific action except clearing the DMA interrupt flags.

```

PE_ISR(DMA_error)

{

// Clear all DMA interrupt flags

DMA_CINT = 0x40;

}

```

➤ My.h – contains basic definitions and external references to objects shared with event code in *Events.c* module.

```

// current buffer with valid values

extern volatile uint16_t BufStart;

// double buffer for values

extern uint16_t MeasuredValues[];

// flag for end of measurement

extern bool Measured;

// GPIO component reference (for testpin)

extern LDD_TDeviceData *GPIOPtr;

// size of the buffer

// must correspond to Init_EDMA property channels / channel 0 / Settings /

Major iteration count

#define ADC_BUFFER_SIZE 40

```

## 7 Conclusion

The ADC, PDB and eDMA peripherals of the Kinetis MCU provide the user the powerful means to implement various analog measurement tasks without need of any intervention from the MCU core. Processor Expert provides a valuable means to speed the development of initialization and peripheral driver code within its visual user interface.

# **8 Revision History**

### **Table 2. Revision History**

| Rev. Number | Date      | Substantive Change |

|-------------|-----------|--------------------|

| A           | 1/31/2013 | Initial creation   |

#### How to Reach Us:

#### Home Page:

www.freescale.com

#### Web Support:

http://www.freescale.com/support

#### USA/Europe or Locations Not Listed:

Freescale Semiconductor Technical Information Center, EL516 2100 East Elliot Road Tempe, Arizona 85284 +1-800-521-6274 or +1-480-768-2130 www.freescale.com/support

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) www.freescale.com/support

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064, Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor China Ltd. Exchange Building 23F No. 118 Jianguo Road Chaoyang District Beijing 100022 China +86 010 5879 8000 support.asia@freescale.com

#### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center 1-800-441-2447 or 303-675-2140 Fax: 303-675-2150 LDCForFreescaleSemiconductor@hibbertgroup.com Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale, the Freescale logo, CodeWarrior, are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. ARM is the registered trademark of ARM Limited. ARMnnn is the trademark of ARM Limited.

© Freescale Semiconductor, Inc. 2013. All rights reserved.

Document Number: AN4688 Rev. A

01/2013