## **Freescale Semiconductor**Application Note

Document Number: AN4334

Rev. 0, 03/2012

# Use of PGA on MC56F800x Interaction of PDB, PGA and ADC

by: William Jiang

**System and Application, Microcontroller Solutions Group**

### 1 Introduction

MC56F800x DSCs have two integrated Programmable Gain Amplifiers (PGA) that can amplify the differential signals by up to 32 times and convert it to the single ended signal, which is one of the on-chip ADC inputs.

On old maskset 1M53M devices, with PGA hardware trigger mode enabled in both PGAs, each Programmable Delay Block (PDB) trigger signal will cause a PGA to generate pre-trigger signal to both ADCs. This results in the ADC pre-trigger signal contention and the sample\_select signal inside the ADCs may toggle and cause the wrong ADC status and control register to control the conversion.

The new maskset devices (2M53M or newer) fixed this issue with new enhanced features and support sampling four analog signals per single hardware trigger. The applications designed for old maskset devices, can run smoothly on the new maskset devices.

This application note describes the new enhanced features of PGA and the possible valid PGA configurations for different signal sampling schemes.

#### **Contents**

| 1 | Introduction             | 1  |

|---|--------------------------|----|

| 2 | PGA new features         | 2  |

| 3 | Valid PGA configurations | 5  |

| 1 | Conclusion.              | 20 |

### 2 PGA new features

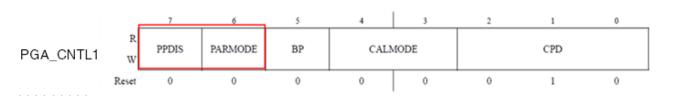

Two new control bits are added: PARMODE bit (bit6) and PPDIS bit (bit7) in PGA\_CNTL1.

Figure 1. PGA\_CNTL1 register definition

- PPDIS bit Ping-Pong disable bit:

- 1 Allow only the Pretrigger to the associated ADC to be sent.

- 0 Allow both Pretriggers to be sent to both ADCs.

- PARMODE bit -- PGA Parallel Mode bit:

- 1 PGA Parallel Mode is enabled. PGA passes PDB Pretriggers to ADC Pretrigger inputs.

- 0 PGA Parallel Mode is not enabled. PGA passes PGA generated Pretriggers to ADC Pretrigger inputs.

The PGA is designed to operate in conjunction with the ADC. The ADC has been enhanced to allow two different conversions to be pre-programmed into the ADC, using duplicate copies of the ADC status and control register 1. Conversions specified by ADCn\_ADCSC1A and ADCn\_ADCSC1B can be executed one after the other as a result of two sequential trigger events and the result will be stored in ADCn\_ADCRA and ADCn\_ADCRB respectively.

Prior to each conversion, a Pretrigger input into the ADC specifies whether ADCn\_ADCSC1A or ADCn\_ADCSC1B should control the next conversion. These Pretriggers occur one peripheral clock prior to the actual hardware trigger into the ADC. Because the PGA adds latency to each analog-to-digital conversion, ADC trigger and Pretrigger timing must be adjusted accordingly.

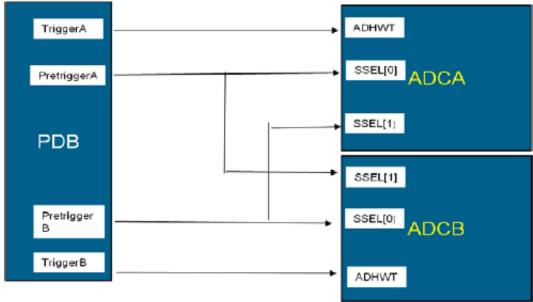

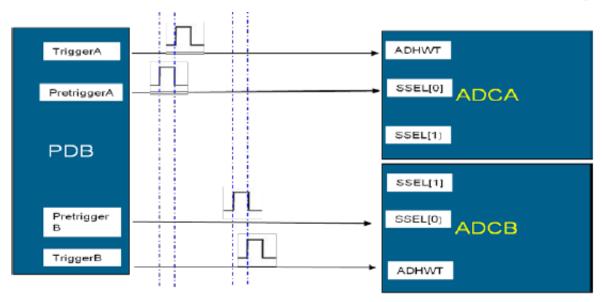

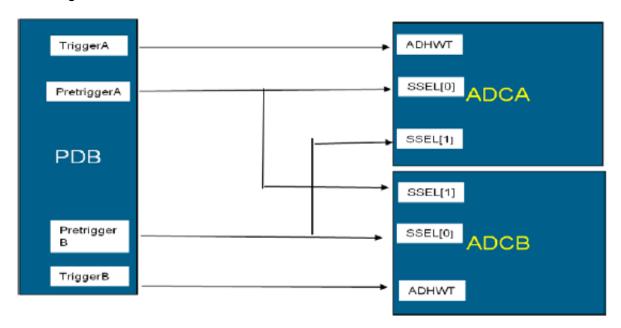

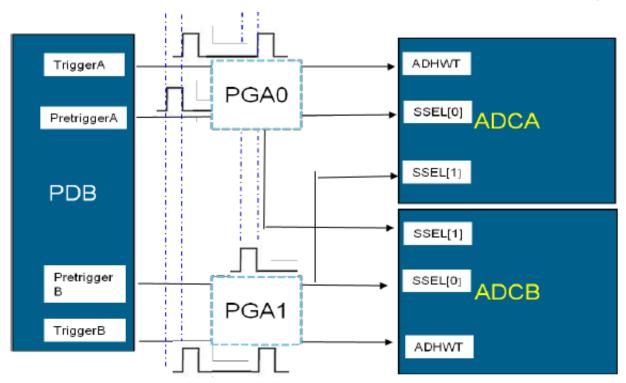

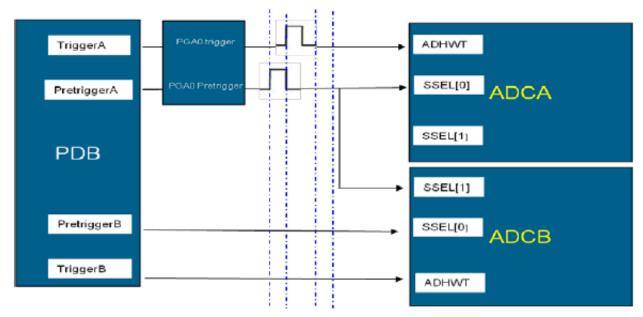

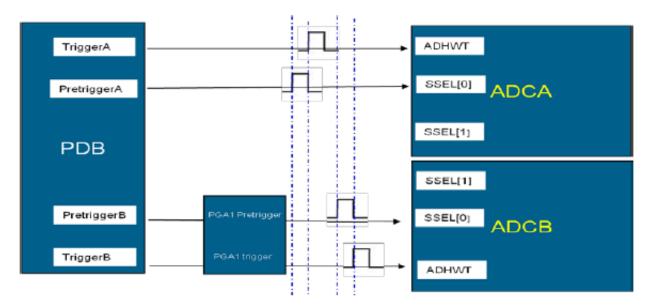

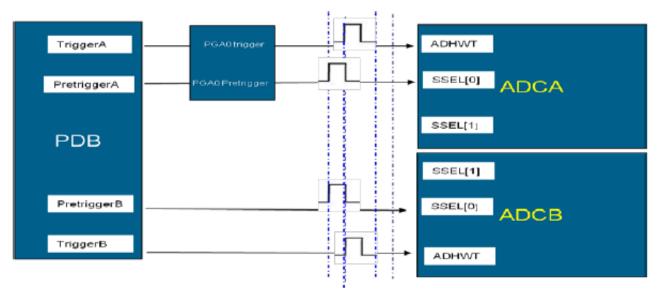

The Figure below shows the PGA diagram and the interaction between PDB, PGA and ADC. ADC A is acronym of ADC0, and ADC B is acronym of ADC1. The logics with blue circle in dotted lines are newly added. Each PGA is associated with a separate ADC module. Note that both ADCs get both Pretrigger. This allows simultaneous conversions on ADC 0 and ADC 1. If a PGA is not enabled for use, the associated PDB generated Pretriggers and trigger are passed unchanged. Likewise, use of a PGA software trigger causes the associated PDB pre-trigger to be available for use by the other ADC.

When the PGA is enabled for use with hardware trigger, it consumes the PDB generated trigger and Pretrigger, and generates new ones for use by the ADCs. One of the ADC Pretriggers generated by a PGA can be disabled to avoid contention with the other pre-trigger. Disabling both Pretriggers generated by both PGAs allow parallel independent ADC conversions.

Programmable Delay Block Pre-TriggerA TriggerA Pre-TriggerB TriggerB PGA0 PGA1 trigger from PDB trigger from PDB pre-trigge pre-trigger from PDB from PDB based based pga config pga config ADC pre-trigger ADC trigger ADHWT SSEL[0 SSEL[0] ADHWT ADC A ADC B SSEL[1 SSEL[1]

Figure 2. Interaction between PDB, PGA and ADC

The valid PGA configurations for different ADC conversion mode are listed in Table below.

There are following restrictions:

- pga\_parallel\_mode bits need to be set to the same value in both PGAs and set to 1 during ping-pong mode

- ppdis bits are used to enable parallel independent conversions on ADC\_A and ADC\_B

- swten bits cannot be set on disabled PGA

- when swten is set, the corresponding parmode bit must be set to 0

#### NOTE

- pga0en is PGA0 enable signal (PGA0\_CNTL0[EN])

- pga1en is PGA1 enable signal (PGA1\_CNTL0[EN])

- swten0 is PGA0 software trigger mode enable signal (PGA0\_CNTL0[TM])

- swten1 is PGA1 software trigger mode enable signal (PGA1\_CNTL0[TM])

- pga0\_parallel\_mode is PGA0 parallel mode disable signal PGA0\_CNTL1[PARMODE])

- pga1\_parallel\_mode is PGA1 parallel mode disable signal (PGA1\_CNTL1[PARMODE])

- ppdis0 is PGA0 ping-pong disable signal (PGA0\_CNTL1[PPDIS])

- ppdis1 is PGA1 ping-pong disable signal (PGA1\_CNTL1[PPDIS])

#### rua new features

## Table 1. Valid PGA configurations for different ADC conversion modes

| Mode                                             | Trigger<br>Setup                                   | pga0en | pga1en | swten0 | swten1 | ppdis0 | ppdis1 | parmode0 | parmode1 |

|--------------------------------------------------|----------------------------------------------------|--------|--------|--------|--------|--------|--------|----------|----------|

| One-shot<br>PGA<br>disabled                      | PDB one-<br>shot                                   | 0      | 0      | 0      | 0      | Х      | Х      | Х        | Х        |

| Ping-Pong<br>PGA<br>disabled                     | PDB two-<br>shot                                   | 0      | 0      | 0      | 0      | 0      | 0      | Х        | Х        |

| One-shot<br>PGA<br>enabled                       | PDB one-<br>shot                                   | 1      | 1      | 0      | 0      | 1      | 1      | Х        | Х        |

| Ping-Pong<br>PGA<br>enabled                      | PDB two-<br>shot                                   | 1      | 1      | 0      | 0      | 0      | 0      | 1        | 1        |

| SW/HW<br>trigger<br>parallel<br>independe<br>nt  | PGA0 SW<br>trigger<br>PDB<br>trigger B<br>one-shot | 1      | 1      | 1      | 0      | Х      | 1      | 0        | 0        |

| SW/HW<br>trigger<br>parallel<br>independe<br>nt  | PGA1 SW<br>trigger<br>PDB<br>trigger A<br>one-shot | 1      | 1      | 0      | 1      | 1      | Х      | 0        | 0        |

| PGA SW<br>trigger<br>parallel<br>independe<br>nt | PGA SW<br>trigger                                  | 1      | 1      | 1      | 1      | Х      | Х      | 0        | 0        |

| PGA0 HW<br>trigger<br>single                     | PDB<br>trigger A<br>one-shot                       | 1      | 0      | 0      | 0      | 1      | Х      | 0        | 0        |

| PGA0 HW<br>PGA1<br>bypass                        | PDB one-<br>shot                                   | 1      | 0      | 0      | 0      | 1      | Х      | 0        | 0        |

| PGA0 SW<br>trigger<br>single                     | PGA0 SW<br>trigger                                 | 1      | 0      | 1      | 0      | Х      | 1      | 0        | 0        |

| PGA1 HW<br>trigger<br>single                     | PDB<br>trigger B<br>one-shot                       | 0      | 1      | 0      | 0      | Х      | 1      | 0        | 0        |

| PGA1 HW<br>trigger,<br>PGA0<br>bypass            | PDB one-<br>shot                                   | 0      | 1      | 0      | 0      | 1      | 1      | 0        | 0        |

| PGA1 SW<br>trigger<br>single                     | PGA1 SW<br>trigger                                 | 0      | 1      | 0      | 1      | 1      | Х      | 0        | 0        |

## 3 Valid PGA configurations

This section describes valid PGA configurations with reference to PDB triggers and ADC results for different sampling schemes. The PGA block may not be shown in the following figures in case the PGA is bypassed. PDB pre-trigger and trigger signals in PDB one-shot or two-shot mode are drawn in the following figures for the simplicity too. "X" for a register bit means don't care.

## 3.1 One-shot PGAs Disabled, PDB Trigger A disabled

In this configuration, both PGAs are disabled and bypassed. Figure below depicts the interaction of the PDB, ADC in this configuration.

PretriggerA

PretriggerA

PretriggerB

ADHWT

SSEL[0] ADCA

SSEL[1]

SSEL[1]

SSEL[1]

ADCB

ADHWT

Figure 3. One-shot PGAs disabled with PDB Trigger A disabled

PGA setup is as below:

- PGA0 CNTL0[EN] = PGA1 CNTL0[EN] = 0;

- PGA0\_CNTL1[PPDIS] = PGA1\_CNTL1[PPDIS] = 0;

- PGA0\_CNTL1[PARMODE] = PGA1\_CNTL1[PARMODE] = X;

- PGA0\_CNTL0[TM] = PGA1\_CNTL0[TM] = 0;

PDB trigger setup is as below:

- PDB one-shot mode

- TriggerA is disabled

- TriggerB is enabled and function of Delay B only

PDB PretriggerB selects ADC0\_SC1B/ADCRB, ADC1\_SC1A/ADCRA.

In this configuration, ADC samples per trigger is 1 sample in ADCRA for ADCB.

## 3.2 One-shot PGA Disabled, PDB TriggerB disabled

In this configuration, both PGAs are disabled, and, bypassed. Figure below depicts the interaction of the PDB, ADC in this configuration.

Figure 4. One-shot PGAs disabled with PDB Trigger B disabled

PGA setup is as below:

- PGA0\_CNTL0[EN] = PGA1\_CNTL0[EN] = 0;

- PGA0\_CNTL1[PPDIS] = PGA1\_CNTL1[PPDIS] = 0;

- PGA0\_CNTL1[PARMODE] = PGA1\_CNTL1[PARMODE] = X;

- PGA0\_CNTL0[TM] = PGA1\_CNTL0[TM] = 0;

PDB trigger setup is as below:

- PDB one-shot mode

- TriggerA is enabled and function of Delay A only

- · TriggerB is disabled

PDB PretriggerA selects ADC0\_SC1A/ADCRA, ADC1\_SC1B/ADCRB.

In this configuration, ADC samples per trigger is 1 sample in ADCRA for ADCA.

## 3.3 One-shot PGAs disabled, ping-pong disabled

In this configuration, both PGAs are disabled, bypassed, and both PGA's ping-pong are disabled. Figure below depicts the interaction of the PDB, ADC in this configuration.

Figure 5. One-shot PGAs disabled, ping-pong disabled

- $PGA0\_CNTL0[EN] = PGA1\_CNTL0[EN] = 0$

- PGA0\_CNTL1[PPDIS] = PGA1\_CNTL1[PPDIS] = 1

- PGA0\_CNTL1[PARMODE] = PGA1\_CNTL1[PARMODE] = X

- PGA0\_CNTL0[TM] = PGA1\_CNTL0[TM] = 0

PDB trigger Setup is as below:

- · PDB one-shot

- Both TriggerA and TriggerB are enabled

PDB PretriggerA selects ADC0\_SC1A/ADCRA.

PDB PretriggerB selects ADC1\_SC1A/ADCRA.

In this configuration, ADC samples per trigger is 1 sample in ADC0\_ADCRA for ADCA and 1 sample in ADC1\_ADCRA for ADCB.

## 3.4 Ping-Pong PGA Disabled

In this configuration, both PGAs are disabled, bypassed. Figure below depicts the interaction of the PDB, ADC in this configuration.

Figure 6. Ping-Pong PGA's disabled

#### PGA setup is as below:

- PGA0\_CNTL0[EN] = PGA1\_CNTL0[EN] = 0

- PGA0\_CNTL1[PPDIS] = PGA1\_CNTL1[PPDIS] = 1

- PGA0\_CNTL1[PARMODE] = PGA1\_CNTL1[PARMODE] = X

- PGA0\_CNTL0[TM] = PGA1\_CNTL0[TM] = 0

#### PDB trigger setup is as below:

- PDB two-shot mode

- DelayB is greater than or equal to the DelayA plus the ADC conversion time or vice versa

- Both TriggerA and TriggerB are enabled and function of both Delay A and Delay B

PDB PretriggerA selects ADC0\_SC1A/ADCRA, ADC1\_SC1B/ADCRB.

PDB PretriggerB selects ADC0\_SC1B/ADCRB, ADC1\_SC1A/ADCRA.

In this configuration, ADC samples per trigger is 4:

For ADCA, the first sample is in ADC0 ADCRA, the second sample in ADC0 ADCRB.

For ADCB, the first sample is in ADC1\_ADCRB, the second sample in ADC1\_ADCRA.

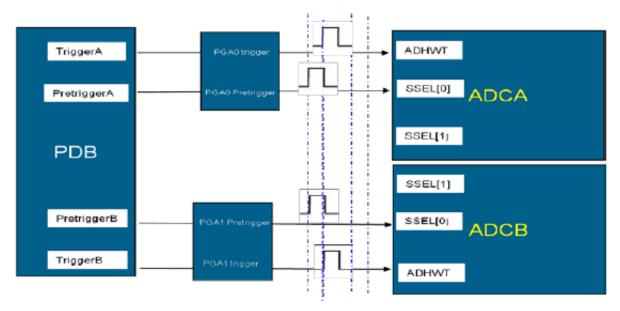

## 3.5 Ping-Pong PGA's enabled

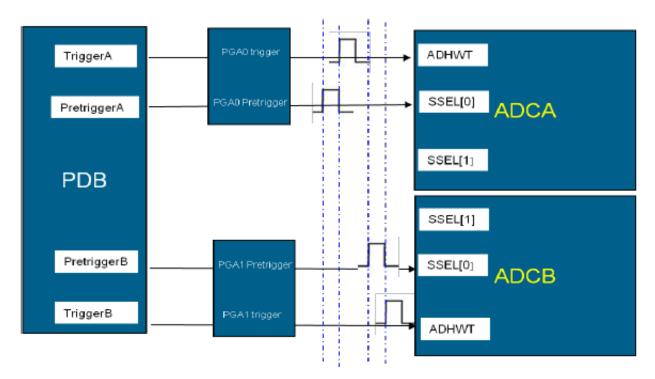

In this configuration, both PGAs are enabled, and both PGA's parallel mode are enabled. Figure below depicts the interaction of the PDB, PGA and ADC in this configuration.

Figure 7. Ping-Pong PGAs Enabled

- PGA0\_CNTL0[EN] = PGA1\_CNTL0[EN] = 1

- PGA0\_CNTL1[PARMODE] = PGA1\_CNTL1[PARMODE] = 1

- PGA0\_CNTL1[PPDIS] = PGA1\_CNTL1[PPDIS] = 0

- PGA0 CNTL0[TM] = PGA1 CNTL0[TM] = 0

#### PDB trigger Setup is as below:

- PDB one-shot mode

- DelayB is greater than or equal to the DelayA plus the ADC conversion time or vice versa

- Both TriggerA and TriggerB are enabled and function of both Delay A and Delay B

PDB PretriggerA selects ADC0\_SC1A/ADCRA, ADC1\_SC1B/ADCRB.

PDB PretriggerB selects ADC0\_SC1B/ADCRB, ADC1\_SC1A/ADCRA.

In this configuration, ADC samples per trigger is 4:

For ADCA, the first sample is in ADC0\_ADCRA, the second sample is in ADC0\_ADCRB. For ADCB, the first sample is in ADC1\_ADCRB, the second sample is in ADC1\_ADCRA.

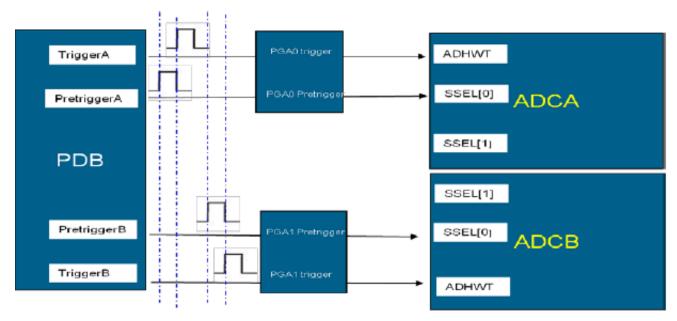

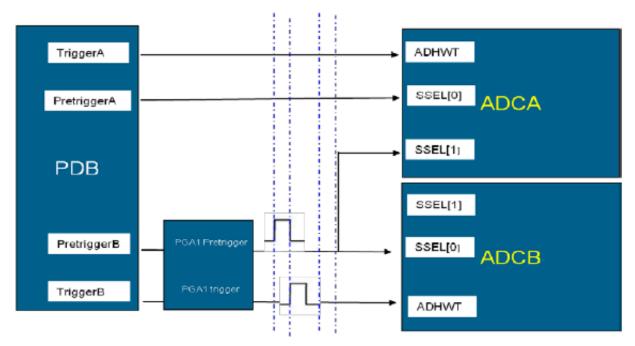

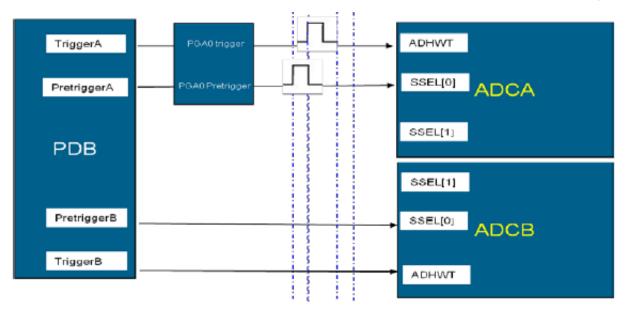

## 3.6 One-shot PGA's enabled

In this configuration, both PGAs are enabled, but PGA's ping-pong are disabled, PGA's parallel mode are disabled too. Figure below depicts the interaction of the PDB, PGA, ADC in this configuration.

Figure 8. One-shot PGAs enabled

PGA setup is as below:

- PGA0\_CNTL0[EN] = PGA1\_CNTL0[EN] = 1

- PGA0\_CNTL1[PPDIS] = PGA1\_CNTL1[PPDIS] = 1

- PGA0\_CNTL1[PARMODE] = PGA1\_CNTL1[PARMODE] = 0

- PGA0\_CNTL0[TM] = PGA1\_CNTL0[TM] = 0

PDB trigger Setup is as below:

- PDB one-shot mode

- TriggerA is enabled and function of Delay A only

- TriggerB is enabled and function of Delay B only

PGA0 generated Pre-triggerA selects ADC0\_SC1A/ADCRA.

PGA1 generated PretriggerB selects ADC1\_SC1A/ADCRA.

In this configuration, ADC samples per trigger is 2 samples:

- For ADCA, 1 sample is in ADC0\_ADCRA

- For ADCB, 1 sample is in ADC1\_ADCRA

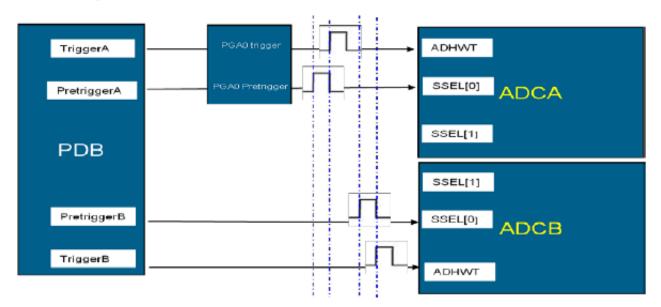

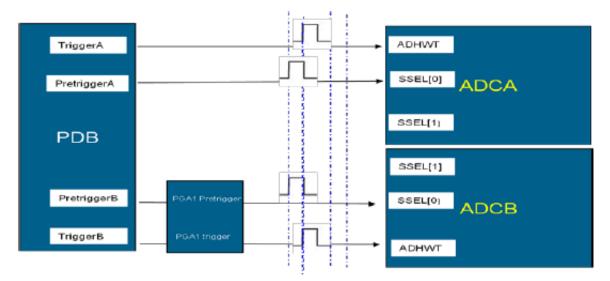

## 3.7 One-shot PGA's enabled, parallel mode enabled

In this configuration, both PGAs are enabled, parallel mode is enabled, but PGA's ping-pong are disabled. Figure below depicts the interaction of the PDB, PGA, ADC in this configuration.

Figure 9. One-shot PGAs enabled, parallel mode enabled

- PGA0\_CNTL0[EN] = PGA1\_CNTL0[EN] = 1

- PGA0\_CNTL1[PPDIS] = PGA1\_CNTL1[PPDIS] = 1

- PGA0\_CNTL1[PARMODE] = PGA1\_CNTL1[PARMODE] = 1

- PGA0\_CNTL0[TM] = PGA1\_CNTL0[TM] = 0

PDB trigger Setup is as below:

- PDB one-shot mode

- TriggerA is enabled and function of Delay A only

- TriggerB is enabled and function of Delay B only

PDB PretriggerA selects ADC0\_SC1A/ADCRA.

PDB PretriggerB selects ADC1\_SC1A/ADCRA.

In this configuration, ADC samples per trigger is 2 samples:

- For ADCA, 1 sample is in ADC0\_ADCRA

- For ADCB, 1 sample is in ADC1\_ADCRA

## 3.8 PGA0 HW PGA1 bypass

In this configuration, PGA0 is enabled, PGA1 is bypassed, both PGA's ping-pong are disabled. Figure below depicts the interaction of the PDB, ADC in this configuration.

Figure 10. PGA0 HW PGA1 bypass

PGA setup is as below:

- PGA0\_CNTL0[EN] =1, PGA1\_CNTL0[EN] = 0

- PGA0\_CNTL1[PPDIS] = PGA1\_CNTL1[PPDIS] = 1

- PGA0 CNTL1[PARMODE] = PGA1 CNTL1[PARMODE] = 0

- PGA0\_CNTL0[TM] = PGA1\_CNTL0[TM] = 0

PDB trigger Setup is as below:

- PDB one-shot mode

- TriggerA is enabled and function of Delay A only

- TriggerB is enabled and function of Delay B only

PGA0 generated pretrigger selects ADC0\_SC1A/ADCRA.

PDB Pretrigger B selects ADC1\_SC1A/ADCRA.

In this configuration, ADC samples per trigger is 2 samples:

- For ADCA, 1 sample is in ADC0\_ADCRA

- For ADCB, 1 sample is in ADC1\_ADCRA.

## 3.9 PGA0 HW trigger single

In this configuration, PGA0 is enabled, PGA1 is bypassed, both PGA's ping-pong are disabled. Figure below depicts the interaction of the PDB, PGA and ADC in this configuration.

Figure 11. PGA0 HW trigger single

- PGA0 CNTL0[EN] =1, PGA1 CNTL0[EN] = 0

- PGA0\_CNTL1[PPDIS] = 1,PGA1\_CNTL1[PPDIS]= X

- PGA0 CNTL1[PARMODE] = PGA1 CNTL1[PARMODE] = 0

- PGA0\_CNTL0[TM] = PGA1\_CNTL0[TM] = 0

#### PDB trigger Setup is as below:

- PDB one-shot mode

- TriggerA is enabled and function of Delay A only

- TriggerB is disabled

PGA0 generated Pretrigger selects ADC0\_SC1A/ADCRA, ADC1\_SC1B/ADCRB.

In this configuration, ADC samples per trigger is 1 sample:

1 sample is in ADC0\_ADCRA

## 3.10 PGA1 HW trigger PGA0 bypass

In this configuration, PGA1 is enabled, PGA0 is bypassed, both PGA's ping-pong are disabled. Figure below depicts the interaction of the PDB, PGA0, ADC in this configuration.

Figure 12. PGA1 HW trigger PGA0 bypass

PGA setup is as below:

- PGA0\_CNTL0[EN] =0, PGA1\_CNTL0[EN] = 1

- PGA0\_CNTL1[PPDIS] = PGA1\_CNTL1[PPDIS] = 1

- PGA0\_CNTL1[PARMODE] = PGA1\_CNTL1[PARMODE] = 0

- PGA0\_CNTL0[TM] = PGA1\_CNTL0[TM] = 0

PDB trigger Setup is as below:

- PDB one-shot mode

- TriggerA is enabled and function of Delay A only

- TriggerB is enabled and function of Delay B only

PGA1 generated Pretrigger selects ADC1\_SC1A/ADCRA.

PDB PretriggerA selects ADC0\_SC1A/ADCRA.

In this configuration, ADC samples per trigger is 2 samples:

- For ADCA, 1 sample is in ADC0\_ADCRA.

- For ADCB, 1 sample is in ADC1\_ADCRA.

## 3.11 PGA1 HW trigger single

In this configuration, PGA1 is enabled, PGA0 is bypassed, PGA1's ping-pong is disabled. Figure below depicts the interaction of the PDB, PGA,ADC in this configuration.

Figure 13. PGA1 HW trigger single

- PGA0\_CNTL0[EN] =0, PGA1\_CNTL0[EN] = 1

- PGA0\_CNTL1[PPDIS] = X,PGA1\_CNTL1[PPDIS]=1

- PGA0\_CNTL1[PARMODE] = PGA1\_CNTL1[PARMODE] = 0

- PGA0 CNTL0[TM] = PGA1 CNTL0[TM] = 0

PDB trigger Setup is as below:

- PDB one-shot mode

- Trigger B is enabled and function of Delay B only

- Trigger A is disabled

PGA1 generated pretrigger selects ADC1\_SC1A/ADCRA, and ADC0\_SC1B/ADCRB.

In this configuration, ADC samples per trigger is 1 sample:

For ADCB, 1 sample is in ADC1\_ADCRA.

## 3.12 SW/HW trigger parallel independent, PGA1 SW trigger PDB trigger A one-shot

In this configuration, both PGA are enabled, PGA0's ping-pong is disabled, PGA1 uses software trigger. Figure below depicts the interaction of the PDB, PGA, ADC in this configuration.

Figure 14. PGA1 SW trigger PDB trigger A one-shot

PGA setup is as below:

- PGA0\_CNTL0[EN] =1, PGA1\_CNTL0[EN] = 1

- PGA0\_CNTL1[PPDIS] = 1, PGA1\_CNTL0[TM] = 1

- PGA0\_CNTL1[PARMODE] = PGA1\_CNTL1[PARMODE] = 0

- PGA1\_CNTL1[PPDIS] = X, PGA0\_CNTL0[TM] = 0

PDB trigger Setup is as below:

- · PDB one-shot mode

- TriggerA is enabled and function of Delay A only

- Trigger B is enabled, but will be masked by PGA1

PGA1 generated pretrigger selects ADC1\_SC1A/ADCRA.

PDB PretriggerA selects ADC0\_SC1A/ADCRA.

In this configuration, ADC samples per trigger is 2 samples:

- For ADCA, 1 sample is in ADC0\_ADCRA

- For ADCB, 1 sample is in ADC1\_ADCRA

## 3.13 SW/HW trigger parallel independent, PGA0 SW trigger PDB trigger B one-shot

In this configuration, both PGAs are enabled, PGA1's ping-pong is disabled, PGA0 uses software trigger. Figure below depicts the interaction of the PDB, PGA, ADC in this configuration.

Figure 15. PGA0 SW trigger PDB trigger B one-shot

- PGA0\_CNTL0[EN] =1, PGA1\_CNTL0[EN] = 1

- PGA1\_CNTL1[PPDIS] = 1, PGA0\_CNTL0[TM] = 1

- PGA0\_CNTL1[PARMODE] = PGA1\_CNTL1[PARMODE] = 0

- PGA0\_CNTL1[PPDIS] =X, PGA1\_CNTL0[TM] = 0

PDB trigger setup is as below:

- PDB one-shot mode

- Trigger B is enabled and function of Delay B only

- Trigger A is enabled, but will be masked by PGA0

PGA0 generated Pretrigger selects ADC0\_SC1A/ADCRA.

PDB PretriggerB selects ADC1 SC1A/ADCRA.

In this configuration, ADC samples per trigger is 2 samples:

- For ADCA, 1 sample is in ADC0 ADCRA

- For ADCB, 1 sample is in ADC1\_ADCRA

## 3.14 PGA SW trigger parallel independent

In this configuration, both PGAs are enabled, both PGA use software trigger. Figure below depicts the interaction of the PDB, PGA and ADC in this configuration.

Figure 16. PGA SW trigger parallel independent

PGA setup is as below:

- PGA0\_CNTL0[EN] =1, PGA1\_CNTL0[EN] = 1

- PGA0\_CNTL0[TM] = 1, PGA1\_CNTL0[TM] = 1

- PGA0\_CNTL1[PARMODE] = PGA1\_CNTL1[PARMODE] = 0

- PGA0\_CNTL1[PPDIS] = PGA1\_CNTL1[PPDIS] = X

PDB trigger setup is as below:

- PDB one-shot mode

- Trigger B and Trigger A are enabled, but will be masked by both PGAs

PGA0 generated Pretrigger selects ADC0\_SC1A/ADCRA.

PGA1 generated Pretrigger selects ADC1\_SC1A/ADCRA.

In this configuration, ADC samples per trigger is 2 samples:

- For ADCA, 1 sample is in ADC0\_ADCRA

- For ADCB, 1 sample is in ADC1\_ADCRA

## 3.15 PGA0 SW trigger single

In this configuration, PGA0 is enabled, PGA1 is bypassed, PGA0 uses software trigger, PGA1's ping-pong is disabled. Figure below depicts the interaction of the PDB, PGA, ADC in this configuration.

Figure 17. PGA0 SW trigger single

- PGA0\_CNTL0[EN] =1, PGA1\_CNTL0[EN] = 0

- PGA0\_CNTL0[TM] = 1, PGA1\_CNTL0[TM] = 0

- PGA0\_CNTL1[PPDIS] = X,PGA1\_CNTL1[PPDIS] = 1

- PGA0\_CNTL1[PARMODE] = PGA1\_CNTL1[PARMODE] = 0

PDB trigger setup is as below:

- PDB one-shot mode

- Trigger A is enabled, but will be masked by PGA0

- Trigger B is disabled

PGA0 generated Pretrigger selects ADC0 SC1A/ADCRA.

In this configuration, ADC samples per trigger is 1 sample:

• For ADCA, 1 sample is in ADC0\_ADCRA.

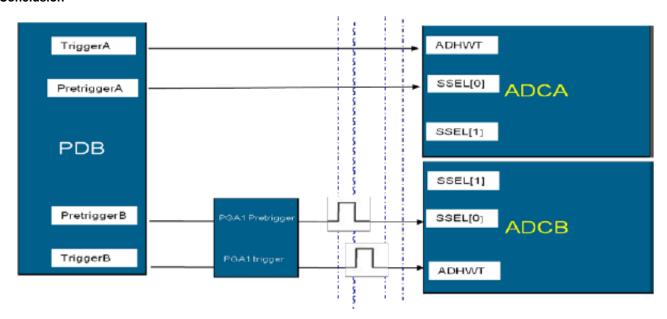

## 3.16 PGA1 SW trigger single

In this configuration, PGA1 is enabled, PGA0 is bypassed, PGA1 uses software trigger, PGA0's ping-pong is disabled. Figure below depicts the interaction of the PDB, PGA, ADC in this configuration.

#### Conclusion

Figure 18. PGA1 SW trigger single

PGA setup is as below:

- PGA1\_CNTL0[EN] =1, PGA0\_CNTL0[EN] = 0

- $PGA1\_CNTL0[TM] = 1$ ,  $PGA0\_CNTL0[TM] = 0$

- PGA0\_CNTL1[PPDIS] = 1,PGA1\_CNTL1[PPDIS] = X

- PGA0\_CNTL1[PARMODE] = PGA1\_CNTL1[PARMODE] = 0

PDB trigger setup is as below:

- PDB one-shot mode

- Trigger B is enabled, but will be masked by PGA1

- Trigger A is disabled

PGA1 generated Pretrigger selects ADC1\_SC1A/ADCRA.

In this configuration, ADC samples per trigger is 1 sample:

• For ADCB, 1 sample is in ADC1\_ADCRA.

## 4 Conclusion

There are 16 PGA configurations introduced in this application note. A PGA configuration can be selected based on the specific application requirements. To get four samples per hardware trigger, the recommended PGA configuration is Ping-Pong PGA's enabled in case both PGAs are used, or Ping-Pong PGA's disabled. To get two samples per hardware trigger, the recommended PGA configurations are One-shot PGA's enabled with parallel mode enabled, One-shot PGA's disabled with ping-pong disabled, One-shot PGA's disabled with PDB Trigger A disabled, One-shot PGA's disabled with PDB Trigger B disabled. These configurations eliminate the possible contentions between the PGA generated Pretrigger signals and are safe to get exact number of samples per hardware trigger.

#### How to Reach Us:

#### **Home Page:**

www.freescale.com

#### Web Support:

http://www.freescale.com/support

#### **USA/Europe or Locations Not Listed:**

Freescale Semiconductor

Technical Information Center, EL516

2100 East Elliot Road

Tempe, Arizona 85284

+1-800-521-6274 or +1-480-768-2130

www.freescale.com/support

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) www.freescale.com/support

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor China Ltd.

Exchange Building 23F

No. 118 Jianguo Road

Chaoyang District

Beijing 100022

China

+86 10 5879 8000

support.asia@freescale.com

Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductors products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claims alleges that Freescale Semiconductor was negligent regarding the design or manufacture of

RoHS-compliant and/or Pb-free versions of Freescale products have the functionality and electrical characteristics as their non-RoHS-complaint and/or non-Pb-free counterparts. For further information, see http://www.freescale.com or contact your Freescale sales representative.

For information on Freescale's Environmental Products program, go to http://www.freescale.com/epp.

Freescale<sup>TM</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners.

© 2012 Freescale Semiconductor, Inc.

Document Number: AN4334 Rev. 0, 03/2012