## Freescale Semiconductor

**Application Note**

Document Number: AN3974 Rev. 0, 01/2010

# Different Display Configurations on i.MX35 Linux PDK

by Multimedia Application Division Freescale Semiconductor, Inc. Austin, TX

This application note provides information, considerations and steps to add or adapt a new display panel to the BSP distribution for i.MX35 PDK. It provides details about general panel and generalities of display controller from the module. It also describes the development process to adapt a new panel to the Board Support Package (BSP) taking into consideration the framework driver structure provided by the operating system. This application note assumes that the reader is familiar with LTIB packages and Linux device driver concepts.

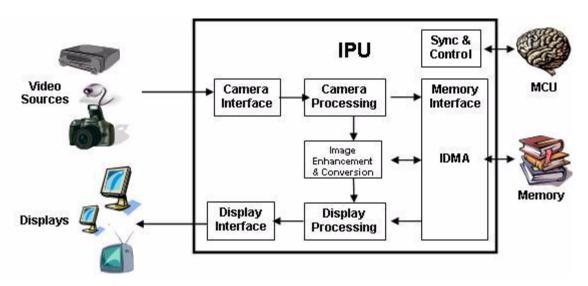

The i.MX35 multimedia processor supports many display types. The Image Processing Unit (IPU) handles the display devices. This module also controls graphic interfaces such as cameras and 2D graphics acceleration. All IPU sub-modules are connected using a private DMA interface (IDMA). The IDMA is used only for the IPU to transfer data between sub-modules and also between IPU and the external memory.

#### Contents

| l. | LCD Principles                 | 2  |

|----|--------------------------------|----|

| 2. | Synchronous Display Interface  | 5  |

| 3. | Display Configuration in Linux | 22 |

| 1. | References                     | 52 |

| 5. | Revision History               | 52 |

© Freescale Semiconductor, Inc., 2010. All rights reserved.

Figure 1 shows a functional diagram of IPU.

Figure 1. IPU Functional Diagram

The selection of proper Liquid Crystal Display (LCD) in a mobile device is a challenge and involves conflicts in the requirements. The following are examples of such conflicts:

- Large amount of data implying high rate of data transfer and processing and requiring significant resources.

- Flexibility to support a variety of use cases.

- Size, cost and power consumption.

Freescale's reference designs for the i.MX family demonstrate the functionality of the LCD, however developers can find many reasons to replace the display in their products. Features such as screen size, resolution, weight, power consumption and price are important in a commercial multimedia product. Another important fact regarding LCD panels is that many displays become obsolete quickly. For this reason, it may be hard to find the same LCD panel included in the reference design when the users are creating their own product.

While some information would be useful for Smart Displays, this application note is intended only for dumb displays and especially those which do not have a SHARP synchronous interface. Do not confuse the SHARP LCD panels with the SHARP interface. Many SHARP LCD panels do not use the SHARP interface.

## 1 LCD Principles

This section describes the principles of a LCD.

## 1.1 LCD Basics

A LCD is an electronic device which consists of an array of pixels of color or monochrome units. Every element in the array consist of a special material, which allows them to change the characteristics of the

NP

light that passes through them. These devices cannot emit light and because of this reason another element called backlight is usually shipped with the panel to create a fully functional display device.

## 1.1.1 Resolution

Resolution is the number of pixels contained in the LCD array. It has two dimensions: horizontal and vertical. There are some standard resolutions available in the market that must be followed.

| Video Name | Description                          | Width | Height | Aspect Ratio |

|------------|--------------------------------------|-------|--------|--------------|

| CGA        | Color Graphics Adaptor               | 320   | 200    | 8:5          |

| QVGA       | Quarter VGA                          | 320   | 240    | 4:3          |

| VGA        | Video Graphics Array                 | 640   | 480    | 4:3          |

| NTSC       | National Television System Committee | 720   | 480    | 4:3          |

| PAL        | Phase Alternating Line (TV)          | 720   | 576    | 4:3          |

| WVGA       | Wide VGA                             | 800   | 480    | 5:3          |

| SVGA       | Super VGA                            | 800   | 600    | 4:3          |

| WSVGA      | Wide Super VGA                       | 1024  | 600    | —            |

| XGA        | Extended Graphic Array               | 1024  | 768    | 4:3          |

Some of the most common video resolution standards are shown in Table 1. Table 1. Common Video Resolution Standards

There are many resolution standards, but as SVGA is the maximum standard resolution supported by the i.MX35 processor, larger resolutions are not included in this table.

All resolutions mentioned in Table 1 refer to a landscape orientation, which means that there are more pixels in the horizontal axis than the vertical. However, Portrait LCD panels are also available in the market with the same standard resolution but the horizontal and vertical dimensions are inverted. In that case, Portrait LCD panels have more vertical pixels than horizontal pixels.

Figure 2 shows the Portrait and Landscape orientation of the LCD panels.

Figure 2. Portrait and Landscape Orientation

Selecting a proper LCD orientation is important, because both electronic and optical features are optimized for applications that use the native orientation of the panel. Besides the optical characteristics, dumb displays include an embedded LCD controller, and the chip draws the pixels from left to right and also

#### LCD Principles

from top to bottom. In some scenarios, images or LCDs are shown using a nonnative orientation. In that case, display contents should be preprocessed to create a buffer where the image is written with the purpose of matching the way (order) in which the LCD controller expects to receive the pixel information. This operation is called rotation and i.MX35 includes hardware to perform it. It is recommended to select an LCD panel which can work using the native orientation, to avoid image processing overhead.

Figure 3 shows both portrait and Landscape LCD panels displaying images in a nonnative orientation.

Figure 3. Rotated Frames on Portrait and Landscape Orientation

It is important to mention that rotation could be  $90^{\circ}$ ,  $180^{\circ}$  or  $270^{\circ}$  (that is, it is not limited only to  $90^{\circ}$ ). Note that if such rotations are chosen, then each frame should be rotated before sending them for the display.

### 1.1.1.1 Size

The size of an LCD panel is usually measured diagonally in inches, from corner to corner. When choosing between a VGA (640 x 480) panel and a QVGA (320 x 240) panel, one could expect the VGA panel to be of a larger size as it has more pixels (four time as many), but this is not always the case. LCD manufacturing processes allow size and resolution to be independent variables; it is hard to determine the size of a panel only from its resolution. Screens that are lager in size consume more power than smaller ones and they also impact the size and weight of the final product. On the other hand, high resolutions on small LCD screens can complicate the visibility of on-screen objects for the final user. Sometimes it is hard to determine how well a particular LCD panel 1 fits in an application based only on the information from the datasheet.

### 1.1.1.2 Color Spaces

A color space is used to represent colors. There are two main color spaces, RGB (that is, RGB565, RGB888, RGBA8888) and YUV (that is, YUV 4:4:4, YUV 4:2:2, YUV 4:2:0). The i.MX35 supports both the color spaces.

#### NOTE

Display panels can receive only data using the RGB color space.

## 1.2 LCD Types

This section describes the various LCD types.

## 1.2.1 Synchronous Panel (Dumb Display)

Dumb display or synchronous display stands for panels which require the system to send continuous frame data. The refresh is done by sending all pixels that compose a full frame, for every single frame. In general, smart displays are more expensive than dumb displays, and that is one of the reasons why it is more common to use synchronous (dumb) panels in a final product. This application note focusses on Thin Film Transistor Liquid Crystal Display (TFT) which is a particular group of synchronous panels.

## 1.2.1.1 Asynchronous Panel (Smart Displays)

The advantage of Smart displays is that the i.MX35 only has to send display data when the image has changed, and most of the times, it can send only the data for the portion of the image that has changed. Images can be sent at any time and the embedded Smart LCD display controller handles the screen refresh. The i.MX35 processor can handle up to three asynchronous displays simultaneously and can handle synchronous interface at the same time. This means that if the application requires two LCD panels, then one of them must use an asynchronous interface.

## 2 Synchronous Display Interface

The i.MX35 Synchronous Display controller can be configured to handle the following four different types of devices:

- TFT monochrome

- TFT color

- YUV progressive

- YUV interlaced

This document focuses only on the Synchronous TFT Color interface. For these cases, i.MX35 provides a 28-line interface which is described in Table 2.

| Signal          | IPU Signal        | Description                |

|-----------------|-------------------|----------------------------|

| HSYNC           | DISPB_D3_HSYNC    | Horizontal Synchronization |

| VSYNC           | DISPB_D3_VSYNC    | Vertical Synchronization   |

| DRDY            | DISPB_D3_DRDY     | Data Enable or Data Ready  |

| PIXCLK          | DISPB_D3_CLK      | Pixel Clock                |

| Red Data [7:0]  | DISPB_DATA[23:16] | Pixel Red component        |

| Green Data[7:0] | DISPB_DATA[15:8]  | Pixel Green Component      |

| Blue Data [7:0] | DISPB_DATA[7:0]   | Pixel Blue Component       |

#### Table 2. 28-Line Interface

The definitions of the signals referred in Table 2 are as follows:

HSYNC

Horizontal synchronization signal, also known as FPLINE or LP, indicates to the LCD that a line has ended and the following valid pixels are part of the next line.

Synchronous Display Interface

| VSYNC    | Vertical synchronization signal, also known as FPFRAME, FLM, SPS or TV. When this signal is active, it indicates to the LCD that the current frame has ended. The LCD display must then restart the line index to zero to draw the next valid data in the first line of the panel.                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DRDY     | When data ready (DRDY) or data enable (DE) is active, it indicates to the LCD that the data in the RGB bus is valid and must be latched (latching happens using the PIXCLK signal). While data enable is active, every PIXCLK pulse makes the LCD draw a pixel using the color described in the RGB bus. The width of this signal should store all pixels (that is, as long as the sum of all pixel clock cycles are in a single line).                                                                                                                                                                                                                                                                  |

| PIXCLK   | Pixel clock signal specifies when RGB data is placed on the bus. There are<br>two possibilities. The first option is when data is written by i.MX35 to the<br>RGB bus on falling edges. In this case, data is stable and ready to be latched<br>by the LCD panel on the rising edges, as long as data enable is active. This<br>behavior corresponds to a high PIXCLK polarity. The second option is<br>called low PIXCLK polarity and it means that i.MX35 writes RGB data in<br>rising edges, and the data are latched by the LCD panel on the falling edges.                                                                                                                                          |

| RGB Data | The i.MX35 can internally use different bit depths per pixel, such as RGB565, RGB666, RGB888, RGBA8888 and so on. In the same manner, the display interface could be configured to support more than one color depth. The i.MX35 processors can use up to 24 data lines (RGB888) as display interface bus. If the color depth used internally is bigger than the display interface, then a RGB to RGB conversion is performed where least significant bits are removed from the pixel, and the remaining bits are sent directly to the display interface. Dithering or filter actions are not performed during this process. The remaining RGB data lines can be used for other purposes including GPIO. |

## 2.1 Extra Signals

There are also some other lines that are usually included on the panel interface. These signals are not part of the 28-line display interface, but they are required for a fully functional module. For example, it is common for some panels to have a reset signal, as well as initialization commands. These commands are usually sent through a serial interface such as I<sup>2</sup>C or SPI. Display panels sometimes have touch panels embedded in them and have a backlight source, which requires additional signals.

## 2.2 SPI Interface

Some LCD displays require an initialization routine through a serial interface, 3-wire, 4-wire, or 5-wire. Even when the i.MX35 IPU has a serial interface (SD\_D\_CLK, SD\_D\_IO and SD\_D\_I), this interface should not be used to send serial commands to the LCDs. This interface is not intended for general purpose usage, instead, it is used only by the IPU when the Asynchronous Display1 or Display2 are configured to use serial interface.

## 2.3 Synchronous Display Interface Examples

Some of the examples of a synchronous display interfaces are described in the following sections.

## 2.3.1 i.MX35 PDK Chunghwa 5.7" VGA LCD Interface

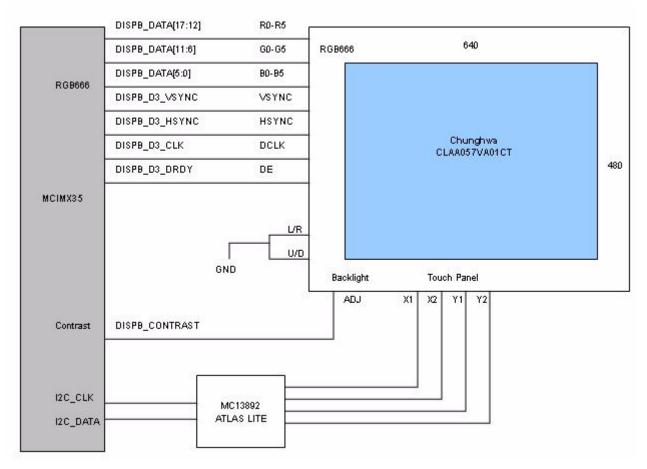

Figure 4 shows an interface between i.MX35 and Chunghwa CLAA057VA01CTVGA Panel.

Figure 4. LCD Interface Between i.MX35 and Chunghwa CLAA057VA01CTVGA Panel

As shown Figure 4, the LCD panel requires HSYNC, VSYNC, DE, PIXCLK and the complete RGB data interface (DISPB\_DATA[17:0]). Additional signals such as RESET signal or serial interface initialization routine commands (SPI or I<sup>2</sup>C) are not required. The backlight unit is controlled by using a PWM signal generated by the i.MX35 (Contrast). The touch panel interface is handled by the MC13892 ATLAS LITE chip.

#### NOTE

Touch Panel functionality is not covered in this application note.

#### Synchronous Display Interface

Each panel has its own interface and requirements, but in general terms, Figure 4 illustrates a typical synchronous panel interface. Determining the typicality of LCD panels is difficult, but the idea shown in Figure 4 can be used as a base for panel interface. The base interface idea is useful when there are many panels which do not use the complete interface. For example, some panels do not require HSYNC or VSYNC signal, or neither of them. Only DRDY, PIXCLK and RGB data are used. Also, many panels do not require a RESET signal or a serial initialization routine to handle display signals. When there is no serial interface, the timing, signals, porches and polarities are specified (fixed). The panels expect that the microprocessors complies with these waveforms, as such panels cannot handle a different interface.

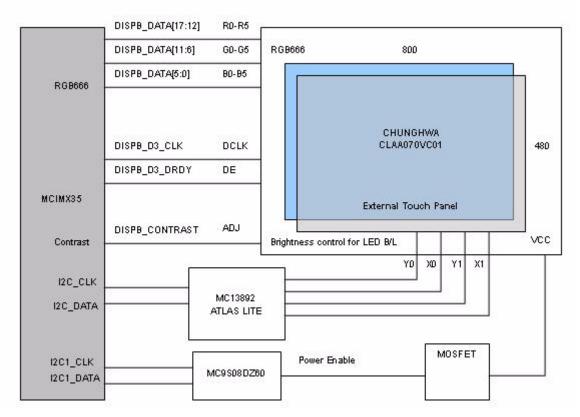

## 2.3.2 i.MX35 PDK Chunghwa CLAA070VC01 7" WVGA LCD Interface

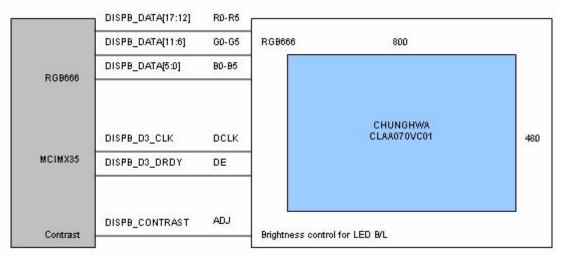

Figure 5 shows a LCD interface between i.MX35 and Chunghwa CLAA070VC01CWVGA Panel.

Figure 5. LCD Interface between i.MX35 and Chunghwa CLAA070VC01 WVGA Panel

This LCD is shipped with the i.MX35 PDK, and it shows a very simple display interface where HSYNC and VSYNC signals are not used. Both HSYNC and VSYNC can be used for other purposes, including GPIO.

The SPI interface is not required as there is also a Chip Select (CSPI1\_SS2) available for other devices. Additionally, the power booster for the backlight unit is included in the module, which means that Contrast signal is directly connected to the Display connector. This display module does not include a touch panel, so it is necessary to add an external touch screen to the LCD panel.

In Figure 5 as in the previous 5.7" VGA LCD interface, only 18 RGB data lines are required, DISPB\_DATA[17:0]. The remaining RGB data lines DISPB\_DATA[23:18] can be used for other purposes such as GPIO or any other alternate function that each pin can perform.

Another drawback of this module is, the display cannot be turned off, since it does not have a RESET signal or SPI interface. This feature is particularly important for mobile devices where power consumption is an issue. If the energy used by the LCD has to be controlled, then external circuits should be used to control the energy. In case of PDK, power ON/OFF settings are handled by an external 8-bit Microprocessor driven by the i.MX35 through an  $I^2C$  bus.

Based on the above observations, the complete LCD circuit for the i.MX35 PDK system looks as shown in Figure 6.

Figure 6. LCD Interface Between i.MX35 and Chunghwa CLAA070VC01VWGA Panel + Touch Panel

The previous examples can be helpful for selecting an LCD display, to determine the advantages and disadvantages of a particular panel.

## 2.4 Synchronous Display Timing and Signals

This section describes the timing and signal waveforms for configuring them in the LCD panel and i.MX35 Display interface. Before selecting a LCD panel, refer the datasheet. This datasheet must show the pin interface, the initialization routine, and the timing charts for the RGB interface as well as the serial interface, if needed. Sometimes, a shorter version of the datasheet is also received, where not all information is given. In such situations, request the full documentation from the supplier. Many times, the document is received with a big watermark in every page telling that it is a preliminary datasheet, and having the final version is recommended.

#### NOTE

There are not many modifications between a preliminary version of LCD datasheet and the final version.

Synchronous Display Interface

## 2.4.1 Timing Concepts

The timing concepts that form the basis for LCD timing are explained below:

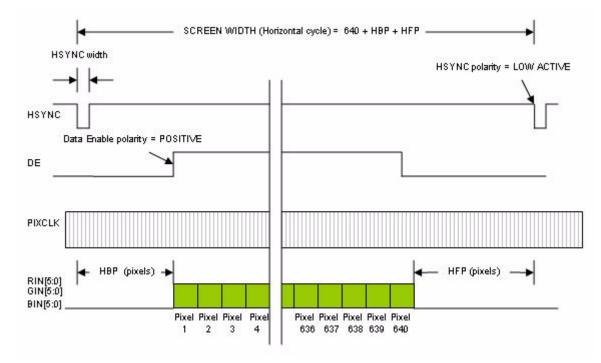

Horizontal Back Porch (HBP)Number of PIXCLK pulses between HSYNC signal and the first valid pixel data.

Horizontal Front Porch (HFP)Number of PIXCLK between last valid pixel data in the line and the next HSYNC pulse.

- Vertical Back Porch (VBP) Number of lines (HSYNC pulses) from when a VSYNC signal is asserted and the first valid line.

- Vertical Front Porch (VFP) Number of lines (HSYNC pulses) between last valid line of the frame and the next VSYNC Pulse.

VSYNC pulse width Number of HSYNC pulses when a VSYNC signal is active.

HSYNC pulse width Number of PIXCLK pulses when a HSYNC signal is active.

- Active Frame widthThe Horizontal Resolution, which means the number of pixels in one line.<br/>For example, for a WVGA display (800H × 480V), the frame width is equal<br/>to 800 pixels.

- Active Frame HeightThe Vertical Resolution of the LCD, using the same WVGA (800H×480V)<br/>for example, the value of the frame height is 480 lines.

- Screen Width Number of pixel clock periods between the last HSYNC and the new HSYNC. So, this value includes the valid pixels and also the Horizontal Back and Front porches.

SCREEN\_WIDTH = ACTIVE\_FRAME\_WIDTH + HBP + HFP

- Eqn. 1

- Screen Height Number of lines between VSYNC pulses. It includes all valid lines and also the Vertical, Back and Front porch.

SCREEN\_HEIGHT = ACTIVE\_FRAME\_HEIGHT + VBP + VFP Eqn. 2

| VSYNC polarity | It is the value that VSYNC takes to indicate the starting of a new frame. It can be ACTIVE LOW when value is 0 or ACTIVE HIGH when it is 1.       |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| HSYNC polarity | It is the value which the HSYNC takes to indicate the starting of a new line.<br>It can be ACTIVE LOW when value is 0 or ACTIVE HIGH when it is 1 |

## 2.4.2 Timing Charts

This section reviews the following charts to clarify the timing issues in a LCD interface. Any datasheet should include this kind of information. In general, three different charts are available as given below:

- The first one should cover the vertical timing.

- The second one specifies the horizontal timing.

- A third one with the pixel clock characteristics.

Additionally, if the display uses a serial interface, then a chart describing the serial interface and RESET is available. This information must be extracted from the datasheet when support for a new LCD panel should be added to a BSP. For example, when a VGA (640H x 480V) LCD panel is used instead of a Chunghwa CLAA057VA01CT, see Figure 5, then the display uses complete RGB interface: RGB666, VSYNC, HSYNC, Data Enable and Pixel clock.

### 2.4.2.1 Vertical Timing

Vertical Timing can be categorized as VGA vertical timing and WVGA vertical timing. These vertical timings are discussed in the following sections.

### 3.4.2.1.1 VGA Vertical Timing

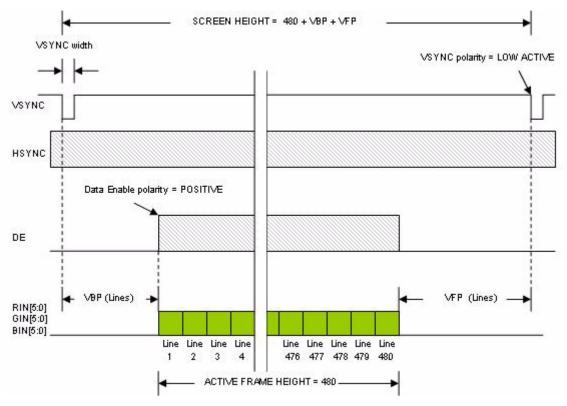

Figure 7 shows vertical timing chart for a hypothetic synchronous display VGA (640H x 480V).

Figure 7. VGA Vertical Timing Example

It is important to mention how signals appear during a VSYNC period. The VSYNC period involves a complete frame cycle. Every pixel of each line in the frame is sent to the panel during this period. The beginning of the frame is asserted by the VSYNC signal (in this case, when the signal goes low). Then, HSYNC immediately marks the beginning of the first line (in this example, it is when HSYNC goes low). But, in order to meet the LCD timing requirements, the first lines are designated for the VBP. During VBP, data enable signal is not present, and the pixel data on the bus during these lines is ignored by the panel. After VBP, DE signal appears inside the boundaries of the HSYNC period. Details about DE during a line cycle are described in the next section. DE appears consequently during all valid lines (Vertical resolution

#### Synchronous Display Interface

= 480V). During this time (ACTIVE FRAME HEIGHT), the LCD panel latches the RGB data on all lines and draws it on the screen. The final stage in the frame cycle is the VFP, where extra lines (HSYNC cycles) appear. During this time, DE remains inactive and again the panel discards any information on the RGB bus. The frame ends when VSYNC signal is asserted again (goes low).

Along with the chart, a table showing the range of the timing parameters can be seen as shown in Table 3. **Table 3. Timing Parameters Range**

| Parameter                        | Symbol | Min | Туре | Мах | Unit |

|----------------------------------|--------|-----|------|-----|------|

| Screen Height or Vertical period | VP     | 515 | 525  | 560 | Line |

| VSYNC pulse width                | VSW    | 1   | 1    | 1   | Line |

| Vertical Back Porch+VSYNC        | VBP    | 34  | 34   | 34  | Line |

| Vertical Front Porch             | VFP    | 1   | 11   | 46  | Line |

| Active Frame Height              | VDISP  | —   | 480  | _   | Line |

| Vertical refresh rate            | FV     | 55  | 60   | 65  | Hz   |

From the above table, the timing features can be verified. In the first waveform, it is shown that VSYNC polarity is ACTIVE LOW, which means that vertical synchronization is normally high, but goes low to indicate the beginning of the new frame. Another feature that can be checked is the VSYNC width (VSW). Timing has certain flexibilities, so timing could be set using more than one value. It is highly recommended to use the typical values, or any values close to them, so use one line as VSYNC width.

VBP and VFP are also shown. Note that these values are measured in Lines or which translates in HSYNC pulses. In this example, VBP could be 34 lines, and VFP is 11 lines wide. Also note that VSYNC width is included into the VBP stage. This means that VBP starts when VSYNC is asserted, and not when the VSYNC returns to the normal state. Using the values described above, the Screen height or Vertical cycle is 525 lines. In some cases, the value of the VBP and VFP is not given in lines; instead it is expressed in nanoseconds or milliseconds. In such cases, additional calculations have to be done to find the number of lines needed to meet those timings.

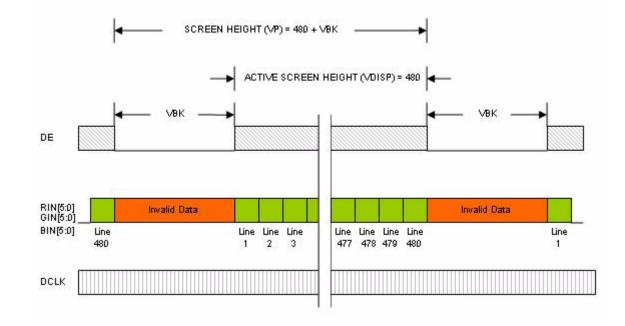

### 3.4.2.1.2 WVGA Vertical Timing

If an LCD panel like the hypothetical WVGA (800H x 480V) shown in Figure 6 and Figure 7, where HSYNC and VSYNC signals are not used, then the waveforms should be analyzed using another perspective.

Figure 8 shows an example of WVGA Vertical timing.

#### Figure 8. WVGA Vertical Timing Example

Table 4 shows the range of timing parameters.

Table 4. Timing Parameters Range

| Parameter                       | Symbol | Min | Туре | Max | Unit |

|---------------------------------|--------|-----|------|-----|------|

| Screen Height or Vertical Cycle | VP     | 90  | 500  | 520 | Line |

| Vertical Blank                  | VBK    | 10  | 20   | 40  | Line |

| Active Frame Height             | VDISP  | 480 | 480  | 480 | Line |

| Vertical Refresh Rate           | FV     | 55  | 60   | 65  | Hz   |

In such cases, VSYNC width, VSYNC polarity, VBP and VFP are not given in the chart. Even when VSYNC is not used, the values are required to be configured the i.MX35 Display Interface. This waveform can be used to understand vertical cycle behavior. For the i.MX35, the sequence remains the same: vertical cycle starts with the VSYNC signal, and then the rest of the VBP follows, then the active frame area, and finally the VFP appears, until the next VSYNC is asserted.

The VSYNC width, VBP and VFP can be found out based on the events occurring during the Vertical Blank Period.

#### Synchronous Display Interface

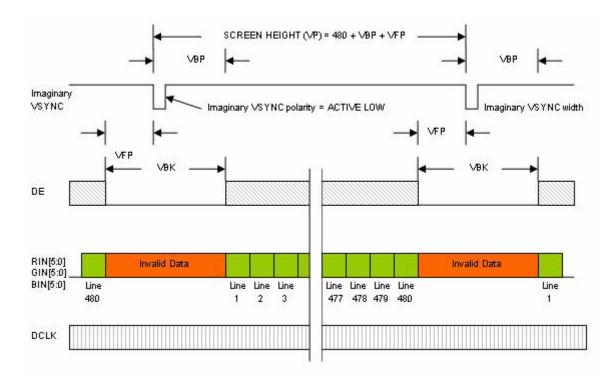

Figure 9 shows an example of WVGA vertical timing.

Figure 9. WVGA Vertical Timing Example with VSYNC Signals

The VSYNC signal can be used as a base to calculate the VFP and VBP. Since it is not used, any polarity can be set. However, setting VSYNC as ACTIVE LOW is recommended. VSYNC width is not strict either, but in these cases VSYNC is usually one line long (VSW=1). Now, to find VBP and VFP, it is important to not that the goal is to meet the Vertical Blank period, so the VBK period can be split into two parts. The first part is for the VFP, before VSYNC is asserted and the other part is for the VBP, including VSYNC. The sum of these values must be equal to the VBK period. Here any division works, but, leave an imaginary VSYNC in the middle of the Blank Period. This means that both VBP and VFP should be equal or almost equal.

Using this example and considering that VBK is 20 lines (typical), VBP+VSYNC could be 10 lines (and equal to VFP). Based on the information described above, vertical timing table is created as shown in Table 5.

| Parameter                       | Symbol | Min | Туре | Max | Unit |

|---------------------------------|--------|-----|------|-----|------|

| Screen Height or Vertical cycle | VP     | 490 | 500  | 520 | Line |

| VSYNC Pulse Width               | VSW    | 1   | 1    | 1   | Line |

| Vertical Back Porch+VSYNC       | VBP    | 1   | 10   | 40  | Line |

| Vertical Front Porch            | VFP    | 0   | 10   | 39  | Line |

| Vertical Blank                  | VBK    | 10  | 20   | 40  | Line |

| Table | 5.  | Vertical | Timina | Table |

|-------|-----|----------|--------|-------|

|       | ••• |          |        |       |

| Parameter             | Symbol | Min | Туре | Max | Unit |

|-----------------------|--------|-----|------|-----|------|

| Active Frame Height   | VDISP  | 480 | 480  | 480 | Line |

| Vertical refresh rate | FV     | 55  | 60   | 65  | Hz   |

Table 5. Vertical Timing Table (continued)

### 2.4.2.2 Horizontal Timing

Horizontal Timing can be categorized as VGA horizontal timing and WVGA horizontal timing. These horizontal timing are discussed in the following sections.

### 3.4.2.2.1 VGA Horizontal Timing

Figure 10 shows an example of line period datasheet chart.

Figure 10. VGA Horizontal Timing Example

The line cycle begins when HSYNC is asserted, in this case when the signal goes low, then the HBP stage continues. During this time, the Data Enable signal remains inactive. After that the horizontal active area (ACTIVE FRAME WIDTH) begins. This stage starts when data enable is asserted. Because in this case, DE is active high, it starts when DE signal goes high. While DE is active, the panel latches the RGB data placed on the bus and draw a new pixel on the screen -in the current line-, for every pixel clock pulse. Data enable width is always equal to the horizontal resolution of the panel. In this example DE is 640 pixels long. After the active area, the HFP occurs, by this time, DE is inactive again and all the pixels in the line have been drawn. The line cycle ends when the new HSYNC pulse is asserted.

Similar to vertical timing, Table 6 shows horizontal timing characteristics (PIXCLK refers to pixel clock pulses).

| Parameter                        | Symbol | Min | Туре | Мах | Unit   |

|----------------------------------|--------|-----|------|-----|--------|

| Screen Width or Horizontal cycle | HP     | 750 | 800  | 900 | PIXCLK |

| HSYNC Pulse width                | HSW    | 1   | 1    | 1   | PIXCLK |

| Horizontal Back Porch+HSYNC      | HBP    | 46  | 46   | 46  | PIXCLK |

| Horizontal Front Porch           | HFP    | 64  | 114  | 214 | PIXCLK |

| Active Frame Width               | HDISP  | —   | 640  | —   | PIXCLK |

Table 6. Horizontal Timing Characteristics

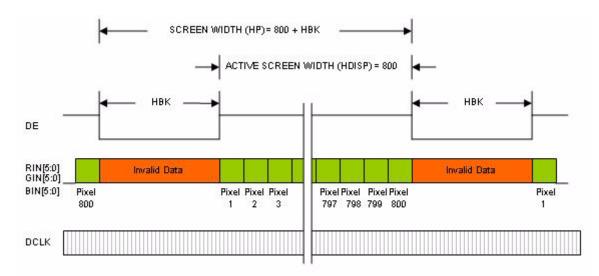

## 3.4.2.2.2 WVGA Horizontal Timing

The chart and table available for the WVGA (800H x 480V) datasheet is similar to the one shown in Figure 11.

Figure 11. WVGA Horizontal Timing Example

Table 7 shows the WVGA horizontal timing.

Table 7. WVGA Horizontal Timing

| Parameter                        | Symbol | Min | Туре | Max | Unit   |

|----------------------------------|--------|-----|------|-----|--------|

| Screen Width or Horizontal cycle | HP     | 850 | 900  | 950 | PIXCLK |

| Horizontal Blank Period          | НВК    | 50  | 100  | 150 | PIXCLK |

| Active Frame Width               | HDISP  | 800 | 800  | 800 | PIXCLK |

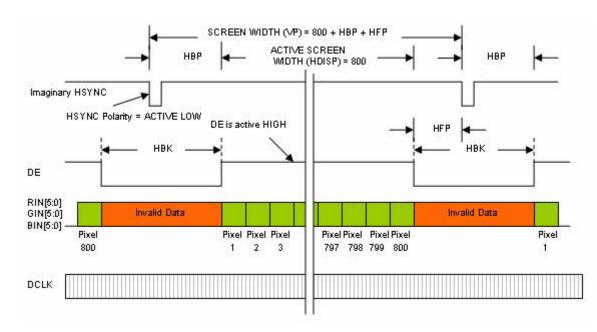

The approach followed in WVGA vertical timing section should be followed here to calculate HYNC width, HBP and HFP. See Section, "3.4.2.1.2 WVGA Vertical Timing," for information on WVGA Vertical timing.

The imaginary HSYNC signal is similar as shown in Figure 12.

Table 8 shows the WVGA horizontal timing.

| Table 8 | . WVGA | Horizontal | Timing |

|---------|--------|------------|--------|

|---------|--------|------------|--------|

| Parameter                        | Symbol | Min | Туре | Мах | Unit   |

|----------------------------------|--------|-----|------|-----|--------|

| Screen Width or Horizontal cycle | HP     | 850 | 900  | 950 | PIXCLK |

| HSYNC Width                      | HSW    | 1   | 1    | 1   | PIXCLK |

| Horizontal Back Porch+HSYNC      | HBP    | 1   | 50   | 150 | PIXCLK |

| Horizontal Front Porch           | HFP    | 0   | 50   | 149 | PIXCLK |

| Horizontal Blank Period          | НВК    | 50  | 100  | 150 | PIXCLK |

| Active Frame Width               | HDISP  | 800 | 800  | 800 | PIXCLK |

Synchronous Display Interface

## 2.4.2.3 Pixel Clock Timing

The VGA, WVGA pixel clock timings and the data polarity are explained in the following sections.

### 3.4.2.3.1 VGA Pixel Clock Timing

Pixel clock waveform characteristics in the datasheet is similar to the one shown in Figure 13.

Figure 13. VGA Pixel Clock Timing Example

Table 9 shows the pixel clock frequency parameter.

Table 9. Pixel Clock Frequency Parameter

| Parameter             | Symbol | Min | Туре | Мах | Unit |

|-----------------------|--------|-----|------|-----|------|

| Pixel Clock Frequency | PCLK   | 23  | 25   | 30  | MHz  |

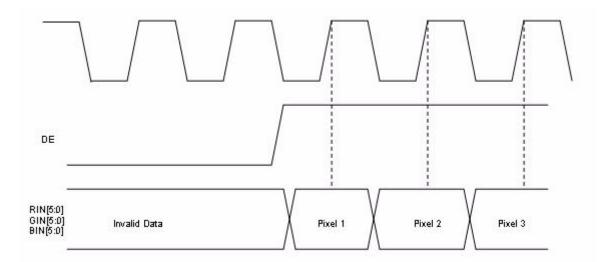

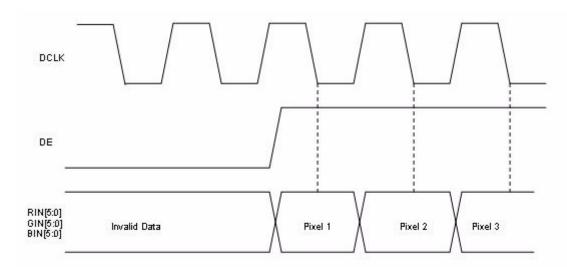

Pixel clock frequency is directly related with the frame refresh rate. Also, it is important as it determines when RGB data is latched by the panel. This is significant because i.MX35 prepares the data one edge before the LCD panel latches the data from the bus. A similar chart is usually included in the datasheet. In this case, data is latched by the LCD panel on DCLK rising edges, so i.MX35 should be configured to write the RGB data to the bus on the (previous) falling edge. In this manner, the data is ready and stable when the LCD panel reads it. This waveform in Figure 13 shows the typical inverse clock polarity. Clock polarity is set in the DI\_DISP\_SIG\_POL i.MX35 register, under the D3\_CLK\_POL bit-field.

### NOTE

The maximum display clock rate cannot be greater than a quarter of the high speed processing clock rate.

The HSP\_CLK in the i.MX35 PDK BSP is 133 MHz, so the maximum pixel clock is 133 MHz / 4 = 33.25 MHz. However, most LCD displays can work with lower frequencies than the typical values.

#### 3.4.2.3.2 WVGA Pixel Clock Timing

The pixel clock chart is similar to the one shown in Figure 14.

Figure 14. WVGA Pixel Clock Timing Example

Table 10 shows Pixel Clock Frequency Parameter.

Table 10. Pixel Clock Frequency Parameter

| Parameter             | Symbol | Min | Туре | Мах | Unit |

|-----------------------|--------|-----|------|-----|------|

| Pixel Clock Frequency | PCLK   | 25  | 27   | 32  | MHz  |

In contrast to the VGA panel, the WVGA display latches RGB data on DCLK falling edges, so i.MX35 should be configured to write the RGB data to the bus on the rising edge. The data is ready and stable when the panel reads it. The waveform in Figure 14 shows the straight clock polarity.

#### 3.4.2.3.3 Data Polarity

The Data Polarity feature is the value of the active signals in the RGB bus which the LCD recognizes. For example, consider that i.MX35 is trying to draw a red pixel (only red component), using an RGB565 interface and the LCD uses straight polarity of the value in the bus would be 0xF800. Then it means that all Red bits are in high and other bits are in low. However, if the LCD utilizes inverse Data Polarity, the value would be 0x07FF, which means Red bits are in low and other bits are in high. Both values represent the red color, and the difference in the value is caused by the data polarity on the LCD panel. This feature is configured using the D3\_DATA\_POL bit-field on the DI\_DISP\_SIG\_POL i.MX35 register.

## 2.4.3 Custom LCD Timing

The examples given in this application note does not require extra signals for LCD functionality. But if the LCD requires a RESET signal or initialization routine through a synchronous serial interface, then a similar chart as shown in Figure 17 can be found.

Synchronous Display Interface

### 2.4.3.1 Reset

The Reset and Serial Command interface are explained in the following sections.

#### 3.4.3.1.1 Reset

Many LCD panels include an LCD controller which requires an external system reset. If the LCD mentions the signal usage, then the timing required for this pulse should be found out.

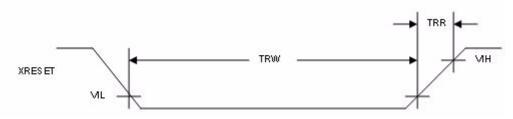

Figure 15 shows an example of Reset signal.

Figure 15. Reset Signal Example

Table 11 shows the Reset parameters.

**Table 11. Reset Parameters**

| Parameter         | Symbol | Min | Туре | Мах | Unit |

|-------------------|--------|-----|------|-----|------|

| Reset Width       | TRW    | 15  | _    | _   | ns   |

| Reset Rising time | TRR    | _   | _    | 10  | ns   |

Based on the above chart, the important fact that can be observed is that the RESET signal is ACTIVE LOW. It means RESET signal must be in high during normal operation, and also that it must be LOW for at least 15 ns to ensure that it was a valid reset. This waveform restricts the rising time of the signal to 10 ns. For this reason, it is recommended not to use a RC circuit to provide this signal. Generally this pin would be driven by an i.MX35 GPIO.

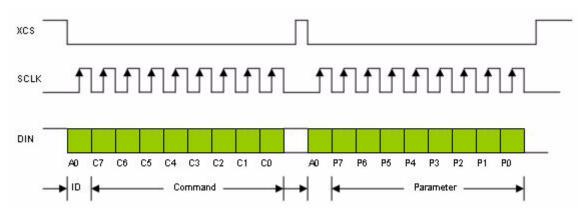

#### 3.4.3.1.2 Serial Command Interface

When a LCD panel has a serial command interface, then a chart similar to the one shown in Figure 16 has to be included in the datasheet.

Figure 16. SPI Command Interface Signal Example

Although it is important to understand how to initialize LCD, this application note does not review all serial interfaces of the LCD.

The protocols and data format are described in the datasheet. The user should have prior knowledge in using synchronous serial interfaces to program these settings. See Chapter 16: Configurable Serial Peripheral Interface (CSPI) of the *MCIMX35 Multimedia Applications Processor Reference Manual* for more information.

## 2.5 LCD Panels Supported by the i.MX35

The i.MX35 processor supports up to four simultaneous displays handled by the Display controllers DISP0, DISP1, DISP2 and DISP3.

Table 12 shows the details of the display controllers.

#### Table 12. Display Controllers

| Display | Display Type | Interface                                          |

|---------|--------------|----------------------------------------------------|

| DISP0   | Asynchronous | Parallel Interface Only                            |

| DISP1   | Asynchronous | Serial and Parallel Interface                      |

| DISP2   | Asynchronous | Serial and Parallel Interface                      |

| DISP3   | Asynchronous | RGB Interface (HSYNC, VSYNC, PIXCLK, up to RGB888) |

Only one of the LCD display controllers on the i.MX35 is synchronous (dumb display). This document focusses on the DISP3 controller. Note that the DISP3 RGB interface is multiplexed with other asynchronous parallel interfaces. It means that the data can be sent to a synchronous display (DISP3) and also to another parallel display device at the same time. But, the i.MX35 sends data to the asynchronous panel (smart display) while the synchronous interface is inactive (during Horizontal and vertical back and

front porches). As a result, the frame rate of smart displays can be affected when multiple displays are attached to the i.MX35.

The synchronous LCD interface on the i.MX35 is very flexible. It can handle many types of LCD devices, as long as these devices have the following characteristics.

- Synchronous Display (Dumb Display).

- RGB interface (RGB888 maximum).

- Resolution up to SVGA.

- Utilization of at least data enable and pixel clock to latch RGB Data (some LCDs need HSYNC and VSYNC signals also, which are also supported by the i.MX35).

- Maximum pixel clock frequency of 33.25 MHz.

In addition, the i.MX35 can handle dumb displays with a SHARP interface, but its support is limited to certain models. See Section 4.7.13.2 Interface to Sharp HR-TFT Panels in *i.MX35 (MCIMX35) Multimedia Applications Processors datasheet* for information regarding the timing restrictions.

As this application note is only intended for nonsharp dumb displays, smart displays and SHARP displays interfaces are not covered.

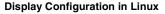

## 3 Display Configuration in Linux

This section describes how to add a new panel to Linux. It also describes the general display infrastructure in Linux and analyzes the i.MX family implementation.

## 3.1 Linux Framebuffer

The framebuffer device provides an abstraction for the graphics driver. It represents the frame buffer of some video hardware, and allows application software to access the graphic hardware through a well-defined interface. The advantage is that the software does not need to know anything about the low-level interface.

The framebuffer is a concept related to the video controller for a graphics display. The framebuffer is a memory buffer for the video controller that contains a data frame. This data frame is shown as an information on the display. The information provided to the frame is basically, color values for each pixel.

Some of the advantages of the Framebuffer infrastructure are its ease-of-use and the user applications can access video memory directly (using mmap). As Framebuffer is implemented as a character device, user applications can interface with the device using common system calls such as open(), read(), write() and ioctl(). All these functions are part of the file operations interface that every character device should contain.

However, the framebuffer has the advantage of mmap(). This function, by definition, maps files or devices to program memory. In this case, the video buffer area is the resource that is mapped. So, the user can apply mmap() to get the user space memory equivalent of the hardware video frame buffer.

The result is that the user gets a pointer to the framebuffer memory and the changes made to this memory is reflected on the display.

A similar procedure can be done using write() and seek() operations. However, this procedure is time consuming, as these functions may need to be called several times to cover a particular area of the framebuffer, or the whole display area.

## 3.1.1 Linux Framebuffer Structures

The Framebuffer in Linux provides a set of structures (some of which are used for user-space applications) that are important elements to be taken into consideration while developing a new panel driver.

The important data structures are:

- fb\_fix\_screeninfo

- fb\_bitfield

- fb\_ops

- fb\_info

- fb\_videomode

These definitions are available in the file .../include/linux/fb.h. In the following paragraphs, these structures are briefly described. See .../include/linux/fb.h file for more information and definition of each structure.

| struct fb_fix_screeninfo | This structure contains the fixed parameters for the graphics card/controller.<br>One of these fixed parameters is the start of the framebuffer memory<br>(unsigned long smem_start). This structure can be used in user applications.<br>Other important elements are:                                                                                                                                                                                                                                                                                                                                                                                          |

|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| struct fb_var_screeninfo | u32 smem_len: Length of the framebuffer memoryu32 type: Pixel format This structure contains the parameters for the graphics card/controller that can be modified. These are the features that the user configures such as resolution, number of bits per pixel (u32 bits_per_pixel). It also contains a structure that defines the length and bit offset for each color (struct fb_bitfield). This structure can be used in user applications. Other important elements are:                                                                                                                                                                                    |

| struct fb_bitfield       | <pre>u32 xres: Visible resolution in x<br/>u32 yres: Visible resolution in y<br/>u32 xoffset: Offset from virtual to visible in x axis.<br/>u32 yoffset: Offset from virtual to visible in y axis.<br/>struct fb_bitfield <color>: Color bitfields for red, green, blue and<br/>transparency (four of these are declared).<br/>This structures contain the details of each color in a pixel. The fields are the<br/>offset (beginning of a bitfieldu32 offset) the length (u32 length) and<br/>the most significant bit flag. One of these structures is declared for each<br/>color (red, green, blue and transparency) inside fb_var_screeninfo.</color></pre> |

|                          | <pre>struct fb_bitfield <color> {u32 offset; /* beginning of bitfield*/u32 length;/* length of bitfield*/u32 msb_right;/* != 0 : Most significant bit is */</color></pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

```

/* right */

};

```

For example, in a configuration where the mode is RGB888, the pixel width is 3 bytes. This means:

```

red.legth= 8 → red.offset= 24

green.length= 8 → green.offset = 16

blue.length= 8 → blue.offset = 8

```

struct fb\_ops

This structure contains function pointers to framebuffer operations. The operations range from basic or common functions for a driver, such as open and release, to functions oriented to the parameter settings or ioctl calls. Some of the functions are:

int (\*fb\_open)(struct fb\_info \*info, int user)

The operation for opening a fb device that is passed as an argument to a fb\_info structure pointer.

int (\*fb\_set\_par)(struct fb\_info \*info)

The operation for setting the video mode and other parameters, according to the content of the var (fb\_var\_screeninfo) element from the fb\_info structure pointer that is passed as an argument.

int (\*fb\_blank)(int blank, struct fb\_info \*info)

The operation to blank the display, passed as an argument to an fb\_info structure pointer.

int (\*fb\_ioctl)(struct fb\_info \*info, unsigned int cmd, unsigned long arg)

The function for input output operations such as performing request of structure values, or configuring structure values passed as an argument to a fb\_info structure pointer and a command to perform.

int (\*fb\_mmap)(struct fb\_info \*info, struct vm\_area\_struct \*vma)

The operation for executing mmap instruction passed as an argument to a fb\_info structure pointer and a pointer to a virtual memory area struct.

struct fb\_videomode This structure is used when the user wants to add support for a new panel. This structure gives specific information about the new panel such as name, resolution, pixel clock, timings for synchronization, margins and other variables that were described in previous sections, regarding LCD timings. The structure filling is described in the panel sections.

```

struct fb_videomode {

const char *name;/* optional */

u32 refresh;/* optional */

u32 yres;

u32 yres;

u32 pixclock;

u32 left_margin;

u32 right_margin;

u32 upper_margin;

u32 lower_margin;

u32 lower_margin;

u32 vsync_len;

u32 vsync_len;

```

NP

u32 sync;

u32 vmode;

u32 flag;

;

This is an important structure in the framebuffer framework. It is the place where all the previously mentioned structures are declared. Other structures and elements are also included, such as pointers to a device, to an event queue, or current display device specifications. It also contains structures that are enabled depending on conditional building. For example, when the support for backlight is enabled.

When a framebuffer driver gets registered with the kernel, it makes use of a pointer to this type of structure, containing the information (in several different structures) for the current specific hardware panel. This structure is visible only to the kernel.

```

struct fb_info {

...

struct fb_var_screeninfo var;/* Current var */

struct fb_fix_screeninfo fix;/* Current fix */

struct fb_monspecs monspecs;/* Current Monitor specs */

struct work_struct queue;/* Framebuffer event queue */

...

struct fb_cmap cmap;/* Current cmap */

...

struct fb_videomode *mode;/* current mode */

...

struct fb_ops *fbops;

struct device *device;/* This is the parent */

struct device *dev;/* This is this fb device */

...

};

```

Framebuffer implementation is available in the following file:

.../drivers/video/fbmem.c

The following section, see Section 3.2, "Linux Framebuffer for i.MX," describes this file and all the i.MX framebuffer implementation sources. It also describes the important functions and structures and a general flow chart for the initialization process.

Summarizing the framebuffer framework:

- For using the framework in user-space, the framebuffer device is like a /dev/mem (/dev/fb\* char device), so file operations used for any character devices can be used (open, read, write, mmap).

- A good example of a framebuffer driver is the virtual framebuffer that is located at .../drivers/video/vfb.c. This implementation follows some actions that should be followed for the development of any framebuffer driver like: filling the fix and var structures contained in the fb\_info structure targeted to the current panel; filling the file operations structure and then the driver information for the fb\_info structure. The following step is to initialize hardware and the memory area, and finally the registration of the framebuffer driver using a pointer to the current fb\_info structure

## 3.2 Linux Framebuffer for i.MX

The LCD driver and the framebuffer implementation for the i.MX family requires the framebuffer framework. This framework is used to have hardware access ability and to create an abstraction layer for the software, so it does not need to know about the low level.

Once the driver is loaded (if it was marked on the kernel configuration screen, under device drivers >> graphics support), the hardware can be accessed using special nodes (like any other character device) that are located in the /dev directory of the root. As mentioned earlier, the nodes are available in /dev/fb\*.

The usage of the nodes (/dev/fb\*) as an access mechanism allows some ioctls to interact, set, or get information from the device. Some of the ioctl functions are as follows:

- Request information such as name, organization, addresses, length.

- Request and change variable information about the hardware such as geometry, depth, color or timing.

- Get and set parts.

The following section describes the i.MX framebuffer implementation that interacts with the generic framebuffer driver. A general description of the initialization process is also provided and a flow chart that shows the different stages of the framebuffer implementation is also provided.

## 3.2.1 Initialization Process

As any other driver initialization process, the framebuffer contains several sections. In each section, specific functions to initialize resources and probe or testing hardware are used. All files that are important part of the framebuffer startup should initialize and pass through the binding process. Therefore, functions like init and probe are described constantly, because these functions consume most of the time during the fb startup.

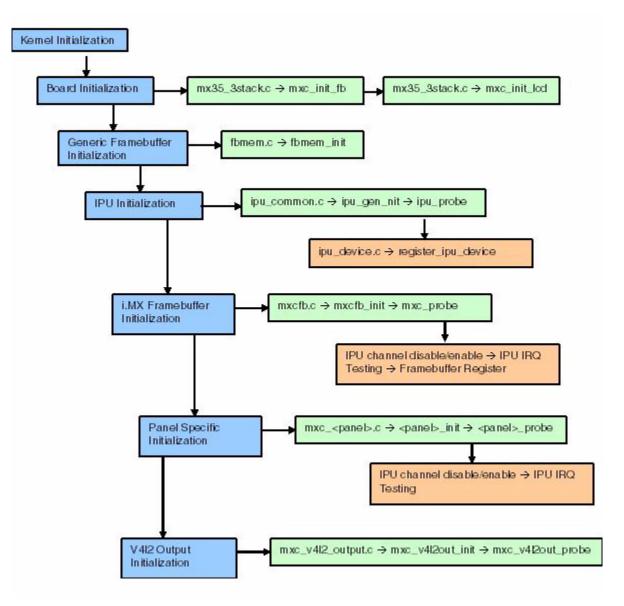

Kernel Start up (mx35\_3Stack.c)

The initialization process of the framebuffer starts early, when the kernel calls the functions associated with the configuration of the board (in this case, the i.MX35 3-Stack Board). This function, called mxc\_board\_init, is basically the initialization of the important subsystems on the board. Among these systems, the framebuffer is started by registering a platform device containing some data relevant to the driver such as name, dma mask, and so on (mxc\_init\_fb).

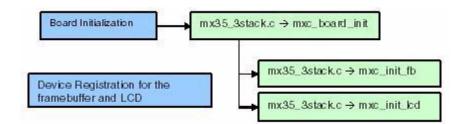

Framebuffer Initialization (fbmem.c)

This is the initialization of the framebuffer driver but it is not attached to any specific platform. By default, it starts the resources and important structures (most of the structures are described in the previous section) using the fbmem\_init function (it registers the fb char device).

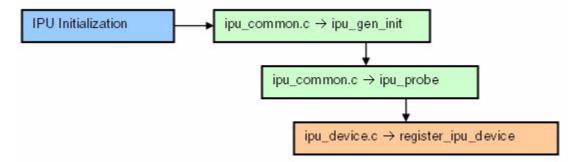

#### IPU initialization (ipu\_common.c)

The next step is setting up the IPU module from the IPU generic parameters, to its registration as a device on the system, and the initial configuration of

processes and associated modules, such as Synchronous Display Controller (SDC).

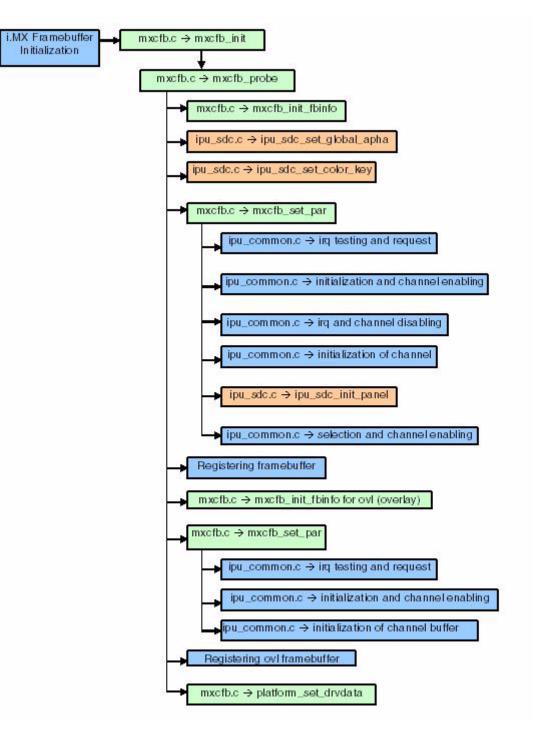

#### i.MX Framebuffer Initialization (mxcfb.c)

After the IPU gets registered as a device, initialized, and probed, the next layer of software related to the implementation of the frame buffer for the i.MX family is initialized and tested with its components. The framebuffer carries out the initialization and other activities, and calls the IPU functions. The initialization process covers the registration of the framebuffer for i.MX as a platform driver. Most of the process is covered by the probe function, where (among other resources settings) the framebuffer gets registered. The probe function for the framebuffer, in general, executes tests related to the IPU such as initializing modes for the SDC module, tests for IPU\_IRQ, enabling channels, disabling channels, and registering the framebuffer.

#### Specific Panel Driver (mxcfb\_claa\_wvga.c, mxcfb\_epson\_vga or similar)

The driver for the i.MX platform can be termed as a generic driver that can work for several panels (see mxcfb\_modedb.c file for information on the available panel configurations). However, a new panel requires a specific driver, as it can have a different interface. In such cases, the driver is similar to the mxcfb.c; but, is more specific. The usage of the initialization and probe functions are also similar. This driver does not replace the mxcfb.c, but it is complementary to it. So, to enable proper functionality of the panel, both files should be built into the system.

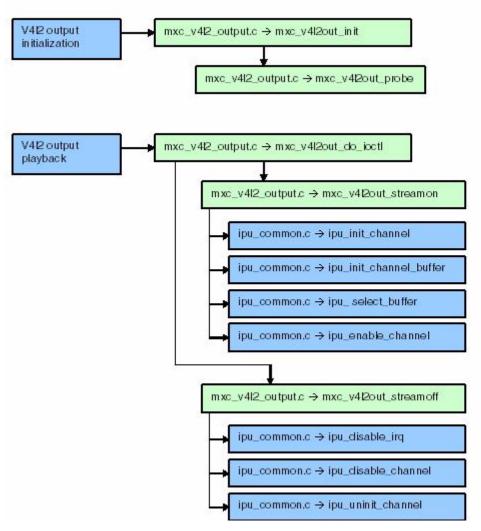

#### Video 4 Linux Initialization (mxc\_v4l2\_output.c)

All elements to set up the framebuffer and to get the display working have been set. If video usage is required, then an extra step is needed. The BSP contains generic drivers that follow the v4l2 specification, for capture and output. These drivers are loaded after all the framebuffer and IPU setup is complete. The output driver makes use of IPU post-processing functions for its operation. It also contains an initialization routine and a probe routine.

## 3.2.2 Initialization Flow Chart

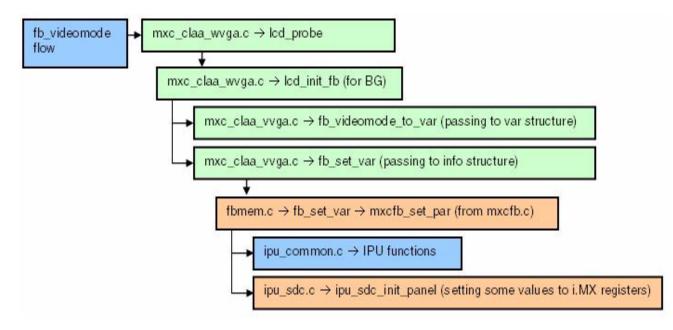

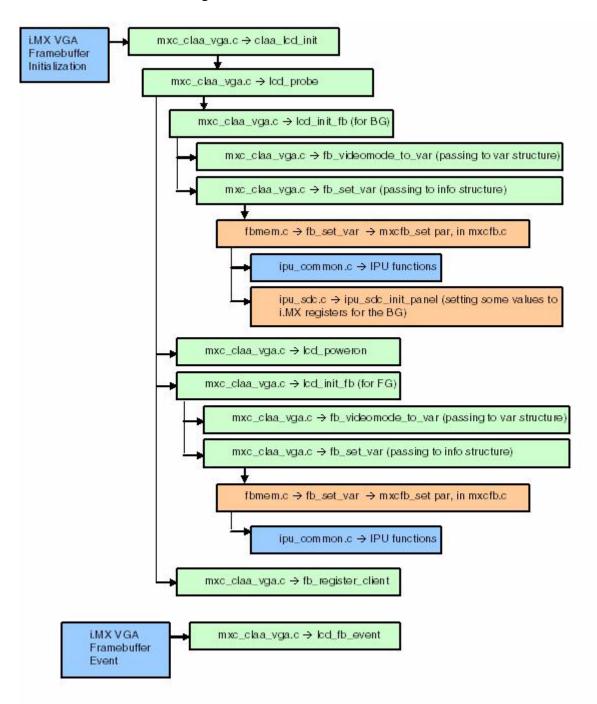

Figure 17 shows the initialization flow chart.

Figure 17. Initialization Flow Chart

## 3.2.3 Files and Important elements

This section provides more details on the files mentioned earlier in Section 3.2, "Linux Framebuffer for i.MX," and other files.

### 3.2.3.1 mx35\_3stack.c

#### Location: /arch/arm/mach-mx35/mx35\_3stack.c

**Generalities**: This file contains the initialization and set up routines for the i.MX35 3-Stack Board. It is called during kernel start up. The most important function is mxc\_board\_init, as it calls several different module specific routines, mxc\_init\_fb among them, which registers the framebuffer as a platform device. Not a lot of information is provided. It gives a name, DMA mask, and some platform data (a char with the type of panel). The mxc\_board\_init sets the clocks, GPIO modules, the PMIC, and so on. Also, there is a small initialization of a LCD structure in the function mxc\_init\_lcd. This registers a platform device structure for the LCD.

```

static struct platform_device lcd_dev = {

.name = "lcd_claa",

.id = 0,

.dev = {

.release = mxc_nop_release,

.platform_data = (void *)&lcd_data,

},

};

static void mxc_init_lcd(void)

platform_device_register(&lcd_dev);

#if defined(CONFIG_FB_MXC_SYNC_PANEL) || defined(CONFIG_FB_MXC_SYNC_PANEL_MODULE)

/* mxc lcd driver */

static struct platform_device mxc_fb_device = {

.name = "mxc_sdc_fb",

.id = 0,

.dev = {

.release = mxc_nop_release,

.coherent dma mask = 0xFFFFFFFF,

},

};

static void mxc_init_fb(void)

ł

(void)platform_device_register(&mxc_fb_device);

}

#else

static inline void mxc_init_fb(void)

#endif

```

#### mx35\_3stack Flow Chart:

Figure 18 shows the mx35\_3stack flow chart.

Figure 18. mx35\_3stack Flow Chart

## 3.2.3.2 fbmem.c

Location: /drivers/video/fbmem.c

**Generalities**: This file contains initialization of the framebuffer subsystem for Linux. Apart from the initialization, it also includes the file operations (fops) common for a char device plus the usage of the mmap() function, which is widely used in this case (and not always used in other char devices). There are also general routines for the panel framebuffer drivers like register and unregister framebuffer devices. Functions that display the logo during the booting process is also available in this file.

**Important Functions or Structures:** The module definition and registering functions are explained below:

struct fb\_info \*registered\_fb[FB\_MAX] \_\_read\_mostly

This can be seen as the global fb\_info structure for the framebuffer system.

int num\_registered\_fb \_\_read\_mostly

int is used to hold the frambuffers registered in the system.

static int \_\_init fbmem\_init(void)

Initialization of the framebuffer subsystem as a char driver, passing the fops table as a parameter (with the pointers to each one of the file operation functions). It also creates a class for graphics.

static void \_\_exit fbmem\_exit(void)R

Releases the char driver and deletes the graphics class.

int register\_framebuffer(struct fb\_info \*fb\_info)

Registers a framebuffer device taking the fb info structure as an argument.

int unregister\_framebuffer(struct fb\_info \*fb\_info)

Unregisters a framebuffer device taking the fb info structure as an argument.

file\_operations fb\_fops This structure contains the file operations for the frame buffer subsystem implemented as a char driver. The common read, write, open and ioctl are available, but mmap is also an important member.

```

static const struct file_operations fb_fops = {

.owner =THIS_MODULE,

.read =fb_read,

.write =fb_write,

.ioctl =fb ioctl,

#ifdef CONFIG_COMPAT

.compat_ioctl = fb_compat_ioctl,

#endif

.mmap =fb_mmap,

.open =fb_open,

.release =fb_release,

#ifdef HAVE_ARCH_FB_UNMAPPED_AREA

.get_unmapped_area = get_fb_unmapped_area,

#endif

#ifdef CONFIG_FB_DEFERRED_IO

.fsync =fb_deferred_io_fsync,

#endif

};

```

static int fb\_ioctl(struct inode \*inode, struct file \*file, unsigned int cmd, unsigned long arg)

A regular ioctl function for a character device, where the command to execute is passed as an argument and acts depending on the case selected. Some of the cases are: FBIOGET\_VSCREENINFO and FBIOGET\_FSCREENINFO that collects information about the variable or fixed values in the fb\_information structure.

static int fb\_mmap(struct file \*file, struct vm\_area\_struct \* vma)

mmap implementation for the framebuffer char driver.

#### fbmem.c Flow Chart:

Figure 19 shows the fbmem.c flow chart.

Figure 19. fbmem.c Flow Chart

Some of the IPU files are discussed in the following sections.

#### 3.2.3.3 ipu\_common.c

Location: drivers/mxc/ipu/ipu\_common.c

**Generalities**: This file contains the common software routines for IPU functionality such as channel, buffer, and IRQ management. It also contains the platform\_driver structure implemented for the IPU, init, and exit functions for the module

**Important Functions or Structures:** The module definition and registering functions are explained below:

platform\_driver mxcipu\_driverThis structure contains the power management pointers to the routines for testing the platform driver and behavior in low power modes.

```

static struct platform_driver mxcipu_driver = {

.driver = {

.name = "mxc_ipu",

},

.probe = ipu_probe,

.suspend = ipu_suspend,

.resume = ipu_resume,

};

```

int32\_t \_\_init ipu\_gen\_init(void)

This is an initialization routine for the IPU platform driver. It registers the mxcipu\_driver.

static void \_\_\_exit ipu\_gen\_uninit(void)

This exit routine is used for the IPU platform driver. It releases the IPU IRQs and unregisters the mxcipu\_driver.

static int ipu\_probe(struct platform\_device \*pdev)

This is Probe function for the mxcipu\_driver and it is called when the registration is made. It sets IRQ request and clocks for the IPU. It also registers the IPU device (see ipu\_device.c).

Common IPU functions: The common IPU functions are explained below:

| ipu_request_irq         | This function registers an interrupt handler for the specified interrupt lines that are defined in the enumeration ipu_irq_line (located in the ipu.h file).                                                                                                                                                |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ipu_disable_irq         | This function disables the interrupt for the specified interrupt line.                                                                                                                                                                                                                                      |

| ipu_enable_irq          | This function enables the interrupt for the specified interrupt line.                                                                                                                                                                                                                                       |

| ipu_init_channel_buffer | This function is called to initialize a buffer for a logical IPU channel. The parameters entered as inputs are physical addresses for the buffers, type of the buffers, logical channel ID, width and height in pixels and so on.                                                                           |

| ipu_select_buffer       | This function is used to mark a channel's buffers as ready. The channel ID and buffer type are passed as parameters.                                                                                                                                                                                        |

| ipu_init_channel        | This function is called to initialize a logical IPU channel. It uses a logical channel ID and a union with channel initialization parameters (ipu_channel_params_t included in ipu.h).                                                                                                                      |

| ipu_uninit_channel      | This function is used to uninitialize a logical IPU channel.                                                                                                                                                                                                                                                |

| ipu_link_channels       | This function links 2 channels together for automatic frame<br>synchronization. There are 2 parameters, one is the logical channel ID for<br>the source and the other is the logical channel ID for the destination, the<br>output of the source channel is linked to the input of the destination channel. |

| ipu_unlink_channels     | This function unlinks two channels and disables the automatic frame synchronization.                                                                                                                                                                                                                        |

ipu\_enable\_channel

This function enables a logical channel taking the channel ID as input.

ipu\_disable\_channel

This function disables a logical channel taking the channel ID as input.

ipu\_common.c Flow Chart:

Figure 20 shows the ipu\_common.c flow chart.

Figure 20. ipu\_common.c Flow Chart

#### NOTE

Many IPU functions that are widely called from framebuffer and v4l2 drivers (such as ipu\_init\_channel) are defined in ipu\_common.c.

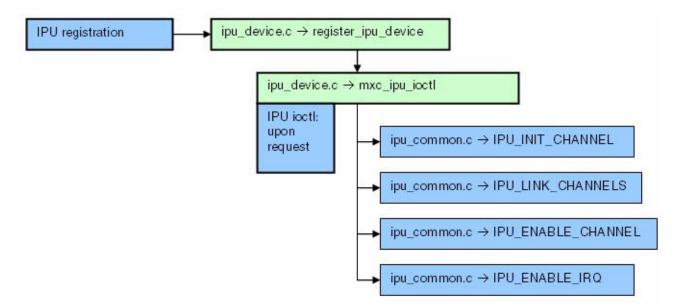

## 3.2.3.4 ipu\_device.c

Location: drivers/mxc/ipu/ipu\_device.c

**Generalities**: This file contains the structure and functions for the fops operations related to the mxc\_ipu device. It also contains a generic interrupt handler for the IPU related IRQs

Important Functions or Structures: The registering and other important functions are explained below:

int register\_ipu\_device() This function registers the mxc\_ipu as a char device, providing fops table and name. It also creates a class in the device model structure. This function is called from the probe() function in ipu\_common.c

static irqreturn\_t mxc\_ipu\_generic\_handler(int irq, void \*dev\_id)

This function is a generic handler for any IRQ that the IPU should process.

file\_operations mxc\_ipu\_fopsThis structure contains the file operations for the mxc\_ipu device.

```

static struct file_operations mxc_ipu_fops = {

.owner = THIS_MODULE,

.open = mxc_ipu_open,

.mmap = mxc_ipu_mmap,

.release = mxc_ipu_release,

.ioctl = mxc_ipu_ioctl

};

```

static int mxc\_ipu\_ioctl(struct inode \*inode, struct file \*file, unsigned int cmd, unsigned long arg)

ioctl function for the mxc\_ipu device. This function Processes commands passed as arguments. Most commands are specific functions described

earlier in the section ipu\_common.c such as IPU\_INIT\_CHANNEL, IPU\_LINK\_CHANNELSand so on.

#### ipu\_device.c Flow Chart:

Figure 21 shows the ipu\_device.c flow chart.

Figure 21. ipu\_device.c Flow Chart

Other important files for the IPU structure are explained below:

### 3.2.3.5 ipu\_sdc.c

Location: drivers/mxc/ipu/ipu\_sdc.c

**Generalities**: This file contains routines related to the SDC module on the IPU. The examples range from the sdc\_init to routines for setting alpha blending modes or color keys for the SDC plane.

## 3.2.3.6 ipu\_ic.c

Location: drivers/mxc/ipu/ipu\_ic.c

Generalities: This file contains routines for color conversion and resizing the sub modules of the IPU.

## 3.2.3.7 mxcfb\_modedb.c

Location: drivers/video/mxc/mxcfb\_modedb.c

**Generalities**: This file contains the declaration of an array of fb\_videomode structures related to the mxc framebuffer implementation. The elements are Sharp-VGA, NEC-VGA, TV out modes and so on. The data available on each structure refers to the important elements that describes each panel such as

resolution, timing and so on. See include/linux/fb.h for more information for the parameters contained in the structure.

## 3.2.3.8 mxcfb.c

Location: drivers/video/mxc/mxcfb.c

**Generalities**: This driver contains registering and initialization routines for the implementation of the framebuffer oriented to the i.MX Family. The structure related to the framebuffer, functions for registering the driver and setting up the frame buffer system for the normal framebuffer data structures for the overlay are initialized if they are enabled.

**Important Functions or Structures:** The module definition and registering functions are explained below:

platform\_driver mxcfb\_driverThe Structure created for the framebuffer driver implementation contains

the pointers to functions related to power management callbacks such as probe or suspend.

```

static struct platform_driver mxcfb_driver = {

.driver = {

.name = MXCFB_NAME,

},

.probe = mxcfb_probe,

.suspend = mxcfb_suspend,

.resume = mxcfb_resume,

};

The Structure that encapsulates two fb_info structures. The first structure

mxcfb_data

acts for the normal framebuffer and the second one for the overlay. This

structure also contains other flags.

struct mxcfb_data {

struct fb_info *fbi;

struct fb_info *fbi_ovl;

volatile int32_t vsync_flag;

wait_queue_head_t vsync_wq;

wait_queue_head_t suspend_wq;

bool suspended;

int backlight level;

};

int init mxcfb init(void)

The entry function for the framebuffer. It registers the platform driver

structure containing callback functions for power management and

shutdown conditions.

This is an framebuffer exit function. Its functions are: unmaps the video

void mxcfb_exit(void)

memory of the framebuffer structures, unregisters the fb info structure of

the framebuffer. These activities are carried by the fb info structure for the

framebuffer and the overlay. It also unregisters the platform driver structure

of the framebuffer.

```

static int mxcfb\_probe(struct platform\_device \*pdev)

This is the function member of the platform driver structure pointers. The probe function should verify if the specified device hardware exists. Several

|                                                                                                                                        | processes are executed in the probe function such as framebuffer<br>initialization, memory allocation, framebuffer registration (fb_info<br>structures for normal and overlay structures) and also IPU initialization that<br>involves setting the transparent color key for SDC graphic plane and the<br>foreground/background alpha blending modes.                  |

|----------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| static struct fb_info *mxcfb                                                                                                           | _init_fbinfo(struct device *dev, struct fb_ops *ops)                                                                                                                                                                                                                                                                                                                   |

|                                                                                                                                        | This function is called by mxc_probe. It allocates memory for the fb_info structure and fills information such as color maps and so on in the fields that are related to this structure.                                                                                                                                                                               |

| platform_set_drvdata(pdev,                                                                                                             | &mxcfb_drv_data)                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                        | This function is used to pass the address and information available in the mxcfb_drv_data structure to the platform device.                                                                                                                                                                                                                                            |

| Some of the file operations                                                                                                            | are discussed below.                                                                                                                                                                                                                                                                                                                                                   |

| fb_ops mxcfb_ops                                                                                                                       | This structure contains the pointers to the functions that can be used by the framebuffer driver to perform functions such as rectangle filling or cursor definitions. This structure is used for the normal framebuffer implementation.                                                                                                                               |

|                                                                                                                                        | <pre>uct fb_ops mxcfb_ops = {     owner = THIS_MODULE,     fb_set_par = mxcfb_set_par,     fb_check_var = mxcfb_check_var,     fb_setcolreg = mxcfb_setcolreg,     fb_pan_display = mxcfb_pan_display,     fb_ioctl = mxcfb_ioctl,     fb_fillrect = cfb_fillrect,     fb_copyarea = cfb_copyarea,     fb_imageblit = cfb_imageblit,     fb_blank = mxcfb_blank,</pre> |

| };<br>fb_ops mxcfb_ovl_ops                                                                                                             | This structure contains the pointers to the functions that can be used by the framebuffer driver to perform functions such as rectangle filling or cursor definitions. This structure is used for the overlay framebuffer implementation.                                                                                                                              |

| .owner = T<br>.fb_set_pa<br>.fb_check_<br>.fb_setcol<br>.fb_pan_di<br>.fb_ioctl<br>.fb_ioctl<br>.fb_fillre<br>.fb_copyar<br>.fb_imageb | <pre>bs mxcfb_ovl_ops = { HIS_MODULE, r = mxcfb_set_par, var = mxcfb_check_var, reg = mxcfb_setcolreg, splay = mxcfb_pan_display, = mxcfb_ioctl_ovl, mxcfb_mmap, ct = cfb_fillrect, ea = cfb_copyarea, lit = cfb_imageblit, = mxcfb_blank_ovl,</pre>                                                                                                                   |

static int mxcfb\_mmap(struct fb\_info \*fbi, struct vm\_area\_struct \*vma)

This function used to handle the mmap function for the mxc framebuffer.

static int mxcfb\_ioctl\_ovl(struct fb\_info \*fbi, unsigned int cmd, unsigned long arg)

static int mxcfb\_ioctl(struct fb\_info \*fbi, unsigned int cmd, unsigned long arg)

These functions are used to handle ioctl commands for the framebuffer. The first function is used for the normal framebuffer structure and the other is for the overlay structure.

static int mxcfb\_set\_par(struct fb\_info \*fbi)

This function is used to set the parameters (most of them from the videomode structure) to the processor's registers and calls ipu\_sdc\_init\_panel. This is also used to change the operating mode.

## mxcfb.c Flow Chart:

Figure 22 shows the mxcfb.c flow chart.

Figure 22. mxcfb.c Flow Chart

## 3.2.3.9 mxc\_v4l2\_output.c

Location: drivers/media/video/mxc/output/mxc\_v4l2\_output.c

**Generalities**: This file contains the implementation of the v4l2 standard for output devices targeted to the i.MX family. The file contains the common char driver infrastructure elements such as an initialization routine for registering the driver, a probe function and the standard file operations (fops) related to the v4l2 implementation. It also includes the functions that enable or disable the playback of video.

**Important Functions or Structures**: The module definition and registering functions are explained below:

platform\_driver mxc\_v4l2out\_driver