# **APPLICATION NOTE**

## AN262\_2 PCA954X FAMILY OF I<sup>2</sup>C / SMBus MULTIPLEXERS and SWITCHES

PCA9540B, PCA9541, PCA9542A, PCA9543A, PCA9544A, PCA9545A, PCA9546A, PCA9547, PCA9548A, PCA9549

Abstract - Philips Semiconductors family of Multiplexers and Switches are detailed in this application note that discusses device operation, software programming, pull up resistor sizing/bus termination and typical applications.

Paul Boogaards - Field Application Engineer Jean-Marc Irazabal - PCA Technical Marketing Manager Steve Blozis - PCA International Product Manager

Specialty Logic Product Line Logic Product Group

## Philips Semiconductors

October 27, 2004

## TABLE OF CONTENTS

| OVERVIEW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | TABLE OF CONTENTS             | 2  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|----|

| DESCRIPTION3APPLICATIONS3FEATURES3OPERATING CHARACTERISTICS4DEVICE PINOUT5ORDERING INFORMATION6DATA SHEETS AND IBIS MODELS6TECHNICAL INFORMATION6BLOCK DIAGRAM PCA954X DEVICES (EXCEPT PCA9541 AND PCA9549)6BLOCK DIAGRAM PCA95418BLOCK DIAGRAM PCA95429PC COMMUNICATIONS9INTERRUPTS11COMMAND SEQUENCING9NITERRUPTS13VOLTAGE CLAMPING13VOLTAGE TRANSLATION14HOW TO USE THE PCA9514 AS A 2-CHANNEL MULTIPLEXER15DETERMINING PULL-UP RESISTORS VALUES15APPLICATIONS19I <sup>2</sup> C MULTIPLEXING19VOLTAGE LEVEL SHIFTING19CAPACITIVE LOAD SHARING19TYPICAL APPLICATION20FREQUENTLY ASKED QUESTIONS20ADDITIONAL INFORMATION26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                               | 2  |

| APPLICATIONS       3         FEATURES       3         OPERATING CHARACTERISTICS       4         DEVICE PINOUT       5         ORDERING INFORMATION       6         DATA SHEETS AND IBIS MODELS       6         TECHNICAL INFORMATION       6         BLOCK DIAGRAM PCA954x DEVICES (EXCEPT PCA9541 AND PCA9549)       6         BLOCK DIAGRAM PCA9541       8         BLOCK DIAGRAM PCA9542       9         PC COMMUNICATIONS       9         INTERRUPTS       11         COMMUNICATIONS       9         INTERRUPTS       11         COMMUNICATIONS       9         INTERRUPTS       11         COMMAND SEQUENCING       9         POWER UP / RESET DEFAULT STATE       13         VOLTAGE CLAMPING       13         VOLTAGE TRANSLATION       14         HOW TO USE THE PCA9541 AS A 2-CHANNEL MULTIPLEXER       15         DETERMINING PULL-UP RESISTORS VALUES       15         APPLICATIONS       19         I <sup>2</sup> C MULTIPLEXING       19         VOLTAGE LEVEL SHIFTING       19         CAPACITIVE LOAD SHARING       19         CAPACITIVE LOAD SHARING       19         TYPICAL APPLICATION |                               |    |

| FEATURES       3         OPERATING CHARACTERISTICS       4         DEVICE PINOUT       5         ORDERING INFORMATION       6         DATA SHEETS AND IBIS MODELS       6         TECHNICAL INFORMATION       6         BLOCK DIAGRAM PCA954X DEVICES (EXCEPT PCA9541 AND PCA9549)       6         BLOCK DIAGRAM PCA9541       8         BLOCK DIAGRAM PCA9541       8         BLOCK DIAGRAM PCA9549       9         PC COMMUNICATIONS       9         INTERRUPTS       11         COMMAND SEQUENCING       13         POWER UP / RESET DEFAULT STATE       13         VOLTAGE CLAMPING       13         VOLTAGE TRANSLATION       14         HOW TO USE THE PCA9541 AS A 2-CHANNEL MULTIPLEXER       15         DETERMINING PULI-UP RESISTORS VALUES       15         APPLICATIONS       19         I <sup>2</sup> C MULTIPLEXING       19         VOLTAGE LEVEL SHIFTING       19         CAPACITIVE LOAD SHARING       19         TYPICAL APPLICATION       20         FREQUENTLY ASKED QUESTIONS       20         ADDITIONAL INFORMATION       26                                                         |                               |    |

| OPERATING CHARACTERISTICS       4         DEVICE PINOUT       5         ORDERING INFORMATION       6         DATA SHEETS AND IBIS MODELS       6         TECHNICAL INFORMATION       6         BLOCK DIAGRAM PCA954X DEVICES (EXCEPT PCA9541 AND PCA9549)       6         BLOCK DIAGRAM PCA9541       8         BLOCK DIAGRAM PCA9541       8         BLOCK DIAGRAM PCA9549       9         PC COMMUNICATIONS       9         INTERRUPTS       11         COMMAND SEQUENCING.       13         POWER UP / RESET DEFAULT STATE       13         VOLTAGE CLAMPING       13         VOLTAGE TRANSLATION       14         How to use THE PCA9541 As A 2-CHANNEL MULTIPLEXER       15         DETERMINING PULI-UP RESISTORS VALUES       15         APPLICATIONS       19         I <sup>2</sup> C MULTIPLEXING       19         VOLTAGE LEVEL SHIFTING       19         CAPACITIVE LOAD SHARING       19         TYPICAL APPLICATION       20         FREQUENTLY ASKED QUESTIONS       20         ADDITIONAL INFORMATION       20                                                                                 |                               |    |

| Device Pinout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                               |    |

| ORDERING INFORMATION6DATA SHEETS AND IBIS MODELS6 <b>TECHNICAL INFORMATION</b> 6BLOCK DIAGRAM PCA954x DEVICES (EXCEPT PCA9541 AND PCA9549)6BLOCK DIAGRAM PCA95418BLOCK DIAGRAM PCA95499PC COMMUNICATIONS9INTERRUPTS11COMMAND SEQUENCING13POWER UP / RESET DEFAULT STATE13VOLTAGE CLAMPING13VOLTAGE TRANSLATION14HOW TO USE THE PCA9541 AS A 2-CHANNEL MULTIPLEXER15DETERMINING PULL-UP RESISTORS VALUES15 <b>APPLICATIONS</b> 19I <sup>2</sup> C MULTIPLEXING19VOLTAGE LEVEL SHIFTING19VOLTAGE LEVEL SHIFTING19TYPICAL APPLICATION20 <b>FREQUENTLY ASKED QUESTIONS</b> 20 <b>ADDITIONAL INFORMATION</b> 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                               |    |

| DATA SHEETS AND IBIS MODELS6TECHNICAL INFORMATION6BLOCK DIAGRAM PCA954X DEVICES (EXCEPT PCA9541 AND PCA9549)6BLOCK DIAGRAM PCA95418BLOCK DIAGRAM PCA95499PC COMMUNICATIONS9INTERRUPTS11COMMAND SEQUENCING13POWER UP / RESET DEFAULT STATE13VOLTAGE CLAMPING13VOLTAGE TRANSLATION14HOW TO USE THE PCA9541 AS A 2-CHANNEL MULTIPLEXER15DETERMINING PULL-UP RESISTORS VALUES15APPLICATIONS19I <sup>2</sup> C MULTIPLEXING19VOLTAGE LEVEL SHIFTING19CAPACITIVE LOAD SHARING19TYPICAL APPLICATION20FREQUENTLY ASKED QUESTIONS20ADDITIONAL INFORMATION26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                               |    |

| TECHNICAL INFORMATION6BLOCK DIAGRAM PCA954x DEVICES (EXCEPT PCA9541 AND PCA9549)6BLOCK DIAGRAM PCA95418BLOCK DIAGRAM PCA95499PC COMMUNICATIONS9INTERRUPTS11COMMAND SEQUENCING13POWER UP / RESET DEFAULT STATE13VOLTAGE CLAMPING13VOLTAGE TRANSLATION14HOW to use THE PCA9541 AS A 2-CHANNEL MULTIPLEXER15DETERMINING PULI-UP RESISTORS VALUES15APPLICATIONS19I²C MULTIPLEXING19VOLTAGE LEVEL SHIFTING19CAPACITIVE LOAD SHARING19TYPICAL APPLICATION20FREQUENTLY ASKED QUESTIONS20ADDITIONAL INFORMATION26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                               |    |

| BLOCK DIAGRAM PCA954x DEVICES (EXCEPT PCA9541 AND PCA9549)6BLOCK DIAGRAM PCA95418BLOCK DIAGRAM PCA9549.9PC COMMUNICATIONS9INTERRUPTS11COMMAND SEQUENCING.13POWER UP / RESET DEFAULT STATE13VOLTAGE CLAMPING13VOLTAGE TRANSLATION.14HOW TO USE THE PCA9541 AS A 2-CHANNEL MULTIPLEXER15DETERMINING PULL-UP RESISTORS VALUES.15APPLICATIONS.19I <sup>2</sup> C MULTIPLEXING19VOLTAGE LEVEL SHIFTING19TYPICAL APPLICATION20FREQUENTLY ASKED QUESTIONS20ADDITIONAL INFORMATION26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                               |    |

| BLOCK DIAGRAM PCA95418BLOCK DIAGRAM PCA95499IFC COMMUNICATIONS9INTERRUPTS11COMMAND SEQUENCING13POWER UP / RESET DEFAULT STATE13VOLTAGE CLAMPING13VOLTAGE CLAMPING13VOLTAGE TRANSLATION14HOW TO USE THE PCA9541 AS A 2-CHANNEL MULTIPLEXER15DETERMINING PULL-UP RESISTORS VALUES15APPLICATIONS19I <sup>2</sup> C MULTIPLEXING19VOLTAGE LEVEL SHIFTING19CAPACITIVE LOAD SHARING19TYPICAL APPLICATION20FREQUENTLY ASKED QUESTIONS20ADDITIONAL INFORMATION26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                               |    |

| BLOCK DIAGRAM PCA95499IPC COMMUNICATIONS9INTERRUPTS11COMMAND SEQUENCING13POWER UP / RESET DEFAULT STATE13VOLTAGE CLAMPING13VOLTAGE TRANSLATION14HOW TO USE THE PCA9541 AS A 2-CHANNEL MULTIPLEXER15DETERMINING PULL-UP RESISTORS VALUES15APPLICATIONS19I <sup>2</sup> C MULTIPLEXING19VOLTAGE LEVEL SHIFTING19CAPACITIVE LOAD SHARING19TYPICAL APPLICATION20FREQUENTLY ASKED QUESTIONS20ADDITIONAL INFORMATION26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                               |    |

| PC COMMUNICATIONS.9INTERRUPTS11COMMAND SEQUENCING13POWER UP / RESET DEFAULT STATE13VOLTAGE CLAMPING13VOLTAGE CLAMPING13VOLTAGE TRANSLATION.14HOW TO USE THE PCA9541 AS A 2-CHANNEL MULTIPLEXER15DETERMINING PULL-UP RESISTORS VALUES.15APPLICATIONS.19I <sup>2</sup> C MULTIPLEXING.19VOLTAGE LEVEL SHIFTING19CAPACITIVE LOAD SHARING19TYPICAL APPLICATION.20FREQUENTLY ASKED QUESTIONS20ADDITIONAL INFORMATION26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                               |    |

| INTERRUPTS11COMMAND SEQUENCING13POWER UP / RESET DEFAULT STATE13VOLTAGE CLAMPING13VOLTAGE CLAMPING13VOLTAGE TRANSLATION14HOW TO USE THE PCA9541 AS A 2-CHANNEL MULTIPLEXER15DETERMINING PULL-UP RESISTORS VALUES15APPLICATIONS19I <sup>2</sup> C MULTIPLEXING19VOLTAGE LEVEL SHIFTING19CAPACITIVE LOAD SHARING19TYPICAL APPLICATION20FREQUENTLY ASKED QUESTIONS20ADDITIONAL INFORMATION26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                               |    |

| COMMAND SEQUENCING13POWER UP / RESET DEFAULT STATE13VOLTAGE CLAMPING13VOLTAGE TRANSLATION14HOW TO USE THE PCA9541 AS A 2-CHANNEL MULTIPLEXER15DETERMINING PULL-UP RESISTORS VALUES15APPLICATIONS19I <sup>2</sup> C MULTIPLEXING19VOLTAGE LEVEL SHIFTING19VOLTAGE LEVEL SHIFTING19TYPICAL APPLICATION20FREQUENTLY ASKED QUESTIONS20ADDITIONAL INFORMATION26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                               |    |

| POWER UP / RESET DEFAULT STATE13VOLTAGE CLAMPING13VOLTAGE TRANSLATION14HOW TO USE THE PCA9541 AS A 2-CHANNEL MULTIPLEXER15DETERMINING PULL-UP RESISTORS VALUES15 <b>APPLICATIONS</b> 19I <sup>2</sup> C MULTIPLEXING19VOLTAGE LEVEL SHIFTING19CAPACITIVE LOAD SHARING19TYPICAL APPLICATION20 <b>FREQUENTLY ASKED QUESTIONS</b> 20 <b>ADDITIONAL INFORMATION</b> 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                               |    |

| Voltage Clamping13Voltage Translation14How to use the PCA9541 as a 2-channel multiplexer15Determining Pull-Up Resistors values15APPLICATIONS19I <sup>2</sup> C Multiplexing19Voltage Level Shifting19Capacitive Load Sharing19Typical Application20FREQUENTLY ASKED QUESTIONS20ADDITIONAL INFORMATION26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                               |    |

| Voltage Translation14How to use the PCA9541 as a 2-channel multiplexer15Determining Pull-Up Resistors values15APPLICATIONS19I <sup>2</sup> C Multiplexing19Voltage Level Shifting19Capacitive Load Sharing19Typical Application20FREQUENTLY ASKED QUESTIONS20ADDITIONAL INFORMATION26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                               |    |

| How to use the PCA9541 as a 2-channel multiplexer15Determining Pull-Up Resistors values15APPLICATIONS19I²C Multiplexing19Voltage Level Shifting19Capacitive Load Sharing19Typical Application20FREQUENTLY ASKED QUESTIONS20ADDITIONAL INFORMATION26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                               |    |

| DETERMINING PULL-UP RESISTORS VALUES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                               |    |

| I <sup>2</sup> C MULTIPLEXING       19         VOLTAGE LEVEL SHIFTING       19         CAPACITIVE LOAD SHARING       19         TYPICAL APPLICATION       20         FREQUENTLY ASKED QUESTIONS       20         ADDITIONAL INFORMATION       26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                               |    |

| Voltage Level Shifting       19         Capacitive Load Sharing       19         Typical Application       20         FREQUENTLY ASKED QUESTIONS       20         ADDITIONAL INFORMATION       26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | APPLICATIONS                  |    |

| Voltage Level Shifting       19         Capacitive Load Sharing       19         Typical Application       20         FREQUENTLY ASKED QUESTIONS       20         ADDITIONAL INFORMATION       26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | I <sup>2</sup> C Multiplexing |    |

| Typical Application   20     FREQUENTLY ASKED QUESTIONS   20     ADDITIONAL INFORMATION   26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                               |    |

| FREQUENTLY ASKED QUESTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | CAPACITIVE LOAD SHARING       |    |

| ADDITIONAL INFORMATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | TYPICAL APPLICATION           | 20 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | FREQUENTLY ASKED QUESTIONS    |    |

| REVISION HISTORY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ADDITIONAL INFORMATION        |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | REVISION HISTORY              |    |

## **OVERVIEW**

#### Description

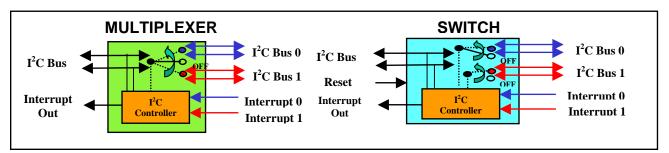

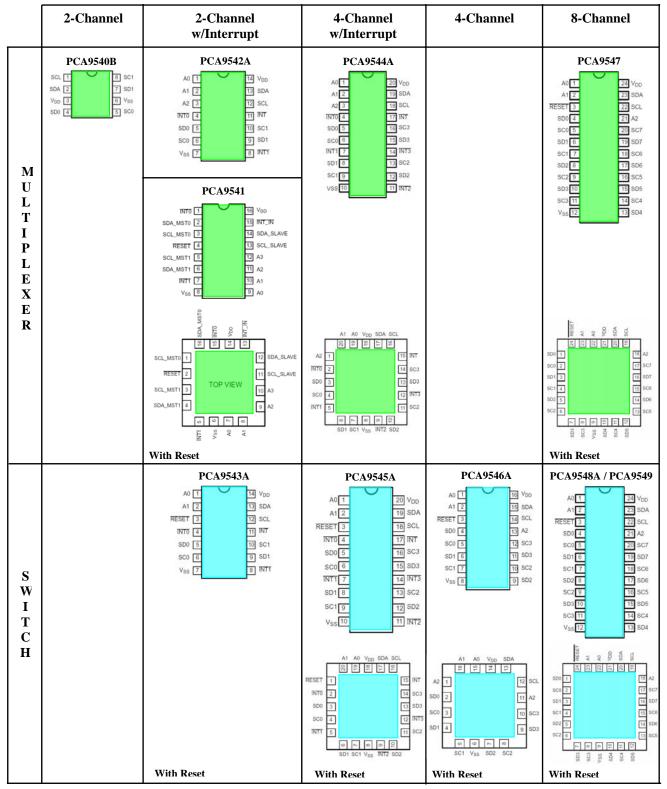

The Philips family of Multiplexers and Switches consists of bi-directional translating switches controlled via the  $I^2C$  or SMBus to fan out an upstream SCL/SDA pair to 2, 4 or 8 downstream channels of SCx/SDx pairs. The Multiplexers allow only one downstream channel to be selected at a time, while the Switches allow any individual downstream channel or combination of downstream channels to be selected, depending on the content of the programmable control register. Once one or several channels have been selected, the device acts as a wire, allowing the master on the upstream channel to send commands to devices on all the active downstream channels, and devices on the active downstream channels to communicate with each other and the master. External pull-up resistors are used to pull each individual channel up to the desired voltage level. Combined interrupt output and hardware reset input are device options that are featured.

## Applications

These devices can be used for a wide variety of applications:

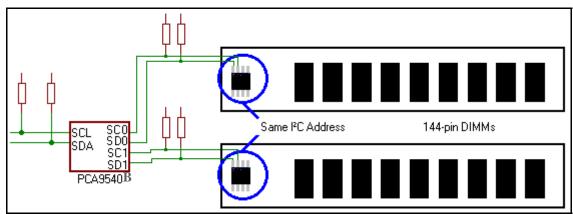

$I^2C$  Multiplexing - Some specialized devices only have one  $I^2C$  or SMBus address and sometimes several identical devices are needed in the same system. The multiplexers and switches split the  $I^2C$  bus into several sub-branches and allow the  $I^2C$  master to select and address one of multiple identical devices, in order to resolve address conflict issues.

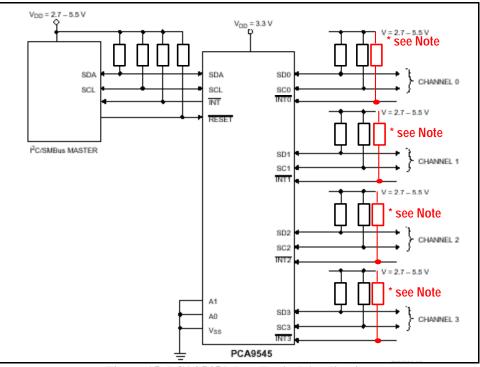

**Voltage Level Shifting** - Many I<sup>2</sup>C and SMBus devices operate at different voltage levels but need to operate on a common bus. The multiplexers and switches allow translation between 1.65 V and 5.5 V. So, for example, a 5 V I<sup>2</sup>C master on the upstream channel can communicate with a 3.3 V (non 5 V tolerant) SMBus device on channel 0 and a 2.5 V I<sup>2</sup>C device on channel 1. The channel pass gates are constructed such that the  $V_{DD}$  pin can be used to limit the maximum high voltage that will be passed by the device. This allows the use of different bus voltages on each pair, so that 1.8 V or 2.5 V or 3.3 V devices can communicate with 5 V devices without any additional protection. All I/O pins are tolerant up to 6.0 V. The Switches are best for this application since multiple downstream channels can be active at the same time.

**Capacitive Load Sharing** - Adding more  $I^2C$  and SMBus devices on the bus may exceed the 400 pF limitation. The multiplexers and switches can isolate devices that are not currently needed to reduce the overall system loading and maintain the total system load below 400 pF. When active, the channels act as a wire and the cumulative capacitive loading of the upstream channel and all active downstream channels must be considered.

#### Features

**Interrupt Function** - Interrupt inputs, one for each of the downstream channels, are provided as an option on both the Multiplexers and Switches. The single interrupt output acts as an OR of the interrupt inputs and is not latched.

**Hardware Reset** - An external active low hardware reset pin (/RESET) is provided on the Switches in addition to the Power On Reset (POR) feature found on both the Multiplexers and Switches. Either /RESET or POR resets the downstream channels to the default state of no channels selected. The reset feature is useful should a downstream device

lock up the bus and the master loses the ability to communicate. The master can use the reset to restore communication within the upstream channel and then selectively restore communication with the downstream channels without having to cycle power to the equipment or to other  $I^2C$  bus devices. The PCA9541 option /01 and /02 and the PCA9547 have one channel active at start up for applications that want a connection without having to address the multiplexer.

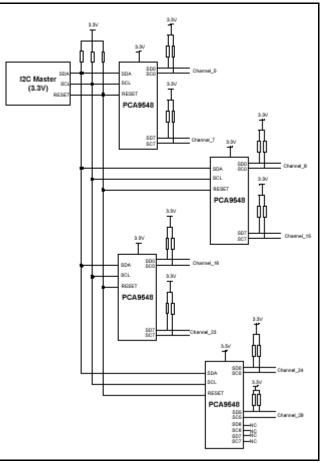

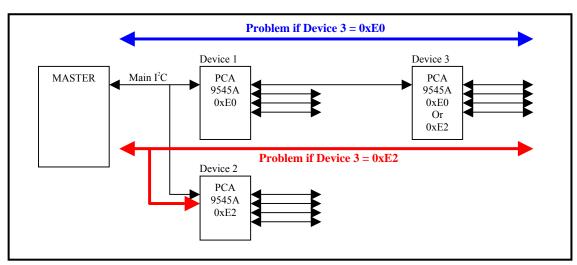

**Hardware Pins** - Up to three hardware pins (A0, A1, A2), except the PCA9541 that has an additional pin (A3), are provided to change the  $I^2C$  address and allow up to eight PCA954X devices (up to sixteen for the PCA9541) to share the same  $I^2C/SMBus$ .

|             | Ð                    |                 |                |                    |                | FEAT      | URES        |           |       |       |  |

|-------------|----------------------|-----------------|----------------|--------------------|----------------|-----------|-------------|-----------|-------|-------|--|

|             | 'no                  |                 |                | t)                 | н              | PACKAGES  |             |           |       |       |  |

| DEVICE NAME | MULTIPLEXER (In/Out) | SWITCH (In/Out) | # of ADDRESSES | INTERRUPT (In/Out) | HARDWARE RESET | PIN COUNT | SO (narrow) | SO (wide) | TSSOP | HVQFN |  |

| PCA9540B    | 1-2                  |                 | 1              |                    |                | 8         | D           |           | DP    |       |  |

| PCA9541     | 2-1                  |                 | 16             | 1-2                | •              | 16        | D           |           | PW    | BS    |  |

| PCA9542A    | 1-2                  |                 | 8              | 2-1                |                | 14        | D           |           | PW    |       |  |

| PCA9543A    |                      | 1-2             | 4              | 2-1                | •              | 14        | D           |           | PW    |       |  |

| PCA9544A    | 1-4                  |                 | 8              | 4-1                |                | 20        |             | D         | PW    | BS    |  |

| PCA9545A    |                      | 1-4             | 4              | 4-1                |                | 20        |             | D         | PW    | BS    |  |

| PCA9546A    |                      | 1-4             | 8              |                    | •              | 16        | D           |           | PW    | BS    |  |

| PCA9547     | 1-8                  |                 | 8              |                    | •              | 24        |             | D         | PW    | BS    |  |

| PCA9548A    |                      | 1-8             | 8              |                    | •              | 24        |             | D         | PW    | BS    |  |

| PCA9549     |                      | 8-bit           | 8              |                    | •              | 24        |             | D         | PW    | BS    |  |

Table 1. PCA954X Features

## **Operating Characteristics**

- 2.3 V to 5.5 V operating voltage

- •6.0 V tolerant I<sup>2</sup>C I/Os

- 0 kHz to 400 kHz operating frequency

- -40 °C to 85 °C operating temperature range

- I<sup>2</sup>C and SMBus compatible

- •ESD protection exceeds:

- •2000 V HBM per JESD22-A114

- •200 V MM per JESD22-A115

- •1000 V CDM per JESD22-C101

- JEDEC Standard JESD78 Latch-up testing exceeds 100 mA

- Manufactured in high volume BiCMOS process

#### **Device Pinout**

Table 2. PCA954X Pin Out

### **Ordering Information**

| Package | Container | PCA9540B      | PCA9541/0X <sup>(1)</sup> | PCA9542A      | PCA9543A      | PCA9544A     |

|---------|-----------|---------------|---------------------------|---------------|---------------|--------------|

| SO      | Tube      | PCA9540BD     | PCA9541D/0X               | PCA9542AD     | PCA9543AD     | PCA9544AD    |

| 30      | T & R     | PCA9540BD-T   | PCA9541D/0X-T             | PCA9542AD-T   | PCA9543AD-T   | PCA9544AD-T  |

| TSSOP   | Tube      | Not available | PCA9541PW/0X              | PCA9542APW    | PCA9543APW    | PCA9544APW   |

| 1330F   | T & R     | PCA9540BDP-T  | PCA9541PW/0X-T            | PCA9542APW-T  | PCA9543APW-T  | PCA9544APW-T |

| HVQFN   | T & R     | Not available | PCA9541BS/0X-T            | Not available | Not available | PCA9544ABS-T |

|         |           |               |                           |               |               |              |

| Package | Container | PCA9545A      | PCA9546A                  | PCA9547       | PCA9548A      | PCA9549      |

| SO      | Tube      | PCA9545AD     | PCA9546AD                 | PCA9547D      | PCA9548AD     | PCA9549D     |

| 30      | T & R     | PCA9545AD-T   | PCA9546AD-T               | PCA9547D-T    | PCA9548AD-T   | PCA9549D-T   |

| TSSOP   | Tube      | PCA9545APW    | PCA9546APW                | PCA9547PW     | PCA9548APW    | PCA9549PW    |

| 1330P   | T & R     | PCA9545APW-T  | PCA9546APW-T              | PCA9547PW-T   | PCA9548APW-T  | PCA9549PW-T  |

| HVQFN   | T & R     | PCA9545ABS-T  | PCA9546ABS-T              | PCA9547BS-T   | PCA9548ABS-T  | PCA9549BS-T  |

Note (1): X = 1, 2 or 3 and applies to the 3 different versions that are available

#### Table 3. PCA954X Ordering Information

The PCA9540/42/43/44/45/46/48 were made in a BiCMOS process in the Philips Semiconductors Albuquerque fabrication plant (ABQ), which was shut down in 2003, and the devices have been discontinued (DN-53). The replacement devices, PCA9540B/42A/43A/44A/45A/46A and 48A, are made in a CMOS process from Philips Semiconductors Boblingen Germany fabrication plant (PSB) and are drop in replacements. Technical comparison data can be requested from <u>I2C.Support@philips.com</u> to assist with the conversion.

#### Data Sheets and IBIS Models

Data sheets and IBIS models can be downloaded from <u>www.philips.com/i2clogic</u>

## **TECHNICAL INFORMATION**

#### Block Diagram PCA954x devices (Except PCA9541 and PCA9549)

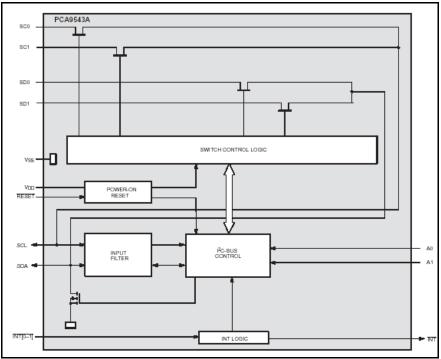

The PCA954X devices are bi-directional translating Multiplexers and Switches, controlled via the I<sup>2</sup>C-bus. The PCA9543A block diagram is shown in Figure 1 as an example for the entire family. The SCL/SDA upstream pair fans out to downstream pairs, or channels that are controlled by FET switches. The number of downstream pairs is device dependent. Exactly the same I<sup>2</sup>C signals on the upstream channel are passed onto all the downstream channels without amplification and the 400 pF I<sup>2</sup>C bus limitation must be observed for the upstream channel and all active downstream channels. Pull-up resistors are **REQUIRED** on all upstream and downstream channels.

$I^2C$  commands from the bus master on the upstream channel or any active downstream channel can turn on or turn off any channel. The channel status is changed when the stop command is sent. From the default condition of no channels active (except for the PCA9547 which defaults with Channel 0 active), only a master located on the upstream channel can activate downstream channels. A master on an unconnected downstream channel (not active) cannot activate its own or any other channel since the commands cannot reach the I<sup>2</sup>C-bus Control block. Once that downstream channel is activated however, any master on that channel can communicate with the I<sup>2</sup>C-bus Control block and can control other downstream channels.

The Multiplexers and Switches operate basically the same with the primary difference being within the  $I^2C$ -bus Control block. The Multiplexer  $I^2C$ -bus Controller activates only one channel at a time while the Switch  $I^2C$ -bus Controller activates as many channels as there are available, in any combination, as determined by the contents of the programmable control register.

Figure 1. PCA9543A Block Diagram

Both PCA954X Multiplexers and Switches offer a built-in Power-On Reset (POR) circuit block, which ensures all downstream channels are deactivated while the device is being powered up. The outputs are held in a high-impedance state that supports hot insertion.

Only certain devices offer an external hardware pin reset capability (/RESET). Holding the /RESET pin low will deactivate all the downstream channels, as well as reset the I<sup>2</sup>C state machine. This is useful when a rogue device on one of the downstream channels is holding the bus low. It allows the master to deactivate all downstream channels and regain control of the upstream bus without having to cycle power to the equipment to perform a POR to all I<sup>2</sup>C devices. A 10 k $\Omega$  (or sized to the master's output capacity) pull-up resistor is required to hold the /RESET pin high for normal device operation.

An Interrupt input pin is provided for each SCx/SDx downstream pair on select PCA954X Multiplexers and Switches. The active low open-drain interrupt output acts as an OR of the interrupt inputs and is not latched (When interrupt inputs are logic level high, the interrupt output is logic level high. When one or several interrupt occur and the interrupt inputs go to logic level low, the interrupt output goes logic level low). When the interrupt input condition disappears, the Interrupt output condition disappears as well.

Up to three external hardware address pins (A0, A1, A2) are provided that allow modification of the I<sup>2</sup>C address, which allows up to eight PCA954X devices to operate on the same I<sup>2</sup>C bus. The address pins must be held high to  $V_{DD}$  or low to ground. It is recommended they be held high through a 10 k $\Omega$  pull-up resistor to limit current flow in case of a short but if desired they can be tied directly to  $V_{DD}$ . Package pin limitations limit the number of address pins on some devices and that address bit is fixed internally.

All PCA954X Multiplexers and Switches can operate with a  $V_{DD}$  between 2.3 V to 5.5 V and the SDx/SCx pins are tolerant to voltages up to 6.0 V. The pass gates of the PCA954X devices are constructed such that the  $V_{DD}$  pin can be used to limit the maximum high voltage, which will be passed by the devices. This allows the use of different bus voltages on each SCx/SDx pair, so that, for example, 3.3 V devices can communicate with 5 V devices without any additional protection. External pull-up resistors pull the SCx/SDx pairs up to the desired voltage level.

The PCA954X devices can drive the SDA line and will do so to acknowledge commands sent to its specific I<sup>2</sup>C address. The PCA954X devices are slaves that **CANNOT** drive the SCL line. SCL and SDA signals driven by other devices pass transparently through the PCA954X device FET switches to any active channel.

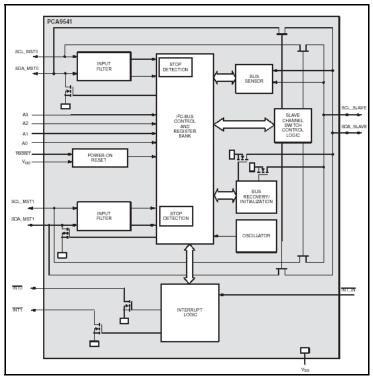

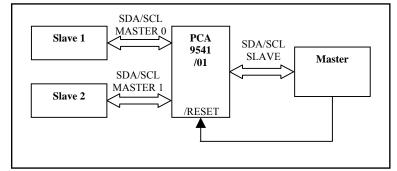

## Block Diagram PCA9541

The PCA9541 is primarily a 2-to-1 I<sup>2</sup>C master selector designed for high reliability dual master I<sup>2</sup>C applications where system operation is required, even when one master fails or the controller card is removed for maintenance. The two masters (e.g., primary and back-up) are located on separate I<sup>2</sup>C-buses (SDA/SCL\_MASTER0 and SDA/SCL\_MASTER1) that connect to the same downstream I<sup>2</sup>C-bus (SDA/SCL\_SLAVE) slave devices. I<sup>2</sup>C commands are sent by either I<sup>2</sup>C-bus master and are used to select one master at a time. Either master at any time can gain control of the slave devices if the other master is disabled or removed from the system. The failed master is isolated from the system and will not affect communication between the on-line master and the slave devices on the downstream I<sup>2</sup>C-bus.

Figure 2. PCA9541 Block Diagram

Three versions are offered for different architectures:

- PCA9541/01 with channel 0 selected at start-up

- PCA9541/02 with channel 0 selected after start-up and after stop condition is detected

- PCA9541/03 with no channel selected after start-up.

The 3 versions offer a built-in Power-On Reset (POR) circuit block, which ensures all downstream channels are deactivated while the device is being powered up. The outputs are held in a high impedance state that supports hot insertion.

The devices also offer an external hardware pin reset capability (/RESET). Holding the /RESET pin low will deactivate all the downstream channels, as well as reset the I<sup>2</sup>C state machine. It allows the master to initialize the device in a known default state (different depending on the version that is used). A 10 k $\Omega$  (or sized to the master's output capacity) pull-up resistor is required to hold the /RESET pin high for normal device operation.

The interrupt outputs are used to provide an indication of which master has control of the bus. One interrupt input (/INT\_IN) collects downstream information and propagates it to the 2 upstream I<sup>2</sup>C-buses (/INT0 and /INT1) if enabled. /INT0 and /INT1 are also used to let the previous bus master know that it is not in control of the bus anymore and to indicate the completion of the bus recovery/initialization sequence. Those interrupts can be disabled and will not generate an interrupt if the masking option is set.

External pull-up resistors pull the bus to the desired voltage level for each channel. All I/O pins are 6.0 V tolerant.

The PCA9541 device targets primarily applications different from the multiplexers and switches that are discussed in this application note. However, it can be used as a 2-channel multiplexer that defaults to channel 0 under certain conditions. Please refer to the paragraph "How to use the PCA9541 as a 2-channel multiplexer" for more detail.

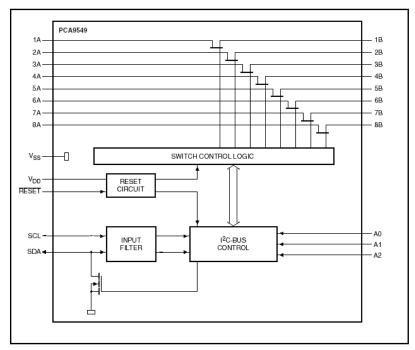

## Block Diagram PCA9549

The PCA9549 is similar to the PCA9548A with each channel selection now digital CBT type switch instead of an I<sup>2</sup>Cbus channel. The primary application is to allow digital signals to be turned on and off remotely via the I<sup>2</sup>C-bus. One example is it can be used to control the resistance in a test set up with different resistors (e.g., 100  $\Omega$ , 1 k $\Omega$ , 10 k $\Omega$ , 100 k $\Omega$ , 1 M $\Omega$ , 10 M $\Omega$ , 100 M $\Omega$ ) on each switch channel, allowing various resistance combinations controlled via the I<sup>2</sup>C-bus.

Figure 3. PCA9549 Block Diagram

#### **I<sup>2</sup>C Communications**

All PCA954X devices support both standard mode (100 kHz) and fast mode (400 kHz) I<sup>2</sup>C protocols. Once the channels have been selected and the stop command sent, the PCA954X devices act as a wire and will support up to 400 kHz I<sup>2</sup>C protocol throughput. A standard I<sup>2</sup>C communication between a master controller and a PCA954X device contains the following sequence:

- A Start condition

- A 8-bit word with the following information:

- a) PCA954X device addressing. 7 bits (as shown in Table 4) compose the address.

- b) The 8<sup>th</sup> bit (LSB, Least Significant Bit) is the Read (LSB at "1") or Write (LSB at "0") instruction

- Acknowledge from the slave (PCA954X addressed device)

- If a Write instruction is requested, the next 8-bit word is the Control register. It contains channel selection information. This register is explained in the Tables 2 and 3 below.

- If a Read instruction is requested, the master controller turns to a master receiver and the slave PCA954X device turns to a slave transmitter. Interrupt status (if the device has this feature) and channel selection status (2 or 4 LSB or the entire register depending on the device) are then provided to the master controller.

- If the previous 8-bit word was a Write, the slave PCA954X will send an Acknowledge to the master controller.

- If the previous 8-bit word was a Read, the slave PCA954X will not send an Acknowledge to the master controller.

- A Stop condition. When this condition will be detected by the PCA954X, the new channel configuration will be generated (if requested in the previous I<sup>2</sup>C communication).

| Device Type |     | I <sup>2</sup> C Address |     |      |       |      |    |     |  |

|-------------|-----|--------------------------|-----|------|-------|------|----|-----|--|

| Bit         | 7   | 6                        | 5   | 4    | 3     | 2    | 1  | 0   |  |

| PCA9540B    | 1   | 1                        | 1   | 0    | 0     | 0    | 0  | 1/0 |  |

| PCA9541     | 1   | 1                        | 1   | A3   | A2    | A1   | A0 | 1/0 |  |

| PCA9542A    | 1   | 1                        | 1   | 0    | A2    | A1   | A0 | 1/0 |  |

| PCA9543A    | 1   | 1                        | 1   | 0    | 0     | A1   | A0 | 1/0 |  |

| PCA9544A    | 1   | 1                        | 1   | 0    | A2    | A1   | A0 | 1/0 |  |

| PCA9545A    | 1   | 1                        | 1   | 0    | 0     | A1   | A0 | 1/0 |  |

| PCA9546A    | 1   | 1                        | 1   | 0    | A2    | A1   | A0 | 1/0 |  |

| PCA9547     | 1   | 1                        | 1   | 0    | A2    | A1   | A0 | 1/0 |  |

| PCA9548A    | 1   | 1                        | 1   | 0    | A2    | A1   | A0 | 1/0 |  |

| PCA9549     | 1   | 1                        | 1   | 0    | A2    | A1   | A0 | 1/0 |  |

|             | Tab | le 4.                    | PCA | 954X | Addre | sses |    |     |  |

Notes:

- A0, A1 and A2 in blue (dark gray) are the hardware programmable input pins that are connected to either V<sub>DD</sub> (logic level 1) or GND (logic level 0) and modify the device's I<sup>2</sup>C address.

- Up to four PCA954X devices can be attached to the same I<sup>2</sup>C bus when there are 2 address pins available.

- Up to eight PCA954X devices can be attached to the same I<sup>2</sup>C bus when there are 3 address pins available.

- Up to sixteen PCA9541 devices can be attached to the same  $I^2C$  bus when there are 4 address pins available.

- Since all PCA954X devices have the same fixed bits 7, 6, 5 and 4, the maximum allowed on the I<sup>2</sup>C bus is 8 of any combination of PCA954X devices.

- PCA9541 has 4 programmable address pins thus allowing 16 devices to share the same I<sup>2</sup>C-bus

The PCA954X multiplexers contain one Control register, which can be written to or read from. When writing to this register, the lower bits or the entire register (depending on the device) determine the active channel(s). At Power-up and when a Reset operation (Switches only) is initiated (/RESET asserted low), all channels are deactivated and no channels are active.

Table 5 describes the channel selection for the 2-channel PCA9540B/42A/43A, the 4-channel PCA9544A and the 8-channel PCA9547. "x" is don't care (0 or 1).

|   | ( | Contr | ol Re | giste | r |   |              | <b>Device Chan</b> | nel Selection |           |

|---|---|-------|-------|-------|---|---|--------------|--------------------|---------------|-----------|

| 6 | 5 | 4     | 3     | 2     | 1 | 0 | PCA9540B/42A | PCA9543A           | PCA9544A      | PCA9547   |

| х | Х | Х     | 0     | 0     | 0 | 0 | None         | None               | None          | None      |

| х | Х | Х     | 0     | 0     | 0 | 1 | None         | Channel 0          | None          | None      |

| х | Х | Х     | 0     | 0     | 1 | 0 | None         | Channel 1          | None          | None      |

| х | Х | Х     | 0     | 0     | 1 | 1 | None         | Channel 0 & 1      | None          | None      |

| х | Х | Х     | 0     | 1     | 0 | 0 | Channel 0    | None               | Channel 0     | None      |

| х | Х | Х     | 0     | 1     | 0 | 1 | Channel 1    | Channel 0          | Channel 1     | None      |

| х | Х | Х     | 0     | 1     | 1 | 0 | None         | Channel 1          | Channel 2     | None      |

| Х | Х | Х     | 0     | 1     | 1 | 1 | None         | Channel 0 & 1      | Channel 3     | None      |

| х | Х | Х     | 1     | 0     | 0 | 0 | None         | None               | None          | Channel 0 |

| х | Х | х     | 1     | 0     | 0 | 1 | None         | Channel 0          | None          | Channel 1 |

| х | Х | х     | 1     | 0     | 1 | 0 | None         | Channel 1          | None          | Channel 2 |

| х | Х | х     | 1     | 0     | 1 | 1 | None         | Channel 0 & 1      | None          | Channel 3 |

| х | Х | х     | 1     | 1     | 0 | 0 | Channel 0    | None               | Channel 0     | Channel 4 |

| х | Х | х     | 1     | 1     | 0 | 1 | Channel 1    | Channel 0          | Channel 1     | Channel 5 |

| х | Х | х     | 1     | 1     | 1 | 0 | None         | Channel 1          | Channel 2     | Channel 6 |

| Х | Х | Х     | 1     | 1     | 1 | 1 | None         | Channel 0 & 1      | Channel 3     | Channel 7 |

Table 5. 2, 4 and 8 Channel Device Active Channel Selection

Table 6 describes the channel selection for the 4-channel PCA9545A/46A and 8-channel PCA9548A/PCA9549. The PCA9545A/46A/48A and PCA9549 will respond to the channels in gray but only the 8-channel PCA9548A/PCA9549 will respond to the channels in blue (dark gray). "◆" in the Active Channel columns indicates that the channel is active.

|   |   | Con | trol l | Regis | ster |   |   |   |   |   | Active | Channe | ls |   |   |

|---|---|-----|--------|-------|------|---|---|---|---|---|--------|--------|----|---|---|

| 7 | 6 | 5   | 4      | 3     | 2    | 1 | 0 | 0 | 1 | 2 | 3      | 4      | 5  | 6 | 7 |

| 0 | 0 | 0   | 0      | 0     | 0    | 0 | 0 |   |   |   |        |        |    |   |   |

| 0 | 0 | 0   | 0      | 0     | 0    | 0 | 1 | • |   |   |        |        |    |   |   |

| 0 | 0 | 0   | 0      | 0     | 0    | 1 | 0 |   | • |   |        |        |    |   |   |

| 0 | 0 | 0   | 0      | 0     | 0    | 1 | 1 | • | • |   |        |        |    |   |   |

| 0 | 0 | 0   | 0      | 0     | 1    | 0 | 0 |   |   | • |        |        |    |   |   |

| 0 | 0 | 0   | 0      | 0     | 1    | 0 | 1 | • |   | • |        |        |    |   |   |

| 0 | 0 | 0   | 0      | 0     | 1    | 1 | 0 |   | • | • |        |        |    |   |   |

| 0 | 0 | 0   | 0      | 0     | 1    | 1 | 1 | • | • | • |        |        |    |   |   |

| 0 | 0 | 0   | 0      | 1     | 0    | 0 | 0 |   |   |   | •      |        |    |   |   |

| 0 | 0 | 0   | 0      | 1     | 0    | 0 | 1 | • |   |   | •      |        |    |   |   |

| 0 | 0 | 0   | 0      | 1     | 0    | 1 | 0 |   | • |   | •      |        |    |   |   |

| 0 | 0 | 0   | 0      | 1     | 0    | 1 | 1 | • | • |   | •      |        |    |   |   |

| 0 | 0 | 0   | 0      | 1     | 1    | 0 | 0 |   |   | • | •      |        |    |   |   |

| 0 | 0 | 0   | 0      | 1     | 1    | 0 | 1 | • |   | • | •      |        |    |   |   |

| 0 | 0 | 0   | 0      | 1     | 1    | 1 | 0 |   | • | • | •      |        |    |   |   |

| 0 | 0 | 0   | 0      | 1     | 1    | 1 | 1 | • | • | • | •      |        |    |   |   |

| 0 | 0 | 0   | 1      | 0     | 0    | 0 | 0 |   |   |   |        | •      |    |   |   |

| 0 | 0 | 0   | 1      | 0     | 0    | 0 | 1 | • |   |   |        | •      |    |   |   |

|   |   |     |        | •••   |      |   |   |   |   |   |        |        |    |   |   |

| 0 | 0 | 1   | 0      | 0     | 0    | 0 | 0 |   |   |   |        |        | •  |   |   |

| 0 | 0 | 1   | 0      | 0     | 0    | 0 | 1 | • |   |   |        |        | •  |   |   |

|   |   |     |        | •••   | •••  |   |   |   |   |   |        |        |    |   |   |

| 0 | 1 | 0   | 0      | 0     | 0    | 0 | 0 |   |   |   |        |        |    | • |   |

| 0 | 1 | 0   | 0      | 0     | 0    | 0 | 1 | • |   |   |        |        |    | • |   |

|   |   |     |        | •••   | •••  |   |   |   |   |   |        |        |    |   |   |

| 1 | 0 | 0   | 0      | 0     | 0    | 0 | 0 |   |   |   |        |        |    |   | • |

| 1 | 0 | 0   | 0      | 0     | 0    | 0 | 1 | • |   |   |        |        |    |   | • |

|   |   |     |        | •••   |      |   |   |   |   |   |        |        |    |   |   |

Table 6. 4 and 8 Channel Device Active Channel Selection

#### Note:

Several channels can be enabled at the same time. For example, in the PCA9548A/PCA9549, "10011101" means that channels 0, 2, 3, 4 and 7 are enabled and channels 1, 5 and 6 are disabled.

The control register can also be read in order to determine which channel(s) is (are) enabled or to check that a previous switch command has been correctly interpreted by the slave. For devices offering an Interrupt capability, a reading of the control register after Interrupt detection from the master controller will also determine which downstream channel(s) generated an Interrupt signal. A more detailed description of the interrupt function follows.

#### Interrupts

Devices offering the Interrupt capability provide the following pins:

- An active low Interrupt input pin for each SCx/SDx downstream pair.

- An open-drain Interrupt output. This signal acts as an OR of the interrupt inputs.

When no Interrupt is present (all the Interrupt inputs are at logic level High), then the Interrupt output is also at logic Level High. When any of the Interrupt inputs is logic level Low, then the Interrupt output is also Low. The control register reflects the inverted state of the interrupt inputs (as shown in Table 7). When the interrupting input signal goes away (returns to a High state), the output will also return to a High state (not latched) and the device does not keep in memory what caused the interrupt (the control register interrupt bits return to '0', values are not latched). The PCA9542A/43A only have interrupt channels 0 and 1 and don't include any of the interrupts in channel 2 and 3 (blue (dark gray) highlighted columns). The PCA9544A/45A have interrupt channels 0 through 3. " $\blacklozenge$ " in the Interrupt channel columns indicates that there is an interrupt.

|   |   | С | ontrol | Regist | er |   |   | Inter | rupt In | put Ch | annel |

|---|---|---|--------|--------|----|---|---|-------|---------|--------|-------|

| 7 | 6 | 5 | 4      | 3      | 2  | 1 | 0 | 0     | 1       | 2      | 3     |

| 0 | 0 | 0 | 0      | Х      | Х  | Х | Х |       |         |        |       |

| 0 | 0 | 0 | 1      | Х      | Х  | Х | х | •     |         |        |       |

| 0 | 0 | 1 | 0      | Х      | Х  | Х | х |       | •       |        |       |

| 0 | 0 | 1 | 1      | Х      | Х  | Х | Х | •     | •       |        |       |

| 0 | 1 | 0 | 0      | Х      | Х  | Х | Х |       |         | •      |       |

| 0 | 1 | 0 | 1      | Х      | Х  | Х | Х | •     |         | •      |       |

| 0 | 1 | 1 | 0      | Х      | Х  | Х | х |       | •       | •      |       |

| 0 | 1 | 1 | 1      | Х      | Х  | Х | Х | •     | •       | •      |       |

| 1 | 0 | 0 | 0      | Х      | Х  | Х | Х |       |         |        | •     |

| 1 | 0 | 0 | 1      | Х      | Х  | Х | х | •     |         |        | •     |

| 1 | 0 | 1 | 0      | Х      | Х  | Х | Х |       | •       |        | •     |

| 1 | 0 | 1 | 1      | Х      | Х  | Х | Х | •     | •       |        | •     |

| 1 | 1 | 0 | 0      | Х      | Х  | Х | Х |       |         | •      | •     |

| 1 | 1 | 0 | 1      | Х      | Х  | Х | Х | •     |         | •      | •     |

| 1 | 1 | 1 | 0      | Х      | Х  | Х | Х |       | •       | •      | •     |

| 1 | 1 | 1 | 1      | Х      | Х  | Х | Х | •     | •       | •      | •     |

Table 7. Interrupt Table

Notes:

- Interrupt inputs (values in the control register) and output are not latched

- Interrupt register cannot be changed programmatically (Read-only information).

The main function of the Interrupt feature is to let the upstream master know that it needs to service one of the downstream buses. By reading the control register, it is easy for the master to determine which of the downstream buses requires servicing.

#### Interrupt input signals:

Interrupt inputs don't have any internal pull-up resistors and <u>MUST NOT</u> be left floating in order to avoid any undesired interrupt conditions or additional current consumption due to undefined logic states. If one or several inputs are not used, they must be connected to  $V_{DD}$  through a pull-up resistor (4.7 k $\Omega$  for example).

- If the device generating the interrupt has an open-drain structure or can be 3-stated, a pull-up resistor to V<sub>DD</sub> must be used.

- If the device generating the interrupt has a totem pole output structure and cannot be 3-stated; pull-up resistors to V<sub>DD</sub> are not required.

Interrupt inputs have been implemented to offer an Interrupt capability (e.g., a downstream device sends request to the master to request a maintenance or a supervision operation). The interrupt inputs can also be used as regular GPI (General Purpose Inputs) since the information can then be read through the Interrupt register.

## **Command Sequencing**

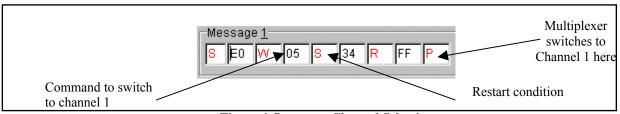

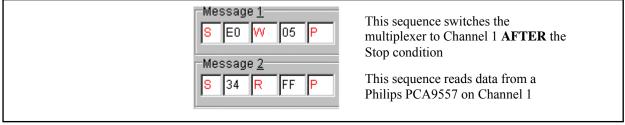

Although the PCA954X multiplexers and switches are very simple to use, it must be understood that a <u>STOP</u> <u>condition</u> must be generated before the channel is switched.

For example, the sequence shown in Figure 4 sends a command to the multiplexer to switch to channel 1, followed by a command to read the Philips PCA9557 (the S is a START or RESTART condition while the P is a STOP condition). Although this is a valid I<sup>2</sup>C sequence, it could give unexpected results if you are not aware that you are reading the Philips PCA9557 from the original channel, not channel 1 because the multiplexer will switch to channel 1 **ONLY** after the STOP condition has been sent.

**Figure 4. Incorrect Channel Selection**

In order to get read valid data from the Philips PCA9557 located on channel 1, the following message should be sent:

Figure 5. Correct Channel Selection

To ensure that a communication with the correct downstream channel is initiated, the address information must be sent first, followed by the desired channel (in this case channel 1), and then followed by a Stop command, as shown in Figure 5. Now all I<sup>2</sup>C messages are being transmitted through the correct channel.

Note that once the master controller has configured the PCA954X, the device behaves like a wire (transparent switch behavior) and will keep the programmed configuration until the master controller addresses it again in order to change the configuration. Each I<sup>2</sup>C message addressed to another device connected to a downstream channel will pass through the PCA954X device and there is no need to access and configure the PCA954X device again.

## Power up / Reset default state

All the devices power up with no downstream channel selected, except for the PCA9541/01, PCA9541/02 and PCA9547, which powers up with Channel 0 selected.

A reset performed on the PCA9543A, PCA9545A, PCA9546A, PCA9548A and PCA9549 cause all the downstream channels to be unselected (open).

A reset performed on the PCA9541/01, PCA9541/02 and PCA9547 causes Channel 0 to be selected.

## Voltage Clamping

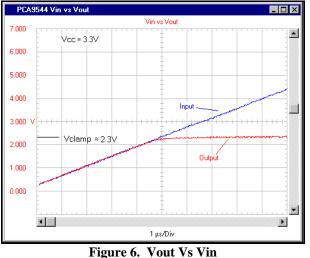

The PCA954X Multiplexers and Switches contain pass transistor, which are very fast and have very low on-resistance. When the pass transistor is enabled and the input voltage is low, the output is also low and the pass transistor has a typical on-resistance around 25  $\Omega$ . As the input voltage rises, the output voltage should track the input voltage closely until it reaches a value approximately 1V below V<sub>DD</sub>. At this voltage, the output is clamped (V<sub>clamp</sub>). This phenomenon

can be seen in Figure 6 below. The clamping voltage will be somewhat lowered by a load on the output (shown with open output).

#### Voltage Translation

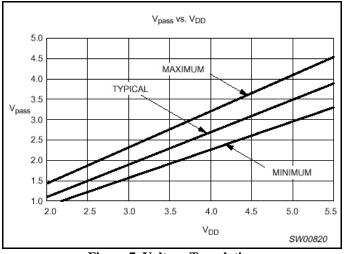

The voltage clamping can be advantageous when there is a need to communicate between two I<sup>2</sup>C voltage levels. The PCA954X will clamp the voltage to a value below its  $V_{DD}$ . Then pull-up resistors can be used to pull-up the output voltage of each individual branch to a suitable range. This can be seen in Figure 7.

Figure 7. Voltage Translation

The graph shows that the  $I^2C$  voltage can be translated between the various channels of the PCA954X device. For example, if the upstream channel uses 5 V while the downstream channel uses 3.3 V. If the PCA954X is supplied with 3.3 V, it will clamp the voltage to about 2.3 V so the 5 V will not appear on the 3.3 V side. A pull-up resistor on the 3.3 V side then pulls it all the way up to the 3.3 V rail. In most situations, a design engineer should use the maximum voltage curve since this is the situation you would find over the entire temperature range. The important thing to note is that the multiplexers/switches should be supplied with the lowest  $I^2C$  voltage needed to ensure proper voltage translation.

#### How to use the PCA9541 as a 2-channel multiplexer

Figure 8. Two-channel multiplexer using a PCA9541

In this application, a PCA9541/01, which defaults with SDA/SCL\_MASTER0 enabled (upstream channel 0 connected to downstream channel), is used in a configuration where its 2 upstream  $I^2C$  channels (SDA/SCL\_MST0 and SDA/SCL\_MST1) contain the 2 slave devices and it downstream channel (SDA/SCL\_SLAVE) contains the master device.

- At power up, PCA9541/01 is configured with SDA/SCL\_MASTER0 connected with the downstream slave channel. The master located in the slave side can then directly access Slave 1 device.

- When the master wants to communicate with Slave 2 device, it has to configure PCA9541/01 through its Control register to enable SDA/SCL\_MASTER1.

- From there, if the Master wants to communicate again with Slave 1 device, it can access SDA/SCL\_MASTER by 2 different methods:

- 1. Generate a /RESET strobe causing the PCA9541/01 to go to its default state (SDA/SCL\_MASTER0 enabled)

- 2. Write to the Control Register in order to "give up" the control of SDA/SCL\_MASTER1 and enable SDA/SCL\_MASTER0.

#### **Determining Pull-Up Resistors values**

The PCA954X devices provide excellent isolation between the channels but do not provide any additional drive capability between the upstream and downstream buses. Therefore, both the upstream and downstream loads (i.e., bus capacitance and device input loads) must be taken into consideration when choosing the value of a pull-up resistor.

Note that the PCA954X supply should normally be connected to the lowest bus voltage to ensure proper voltage clamping.

• <u>Example 1: Typical application using a multiplexer. Pull-up resistors calculations</u>

Here is an application example to illustrate this point:

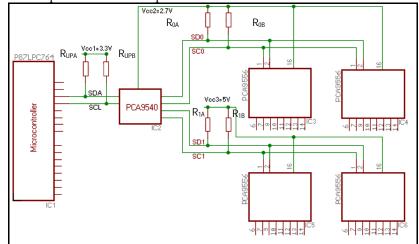

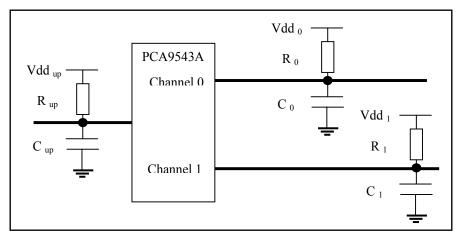

Figure 9. Typical Circuit Example

Assumptions are explained in Table 8.

|                  | Supply Voltage | Load capacitance                |

|------------------|----------------|---------------------------------|

| Upstream channel | 3.3 V          | $C_{upstream} = 100 \text{ pF}$ |

| Channel 0        | 2.5 V          | $C_{channel0} = 300 \text{ pF}$ |

| Channel 1        | 5.0 V          | $C_{channel1} = 200 \text{ pF}$ |

|                  |                |                                 |

| Table 8. | Electrical | parameters |

|----------|------------|------------|

|----------|------------|------------|

Note: Load capacitance includes device input capacitance and board capacitance.

The main considerations in choosing the pull-up resistor are:

1. Ensuring that the current does not exceed the maximum  $I_{ol} = 3$  mA at 0.4 V. This determines the minimum resistor value.

Ensuring that the rise time does not exceed 1.0 µs for a standard mode (100 kHz) bus or 300 ns for the high-speed mode (400 kHz) (affected by the bus capacitance and pull-up resistor). This determines the maximum resistor value.

When the input voltage to the multiplexer is low, the resistance of the switch is assumed to be negligible in comparison to the pull-up resistors.

For this example of devices operating in the standard mode (100 kHz), the current consumption is not very important, so the maximum 3 mA current is allowed to flow when SDA and SCL are low.

$I_{UPA}$  is the current through  $R_{UPA}$ .

$I_{0A}$  is the current through  $R_{0A}$ .

$I_{1A}$  is the current through  $R_{1A}$ , etc.

If the voltage across the open-drain FETs is assumed to be zero, then the following equation is used to calculate the pull-up resistors:

Since the capacitance of the upstream branch is  $\frac{1}{4}$  of the total capacitance of the SCL + SC0 branch, set  $I_{UP} = 3 \text{ mA} / 4 = 0.75 \text{ mA}$ . Therefore, the pull-up resistor in the upstream channel can have a current of  $I_{UP} = 0.75 \text{ mA}$  and pull-up in the downstream channels can be set to  $I_0 = I_1 = 2.25 \text{ mA}$ .

$\begin{array}{l} R_{UPA} = R_{UPB} &= 3.3 \ V \ / \ 0.75 \ mA = 4.4 \ k\Omega \\ R_{0A} = R_{0B} &= 2.5 \ V \ / \ 2.25 \ mA = 1.11 \ k\Omega \\ R_{1A} = R_{1B} &= 5.0 \ V \ / \ 2.25 \ mA = 2.2 \ k\Omega \end{array}$

Additional verification:

Ensure the rise time specification of 1  $\mu$ s for standard mode I<sup>2</sup>C is not exceeded. Consider the V<sub>DD</sub>-related input threshold of V<sub>IH</sub> = 0.7 x V<sub>DD</sub> and V<sub>IL</sub> = 0.3 x V<sub>DD</sub> for the purposes of RC time constant calculation.

$V(t) = V_{DD} (1-1/e^{-t/RC})$  where t is the time since the charging started and RC is the time constant.  $V(t1) = 0.3 \text{ x } V_{DD} = V_{DD} (1-1/e^{t \ 1/RC})$ ; then t1 = 0.3566749 x RC  $V(t2) = 0.7 \text{ x } V_{DD} = V_{DD} (1-1/e^{t \ 2/RC})$ ; then t2 = 1.2039729 x RC $T_{rise} = t2 - t1 = 0.8472979 \text{ x } RC$

Scenario 1: No downstream channel enabled

$T_{rise} = 0.8472979 \text{ x } R_{UPA}C_{upstream}$ = 0.8472979 x 4400 x 100e-12 = 0.37  $\mu$ s

Scenario 2: Channel 0 enabled

$T_{\text{rise}} = 0.8472979 \text{ x } (R_{\text{UPA}} / / R_{0\text{A}}) (C_{\text{upstream}} / / C_{\text{channel0}})$ = 0.8472979 x  $\frac{4400 \text{ x } 1110}{4400 + 1110} \text{ x } (100 \text{ e-}12 + 300 \text{ e-}12)$ = 0.30 µs Scenario 3: Channel 1 enabled  $T_{rise} = 0.8472979 \text{ x} (R_{UPA} // R_{1A}) (C_{upstream} // C_{channel1})$  $= 0.8472979 \text{ x } \frac{4400 \text{ x} 2200}{4400 \text{ x} 2200} \text{ x } (100 \text{ e}-12 + 200 \text{ e}-12)$ 4400+2200  $= 0.37 \, \mu s$

All rise times are well below the maximum rise time of 1 µs.

Example 2: Equivalent resistance and capacitance values for multiple channel devices

The example in Figure 10 is made with the PCA9543A, 2-channel switch. It can easily be extended to the 4 and 8channel devices.

**Figure 10. Multiple Channel Example**

- $R_{up}$ ,  $R_0$  and  $R_1$ : pull-up resistors on respectively the upstream channel, downstream channel 0 and downstream channel 1.

- Cup, Co and C1: equivalent capacitance on respectively the upstream channel, downstream channel 0 and downstream channel 1.

- The upstream channel is the main I<sup>2</sup>C-bus and can be connected to no downstream channels, to channel 0, channel 1 or both channel 1 and 2 at the same time.

- 1. No channel selected:

| - Equivalent resistance of the I <sup>2</sup> C-bus  | $= R_{up}$ |

|------------------------------------------------------|------------|

| - Equivalent capacitance of the I <sup>2</sup> C-bus | $= C_{up}$ |

- Equivalent capacitance of the I<sup>2</sup>C-bus

- 2. Upstream channel connected to downstream channel 0:

- Equivalent resistance of the I<sup>2</sup>C-bus  $= \frac{R_{up}}{R_{up}} \frac{R_{up} \times R_0}{R_{up}} (R_{up} + R_0)$ =  $\frac{C_{up}}{R_{up}} C_0 = C_{up} + C_0$ - Equivalent capacitance of the I<sup>2</sup>C-bus

- 3. Upstream channel connected to downstream channel 1:

| - Equivalent resistance of the I <sup>2</sup> C-bus  | $= R_{up} // R_1 = (R_{up} \times R_1) / (R_{up} + R_1)$ |

|------------------------------------------------------|----------------------------------------------------------|

| - Equivalent capacitance of the I <sup>2</sup> C-bus | $= C_{up} // C_1 = C_{up} + C_1$                         |

- 4. Upstream channel connected to downstream channel 0 and downstream channel 1: - Equivalent resistance of the I<sup>2</sup>C-bus  $= R_{up} / / R_1 / / R_2 = 1 / (1 / R_{up} + 1 / R_1 + 1 / R_2)$  $= C_{up} // C_0 // C_1 = C_{up} + C_0 + C_1$ - Equivalent capacitance of the I<sup>2</sup>C-bus

- 5. For applications using more than 2 channels: - Equivalent resistance of the I<sup>2</sup>C-bus = Upstream pull-up resistors and all the connected downstream channel pull-up resistors in parallel - Equivalent capacitance of the I<sup>2</sup>C-bus = Upstream equivalent capacitance and all the connected downstream channel equivalent capacitance in parallel

• Quick overview: Maximum and minimum pull-up resistors values

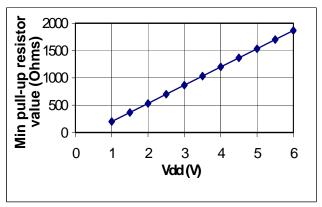

The supply voltage limits the **minimum** value of the pull-up resistor due to a minimum sink current value of 3 mA at  $V_{OL}max = 0.4$  V (see Figure 11).

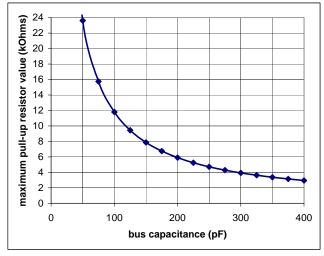

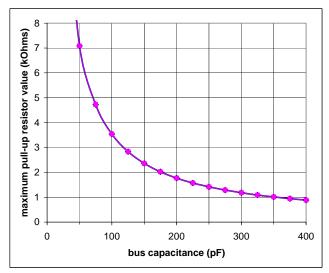

The bus capacitance is the total capacitance of wire, connections and pins. This capacitance limits the **maximum** value of the pull-up resistors due to the specified rise time (see Figure 12 and Figure 13).