# Application Note MCF5272 Interrupt Service Routine for the Physical Layer Interface Controller

Jean Louis Dolmeta Networking and Computing Systems Group

# Part I Summary and Scope

#### 1.1 Overview

The physical layer interface controller (PLIC) is a peripheral module of the ColdFire<sup>®</sup> MCF5272 intended to support ISDN applications such as CODECs, ISDN transceivers, and other peripherals. The PLIC supports two modes of operation: IDL and GCI physical layer protocols. It also has four dedicated TDM ports for connecting to external devices.

This document consists of four main parts:

- 1. A brief description of the inter digital link (IDL) mode of operation

- 2. The general circuit interface (GCI) explanation

- 3. A description of the interrupt service routine used to handle the data transfer for both modes of operation

- 4. Some examples of ColdFire microprocessor assembly code to perform quick evaluation of the MCF5272. See Part VIII, "Appendix A."

The reader is strongly recommended to read the MCF5272 User's Manual at www.mot.com/ColdFire before going through this document. The register and bit explanations therein help the reader to better understand the device's internal architecture.

© Freescale Semiconductor, Inc., 2004. All rights reserved.

**Summary and Scope Contents**

# 1.2 Contents

| Paragraph Number | Title                                       | Page |

|------------------|---------------------------------------------|------|

| II               | Inter Digital Link Mode of Operation        | 1    |

| 2.1              | Introduction                                | 1    |

| III              | General Circuit Interface Mode of Operation | 2    |

| 3.1              | GCI History                                 | 2    |

| 3.2              | Monitor Channel Operation                   | 3    |

| 3.3              | Command Indicate Operation                  | 4    |

| IV               | GCI/IDL to the MCF5272                      | 4    |

| 4.1              | Data Registers                              | 5    |

| 4.2              | Monitor Channel Registers                   | 5    |

| 4.2.1            | Monitor Channel Receive                     | 5    |

| 4.2.2            | Monitor Channel Transmit                    | 5    |

| 4.3              | Command Indicate Registers                  | 6    |

| 4.3.1            | Command Indicate Receive                    | 6    |

| 4.3.2            | Command Indicate Transmit                   | 6    |

| V                | Periodic Interrupt Process                  | 7    |

| 5.1              | Bubbles Definitions                         | 7    |

| 5.2              | One-Port Processing                         | 8    |

| 5.3              | Multi-Ports Processing                      | 11   |

| VI               | Aperiodic Interrupt Process                 | 12   |

| 6.1              | Aperiodic One-Port Sequence                 | 12   |

| 6.2              | Multi-Ports Case                            | 13   |

| 6.3              | Brief Register Explanation                  | 14   |

| 6.4              | Monitor Channel Sequence                    | 15   |

| 6.4.1            | Transmit Sequence                           | 15   |

| 6.4.2            | Receive Sequence                            | 16   |

| 6.5              | Transmit Abort Condition                    | 17   |

| 6.6              | Command Indicate Channel                    | 17   |

| 6.6.1            | Transmit Sequence                           | 17   |

| 6.6.2            | Receive Sequence                            | 18   |

|                  |                                             |      |

#### **Summary and Scope Contents**

| VII   | Assembly Code                                | 19 |

|-------|----------------------------------------------|----|

| 7.1   | Interrupt Controller                         | 19 |

| 7.2   | Interrupt Vector Generation                  | 20 |

| 7.3   | Prioritization Level: ICR2 Register          | 21 |

| 7.4   | Programmable Interrupt Vector Register: PIVR | 22 |

| 7.5   | MBAR Configuration                           | 22 |

| 7.6   | Hardware Configuration                       | 22 |

| 7.7   | Software Configuration                       | 23 |

| 7.7.1 | Customer Premises Equipment Software         | 23 |

| 7.7.2 | ColdFire Port Configuration                  | 23 |

| 7.7.3 | Debugger Configuration                       | 25 |

| VIII  | Appendix A                                   | 26 |

|       |                                              |    |

#### FIGURES and TABLES

| Item      | Title                                                                | Page |

|-----------|----------------------------------------------------------------------|------|

| Figure 1  | IDL 10-Bit Mode                                                      | 4    |

| Figure 2  | IDL 8-Bit Mode                                                       | 5    |

| Figure 3  | GCI Frame                                                            | 6    |

| Figure 4  | Monitor Channel Protocol                                             | 6    |

| Figure 5  | GCI Monitor Channel Receive Register                                 | 7    |

| Figure 6  | GCI Monitor Channel Transmit Register                                | 8    |

| Figure 7  | PnGCIR Register                                                      | 9    |

| Figure 8  | PnGCIT Register                                                      | 10   |

| Figure    | One-Port Processing Interrupt Service Routine Flow Diagram           | 13   |

| Figure 10 | Multi-Port Processing Interrupt Service Routine Flow Diagram         | 14   |

| Figure 11 | One-Port Processing Aperiodic Interrupt Service Routine Flow Diagram | 15   |

| Figure 12 | Multi-Processing Aperiodic Interrupt Service Routine Flow Diagram    | 16   |

| Figure 13 | Monitor Channel Transmit Sequence Flow Diagram                       | 17   |

| Figure 14 | Monitor Channel Receive Sequence Flow Diagram                        | 18   |

| Figure 15 | Transmit Abort Condition Flow Diagram                                | 19   |

| Figure 16 | CI Transmit Sequence Flow Diagram                                    | 20   |

| Figure 17 | CI Receive Sequence Flow Diagram                                     | 21   |

| Figure 18 | Interrupt Control Register 2                                         | 23   |

#### Interchip Digital Link Mode of Operation Introduction

| Figure 19 | Programmable Interrupt Vector Register | 24 |

|-----------|----------------------------------------|----|

| Figure 20 | Hardware Configuration                 | 25 |

| Table 1   | PnGMR Register Field Descriptions      | 8  |

| Table 2   | PnGMT Register Field Descriptions      | 8  |

| Table 3   | PnGCIR Register Field Descriptions     | 9  |

| Table 4   | PnGCIT Register Field Descriptions     | 10 |

| Table 5   | PIV Register Field Descriptions        | 24 |

| Table 6   | Port Pins Assignment                   | 25 |

| Table 7   | Port Control Register Values           | 26 |

# Part II Interchip Digital Link Mode of Operation

#### 2.1 Introduction

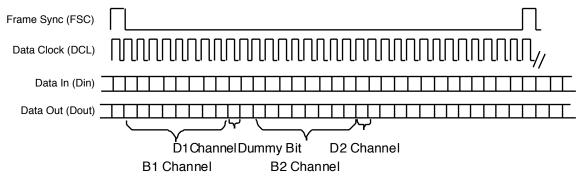

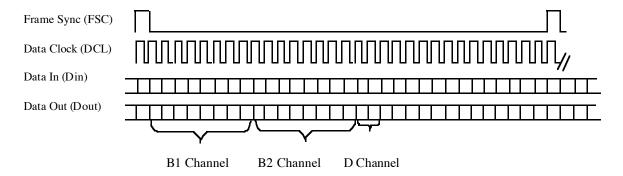

The IDL mode of operation is a four-wire interface used for full-duplex communication between ICs at the board level. This interface consists of a transmit path, a receive path, an associated clock, and a synchronization signal. These signals are known as Dout, Din, DCL, and FSC. The clock determines the rate of exchange of data in both transmit and receive directions and the sync controls when this exchange is to take place. Three channels of data are exchanged every 125 microseconds. These channels consist of two 64-kbps B channels and one 16-kbps D channel used for full-duplex communication. The waveform diagrams are shown in Figure 1 and Figure 2.

Two modes are available:

• The 10-bit mode:

Figure 1. IDL 10-bit Mode

**General Circuit Interface Mode of Operation GCI History**

• The 8-bit mode:

Figure 2. IDL 8-bit Mode

For more information about the different configurations of IDL, please refer to any ISDN product user's manual, such as the MC145574/572 or MC145576 at http://www.freescale.com.

# Part III General Circuit Interface Mode of Operation

# 3.1 GCI History

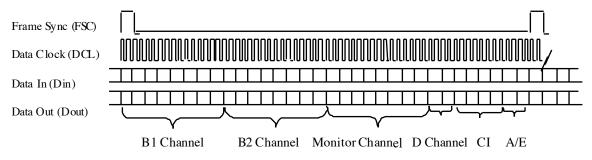

The GCI mode was defined by European companies (Italtel, Siemens, Alcatel, and GPT). GCI is a time division multiplex (TDM) bus that combines the ISDN 2B+D data, control, and status information onto four signal pins. Some benefits of the GCI include the following:

- Operation and maintenance features

- Activation and deactivation facilities (via CI channel)

- Well-defined transmission protocols to ensure correct information transfer between GCI-compatible devices

- Point-to-point and multi-point communication links

- Multiplexed mode of operation where up to eight GCI channels can be combined to form a single data stream

Those four signals consist of the following:

- FSC, frame synchronization: 8-kHz frame pulse

- DCL, data, clock signal: two clocks per data bit

- Din, data in: the data in

- Dout, data out: This pin is an open-drain output and must be pulled to Vdd through a 1.2-k $\Omega$  resistor.

The GCI frame structure has the following format: two B channels, a monitor channel, the ISDN D channel, the command/indicate channel, and the A and E bits. The frame is shown in Figure 3.

General Circuit Interface Mode of Operation Monitor Channel Operation

Figure 3. GCI Frame

# 3.2 Monitor Channel Operation

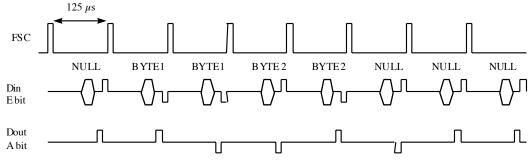

This feature is available only in GCI mode. The monitor channel is used to access the internal registers of any GCI device in order to support maintenance channel operations. All monitor channel messages are two bytes in length. Each byte is sent twice to permit the receiving GCI device to verify data integrity. In ISDN applications, the monitor channel is used for access to the maintenance messages. The A and E bits in the GCI channel are used to control and acknowledge monitor channel transfers between the MCF5272 and another GCI device.

Figure 4 shows the monitor channel protocol used. When the monitor channel is inactive, the A and E bits are both high. The A and E bits are active when they are driven low during their respective bit times. (Note that pull-up resistors are required on Din and Dout.) The E bit represents the transmission of a new monitor channel byte. The A bit from the opposite direction is used to acknowledge the monitor channel byte transfer. An idle monitor channel is indicated by both A and E bits being inactive for two GCI frames. The monitor channel data is 0xFF when inactive. The originating GCI device transmits a byte onto the monitor channel after receiving the A and E bits equal to 1 for at least two consecutive GCI frames. The originating GCI device also clears its outgoing E bit in the same GCI frame as the byte that is transmitted. The transmitted byte is repeated for at least two GCI frames, or is repeated in subsequent GCI frames, until the MCF5272 acknowledges receiving two consecutive GCI frames containing the same monitor byte.

Once the MCF5272 acknowledges the first byte, the sending device sets E high and transmits the first frame of the second byte. Then, the second byte is repeated with the E bit low until it is acknowledged. The destination GCI device verifies that it has received the first byte by clearing the A bit towards the originating GCI device for at least two GCI frames. Successive bytes are acknowledged by the receiving device setting A high on the first instance of the next byte, followed by A being cleared when the second instance of the byte is received. If the receiving GCI device does not receive the same monitor channel byte in two consecutive GCI frames, it indicates this by leaving A = 0 until two consecutive identical bytes are received. The last byte of the sequence is indicated by the originating GCI device when it sets its E bit for two successive GCI frames. The procedure is summarized in Figure 4.

**Figure 4. Monitor Channel Protocol**

GCI/IDL and the MCF5272 Command Indicate Operation

# 3.3 Command Indicate Operation

The command/indicate, or C/I channel, is used to activate and deactivate any GCI devices. Some control functions (such as loopbacks) are also supported over the C/I channel. C/I codes are four bits in length and must be received for two consecutive GCI frames before they are acted on. C/I channel bits are numbered bit 3 through 0, with bit 3 being the most significant. The C/I/ channel bits are transmitted starting with bit 3.

#### Part IV GCI/IDL and the MCF5272

This section gives a brief description of the internal registers in the PLIC.

# 4.1 Data Registers

For both GCI and IDL modes of operation, the maximum data rate transmitted for each digital port is 144 kbps (two 64-kbps B channels and one 16-kbps D channel). Frames of B1, B2, and D channels are packed together in PnRBx/PnTBx registers (with x = 1, 2, 3, 4) for receive and transmit direction respectively. Since the reception and transmission of information on the GCI/IDL interface is deterministic, a common interrupt is generated at 2 kHz. It is expected that a common interrupt service routine will be programmed to service the transmit and receive registers. After reset, the B and D channel shift registers and shadow registers are initialized to all 1's. For more information about the data registers, please refer to the  $MCF5272\ User's\ Manual$ .

# 4.2 Monitor Channel Registers

This section describes receive and transmit channels.

#### 4.2.1 Monitor Channel Receive

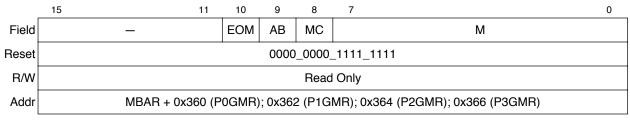

The PnGMR registers are 16-bit registers containing the received monitor channel bits for each of the four receive ports on the MCF5272. A byte of monitor channel data received on a certain port is put into an associated register using the format shown in Figure 5 and described in Table 1. A maskable interrupt is generated when a byte is written into any of the four available MCF5272 ports.

Figure 5. GCI Monitor Channel Receive Register (PnGMR)

GCI/IDL and the MCF5272 Monitor Channel Registers

**Table 1. PnGMR Register Field Descriptions**

| Bits  | Name | Description                                                                                                                                                                                                                                                                                                                                        |

|-------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15–11 | _    | Reserved, should be cleared.                                                                                                                                                                                                                                                                                                                       |

| 10    | EOM  | End of message.  0 Default at reset.  1 Indicates to the CPU that an end-of-message condition has been recognized on the E bit. EOM is automatically cleared when the PnGMR register has been read by the CPU.                                                                                                                                     |

| 9     | AB   | Abort.  0 Default at reset.  1 Indicates that the GCI controller has recognized an abort condition and is acknowledging the abort. It is automatically cleared by the CPU when the PnGMR register has been read.                                                                                                                                   |

| 8     | MC   | Monitor change.  0 Default at reset.  1 Indicates to the CPU that the monitor channel data byte written to the respective PnGMR register has changed and that the data is available for processing. This bit is automatically cleared by the CPU when the PnGMR register has been read. Clearing this bit also clears the aperiodic GMR interrupt. |

| 7–0   | М    | Monitor channel data byte. These bits are written by the monitor channel controller when valid monitor channel bytes are received.                                                                                                                                                                                                                 |

#### 4.2.2 Monitor Channel Transmit

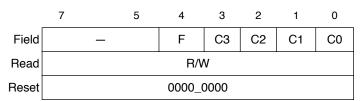

The PnGMT registers are 16-bit registers containing the control and monitor channel bits to be transmitted for each of the four ports on the MCF5272. A byte of monitor channel data to be transmitted on a certain port is put into an associated register using the format shown in Figure 6 and described in Table 2. A maskable interrupt is generated when this byte of data has been successfully transmitted.

| _     | 15                                                                |            | 10 | 9 | 8 | 7 |   | 0 |  |

|-------|-------------------------------------------------------------------|------------|----|---|---|---|---|---|--|

| Field |                                                                   | _          |    | L | R |   | М |   |  |

| Reset | 0000_0000_0000                                                    |            |    |   |   |   |   |   |  |

| R/W   |                                                                   | Read/Write |    |   |   |   |   |   |  |

| Addr  | MBAR + 0x368 (P0GMT); 0x36A (P1GMT); 0x36C (P2GMT); 0x36E (P3GMT) |            |    |   |   |   |   |   |  |

Figure 6. GCI Monitor Channel Transmit Register (PnGMT)

**Table 2. PnGMT Register Field Descriptions**

| Bits  | Name | Description                                                                                                                                                                                                                                                                                                             |

|-------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15–10 | _    | Reserved, should be cleared.                                                                                                                                                                                                                                                                                            |

| 9     | L    | Last.  0 Default reset value  1 Set by the CPU. Indicates to the monitor channel controller to transmit the end of message signal on the E bit. Both PnGMT[L] and PnGMT[R] must be set for the monitor channel controller to send the end of message signal.  The L bit is automatically cleared by the GCI controller. |

GCI/IDL and the MCF5272 Command Indicate Registers

**Table 2. PnGMT Register Field Descriptions**

| Bits | Name | Description                                                                                                                                                                                                                                                                               |

|------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8    | R    | Ready.  0 Default reset value.  1 Set by the CPU. Indicate to the monitor channel controller that a byte of data is ready for transmission. Automatically cleared by the GCI controller when it generates a transmit acknowledge (ACK bit in PnGMTS register) or when the L bit is reset. |

| 7–0  | М    | Monitor channel data byte. Written by the CPU when a byte is ready for transmission.                                                                                                                                                                                                      |

# 4.3 Command Indicate Registers

This section describes receive and transmit command registers.

#### 4.3.1 Command Indicate Receive

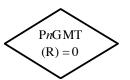

The PnGCIR register is an 8-bit register containing the received C/I bits for one of each of the four ports on the MCF5272. The register is shown in Figure 7 and described in Table 3.

Figure 7. PnGCIR Register

**Table 3. PnGCIR Register Field Descriptions**

| Bits | Name  | Description                                                                                                                                                                                                                                                                                                                     |

|------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7–5  | _     | Reserved, should be cleared.                                                                                                                                                                                                                                                                                                    |

| 4    | F     | Full. This bit is set by the C/I channel controller to indicate to the CPU that new C/I channel data has been received and is available for processing. It is automatically cleared by a CPU read. The clearing of this bit by reading this register also clears the aperiodic GCR interrupt.                                   |

| 3–0  | C3-C0 | C/I bits. These four bits are received on the GCI or SCIT channel 0. When a change in the C/I data value is received in two successive frames, it is interpreted as being valid and is passed on to the CPU via this register. A maskable interrupt is generated when data is written into any of the four available positions. |

#### 4.3.2 Command Indicate Transmit

The PnGCIT registers are 8-bit registers containing the monitor channel bits to be transmitted for each of the four ports on the MCF5272. The register is shown in Figure 8 and described in Table 4.

Periodic Interrupt Process ISR Bubble Definitions

|       | 7 |   | 5 | 4      | 3    | 2  | 1  | 0  |

|-------|---|---|---|--------|------|----|----|----|

| Field |   | _ |   | F      | СЗ   | C2 | C1 | C0 |

| Read  |   |   |   | R/V    | ٧    |    |    |    |

| Reset |   |   |   | 0000_0 | 0000 |    |    |    |

Figure 8. PnGCIT Register

**Table 4. PnGCIT Register Field Descriptions**

| Bits | Name  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7–5  | _     | Reserved, should be cleared.                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 4    | R     | Ready. This bit is set by the CPU to indicate to the C/I channel controller that data is ready for transmission. Setting this bit starts the C/I state machine, which responds with the transmit acknowledge (ACK bit in the PnGCITS register) once transmission of two successive C/I words is complete. This bit is automatically cleared by the GCI controller when it generates an ACK. The clearing of this bit by reading this register also clears the aperiodic GCT interrupt. |

| 3–0  | C3-C0 | C/I bits. The CPU writes C/I data to be transmitted, on the GCI or SCIT channel 0, into these positions. The CPU must ensure that this data is not overwritten before it has been transmitted the required minimum number of times, that is, before a change is detected and confirmed by a receiver. A maskable interrupt is generated when this data has been successfully transmitted.                                                                                              |

# **Part V Periodic Interrupt Process**

This document does not intend to define all the meanings of the PnPSR register. For more information, the user should read the MCF5272 User's Manual. This PnPSR register is involved in the data processing. All PnRBx and PnTBx registers, either in IDL or GCI modes of operation, will use these registers. There is no difference between those two modes as far as they are concerned. PnPSR register is updated every  $500\mu$ s. As long as the interrupt enable (IE) bits are set to invoke the interrupt service routine, the BxRDF bits will be set every  $500\mu$ s, and a register access will be achieved to clear this interrupt.

This section is explained in two parts:

- One port only is enabled: description of how to handle all the bits involved in PnPSR

- Multiple ports are enabled: description of how to access the ports that created this interrupt

#### 5.1 ISR Bubble Definitions

To assure that the following flow charts are well understood, this section defines the bubble shapes used in the illustrations:

• Start or End of the process

Test Condition

**Periodic Interrupt Process One-Port Processing**

• Interrupt creation

Return from Interrupt

Action taken

# 5.2 One-Port Processing

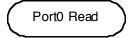

For this PLIC interrupt service routine, the channel priorities are fixed. In the periodic status registers, the B1RDF, B1TDE, and DRDF have top priority, then the B2RDF, B2TDE, and DTDE follow. The xTUE and xROE should be given lowest priority because they should be cleared. This interrupt service routine implementation gives some flexibility by dynamically jumping between the action to take and the verification of the bit that creates the interrupt. Furthermore, the purpose of the code was to first evaluate the product after first silicon. The code and the ISR have been written with this objective in mind. In conclusion, all the actions are taken inside the ISR instead of raising a flag in order to perform it once the ISR has completed. The flow chart is shown in Figure 9.

**Periodic Interrupt Process One-Port Processing**

Figure 9. One-Port Processing Interrupt Service Routine Flow Diagram

**Periodic Interrupt Process Multi-Ports Processing**

Figure 9. One-Port Processing Interrupt Service Routine Flow Diagram (Continued)

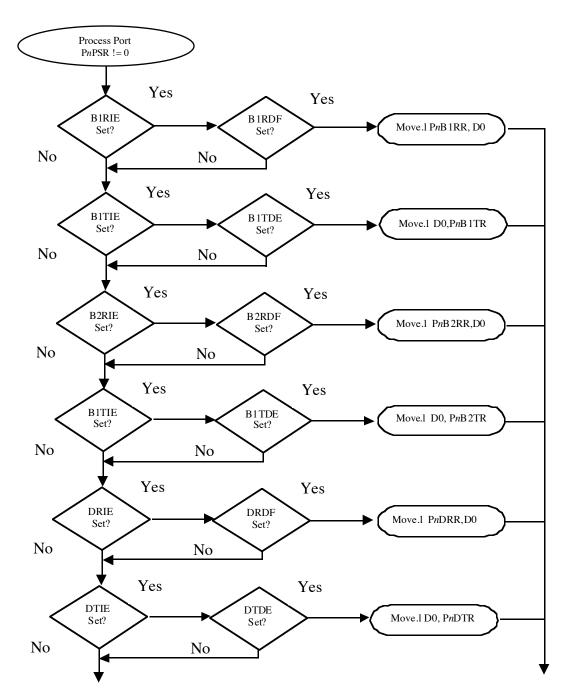

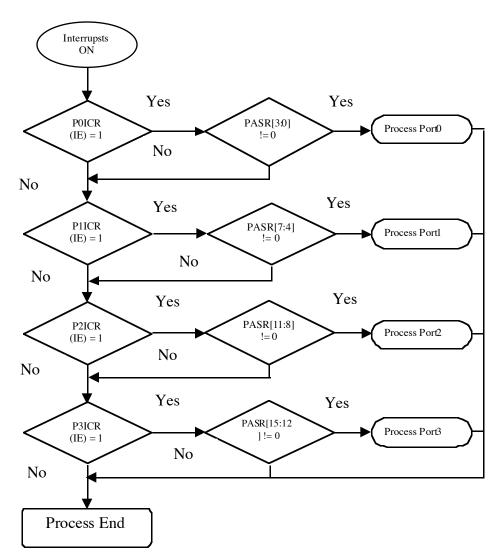

# 5.3 Multi-Ports Processing

Most of the time, more than one port will be enabled, and in order to make the ISR subroutine more efficient, several steps should be taken. When the periodic interrupt occurs, the user does not know yet which port has caused it. To find out, check the following registers:

**Aperiodic Interrupt Process Aperiodic One-Port Sequence**

- 1. PnICR: PLIC Interrupt Configuration register

- 2. PnPSR: PLIC Periodic Status Register

In fact, even if the PLPSR has been updated, the corresponding bit in the PnICR (IE) may not have been programmed; thus the ISR process cannot be called by this port. The flow chart is shown in Figure 10.

Figure 10. Multi-Port Processing Interrupt Service Routine Flow Diagram

# Part VI Aperiodic Interrupt Process

This part describes port sequence, multi-port case, registers, channel sequence, abort condition, and the command indicate channel.

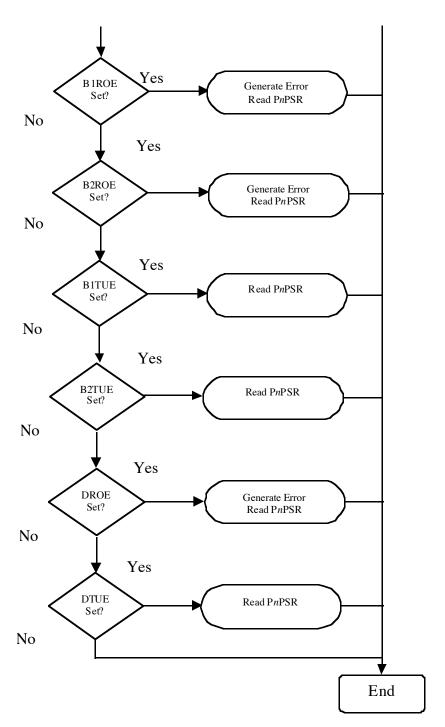

# 6.1 Aperiodic One-Port Sequence

This section explains how the aperiodic interrupt is used with one port enabled. The next section describes a multi-channel approach. When one port is enabled, a level of priority must be set up. For obvious reasons, the CI channel will be top priority because of its ability to activate and deactivate. As far the

**Aperiodic Interrupt Process Multi-Port Case**

monitor channel is concerned, the same philosophy will be applied, and the received path takes higher priority. The flow chart is shown in Figure 11.

Figure 11. One-Port Processing Aperiodic Interrupt Service Routine Flow Diagram

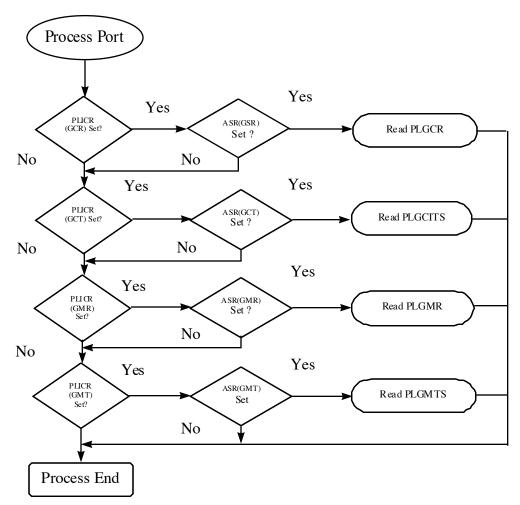

# 6.2 Multi-Port Case

Once the PLIC has many GCI ports enabled, a generic aperiodic interrupt is required to handle all of the possibilities. As previously done in the periodic interrupt, the PnICR will be read so it can save some MIPS in case the port is not enabled. The flow chart is shown in Figure 12.

Aperiodic Interrupt Process Brief Register Explanation

Figure 12. Multi-Processing Aperiodic Interrupt Service Routine Flow Diagram

# 6.3 Brief Register Explanation

This section describes the registers involved in the aperiodic interrupts service routine. The GCI oriented registers are PnGMR, PnGMT, PnGCIR, and PnGCIT. These are the only register that affect the PASR register. For more information about the definition of all those registers, please refer to the PLIC section in the MCF5272 User's Manual for a more detailed description.

# 6.4 Monitor Channel Sequence

This section details the manner in which GCI monitor channel data is handled. Based on the low-level protocol specification, the following information will help the user better understand the GCI monitor channel operation.

**Aperiodic Interrupt Process Monitor Channel Sequence**

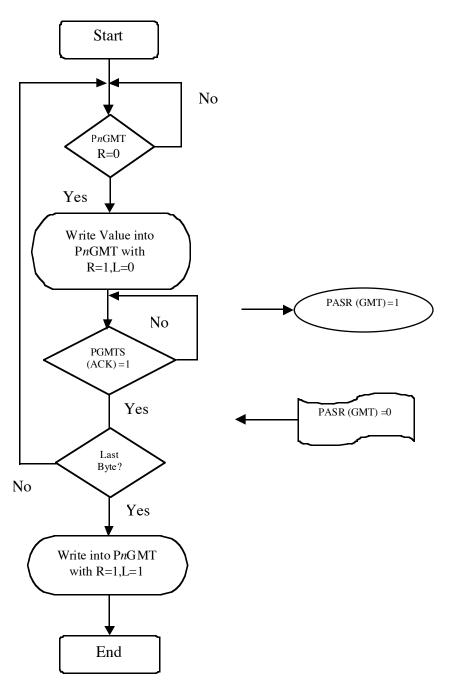

# 6.4.1 Transmit Sequence

Here is the transmit sequence of the GCI protocol using the GCI monitor channel transmit registers. The flow chart is shown in Figure 13.

Figure 13. Monitor Channel Transmit Sequence Flow Diagram

**Aperiodic Interrupt Process Monitor Channel Sequence**

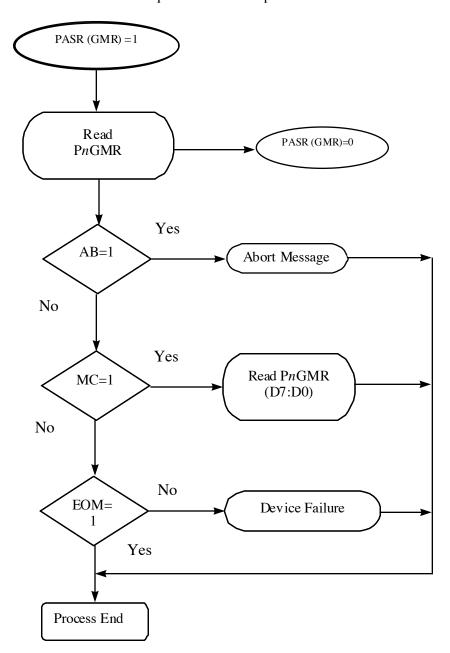

# 6.4.2 Receive Sequence

This section describes with the receive sequence of the GCI protocol. The flow chart is shown in Figure 14.

Figure 14. Monitor Channel Receive Sequence Flow Diagram

**Aperiodic Interrupt Process Transmit Abort Condition**

# 6.5 Transmit Abort Condition

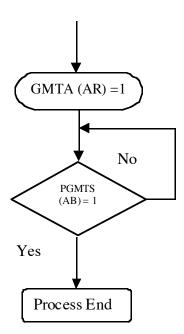

One register is used to indicate an abort condition. The flow chart is shown in Figure 15.

Figure 15. Transmit Abort Condition Flow Diagram

**Aperiodic Interrupt Process Command Indicate Channel**

# 6.6 Command Indicate Channel

This section details the channel for command indication.

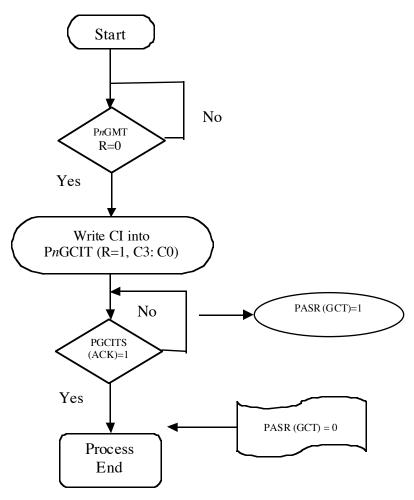

# 6.6.1 Transmit Sequence

Figure 16 explains CI channel operation.

Figure 16. CI Transmit Sequence Flow Diagram

**Assembly Code Interrupt Controller**

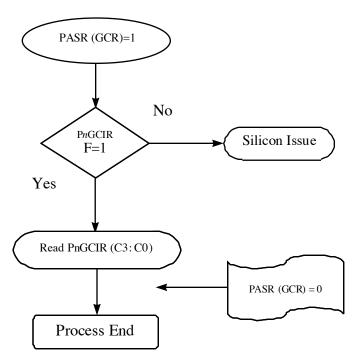

#### 6.6.2 Receive Sequence

The flow chart for the receive sequence is shown in Figure 17.

Figure 17. CI Receive Sequence Flow Diagram

# **Part VII Assembly Code**

This section outlines how the ColdFire core will handle the PLIC. Some assembly code will be shown to better describe the sequence flow of the interrupt service routine. An interrupt occurs every 500 microseconds; therefore, all the actions must be performed within this time.

# 7.1 Interrupt Controller

The MCF5272 microprocessor device has some registers that set the interrupt prioritization levels for each interrupt source.

The on-chip system integration module contains an interrupt controller that is capable of providing up to 32 interrupt sources.

These sources include the following:

- External interrupt signals INT[6:1]

- Software watchdog timer

- Four general-purpose timers

- Two USARTs

- Ethernet controller

- PLIC controller

- DMA controller

- QSPI

- USB module

#### **Assembly Code Interrupt Vector Generation**

All external interrupt inputs are edge-sensitive where the active edge is programmable. The active edge is programmable. An interrupt request must be held valid for at least three consecutive CPU clock cycles to be considered a valid input. Each interrupt input can have its priority programmed by programming the xIPL(2-0) bits in the interrupt control registers. When the ColdFire core responds to a request with an interrupt acknowledge cycle, as is standard in MC52xx implementations, the interrupt controller logic will forward the correct vector depending on the original source of the interrupt. Software can clear pending interrupts from any source via the registers in the interrupt controller logic, and can program the location of the block of vectors used for interrupt sources via the programmable interrupt vector register. For an interrupt to be successfully processed, RAM must be available for the stack, and often this RAM will be selected by one of the programmable chip selects. So upon system startup there is a brief period where RAM is not available for the stack. To ensure no problems resulting from interrupts (particularly of priority level 7) during this period, there is an interlock which prevents any interrupt from reaching the ColdFire core until the first write cycle to the programmable interrupt vector register (PIVR). The user should ensure that both RAM chip selects and the system stack are set up prior to this write operation.

The interrupt controller includes daisy-chaining functions in order to avoid contention when the ColdFire core issues an interrupt acknowledge cycle. So if more than one interrupt source has the same interrupt priority level (IPL), they are daisy chained with INT1 being the highest priority. There are four interrupt control registers which control the interrupt priorities for the external general purpose latched interrupt input signals and the internal I/O modules' signals. These registers allow software to reset any pending interrupts from these external interrupt lines or internal modules. There are up to 32 interrupt inputs, each of which has four bits assigned to it in these registers. The registers can be read or written at any time. When read, the data returned is the last value that was written to the register, with the exception of the reset bits, which are transitory functions. The registers can be accessed by either long word (32-bit), word (16-bit), or byte (8-bit) data transfer instructions. An 8-bit write to one-half of a register will leave the other half intact.

# 7.2 Interrupt Vector Generation

Pending interrupts are presented to the MCF52xx core in order of priority. The core responds to an interrupt request by initiating an interrupt acknowledge cycle to receive a vector number, which allows the core to locate the interrupt's service routine. The interrupt controller is able to identify the source of the interrupt, which is being acknowledged and indicates this to the interrupt module mapper. The mapper determines which slave bus module is to provide the interrupt vector for the identified interrupt source. In most instances it is the interrupt controller itself which will provide the interrupt vector in which case the following procedure is used. The three most significant bits of the interrupt vector are programmed by the user in the programmable interrupt vector register.

# 7.3 Prioritization Level: ICR2 Register

The interrupt control registers (ICRx) allow the user to define which interrupt priority level (IPL), each of these peripheral sources will use. For those modules whose interrupt sources are mapped to the interrupt controller for the vector source, the programmable interrupt vector register (PIVR) allows the user to define a particular vector number to be presented when the respective module receives an interrupt acknowledge from the MCF52xx core via the interrupt controller logic. The interrupt vector register is initialized upon system reset with the uninitialized interrupt vector (hexadecimal 0x0F), and must be programmed with the required vector number for normal operation. It is important not to use reserved interrupt vector locations for this purpose. The dedicated ICRx for the periodic and aperiodic interrupts is ICR2.

**Assembly Code Programmable Interrupt Vector Register: PIVR**

|       |           |          |           |          |            |             | ME        | BASE +0x24 |  |  |

|-------|-----------|----------|-----------|----------|------------|-------------|-----------|------------|--|--|

|       | 31        | 30       | 29        | 28       | 27         | 26          | 25        | 24         |  |  |

| Write | UART1PIR  | UART1PL2 | UART1/PL1 | UART1/PL | 0 UART2PII | R UART2/PL2 | UART2/PL1 | UART2PL0   |  |  |

| Read  | UART1     | UART1PL2 | UART1/PL1 | UART1/PL | 0 UART2    | UART2/PL2   | UART2/PL1 | UART2PL0   |  |  |

| Reset | 0000_0000 |          |           |          |            |             |           |            |  |  |

| '     |           |          |           |          |            |             |           |            |  |  |

|       | 23        | 22       | 21        | 20       | 19         | 18          | 17        | 16         |  |  |

| Writ  | e PLIPIR  | PLIIPL2  | PLIIPL1   | PLIPL0   | PLIAPIR    | PLIAIPL2    | PLIAIPL1  | PLIAIPL0   |  |  |

| Rea   | d PLIP    | PLIIPL2  | PLIIPL1   | PLIPL0   | PLIA       | PLIAIPL2    | PLIAIPL1  | PLIAIPL0   |  |  |

| Rese  | 0000_0000 |          |           |          |            |             |           |            |  |  |

|       |           |          |           |          |            |             |           |            |  |  |

| _     | 15        | 14       | 13        | 12       | 11         | 10          | 9         | 8          |  |  |

| Write | USB0PIR   | USB0IPL2 | ISB0IPL1  | USB0IPL0 | USB1PIR    | USB1IPL2    | USB1IPL1  | USB0IPL0   |  |  |

| Read  | USB0      | USB0IPL2 | ISB0IPL1  | USB0IPL0 | USB1       | USB1IPL2    | USB1IPL1  | USB0IPL0   |  |  |

| Reset |           |          |           | 000      | 0_0000     |             |           |            |  |  |

|       |           |          |           |          |            |             |           |            |  |  |

|       | 7         | 6        | 5         | 4        | 3          | 2           | . 1       | 0          |  |  |

| Write | USB2PIR   | USB2IPL2 | USB2IPL1  | USB2IPL  | 0 USB3PIF  | USB3IPL2    | USB2IPL1  | USB2IPL0   |  |  |

| Read  | ISB2      | USB2IPL2 | USB2IPL1  | USB2IPL  | 0 USB3     | USB3IPL2    | USB2IPL1  | USB2IPL0   |  |  |

| Reset |           |          | ·         | 000      | 0_000      |             | ·         |            |  |  |

Figure 18. Interrupt Controller Register 2

For more explanation about the meaning of those bits, the user should read the *MCF5272 User's Manual*. Here is a brief summary ICRx bits:

*x*PIR: When set to one, the new IPL value is stored. When set to zero, the corresponding INTx interrupt latch and IPL level is unaffected. Any pending interrupt on that line will remain pending.

xIPL(2:0): Interrupt Priority Level (1-7): When set to zero, the corresponding INTx interrupt line is inhibited and will not generate interrupts. Its state can still be read via the ISR1 register. Otherwise, the corresponding INT1x interrupt line is enabled, and will generate an interrupt to the MCF52xx core with the indicated priority level.

For more explanation about the meaning of these bits, see the MCF5272 User's Manual.

# 7.4 Programmable Interrupt Vector Register: PIVR

This register specifies the vector numbers which will be returned by the interrupt controller in response to interrupt acknowledge cycles for the various peripherals and discrete interrupt sources. The high three bits of the vector number are programmed in the PIVR. The low five bits are provided by the interrupt controller depending on the highest priority source which is currently active for the specific interrupt priority level (IPL) being responded to in the current acknowledge cycle.

Assembly Code MBAR Configuration

|       |     |     |     |       |      | ı      | MBASE | +0x3C |

|-------|-----|-----|-----|-------|------|--------|-------|-------|

|       | 7   | 6   | 5   | 4     | 3    | 2      | 1     | 0     |

| Write | IV7 | IV6 | IV5 |       |      | _      |       |       |

| Read  | IV7 | IV6 | IV5 |       | (    | )_1111 |       |       |

| Reset |     |     |     | 0000_ | 1111 |        |       |       |

Figure 19. Programmable Interrupt Vector Register

**Table 5. PIV Register Field Descriptions**

| Bits | Name | Description                                                                                                                                                                                                                                                                                                 |

|------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7–5  |      | Interrupt vectors 7–5. These bits provide the three MSB's of the interrupt vector for interrupt acknowledge cycles from all sources. To conform to ColdFire interrupt vector allocation these bits should be set equal to or greater than 010. This is the same as writing a value of 0x40 to the register. |

| 4–0  | _    | Reserved, should be cleared.                                                                                                                                                                                                                                                                                |

# 7.5 MBAR Configuration

This is one of the first registers that should be written after reset. MBAR configuration is arbitrarily set by the user.

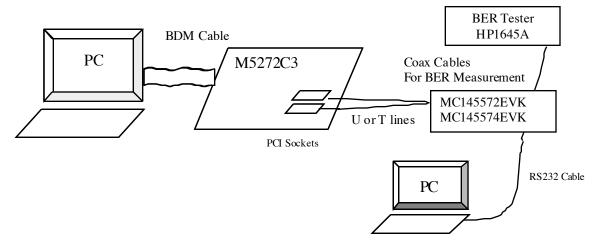

# 7.6 Hardware Configuration

The evaluation board that is used in this setup is the M5272C3. The four ports are available through PCI sockets on the evaluation board. Be sure that, in addition to supplying the evaluation board with power, the user supplies 5V to J7, which supplies power to the daughter cards connected into the PCI sockets. The wire connection between the PC and the board is a BDM wiggler cable. Depending on the tested registers, the external environment could be either MC145572EVK (U Transceiver-oriented board) or MC145574EVK (T transceiver-oriented board). Along with the M5272C3 board, daughter cards will be plugged into these PCI sockets. Most of the time, the T2 daughter boards will be plugged in to evaluate multi-port functionality, D channel access, and other features. The U2 daughter card will be used for IDL BER measurement. The BER tester is the HP1645A, which is directly connected to either the MC145572EVK or MC145574EVK. The hardware setup is as follows:

**Assembly Code Software Configuration**

Figure 20. Hardware Configuration

# 7.7 Software Configuration

This section describes software configuration.

#### 7.7.1 Customer Premises Equipment (CPE)

Depending on the CPE board used, the control software will run differently. This gives the user the ability to control the sourcing transceiver. If the MC145572EVK is used, the RS232 cable is connected and the embedded software will automatically come up with power-on reset. If the MC145574EVK is used, the scp.exe software must be run on a Windows-based PC. (Note: scp.exe software will not run on Windows NT.) Please refer to the specific EVK user's manual for more detailed information about the hardware and software for each.

#### 7.7.2 ColdFire Port Configuration

Writing into the ColdFire core general purpose registers must configure the TDM pins of the MCF5272. With power-on reset, port1 will be automatically configured. Then port0 and some pins of port3 must be configured as a result of the GPIO register access. Table 6 shows the values.

| lab | le | 6. | Port | Pin | Assignments |

|-----|----|----|------|-----|-------------|

|     |    |    |      |     |             |

| Port Pins   | Configured by | Field in Control<br>Register | Control Register<br>Value (Binary) | Map BGA Pin |

|-------------|---------------|------------------------------|------------------------------------|-------------|

| FSC0        | PortA         | PACNT8                       | 01                                 | J2          |

| DCL0        | PortD         | PDCNT0                       | 01                                 | J4          |

| Din0        | PortD         | PDCNT1                       | 01                                 | K1          |

| Dout0       | PortD         | PDCNT4                       | 01                                 | K4          |

| DREQ0       | PortA         | PACNT10                      | 01                                 | K5          |

| DGRANT0     | PortA         | PACNT9                       | 01                                 | J3          |

| FSC1        | Reset         | N/A                          |                                    | L4          |

| DCL1 / DCL2 | Reset         | N/A                          |                                    | M1          |

**Assembly Code Software Configuration**

**Table 6. Port Pin Assignments**

| Port Pins     | Configured by | Field in Control<br>Register | Control Register<br>Value (Binary) | Map BGA Pin |

|---------------|---------------|------------------------------|------------------------------------|-------------|

| Din1 / Din2   | Reset         | N/A                          |                                    | N2          |

| Dout1 / Dout2 | Reset         | N/A                          |                                    | N1          |

| DREQ1         | PortA         | PACNT14                      | 01                                 | M2          |

| DGRANT1       | PortA         | PACNT15                      | 01                                 | M3          |

| FSC2          | PortA         | PACNT12                      | 01                                 | L2          |

| FSC3          | PortA         | PACNT13                      | 01                                 | L3          |

| Din3*         | PortD / Reset | PDCNT5                       | 10 / 00                            | P3 / N2     |

| Dout3         | PortA / Reset | PACNT 7                      | 10 / 00                            | P1 / N1     |

**Note:** The user must keep in mind that ports 1, 2, and 3 share the same resource as long as DCL, Din, and Dout are concerned. This is called the indirect mode. Only the FSC pins are different. In some applications, Din3 and Dout3 might come from other resources, called the direct mode. In this case, PDCNT and PACNT values must be programmed as the above array shows. The MAP BGA pins will, of course, be different.

As a summary, the port control registers values are:

**Table 7. Port Control Register Values**

| Port Control Register | Indirect Mode (Hex) | Direct Mode (Hex) |

|-----------------------|---------------------|-------------------|

| PACNT (MBAR+0x80)     | 55150000            | 55158000          |

| PDCNT (MBAR+0x98)     | 00000105            | 00000905          |

### 7.7.3 Debugger Configuration

Once the code has been compiled with the Diab compiler to the file **main.elf**, the user can download it to the M5272C3 evaluation board via the BDM cable. The configuration file is as follows:

```

set vectbase = 0x000000000

set vectaddr = 0x00000000

@ MBAR = 0x10000001

@ RAMBAR = 0x20000001

# 2MB FLASH on CS0 at 0xFFE000000

write -1 0x10000040=0xFFE00201

write -1 0x10000044=0xFFE00014

# Nothing on CS1 at 0x000000000

write -1 0x10000048=0x000000000

write -1 0x1000004C=0x000000000

# External FSRAM on CS2 at 0x30000000

write -1 0x10000050=0x30000001

write -1 0x10000054=0xFFF80008

```

**Appendix A Software Configuration**

```

# Nothing on CS3 at 0x00000000

# write -1 0x10000058=0x00000000

# write -1 0x1000005C=0x00000000

# CS7 from address 0x00000000 4M byte SDRAM

write -1 0x10000078 = 0x00000701

write -1 0x1000007C = 0xFFC0007C

# setup SDRAM Timing and Control Registers SDCTR then SDCCR

write -1 0x10000184 = 0x0000f415

write -1 0x10000180 = 0x00004211

# rem initialize SDRAM with a write

write -r 0x00040000=0x555555555 # STARTS SDRAM controller

```

# Part VIII Appendix A

This appendix deals with an example of program that has been used to evaluate the MCF5272.

#### **Scope of the program:**

The purpose of that program was not to productize the MCF5272, but to simply evaluate the silicon. This is the reason why the internal architecture might not be optimized to the fullest. Some knowledge of Freescale ISDN products is required, in order to fully activate and send data over the data link. For more information, the user must refer to the MC145572 and MC145574 User's Manuals.

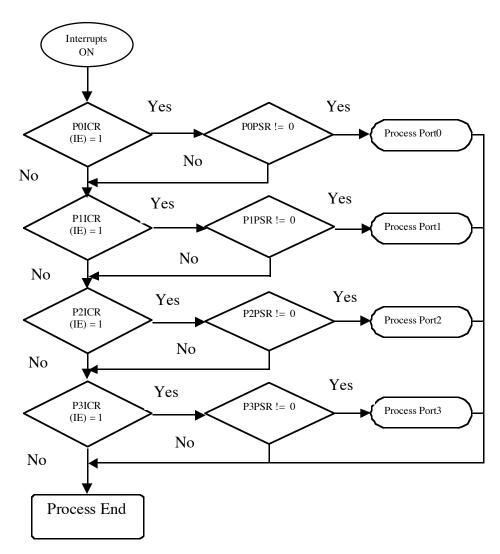

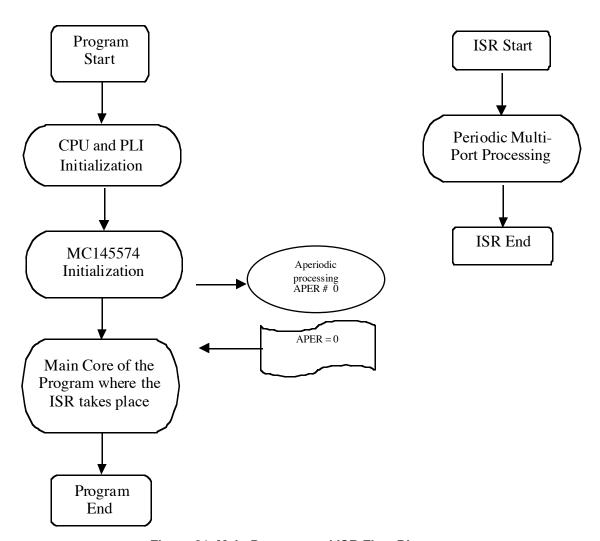

Once the hardware has been correctly set up (see Figure 20), the NT-configured MC145574 chip activates the (NR2 to 0x1) down to the TE-configured MC145574 device. When the link is up and running (NR1 to 0x9), the TE must have the B1 and B2 channels on (NR5 to 0xC). Once connected to the NT-configured T chip, the bit error rate tester (HP 1645A) sends data from the NT device through the link down to the TE device. The purpose of MCF5272 is to capture the received data and to perform a loopback in the ColdFire core via the interrupt service routine. The possible loopbacks that can be tested are all combinations of B channels or D channel by itself. Due to the internal architecture and the special processing of the D channel, the 2B+D loopback cannot be performed. The entire loopback process runs in the ISR. The flow diagram of the program (for both IDL and GCI modes, except that there is no aperiodic interrupt in IDL mode) is as follows:

#### **Appendix A Software Configuration**

Figure 21. Main Program and ISR Flow Diagram

Here below is the MAIN file, with all the invoked files that are necessary

```

.include "configuration.h"

.include "PLIInterupt.s"

.include "PerIntVector.s"

.include "AperIntVector.s"

.include "CoreInit.s"

.include "Init.s"

.include "CPUInit.s"

.include "CPUInit.s"

.include "Table.s"

;Equates

;Interrupt Vectors

;Periodic Interrupt

;Aperiodic Interrupt

;Main file

;Subroutine to init

;Linked to ColdFire Core

.include "Table.s"

```

**Note:** The user must add a space at each beginning of line to make sure the code will be correctly compiled.

This is the file that must be compiled with the following executable file makeit:

#### **Appendix A Software Configuration**

```

das -l -g -Xalign-value -tMCF5206eFN:simple -Xasm-debug-on -I@ -o

main.o target.s

dld -m2 -o main.elf main.o -lc > map

ddump -Rv -o try.mot main.elf

```

Once the main.elf file has been generated, it must be downloaded to the board via the BDM. Shown below are all the files included in main.s.

Configuration.h is the file used for all the definition of the equates. In order to save space, only the important and used equates are shown: i.e. the Initialization registers and the PLIC registers.

- ; Default initial register values

- ; Most of the values are not used for the PLIC evaluation

```

EQU

$00300000

Module Regs Addr

;Addr. of on-chip reg

Init MBAR

EQU

$10000001

;MBAR value

Init_SCR

$0000

EQU

Init PMR

EQU

$0

;Initial value of PMR

$00020000

EQU

UserProgram

;Put program in SDRAM

Init SPR

;Initial value of SPR

EQU

$00E8

Init SCFR

EQU

$1211

;Initial value of SCFR

Init PIVR

EQU

$40

;Initial value of PIVR

$0000000

VBR Init

EQU

$2500

SRValue

EQU

$3

LED

EQU

```

; ADDRESSES OF SYSTEM CONFIGURATION REGISTERS - These are absolute addresses

```

Sys Config Regs

EQU

$00000400

;Absolute address of sers

Sys Config Regs+0

;Module Base Add Register

MBAR

EQU

SCR

EQU

Sys Config Regs+4

;System Config Register

Sys Config Regs+6

SPR

EQU

;System Protection Register

PMR

EQU

Sys_Config_Regs+8

;Power Management Register

Sys_Config_Regs+$C

;Synthesized Clock Freq

SCFR

EQU

Sys Config Regs+$10

DTR

EQU

;Device ID Register

```

; OFFSETS TO MODULES - Offsets w.r.t. contents of MBAR (don't use directly, use register names below)

```

;Offset of SIM's IntC

Intc_Reg_Offset

EQU

$000

Csel Reg Offset

EQU

$040

;Offset of SIM's CSel

Port Reg Offset

EQU

$080

;Offset of SIM's Ports

QSPI_Reg_Offset

EQU

$0A0

;Offset of QSPI module

PWM_Reg_Offset

EQU

$0C0

;Offset of PWM module

DMA_Reg_Offset

EQU

$0E0

;Offset of DMA module

Uart1_Reg_Offset

EQU

$100

;Offset of UART module

;Offset of UART module

Uart2 Reg Offset

EQU

$140

SDRAM_Reg_Offset

;Offset of SDRAM module

EQU

$180

;Offset of Timer module

Timer Reg Offset

EQU

$200

;Offset of PLIC module

PLIC Req Offset

EOU

$300

Ether Req Offset

EQU

$800

;Offset of Ethernet module

USB Reg Offset

EQU

$1000

;Offset of USB module

```

#### Appendix A Software Configuration

; SIM INTERRUPT CONTROLLER REGISTERS

| ICR1<br>ICR2<br>ICR3<br>ICR4<br>ISR<br>PITR<br>PIWR<br>PIWR | EQU<br>EQU<br>EQU<br>EQU<br>EQU<br>EQU<br>EQU | Intc_Reg_Offset+\$20<br>Intc_Reg_Offset+\$24<br>Intc_Reg_Offset+\$28<br>Intc_Reg_Offset+\$2C<br>Intc_Reg_Offset+\$30<br>Intc_Reg_Offset+\$34<br>Intc_Reg_Offset+\$38<br>Intc_Reg_Offset+\$38 | ;Int Control Register<br>;Int Control Register<br>;Int Control Register<br>;Int Control Register<br>;Interrupt Source Register<br>;Prog Interrupt Transition<br>;Prog. Interrupt Wakeup<br>;Prog. Interrupt Vector |

|-------------------------------------------------------------|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ; SIM CHIP                                                  | SELECT RE                                     | GISTERS                                                                                                                                                                                      |                                                                                                                                                                                                                    |

```

BR0

EQU

Csel Reg Offset+$0

;Chip Select Base Register

Csel Reg Offset+$4

OR0

EQU

;CS Option Register

Csel Reg Offset+$8

BR1

EQU

;Chip Select Base Register

OR1

EQU

Csel Reg Offset+$C

;CS Option Register 1

Csel Reg Offset+$10

BR2

EQU

;Chip Select Base Register

OR2

EQU

Csel Reg Offset+$14

;CS Option Register

EQU

Csel Reg Offset+$18

BR3

;Chip Select Base Register

EQU

Csel_Reg_Offset+$1C

OR3

;CS Option Register 3

;CS Base Register 4

BR4

EQU

Csel_Reg_Offset+$20

;CS Option Register 4

OR4

EQU

Csel_Reg_Offset+$24

Csel_Reg_Offset+$28

Csel_Reg_Offset+$2C

BR5

EQU

;CS Base Register 5

EQU

;CS Option Register 5

OR5

EQU

Csel_Reg_Offset+$30

BR6

;CS Base Register 6

Csel_Reg_Offset+$34

OR6

EQU

;CS Option Register 6

BR7

EQU

Csel Req Offset+$38

;CS Base Register 7

OR7

EQU

Csel Reg Offset+$3C

;CS Option Register 7

```

\* SIM PORTS REGISTERS (PORT A and PORT B)

```

PACNT

Port Reg Offset+$00

EQU

;Port A Control Reg

PADDR

EQU

Port Reg Offset+$04

;Port A Data Direction

PADAT

EQU

Port_Reg_Offset+$06

;Port A Data Register

Port_Reg_Offset+$08

PBCNT

EQU

;Port B Control Register

;Port B Data Direction

PBDDR

EOU

Port_Reg_Offset+$0C

PBDAT

EQU

Port Reg Offset+$0E

;Port B Data Register

; Port C has no CNT register - pins controlled by data bus 16/32-bit mode

EQU

Port Reg Offset+$14

;Port C Data Direction

PCDDR

Port_Reg_Offset+$16

PCDAT

;Port C Data Register

EQU

PDCNT

EOU

Port Reg Offset+$18

;Port C Control Register

```

; Port D has no DDR or DAT register - used for pin asignment only

; PLIC MODULE REGISTERS

| P0B1RR | EQU | PLIC Reg Offset+\$00 | ;B1 Data Receive, Port0 |

|--------|-----|----------------------|-------------------------|

| P1B1RR | EQU | PLIC_Reg_Offset+\$04 | ;B1 Data Receive, Port1 |

| P2B1RR | EQU | PLIC Reg Offset+\$08 | ;B1 Data Receive, Port2 |

| P3B1RR | EQU | PLIC_Reg_Offset+\$0C | ;B1 Data Receive, Port3 |

| P0B2RR | EQU | PLIC_Reg_Offset+\$10 | ;B2 Data Receive, Port0 |

| P1B2RR | EQU | PLIC_Reg_Offset+\$14 | ;B2 Data Receive, Port1 |

#### **Appendix A Software Configuration**

| P2B2RR  | EQU | PLIC Reg Offset+\$18 | ;B2 Data Receive, Port2  |

|---------|-----|----------------------|--------------------------|

| P3B2RR  | EQU | PLIC_Reg_Offset+\$1C | ;B2 Data Receive, Port3  |

| P0DRR   | EQU | PLIC Reg Offset+\$20 | ;D Data Receive, Port0   |

| P1DRR   | EQU | PLIC Reg Offset+\$21 | ;D Data Receive, Port1   |

| _       | _   |                      |                          |

| P2DRR   | EQU | PLIC_Reg_Offset+\$22 | ;D Data Receive, Port2   |

| P3DRR   | EQU | PLIC_Reg_Offset+\$23 | ;D Data Receive, Port3   |

| P0B1TR  | EQU | PLIC_Reg_Offset+\$28 | ;B1 Data Transmit, Port0 |

| P1B1TR  | EQU | PLIC Reg Offset+\$2C | ;B1 Data Transmit, Port1 |

| P2B1TR  | EQU | PLIC Reg Offset+\$30 | ;B1 Data Transmit,Port2  |

| P3B1TR  | EQU | PLIC Reg Offset+\$34 | ;B1 Data Transmit, Port3 |

| P0B2TR  | EQU | PLIC Req Offset+\$38 | ;B2 Data Transmit, Port0 |

| P1B2TR  | EQU | PLIC Reg Offset+\$3C | ;B2 Data Transmit, Port1 |

| P2B2TR  | _   |                      | ;B2 Data Transmit, Port2 |

|         | EQU | PLIC_Reg_Offset+\$40 | •                        |

| P3B2TR  | EQU | PLIC_Reg_Offset+\$44 | ;B2 Data Transmit, Port3 |

| P0DTR   | EQU | PLIC_Reg_Offset+\$48 | ;D Data Transmit, Port0  |

| P1DTR   | EQU | PLIC_Reg_Offset+\$49 | ;D Data Transmit, Port1  |

| P2DTR   | EQU | PLIC Reg Offset+\$4A | ;D Data Transmit, Port2  |

| P3DTR   | EQU | PLIC Reg Offset+\$4B | ;D Data Transmit, Port3  |

| PLCR0   | EQU | PLIC Reg Offset+\$50 | ;GCI/IDL config, Port0   |

| PLCR1   | EQU | PLIC Req Offset+\$52 | ;GCI/IDL config, Port1   |

| PLCR2   | EQU | PLIC Reg Offset+\$54 | ;GCI/IDL config, Port2   |

|         | _   | <b>—</b> -—          |                          |

| PLCR3   | EQU | PLIC_Reg_Offset+\$56 | ;GCI/IDL config, Port3   |

| POICR   | EQU | PLIC_Reg_Offset+\$58 | ;GCI Int config, Port0   |

| P1ICR   | EQU | PLIC_Reg_Offset+\$5A | ;GCI Int config, Port1   |

| P2ICR   | EQU | PLIC_Reg_Offset+\$5C | ;GCI Int config, Port2   |

| P3ICR   | EQU | PLIC Reg Offset+\$5E | ;GCI Int config, Port3   |

| P0GMR   | EQU | PLIC Reg Offset+\$60 | GCI Monitor RX, Port0    |

| P1GMR   | EQU | PLIC Reg Offset+\$62 | ;GCI Monitor RX, Port1   |

| P2GMR   | EQU | PLIC Reg Offset+\$64 | ;GCI Monitor RX, Port2   |

| P3GMR   | EQU | PLIC Reg Offset+\$66 | ;GCI Monitor RX, Port3   |

| POGMT   | _   | PLIC Reg Offset+\$68 | ;GCI Monitor TX, Port0   |

|         | EQU |                      |                          |

| P1GMT   | EQU | PLIC_Reg_Offset+\$6A | GCI Monitor TX, Port1    |

| P2GMT   | EQU | PLIC_Reg_Offset+\$6C | ;GCI Monitor TX, Port2   |

| P3GMT   | EQU | PLIC_Reg_Offset+\$6E | ;GCI Monitor TX, Port3   |

| PGMTS   | EQU | PLIC_Reg_Offset+\$71 | GCI Monitor TX status    |

| PGMTA   | EQU | PLIC_Reg_Offset+\$72 | GCI Monitor TX abort     |

| POGCIR  | EQU | PLIC Reg Offset+\$74 | GCI C/I RX, Port0        |

| P1GCIR  | EQU | PLIC_Reg_Offset+\$75 | ;GCI C/I RX, Port1       |

| P2GCIR  | EQU | PLIC Reg Offset+\$76 | ;GCI C/I RX, Port2       |

| P3GCIR  | EQU | PLIC Reg Offset+\$77 | ;GCI C/I RX, Port3       |

| POGCIT  | EQU | PLIC Reg Offset+\$78 | ;GCI C/I TX, Port0       |

| P1GCIT  | EQU | <u> </u>             | ;GCI C/I TX, Port1       |

|         | _   | PLIC_Reg_Offset+\$79 | GGT G/T MY Down 2        |

| P2GCIT  | EQU | PLIC_Reg_Offset+\$7A | ;GCI C/I TX, Port2       |

| P3GCIT  | EQU | PLIC_Reg_Offset+\$7B | ;GCI C/I TX, Port3       |

| PGCITSR | EQU | PLIC_Reg_Offset+\$7F | ;GCI C/I TX status       |

| PDCSR   | EQU | PLIC_Reg_Offset+\$83 | ;D Channel Status        |

| P0PSR   | EQU | PLIC Reg Offset+\$84 | ;Port Status, Port0      |

| P1PSR   | EQU | PLIC Reg Offset+\$86 | ;Port Status, Port1      |

| P2PSR   | EQU | PLIC Reg Offset+\$88 | ;Port Status, Port2      |

| P3PSR   | EQU | PLIC Reg Offset+\$8A | ;Port Status, Port3      |

| PASR    | EQU | PLIC Reg Offset+\$8C | ;Aperiodic Status Reg    |

|         | _   |                      | ;Loopback Control        |

| PLCR    | EQU | PLIC_Reg_Offset+\$8F | •                        |

| PDRQR   | EQU | PLIC_Reg_Offset+\$92 | ;D Channel Request       |

| P0SDR   | EQU | PLIC_Reg_Offset+\$94 | ;Sync Delay, Port0       |

| P1SDR   | EQU | PLIC_Reg_Offset+\$96 | ;Sync Delay, Port1       |

| P2SDR   | EQU | PLIC_Reg_Offset+\$98 | ;Sync Delay, Port2       |

| P3SDR   | EQU | PLIC_Reg_Offset+\$9A | ;Sync Delay, Port3       |

| PCSR    | EQU | PLIC Reg Offset+\$9E | ;Clock Select            |

|         |     | <b>-</b> ·           |                          |

Shown below are the interrupt vector file. As long as the purpose of this evaluation is PLIC oriented, not all vectors need to correspond to a real ISR address:

#### **Appendix A Software Configuration**

|                          | org          | VBR_Init                         |

|--------------------------|--------------|----------------------------------|

| reset_vec                | DC.L         | Init_SSP                         |

| _                        | DC.L         | Code Start                       |

| berr vec                 | DC.L         | berr handler                     |

| aerr_vec                 | DC.L         | aerr_handler                     |

| illeg_vec                | DC.L         | illeg handler                    |

| divz_vec                 | DC.L         | divz_handler                     |

| chk_vec                  | DC.L         | chk_handler                      |

| trapv_vec                | DC.L         | trapv_handler                    |

| privv_vec                | DC.L         | privv_handler                    |

| trace_vec                | DC.L         | trace_handler                    |

| aline_vec                | DC.L         | aline_handler                    |

| fline_vec                | DC.L         | fline_handler                    |

| res12_vec<br>res13_vec   | DC.L<br>DC.L | rsrv_handler<br>rsrv handler     |

| res13_vec                | DC.L         | rsrv_handler                     |

| uninit_vec               | DC.L         | uninit handler                   |

| res16 vec                | DC.L         | rsrv handler                     |

| res17 vec                | DC.L         | rsrv_handler                     |

| res18_vec                | DC.L         | rsrv_handler                     |

| res19 vec                | DC.L         | rsrv handler                     |

| res20 vec                | DC.L         | rsrv handler                     |

| res21_vec                | DC.L         | rsrv_handler                     |

| res22_vec                | DC.L         | rsrv_handler                     |

| res23_vec                | DC.L         | rsrv_handler                     |

| spuri_vec                | DC.L         | spuri_handler                    |

| res25_vec                | DC.L         | rsrv_handler                     |

| res26_vec                | DC.L         | rsrv_handler                     |

| res27_vec                | DC.L         | rsrv_handler                     |

| res28_vec                | DC.L         | rsrv_handler<br>rsrv_handler     |

| res29_vec<br>res30 vec   | DC.L<br>DC.L | rsrv_handler                     |

| res30_vec                | DC.L         | rsrv_handler                     |

| trap0 vec                | DC.L         | trap0 handler                    |

| trap1_vec                | DC.L         | trap1_handler                    |

| trap2 vec                | DC.L         | trap2 handler                    |

| trap3_vec                | DC.L         | trap3 handler                    |

| trap4_vec                | DC.L         | trap4_handler                    |

| trap5 vec                | DC.L         | trap5 handler                    |

| trap6_vec                | DC.L         | trap6_handler                    |

| trap7_vec                | DC.L         | trap7_handler                    |

| trap8_vec                | DC.L         | trap8_handler                    |

| trap9_vec                | DC.L         | trap9_handler                    |

| trap10_vec               | DC.L         | trap10_handler                   |

| trap11_vec               | DC.L         | trap11_handler<br>trap12 handler |

| trap12_vec<br>trap13_vec | DC.L         | trap12_handler                   |

| trap13_vec<br>trap14 vec | DC.L<br>DC.L | trap13_nandler                   |

| trap15 vec               | DC.L         | trap15 handler                   |

| res48 vec                | DC.L         | rsrv_handler                     |

| res49 vec                | DC.L         | rsrv handler                     |

| res50 vec                | DC.L         | rsrv handler                     |

| res51 vec                | DC.L         | rsrv_handler                     |

| res52 vec                | DC.L         | rsrv handler                     |

| res53_vec                | DC.L         | rsrv_handler                     |

| res54_vec                | DC.L         | rsrv_handler                     |

| res55_vec                | DC.L         | rsrv_handler                     |

| res56_vec                | DC.L         | rsrv_handler                     |

| res57_vec                | DC.L         | rsrv_handler                     |

| res58_vec                | DC.L         | rsrv_handler                     |

| res59_vec                | DC.L         | rsrv_handler                     |

| res60_vec<br>res61 vec   | DC.L<br>DC.L | mbar_handler                     |

| TEPOT_AGC                | חר•ח         | mbar_handler                     |

#### **Appendix A Software Configuration**

|                                   |      |                                | • •                       |

|-----------------------------------|------|--------------------------------|---------------------------|

|                                   | DG I |                                |                           |

| res62_vec                         | DC.L | mbar_handler                   |                           |

| res63_vec                         | DC.L | mbar_handler                   |                           |

| i gnur wog                        | DC.L | i gnur handlar                 |                           |

| i_spur_vec<br>int1_vec            | DC.L | i_spur_handler<br>int1 handler |                           |

| int2 vec                          | DC.L | int2 handler                   |                           |

| int3_vec                          | DC.L | int3 handler                   |                           |

| int4 vec                          | DC.L | int4 handler                   |                           |

| i tim1 vec                        | DC.L | i tim1 handler                 | ;Timer interrupt handler  |

| i tim2 vec                        | DC.L | i tim2 handler                 | Timer interrupt handler   |

| i tim3 vec                        | DC.L | i tim3 handler                 | ;Timer interrupt handler  |

| i_tim4_vec                        | DC.L | i_tim4_handler                 | Timer interrupt handler   |

| i_uart1 vec                       | DC.L | i_uart1 handler                | ;UART interrupt handler   |

| i_uart2_vec                       | DC.L | i_uart2_handler                | ;UART interrupt handler   |

| i plic per vec                    | DC.L | i PLIC Periodic                | ;PLIC periodic interrupt  |

| i_plic_aper_vec                   | DC.L | i_PLIC_Aperiodic               | ;PLIC Aperiodic interrupt |

| i_usb0_vec                        | DC.L | i_usb0_handler                 |                           |

| i_usb1_vec                        | DC.L | i_usb1_handler                 |                           |

| i_usb2_vec                        | DC.L | i_usb2_handler                 |                           |

| i_usb3_vec                        | DC.L | i_usb3_handler                 |                           |

| i_usb4_vec                        | DC.L | i_usb4_handler                 |                           |

| i_usb5_vec                        | DC.L | i_usb5_handler                 |                           |

| i_usb6_vec                        | DC.L | i_usb6_handler                 |                           |

| i_usb7_vec                        | DC.L | i_usb7_handler                 |                           |

| i_dma_vec                         | DC.L | i_dma_handler                  |                           |

| i_ether_rx_vec                    | DC.L | i_ether_rx_handler             |                           |

| i_ether_tx_vec                    | DC.L | i_ether_tx_handler             |                           |

| i_ether_ntc_vec                   | DC.L | i_ether_ntc_handler            |                           |

| i_qspi_vec                        | DC.L | i_qspi_handler                 |                           |

| int5_vec                          | DC.L | int5_handler                   |                           |

| int6_vec                          | DC.L | int6_handler                   |                           |

| berr_handler:                     |      |                                |                           |

| aerr_handler:                     |      |                                |                           |

| illeg_handler:                    |      |                                |                           |

| divz_handler:                     |      |                                |                           |

| chk_handler:                      |      |                                |                           |

| trapv_handler:                    |      |                                |                           |

| privv_handler:                    |      |                                |                           |

| trace_handler:                    |      |                                |                           |

| aline_handler:                    |      |                                |                           |

| fline_handler:                    |      |                                |                           |

| rsrv_handler:                     |      |                                |                           |

| uninit_handler:<br>spuri handler: |      |                                |                           |

| trap0 handler:                    |      |                                |                           |

| trapl handler:                    |      |                                |                           |

| trap2 handler:                    |      |                                |                           |

| trap3 handler:                    |      |                                |                           |

| trap4 handler:                    |      |                                |                           |

| trap5 handler:                    |      |                                |                           |

| trap6 handler:                    |      |                                |                           |

| trap7 handler:                    |      |                                |                           |

| trap8_handler:                    |      |                                |                           |

| trap9_handler:                    |      |                                |                           |

| trap10_handler:                   |      |                                |                           |

| trap11_handler:                   |      |                                |                           |

| trap12_handler:                   |      |                                |                           |

| trap13_handler:                   |      |                                |                           |

| trap14_handler:                   |      |                                |                           |

| trap15_handler:                   |      |                                |                           |

| mbar_handler:                     |      |                                |                           |

| i_spur_handler:                   |      |                                |                           |

| int1_handler:                     |      |                                |                           |

|                                   |      |                                |                           |

#### Appendix A Software Configuration

```

int2 handler:

int3 handler:

int4 handler:

i tim1 handler:

i_tim2_handler:

i_tim3_handler:

i_tim4_handler:

i_uart1_handler:

i_uart2_handler:

i usb0 handler:

i usb1 handler:

i usb2 handler:

i usb3 handler:

i_usb4_handler:

i_usb5_handler:

i_usb6_handler:

i_usb7_handler:

i_dma_handler:

i ether rx handler:

i ether tx handler:

i ether ntc handler:

i qspi handler:

int5_handler:

int6 handler:

gon

#$2700

stop

orq

UserProgram

User Ram:

ds.b

10

;Leave 1K for user variables

Stack:

ds.b

10

;Supervisor Stack 1Kbytes

Init SSP

;Initial SSP

```

The file below deals with the general periodic interrupt service routine including all of the bit handling. Not all of the overrun and underrun bits are implemented in this file. Nevertheless, those bits have been verified. Further more, this file has been written as dynamic as possible.

```

*************************

; The program below has been written in the dynamic way. That means