# Freescale Semiconductor

**Application Note**

Document Number: AN2128 Rev. 5, 10/2006

# MPC8240 and MPC8245: Comparison and Compatibility

by Esther C. Alexander

RISC Application

Freescale Semiconductor, Inc.

Austin, TX

This document compares functional and hardware aspects of the MPC8240 with corresponding aspects of the MPC8245.

The MPC8240 is a cost-effective, general-purpose integrated PCI bridge/memory controller processor for applications in networking infrastructure, telecommunications, and other embedded markets. It can be used for control processing in applications such as network routers and switches, mass storage subsystems, network appliances, and print and imaging systems. The MPC8245 is the second generation of the MPC8240. Like the MPC8240, it combines a G2 core microprocessor with a PCI bridge.

Both processors contain a peripheral logic block and a 32-bit superscalar G2 processor core that can operate at a variety of frequencies, allowing the designer to trade performance for lower power consumption. The processor core is clocked from a separate PLL, which is referenced to the peripheral logic PLL so that the microprocessor and the peripheral logic block can operate at different frequencies while maintaining a synchronous bus interface. The interface uses a 64- or 32-bit data bus (depending on memory data bus width) and a 32-bit address bus along with control signals that enable the interface between the processor and peripheral logic to be optimized for performance.

#### Contents

| 1 | Peripheral Logic Comparison                |

|---|--------------------------------------------|

| 2 | Hardware Differences                       |

|   | 2.1 General Parameters                     |

|   | 2.2 Pinout Differences                     |

|   | 2.3 Electrical and Thermal Characteristics |

|   | 2.4 Frequency Comparison                   |

| 3 | Other Compatibility Factors                |

|   | 3.1 General Compatibility                  |

|   | 3.2 Reset Configuration Signal Differences |

|   | 3.3 Register Differences                   |

| 4 | Conclusion                                 |

| 5 | Revision History                           |

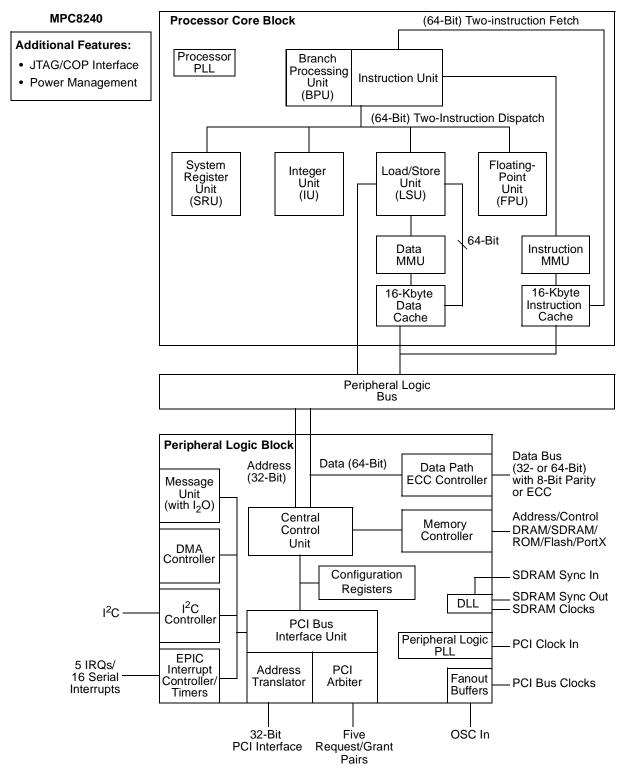

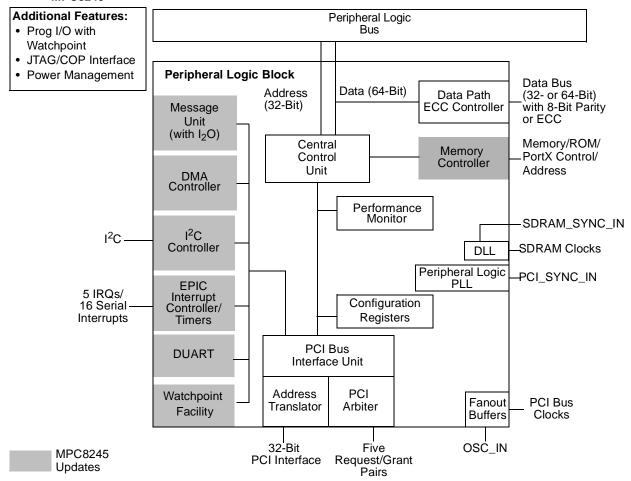

Figure 1 shows the MPC8240 block diagram. The features that differentiate the MPC8245 from the MPC8240 occur in the peripheral logic block. Therefore, a block diagram for the MPC8245 would include the processor core block from Figure 1 and the peripheral logic block shown in Figure 2.

Figure 1. MPC8240 Block Diagram

MPC8240 and MPC8245: Comparison and Compatibility, Rev. 5

### MPC8245

Figure 2. Peripheral Logic Block of the MPC8245

4

# 1 Peripheral Logic Comparison

Table 1 describes the differences between the MPC8240 and the MPC8245 peripheral logic blocks.

**Table 1. Peripheral Logic Block Differences**

| Peripheral Logic Bus                                   | MPC8240                                                            | MPC8245                                                                                    |

|--------------------------------------------------------|--------------------------------------------------------------------|--------------------------------------------------------------------------------------------|

| Integrated memory controller                           | Supports up to 100 MHz SDRAM                                       | Supports up to 133 MHz SDRAM                                                               |

|                                                        | Supports 1 to 8 banks of 16-, 64-<br>128-, 256-Mbit memory devices | Supports 1 to 8 banks of 16-, 64- 128-, 256-, <b>512</b> -Mbit memory devices              |

|                                                        | Supports 1-Mbyte to 1-Gbyte (s) DRAM memory                        | Supports 1-Mbyte to 2-Gbyte SDRAM memory                                                   |

|                                                        | 16 Mbytes of ROM space                                             | <b>272</b> Mbytes of ROM space selectable with reset configuration pin, SDMA1 <sup>1</sup> |

|                                                        | 8-, 32-, or 64-bit PortX, I/O port                                 | 8-, <b>16</b> -, 32-, or 64-bit PortX, I/O port                                            |

|                                                        | 2-ROM chip selects: #0—RCS0,<br>#1—RCS1                            | <b>4</b> -ROM chip selects: #0—RCS0, #1—RCS1, #2—RCS2, #3—RCS3                             |

|                                                        | _                                                                  | Data ready signal (DRDY) <sup>2</sup>                                                      |

|                                                        | _                                                                  | x16 device <sup>3</sup>                                                                    |

| 32-bit PCI interface operating                         | PCI 2.1-compliant                                                  | PCI 2.2-compliant                                                                          |

| up to 66 MHz                                           | _                                                                  | Dual address cycle (DAC) <sup>4</sup> support for 64-bit PCI addressing                    |

| PCI agent mode capability                              | 1 address translation unit                                         | 2 address translation units: 2 inbound and 2 outbound                                      |

| New logic                                              | _                                                                  | Dual UARTs <sup>5</sup> (serial in/serial out)                                             |

|                                                        | _                                                                  | Configurable for a <b>4-pin UART</b> <sup>6</sup>                                          |

|                                                        | _                                                                  | Selectable with reset configuration pin, SDMA0                                             |

| Embedded programmable interrupt controller (EPIC)      | 4 programmable timers                                              | 4 programmable timers with cascade function <sup>7</sup>                                   |

| Inter-integrated circuit (I <sup>2</sup> C) controller | Supported in master and slave mode                                 | Supported in master and slave mode with broadcast enable ability <sup>8</sup>              |

MPC8240 and MPC8245: Comparison and Compatibility, Rev. 5

| Table 1. Peri | pheral Logic | Block Differences | (continued) |

|---------------|--------------|-------------------|-------------|

|               |              |                   |             |

| Peripheral Logic Bus | MPC8240 | MPC8245                                                                        |

|----------------------|---------|--------------------------------------------------------------------------------|

| Performance monitor  |         | System-level performance monitors with interrupts and PCI arbitration monitors |

- Two additional reset configuration signals on the MPC8245 are not used as reset configuration signals on the MPC8240: SDMA0 and SDMA1. The SDMA0 pin selects between the MPC8245 DUART or the MPC8240 backwards-compatible mode PCI\_CLK[0:4] functionality on these multiplexed signals. The default state (logic 1) of SDMA0 selects the MPC8240 backwards-compatible mode of PCI\_CLK[0:4] functionality while a logic 0 state on the SDMA0 signal selects DUART functionality. In DUART mode, four of the five PCI clocks, PCI\_CLK[0:3], are not available. The SDMA1 pin selects between the MPC8245 extended ROM functionality or the MPC8240 backwards-compatible functionality on the multiplexed signals: TBEN, CHK STOP IN, SRESET, TRIG IN, and TRIG OUT. The default state (logic 1) of SDMA1 selects the MPC8240 backwards-compatible mode functionality while a logic 0 state on the SDMA1 signal selects extended ROM functionality. In extended ROM mode, TBEN, CHK\_STOP\_IN, SRESET, TRIG\_IN, and TRIG\_OUT are not available.

- DRDY. Data ready strobe from external PortX device. Usually, an external device asserts it to indicate that a requested transaction is complete.

- x16 device—PortX. A 16-bit general purpose I/O port using ROM controller interface available on RCS2 and RCS3.

- Dual address cycle. Supported in master mode. Dual address cycle (DAC) command (64-bit addressing on PCI bus). DAC differs from single address cycle (SAC) in that the address phase takes two PCI beats instead of one PCI to transfer (64-bit versus 32-bit addressing). Only PCI memory command can use the DAC cycle (that is, no I/O, configuration, interrupt acknowledge, or special cycle command).

- The DUART consists of two (dual) universal asynchronous receiver/transmitters (UARTs). The UART bus is a point-to-point bus, meaning that only two UART devices are attached to the bus. The main functional areas of the UART module are a serial communication channel, 16-bit counter for baud rate generation, internal channel control logic, and interrupt control logic.

- For the MPC8245 to use the DUART module signals, SDMA0 must be pulled low during reset. In the special 4-pin DUART mode, bus line functions SIN1, SOUT1, SIN2, and SOUT2 are used where SIN2 and CTS1 share the same pin, and SOUT2 and RTS1 share the same pin. The clear to send (CTS) and request to send (RTS) functions are disabled. CTS and RTS are on the modem status and modem control registers, respectively.

- Unit cascade mode gives the user the ability to treat the timers as units of measurement or 64-bit timers.

- Broadcast enable allows the MPC8245 to accept broadcast messages from I<sup>2</sup>C bus. Broadcast is enabled by setting bit 1 of the I2CC register. This bit is reserved in the MPC8240.

The hardware differences between the MPC8240 and MPC8245 are divided into the following categories, which are discussed in the following sections:

- General parameters

- Pinout differences

- Electrical and thermal characteristics

- Operating conditions and frequency

### NOTE

The MPC8241 is the lower-cost version of MPC8245. It is a 357 plastic ball grid array (PBGA) package and is functionally the same as the MPC8245, except for differences in frequency, voltage offerings, pin assignments, and packaging. Please refer to the MPC8241 hardware specifications document for details on frequency and source voltage numbers.

MPC8240 and MPC8245: Comparison and Compatibility, Rev. 5 Freescale Semiconductor 5

### 2.1 General Parameters

The nominal core Vdd power supply decreases from 2.5 V on the MPC8240 to 1.8/2.0 V on the MPC8245. The frequency part offerings for the MPC8245 are 266, 300, 333, 350, and 400 MHz. The frequency choices for the MPC8240 are 200 MHz (LZ200) and 250 MHz (RZ250).

**Table 2. General Parameters**

| Parameter         | MPC8240                                                                                            | MPC8245                                                                                                                                                                                                                                                                                                                  |

|-------------------|----------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Technology        | 0.29 µm CMOS, five-layer metal                                                                     | 0.25 μm CMOS, five-layer metal                                                                                                                                                                                                                                                                                           |

| Die size          | 73 mm                                                                                              | 49.2 mm                                                                                                                                                                                                                                                                                                                  |

| Transistor count  | 3.1 million                                                                                        | 4.5 million                                                                                                                                                                                                                                                                                                              |

| Logic status      | Fully static                                                                                       | Fully static                                                                                                                                                                                                                                                                                                             |

| Package           | Surface-mount 352 tape ball grid array (TBGA)                                                      | Surface-mount 352 tape ball grid array (TBGA)                                                                                                                                                                                                                                                                            |

| Core power supply | LZU200: 100 MHz-Mem, 200 MHz-CPU,<br>2.5 ± 5% V<br>RZU250: 100 MHz-Mem, 250 MHz-CPU,<br>2.5–2.75 V | LZU266: 133 MHz-Mem, 266 MHz-CPU, 1.8/2.0 V ±100 mV <sup>1</sup> LZU300: 100 MHz-Mem, 300 MHz-CPU, 1.8/2.0 V ±100 mV <sup>1</sup> LZU333: 133 MHz-Mem, 333 MHz-CPU, 2.0 V ±100 mV <sup>1</sup> LZU350: 100 MHz-Mem, 350 MHz-CPU, 2.0 V ±100 mV <sup>1</sup> RZU400: 133 MHz-Mem, 400 MHz-CPU, 2.1 V ±100 mV <sup>2</sup> |

| I/O power supply  | 3.0 to 3.6 V DC                                                                                    | 3.0 to 3.6 V DC                                                                                                                                                                                                                                                                                                          |

Extended temperature parts (-40° to 105°C) are available for the 266, 300, 333, and 350 MHz parts. See the part number specifications document for these parts in MPC8245TZUPNS/D.

Voltage sequencing requirements for the MPC8245 are similar to those for the MPC8240; however, there are two changes for the MPC8245. First, there is an additional requirement for the MPC8245 that the non-PCI input voltages ( $V_{IN}$ ) must not be greater than either GVdd or OVdd by more than 0.6 V at all times, including during power-on reset. Second, for the MPC8245, LVdd must not exceed OVdd by more than 3.0 V at any time including during power-on reset. The allowable separation between LVdd and OVdd is 3.6 V for the MPC8240. See Table 3 for the definitions of the Vdd, LVdd, OVdd, and GVdd as they pertain to the MPC8240 and the MPC8245.

### 2.2 Pinout Differences

Most pins in the MPC8240 and the MPC8245 have the same name and functions. However, Table 3 lists the differences. For a full signal pin description, consult the appropriate hardware specifications document.

<sup>&</sup>lt;sup>2</sup> See the part number specifications document for this part in MPC8245RZUPNS/D.

**Table 3. Pinout Differences**

|              | Signal                                   | Package Pin Pin Type |                                                              | Dawar Cumply                 | Natas |

|--------------|------------------------------------------|----------------------|--------------------------------------------------------------|------------------------------|-------|

| MPC8240      | MPC8245                                  | Number               | Pin Type                                                     | Power Supply                 | Notes |

| TRIG_IN      | TRIG_IN/RCS2                             | AF20                 | Input—MPC8240<br>I/O—MPC8245                                 | OVdd                         | 1, 2  |

| TRIG_OUT     | TRIG_OUT/RCS3                            | AC18                 | I/O—MPC824<br>Output—MPC8245                                 | OVdd—MPC8240<br>GVdd—MPC8245 | 1, 2  |

| SRESET       | I/O—MPC8245                              |                      | OVdd—MPC8240<br>GVdd—MPC8245                                 | 1, 3                         |       |

| SDBA1/SDMA12 | SDBA1                                    | P1                   | P1 Output GVdd                                               |                              | 3, 4  |

| TEST1        | DRDY                                     | B20 Input OVdd       |                                                              | 1, 5                         |       |

| TBEN         | TBEN/SDMA13                              | B14                  | Input—MPC8240<br>I/O—MPC8245                                 | nt—MPC8240 OVdd<br>—MPC8245  |       |

| CHKSTOP_IN   | CHKSTOP_IN/SDMA14                        | D14                  | Input—MPC8240<br>I/O—MPC8245                                 | GVdd                         | 1, 6  |

| TEST2        | RTC                                      | Y2                   | Input                                                        | GVdd                         | 7     |

| LAVdd        | No Connect                               | D17                  | Power for DLL 2.5 V—<br>MPC8240<br>No connection—<br>MPC8245 | LAVdd                        |       |

|              | D                                        | UART Control         | /Clock Out Signals                                           |                              | ·     |

| PCI_CLK0     | PCI_CLK0/SOUT1                           | AC25                 | Output                                                       | GVdd                         | 8     |

| PCI_CLK1     | PCI_CLK1/SIN1                            | AB25                 | I/O                                                          | GVdd                         | 9     |

| PCI_CLK2     | C2 PCI_CLK2/RTS1/ AE26 Output GVdd SOUT2 |                      | GVdd                                                         | 8                            |       |

| PCI_CLK3     | PCI_CLK3/CTS1/<br>SIN2                   | AF25                 | I/O                                                          | GVdd                         | 9     |

<sup>&</sup>lt;sup>1</sup> A weak pull-up resistor (2 k $\Omega$ -10 k $\Omega$ ) should be placed on this OVdd pin.

<sup>&</sup>lt;sup>2</sup> The TRIG\_IN and TRIG\_OUT pins have the optional function of RCS2 and RCS3. These are additional ROM bank selects.

<sup>3</sup> SDMA12 was switched from the option of sharing with the SDBA1 pin on the MPC8240 to sharing on the SRESET pin of the MPC8245

<sup>&</sup>lt;sup>4</sup> Non-DRAM access output valid specification applies to this pin during non-DRAM accesses.

<sup>&</sup>lt;sup>5</sup> New signal function, DRDY—data ready strobe from PortX device.

<sup>&</sup>lt;sup>6</sup> New signal is one of two new address bits for the most significant address bits (SDMA14, SDMA13) on the MPC8245.

<sup>&</sup>lt;sup>7</sup> Recommend a weak pull-up resistor (2 k $\Omega$ –10 k $\Omega$ ) be placed on this pin to GVdd.

Serial output (SOUT) data and request to send (RTS) signals for UART transactions.

Serial in (SIN) and clear to send (CTS) signals representing data received on the UART receiver serial data input signal, with the least-significant bit received first.

### 2.2.1 Differences between output signals at RESET

During reset, the MPC8240 and the MPC8240 drive most of the output signals to an inactive state. Table 4 compares the output signal states during system reset that differ between the MCP8240 and the MPC8245.

State during System Reset State during System Reset Interface Signal MPC8240 MPC8245 Memory SDMA[1:0] N/A - Reset configuration signals High Impedance SDMA[11:2] Driven SDMA12/SDBA1 (8240) High Impedance Driven if in extended addressing mode, otherwise high impedance SDMA12/SRESET (8245) SDBA0 Driven High Impedance SDBA1 High Impedance Driven SDMA13/TBEN Driven if in extended addressing mode, otherwise high impedance Not an output signal SDMA14/CHKSTOP\_IN PCI\_CLK[0:4] (8240) Clock Driven SOUT1/PCI\_CLK[0] (8245) (Note that PCI\_CLK[1,3] are not Driven output signals on the MPC8245) SOUT2/PCI\_CLK[2] (8245)

**Table 4. Output Signal States during System Reset**

### 2.2.2 **DUART**

The DUART consists of two UARTs that act independently and interface with the CPU. The modules are also accessible from the PCI bus. The UART bus module consists a serial communication channel, 16-bit counter for baud rate generation, internal channel control logic, and interrupt control logic. The DUART communication channel provides a full-duplex asynchronous receiver that operates on frequency from the local memory clock. The transmitter accepts parallel data from the CPU or PCI bus with a write to the transmitter holding register. This data is converted to serial data by the internal transmitter shift register. The receiver accepts the serial data and reconverts it to parallel format and transfers the assembled character from the receiver buffer to the processor or PCI bus in response to a read of the UART receiver buffer register. The receiver status may be polled or interrupt-driven.

### 2.3 Electrical and Thermal Characteristics

The electrical and thermal characteristics include the absolute maximum ratings and recommended operating conditions.

# 2.3.1 Absolute Maximum Ratings

Table 5 lists the absolute maximum rating differences between the two processors compared in this document.

| Table 5. | Absolute | <b>Maximum</b> | Rating | <b>Differences</b> |

|----------|----------|----------------|--------|--------------------|

| Table J. | Absolute | MIGAIIIIGIII   | Naung  | Dilliciciiccs      |

| Characteristic <sup>1</sup>                  | Symbol           | MPC8240      | MPC8245               | Unit |

|----------------------------------------------|------------------|--------------|-----------------------|------|

| Supply Voltage—CPU Core and Peripheral Logic | Vdd              | -0.3 to 2.75 | -0.3 to 2.1           | V    |

| Supply Voltage—Memory Bus Drivers            | GVdd             | -0.3 to 3.6  | -0.3 to 3.6           | V    |

| Supply Voltage—PCI and Standard I/O Buffers  | OVdd             | -0.3 to 3.6  | -0.3 to 3.6           | V    |

| Supply Voltage—PLLs                          | AVdd/AVdd2/LAVdd | -0.3 to 2.75 | _                     | V    |

|                                              | AVdd/AVdd2       | _            | -0.3 to 2.1           | V    |

| Supply Voltage—PCI Reference                 | LVdd             | -0.3 to 5.4  | -0.3 to 5.4           | V    |

| Input Voltage <sup>2</sup>                   | V <sub>IN</sub>  | -0.3 to 3.6  | -0.3 to 3.6           | V    |

| Operational Die-Junction Temperature Range   | TJ               | 0 to 105     | 0 to 105 <sup>3</sup> | °C   |

| Storage Temperature Range                    | T <sub>STG</sub> | -55 to 150   | -55 to 150            | °C   |

Functional and tested operating conditions are given in Table 2. Absolute maximum ratings are stress ratings only, and functional operation at the maximums is not guaranteed. Stresses beyond those listed may affect device reliability or cause permanent damage to the device.

# 2.3.2 Recommended Operating Conditions

Generally, the operating conditions between the MPC8245 and the MPC8240 are the same, but under certain conditions there are some differences, which are listed in Table 6.

**Table 6. Recommended Operating Conditions**

| Characteristics                         | Symbol | Value<br>for the MPC8240 | Value<br>for the MPC8245      | Unit | Cautions                  |

|-----------------------------------------|--------|--------------------------|-------------------------------|------|---------------------------|

| Supply voltage                          | Vdd    | 2.5 ±5%                  | 1.8/2.0 ± 100 mV <sup>1</sup> | V    | 2                         |

| PLL supply voltage—<br>CPU core logic   | AVdd   | 2.5 ±5%                  | 1.8/2.0 ±100 mV <sup>1</sup>  | V    | 2                         |

| PLL supply voltage—<br>peripheral logic | AVdd2  | 2.5 ±5%                  | 1.8/2.0 ± 100 mV <sup>1</sup> | V    | 3                         |

| DLL supply logic                        | LAVdd  | 2.5 ±5%                  | Supplied internally           | V    | MPC8240 only <sup>3</sup> |

See Table 2 for frequency offerings and their specific source voltages.

<sup>&</sup>lt;sup>2</sup> PCI inputs with LVdd = 5 V  $\pm$  5% V DC may be correspondingly stressed at voltages exceeding LVdd + 0.5 V DC.

<sup>&</sup>lt;sup>3</sup> See part number specifications documents for XPC8245RZUxxxPNS and XPC8245TZUxxxPNS.

OVdd must not exceed Vdd/(L)AVdd/AVdd2 by more than 1.8 V at any time including during power-on reset. Also note that the 1.8-V option is only for 266 and 300 MHz parts.

<sup>&</sup>lt;sup>3</sup> Vdd/(L)AVdd/AVdd2 must not exceed OVdd by more than 0.6 V at any time including power-on reset.

# 2.4 Frequency Comparison

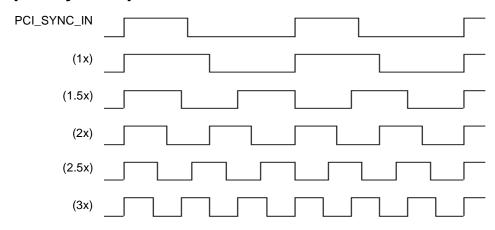

Figure 3. Multiplier Timing Diagram (1x, 1.5x, 2x, 2.5x, and 3x Examples)

There are a few differences in frequency and bit setting arrangements between the MPC8245 and MPC8240. Overall, the internal clock is dependent on the PLL configuration settings in a similar way between the MPC8245 and the MPC8240.

Table 7. Maximum Speeds for MPC8240 and MPC8245

| Unit                         | MPC8240       | MPC8245                                                                                                                       |

|------------------------------|---------------|-------------------------------------------------------------------------------------------------------------------------------|

| MPC603e core processor       | 250 MHz       | 400 MHz                                                                                                                       |

| Integrated memory controller | 100 MHz SDRAM | 133 MHz                                                                                                                       |

| AC timing specifications     | _             | Backward-compatible with those of the MPC8240, in consideration of $T_{os}$ factor. See Section 3.1, "General Compatibility." |

**Note:** The clock multipliers do not allow 133 MHz memory bus speed at 300 and 350 MHz CPU speeds. MPC8241 operates at slower speeds than the MPC8245. For specifics on the MPC8241, see the *MPC8245 Integrated Processor Hardware Specifications*.

Table 8 shows the PLL configuration for the MPC8240. Note that two versions were released (200 and 250 MHz).

Table 8. PLL Configurations for MPC8240

|     |                                   |                                   | 250 MHz <sup>3</sup>                                   |                                                               | 200 MHz <sup>3</sup>           |                                                        |                                                            | Multipliers <sup>4, 5</sup>    |                               |                               |

|-----|-----------------------------------|-----------------------------------|--------------------------------------------------------|---------------------------------------------------------------|--------------------------------|--------------------------------------------------------|------------------------------------------------------------|--------------------------------|-------------------------------|-------------------------------|

| Ref | PLL_<br>CFG<br>[0:4] <sup>1</sup> | CPU <sup>2</sup><br>HID1<br>[0:4] | PCI Clock<br>Input (PCI_<br>SYNC_IN)<br>Range<br>(MHz) | Peripheral<br>Logic/<br>Mem<br>Bus<br>Clock<br>Range<br>(MHz) | CPU<br>Clock<br>Range<br>(MHz) | PCI Clock<br>Input (PCI_<br>SYNC_IN)<br>Range<br>(MHz) | Peripheral<br>Logic/<br>Mem<br>Bus Clock<br>Range<br>(MHz) | CPU<br>Clock<br>Range<br>(MHz) | PCI to<br>Mem<br>(Mem<br>VCO) | Mem to<br>CPU<br>(CPU<br>VCO) |

| 0   | 00000                             | 00110                             | 25–33                                                  | 75–100                                                        | 188–250                        | 25–26                                                  | 75–80                                                      | 188–200                        | 3 (6)                         | 2.5 (5)                       |

| 1   | 00001                             | 11000                             | 25–27                                                  | 75–83                                                         | 225–250                        | Not Usable                                             |                                                            | 3 (6)                          | 3 (6)                         |                               |

| 2   | 00010                             | 00101                             | 50–56 <sup>6</sup>                                     | 50–56                                                         | 100–112                        | 50–56 <sup>6</sup>                                     | 50–56                                                      | 100–112                        | 1 (4)                         | 2 (8)                         |

MPC8240 and MPC8245: Comparison and Compatibility, Rev. 5

Table 8. PLL Configurations for MPC8240 (continued)

|     |                                   |                                   |                                                        | 250 MHz <sup>3</sup>                                          |                                |                                                        | 200 MHz <sup>3</sup>                                       |                                | Multipli                      | iers <sup>4, 5</sup>          |

|-----|-----------------------------------|-----------------------------------|--------------------------------------------------------|---------------------------------------------------------------|--------------------------------|--------------------------------------------------------|------------------------------------------------------------|--------------------------------|-------------------------------|-------------------------------|

| Ref | PLL_<br>CFG<br>[0:4] <sup>1</sup> | CPU <sup>2</sup><br>HID1<br>[0:4] | PCI Clock<br>Input (PCI_<br>SYNC_IN)<br>Range<br>(MHz) | Peripheral<br>Logic/<br>Mem<br>Bus<br>Clock<br>Range<br>(MHz) | CPU<br>Clock<br>Range<br>(MHz) | PCI Clock<br>Input (PCI_<br>SYNC_IN)<br>Range<br>(MHz) | Peripheral<br>Logic/<br>Mem<br>Bus Clock<br>Range<br>(MHz) | CPU<br>Clock<br>Range<br>(MHz) | PCI to<br>Mem<br>(Mem<br>VCO) | Mem to<br>CPU<br>(CPU<br>VCO) |

| 3   | 00011                             | 00101                             |                                                        | Bypass                                                        |                                |                                                        | Bypass                                                     |                                | Bypass                        | 2 (8)                         |

| 4   | 00100                             | 00101                             | 25–28 <sup>6</sup>                                     | 50–56                                                         | 100–113                        | 25–28 <sup>6</sup>                                     | 50–56                                                      | 100–113                        | 2 (8)                         | 2 (8)                         |

| 5   | 00101                             | 00110                             |                                                        | Bypass                                                        |                                |                                                        | Bypass                                                     |                                | Bypass                        | 2.5 (5)                       |

| 7   | 00111                             | 11000                             |                                                        | Bypass                                                        |                                |                                                        | Bypass                                                     |                                |                               | 3 (6)                         |

| 8   | 01000                             | 11000                             | 33 <sup>7</sup> –56 <sup>6</sup>                       | 33–56                                                         | 100–168                        | 33 <sup>7</sup> –56 <sup>6</sup>                       | 33–56                                                      | 100–168                        | 1 (4)                         | 3 (6)                         |

| Α   | 01010                             | 00111                             | 25–27                                                  | 50–55                                                         | 225–250                        |                                                        | Not Usable                                                 |                                | 2 (4)                         | 4.5 (9)                       |

| С   | 01100                             | 00110                             | 25–50                                                  | 50-100                                                        | 125–250                        | 25–40                                                  | 50–80                                                      | 125–200                        | 2 (4)                         | 2.5 (5)                       |

| Е   | 01110                             | 11000                             | 25–41                                                  | 50-83                                                         | 150–250                        | 25–33                                                  | 50–66                                                      | 150–200                        | 2 (4)                         | 3 (6)                         |

| 10  | 10000                             | 00100                             | 25–33                                                  | 75–100                                                        | 150–200                        | 25–33                                                  | 75–100                                                     | 150–200                        | 3 (6)                         | 2 (4)                         |

| 12  | 10010                             | 00100                             | 33–66                                                  | 50-100                                                        | 100–200                        | 33 <sup>8</sup> – 66                                   | 50-100                                                     | 100–200                        | 1.5 (3)                       | 2 (4)                         |

| 14  | 10100                             | 11110                             | 25–35                                                  | 50–71                                                         | 175–250                        | 25–28                                                  | 50–56                                                      | 175–200                        | 2 (4)                         | 3.5 (7)                       |

| 16  | 10110                             | 11010                             | 25–31                                                  | 50–62                                                         | 200–250                        | 25                                                     | 50                                                         | 200                            | 2 (4)                         | 4 (8)                         |

| 18  | 11000                             | 11000                             | 25–33                                                  | 62–83                                                         | 186–250                        | 25–26                                                  | 62–65                                                      | 186–200                        | 2.5 (5)                       | 3 (6)                         |

| 1A  | 11010                             | 11010                             | 50 <sup>8</sup> –62                                    | 50–62                                                         | 200–250                        | 50                                                     | 50                                                         | 200                            | 1 (2)                         | 4 (8)                         |

| 1C  | 11100                             | 11000                             | 33 <sup>8</sup> –55                                    | 50–83                                                         | 150–250                        | 33 <sup>8</sup> –44                                    | 50–66                                                      | 150-200                        | 1.5 (3)                       | 3 (6)                         |

| 1D  | 11101                             | 00110                             | 33 <sup>8</sup> –66                                    | 50-100                                                        | 125–250                        | 33 <sup>8</sup> –53                                    | 50-80                                                      | 125–200                        | 1.5 (3)                       | 2.5 (5)                       |

| 1E  | 11110                             | 01111                             |                                                        | Not Usable                                                    |                                |                                                        |                                                            | Off                            | Off                           |                               |

| 1F  | 11111                             | 11111                             |                                                        |                                                               | Not U                          | sable                                                  |                                                            |                                | Off                           | Off                           |

PLL\_CFG[0:4] settings not listed (00110, 01001, 01011, 01101, 01111, 10001, 10011, 10101, 10111, 11001, and 11011) are reserved.

The MPC8245 PLL\_CFG[0:4] setting 0x02 (0b00010) has a different PCI-to-Mem and Mem-to-CPU multiplier ratio than the same setting on the MPC8240, and thus, is not backwards-compatible.

MPC8240 and MPC8245: Comparison and Compatibility, Rev. 5

The processor HID1 values only represent the multiplier of the processor's PLL (memory to processor multiplier) Thus, multiple MPC8240 PLL\_CFG[0:4] values may have the same processor HID1 value. This implies that system software cannot read the HID1 register and associate it with a unique PLL\_CFG[0:4] value.

<sup>&</sup>lt;sup>3</sup> Range values are shown rounded down to the nearest whole number (decimal place accuracy removed) for clarity.

In PLL bypass mode, the PCI\_SYNC\_IN input signal clocks the internal processor directly, the peripheral logic PLL is disabled, and the bus mode is set for 1:1 (PCI:Mem) mode operation. This mode is intended for factory use only. The AC timing specifications given in this document do not apply in PLL bypass mode.

In clock off mode, no clocking occurs inside the MPC8240 regardless of the PCI\_SYNC\_IN input.

<sup>&</sup>lt;sup>6</sup> Limited due to maximum memory VCO = 225 MHz.

<sup>&</sup>lt;sup>7</sup> Limited due to minimum CPU VCO = 200 MHz.

<sup>&</sup>lt;sup>8</sup> Limited due to minimum memory VCO = 100 MHz.

Some PLL configurations may not be fully backwards-compatible between the MPC8240 and the MPC8245. For example, the MPC8245 PLL\_CFG[0:4] setting 0x0C (0b01100) is capable of accepting a subset of the PCI\_SYNC\_IN input frequency range of that of the MPC8240, and thus, may not be fully backwards-compatible. Also note that certain PLL configurations available in the MPC8245 are not available in the MPC8240. For example, configuration 0x11 (0b10001) does not exist on the MPC8240, but is available in the MPC8245. Table 9 through Table 18 show the PLL settings for the MPC8245. Note that five CPU frequency offerings are available: 266 MHz, 300 MHz, 333 MHz, 350 MHz, and 400 MHz.

Table 9. PLL Configurations (266- and 300-MHz Parts)

|            |                                   | 20                                                                     | 66-MHz Part                                           | 9                              | 30                                                                     | 00-MHz Part                                           | 9                              | Multipliers                    |                                |

|------------|-----------------------------------|------------------------------------------------------------------------|-------------------------------------------------------|--------------------------------|------------------------------------------------------------------------|-------------------------------------------------------|--------------------------------|--------------------------------|--------------------------------|

| Ref. No.   | PLL_CFG<br>[0:4] <sup>10,13</sup> | PCI Clock<br>Input<br>(PCI_<br>SYNC_IN)<br>Range <sup>1</sup><br>(MHz) | Periph<br>Logic/<br>MemBus<br>Clock<br>Range<br>(MHz) | CPU<br>Clock<br>Range<br>(MHz) | PCI Clock<br>Input<br>(PCI_<br>SYNC_IN)<br>Range <sup>1</sup><br>(MHz) | Periph<br>Logic/<br>MemBus<br>Clock<br>Range<br>(MHz) | CPU<br>Clock<br>Range<br>(MHz) | PCI-to-<br>Mem<br>(Mem<br>VCO) | Mem-to-<br>CPU<br>(CPU<br>VCO) |

| 0          | 00000 <sup>12</sup>               | 25–35 <sup>5</sup>                                                     | 75–105                                                | 188–263                        | 25-40 <sup>5,7</sup>                                                   | 75–120                                                | 188–300                        | 3 (2)                          | 2.5 (2)                        |

| 1          | 00001 <sup>12</sup>               | 25–29 <sup>5</sup>                                                     | 75–88                                                 | 225–264                        | 25–33 <sup>5</sup>                                                     | 75–99                                                 | 225–297                        | 3 (2)                          | 3 (2)                          |

| 2          | 00010 <sup>11</sup>               | 50 <sup>18</sup> –59 <sup>5,7</sup>                                    | 50–59                                                 | 225–266                        | 50 <sup>18</sup> –66 <sup>1</sup>                                      | 50–66                                                 | 225–297                        | 1 (4)                          | 4.5 (2)                        |

| 3          | 00011 <sup>11,14</sup>            | 50 <sup>17</sup> –66 <sup>1</sup>                                      | 50–66                                                 | 100–133                        | 50 <sup>17</sup> –66 <sup>1</sup>                                      | 50–66                                                 | 100–133                        | 1 (Bypass)                     | 2 (4)                          |

| 4          | 00100 <sup>12</sup>               | 25–46 <sup>4</sup>                                                     | 50–92                                                 | 100–184                        | 25–46 <sup>4</sup>                                                     | 50–92                                                 | 100–184                        | 2 (4)                          | 2 (4)                          |

| 6          | 00110 <sup>15</sup>               | Bypass                                                                 |                                                       |                                |                                                                        | Bypass                                                |                                | Bypass                         |                                |

| 7<br>Rev B | 00111 <sup>14</sup>               | 60 <sup>6</sup> –66 <sup>1</sup>                                       | 60–66                                                 | 180–198                        | 60 <sup>6</sup> –66 <sup>1</sup>                                       | 60–66                                                 | 180–198                        | 1 (Bypass)                     | 3 (2)                          |

| 7<br>Rev D | 00111 <sup>14</sup>               |                                                                        |                                                       |                                | Not av                                                                 | ailable                                               |                                |                                |                                |

| 8          | 01000 <sup>12</sup>               | 60 <sup>6</sup> –66 <sup>1</sup>                                       | 60–66                                                 | 180–198                        | 60 <sup>6</sup> –66 <sup>1</sup>                                       | 60–66                                                 | 180–198                        | 1 (4)                          | 3 (2)                          |

| 9          | 01001 <sup>12</sup>               | 45 <sup>6</sup> –66 <sup>1</sup>                                       | 90–132                                                | 180–264                        | 45 <sup>6</sup> –66 <sup>1</sup>                                       | 90–132                                                | 180–264                        | 2 (2)                          | 2 (2)                          |

| А          | 01010 <sup>12</sup>               | 25–29 <sup>5</sup>                                                     | 50–58                                                 | 225–261                        | 25–33 <sup>5</sup>                                                     | 50–66                                                 | 225–297                        | 2 (4)                          | 4.5 (2)                        |

| В          | 01011 <sup>12</sup>               | 45 <sup>3</sup> –59 <sup>5</sup>                                       | 68–88                                                 | 204–264                        | 45 <sup>3</sup> –66 <sup>1</sup>                                       | 68–99                                                 | 204–297                        | 1.5 (2)                        | 3 (2)                          |

| С          | 01100 <sup>12</sup>               | 36 <sup>6</sup> –46 <sup>4</sup>                                       | 72–92                                                 | 180–230                        | 36 <sup>6</sup> –46 <sup>4</sup>                                       | 72–92                                                 | 180–230                        | 2 (4)                          | 2.5 (2)                        |

| D          | 01101 <sup>12</sup>               | 45 <sup>3</sup> –50 <sup>5</sup>                                       | 68–75                                                 | 238–263                        | 45 <sup>3</sup> –57 <sup>5</sup>                                       | 68–85                                                 | 238–298                        | 1.5 (2)                        | 3.5 (2)                        |

| Е          | 01110 <sup>12</sup>               | 30 <sup>6</sup> –44 <sup>5</sup>                                       | 60–88                                                 | 180–264                        | 30 <sup>6</sup> –46 <sup>4</sup>                                       | 60–92                                                 | 180–276                        | 2 (4)                          | 3 (2)                          |

| F          | 01111 <sup>12</sup>               | 25 <sup>5</sup>                                                        | 75                                                    | 263                            | 25–28 <sup>5</sup>                                                     | 75–85                                                 | 263–298                        | 3 (2)                          | 3.5 (2)                        |

| 10         | 10000 <sup>12</sup>               | 30 <sup>6</sup> -44 <sup>2,5</sup>                                     | 90–132                                                | 180–264                        | 30 <sup>6</sup> -44 <sup>2</sup>                                       | 90–132                                                | 180–264                        | 3 (2)                          | 2 (2)                          |

| 11         | 10001 <sup>12</sup>               | 25–26 <sup>5,7</sup>                                                   | 100–106                                               | 250–266                        | 25–29 <sup>2</sup>                                                     | 100–116                                               | 250–290                        | 4 (2)                          | 2.5 (2)                        |

| 12         | 10010 <sup>12</sup>               | 60 <sup>6</sup> –66 <sup>1</sup>                                       | 90–99                                                 | 180–198                        | 60 <sup>6</sup> –66 <sup>1</sup>                                       | 90–99                                                 | 180–198                        | 1.5 (2)                        | 2 (2)                          |

### Table 9. PLL Configurations (266- and 300-MHz Parts) (continued)

|             |                                   | 2                                                                      | 66-MHz Part                                           | 9                              | 30                                                                     | 00-MHz Part                                           | 9                              | Multipliers                    |                                |

|-------------|-----------------------------------|------------------------------------------------------------------------|-------------------------------------------------------|--------------------------------|------------------------------------------------------------------------|-------------------------------------------------------|--------------------------------|--------------------------------|--------------------------------|

| Ref. No.    | PLL_CFG<br>[0:4] <sup>10,13</sup> | PCI Clock<br>Input<br>(PCI_<br>SYNC_IN)<br>Range <sup>1</sup><br>(MHz) | Periph<br>Logic/<br>MemBus<br>Clock<br>Range<br>(MHz) | CPU<br>Clock<br>Range<br>(MHz) | PCI Clock<br>Input<br>(PCI_<br>SYNC_IN)<br>Range <sup>1</sup><br>(MHz) | Periph<br>Logic/<br>MemBus<br>Clock<br>Range<br>(MHz) | CPU<br>Clock<br>Range<br>(MHz) | PCI-to-<br>Mem<br>(Mem<br>VCO) | Mem-to-<br>CPU<br>(CPU<br>VCO) |

| 13          | 10011 <sup>12</sup>               |                                                                        | Not available                                         |                                | 25 <sup>2,7</sup>                                                      | 100                                                   | 300                            | 4 (2)                          | 3 (2)                          |

| 14          | 10100 <sup>12</sup>               | 26 <sup>6</sup> –38 <sup>5</sup>                                       | 52–76                                                 | 182–266                        | 26 <sup>6</sup> –42 <sup>5</sup>                                       | 52–84                                                 | 182–294                        | 2 (4)                          | 3.5 (2)                        |

| 15          | 10101 <sup>12</sup>               | Not available                                                          |                                                       |                                | 27 <sup>3</sup> –30 <sup>5,7</sup>                                     | 68–75                                                 | 272–300                        | 2.5 (2)                        | 4 (2)                          |

| 16          | 10110 <sup>12</sup>               | 25–33 <sup>5</sup>                                                     | 50–66                                                 | 200–264                        | 25–37 <sup>5</sup>                                                     | 50–74                                                 | 200–296                        | 2 (4)                          | 4 (2)                          |

| 17          | 10111 <sup>12</sup>               | 25–33 <sup>5</sup>                                                     | 100–132                                               | 200–264                        | 25–33 <sup>2</sup>                                                     | 100–132                                               | 200–264                        | 4 (2)                          | 2 (2)                          |

| 18          | 11000 <sup>12</sup>               | 27 <sup>3</sup> –35 <sup>5</sup>                                       | 68–88                                                 | 204–264                        | 27 <sup>3</sup> –40 <sup>5,7</sup>                                     | 68–100                                                | 204–300                        | 2.5 (2)                        | 3 (2)                          |

| 19          | 11001 <sup>12</sup>               | 36 <sup>6</sup> –53 <sup>5</sup>                                       | 72–106                                                | 180–265                        | 36 <sup>6</sup> –59 <sup>2</sup>                                       | 72–118                                                | 180–295                        | 2 (2)                          | 2.5 (2)                        |

| 1A          | 11010 <sup>12</sup>               | 50 <sup>18</sup> –66 <sup>1</sup>                                      | 50–66                                                 | 200–264                        | 50 <sup>18</sup> –66 <sup>1</sup>                                      | 50–66                                                 | 200–264                        | 1 (4)                          | 4 (2)                          |

| 1B          | 11011 <sup>12</sup>               | 34 <sup>3</sup> –44 <sup>5</sup>                                       | 68–88                                                 | 204–264                        | 34 <sup>3</sup> –50 <sup>5,7</sup>                                     | 68–100                                                | 204–300                        | 2 (2)                          | 3 (2)                          |

| 1C          | 11100 <sup>12</sup>               | 44 <sup>3</sup> –59 <sup>5</sup>                                       | 66–88                                                 | 198–264                        | 44 <sup>3</sup> –66 <sup>1</sup>                                       | 66–99                                                 | 198–297                        | 1.5 (2)                        | 3 (2)                          |

| 1D          | 11101 <sup>12</sup>               | 48 <sup>6</sup> –66 <sup>1</sup>                                       | 72–99                                                 | 180–248                        | 48 <sup>6</sup> –66 <sup>1</sup>                                       | 72–99                                                 | 180–248                        | 1.5 (2)                        | 2.5 (2)                        |

| 1E<br>Rev B | 11110 <sup>8</sup>                | Not usable                                                             |                                                       |                                | Not usable                                                             |                                                       | Off                            | Off                            |                                |

| 1E<br>Rev D | 11110                             | 33 <sup>3</sup> –38 <sup>5</sup>                                       | 66–76                                                 | 231–266                        | 33 <sup>3</sup> –42 <sup>5</sup>                                       | 66–84                                                 | 231–294                        | 2(2)                           | 3.5(2)                         |

Table 9. PLL Configurations (266- and 300-MHz Parts) (continued)

|          |                                   |                                                                        | 66-MHz Part                                           | 9                              | 30                                                                     | 00-MHz Part                                           | 9                              | Multi                          | pliers                         |

|----------|-----------------------------------|------------------------------------------------------------------------|-------------------------------------------------------|--------------------------------|------------------------------------------------------------------------|-------------------------------------------------------|--------------------------------|--------------------------------|--------------------------------|

| Ref. No. | PLL_CFG<br>[0:4] <sup>10,13</sup> | PCI Clock<br>Input<br>(PCI_<br>SYNC_IN)<br>Range <sup>1</sup><br>(MHz) | Periph<br>Logic/<br>MemBus<br>Clock<br>Range<br>(MHz) | CPU<br>Clock<br>Range<br>(MHz) | PCI Clock<br>Input<br>(PCI_<br>SYNC_IN)<br>Range <sup>1</sup><br>(MHz) | Periph<br>Logic/<br>MemBus<br>Clock<br>Range<br>(MHz) | CPU<br>Clock<br>Range<br>(MHz) | PCI-to-<br>Mem<br>(Mem<br>VCO) | Mem-to-<br>CPU<br>(CPU<br>VCO) |

| 1F       | 11111 <sup>8</sup>                | Not usable                                                             |                                                       |                                | Not usable                                                             |                                                       | Off Off                        |                                |                                |

### Notes:

- 1. Limited by the maximum PCI input frequency (66 MHz).

- 2 Limited by the maximum system memory interface operating frequency (100 MHz @ 300 MHz CPU).

- 3. Limited by the minimum memory VCO frequency (133 MHz).

- 4. Limited due to the maximum memory VCO frequency (372 MHz).

- 5. Limited by the maximum CPU operating frequency.

- 6. Limited by the minimum CPU VCO frequency (360 MHz).

- 7. Limited by the maximum CPU VCO frequency (maximum marked CPU speed X 2).

- 8. In clock-off mode, no clocking occurs inside the MPC8245, regardless of the PCI\_SYNC\_IN input.

- 9. Range values are rounded down to the nearest whole number (decimal place accuracy removed).

- 10. PLL\_CFG[0:4] settings not listed are reserved.

- 11. Multiplier ratios for this PLL\_CFG[0:4] setting differ from the MPC8240 and are not backward-compatible.

- 12. PCI\_SYNC\_IN range for this PLL\_CFG[0:4] setting differs from or does not exist on the MPC8240 and may not be fully backward-compatible.

- 13. Bits 7–4 of register offset <0xE2> contain the PLL\_CFG[0:4] setting value.

- 14. In PLL bypass mode, the PCI\_SYNC\_IN input signal clocks the internal processor directly, the peripheral logic PLL is disabled, and the bus mode is set for 1:1 (PCI:Mem) mode operation. This mode is for hardware modeling. The AC timing specifications in this document do not apply in PLL bypass mode.

- 15. In dual PLL bypass mode, the PCI\_SYNC\_IN input signal clocks the internal peripheral logic directly, the peripheral logic PLL is disabled, and the bus mode is set for 1:1 (PCI\_SYNC\_IN:Mem) mode operation. In this mode, the OSC\_IN input signal clocks the internal processor directly in 1:1 (OSC\_IN:CPU) mode operation, and the processor PLL is disabled. The PCI\_SYNC\_IN and OSC\_IN input clocks must be externally synchronized. This mode is for hardware modeling. The AC timing specifications in this document do not apply in dual PLL bypass mode.

- 16. Limited by the maximum system memory interface operating frequency (133 MHz @ 266 MHz CPU).

- 17. Limited by the minimum CPU operating frequency (100 MHz).

- 18. Limited by the minimum memory bus frequency (50 MHz).

Table 10. PLL Configurations (333- and 350-MHz Parts)

|     |                                   | 33                                                                     | 33 MHz Part <sup>9</sup>                           | 1                              | 35                                                                     | 50 MHz Part <sup>9</sup>                           | )                              | Multip                         | liers                          |

|-----|-----------------------------------|------------------------------------------------------------------------|----------------------------------------------------|--------------------------------|------------------------------------------------------------------------|----------------------------------------------------|--------------------------------|--------------------------------|--------------------------------|

| Ref | PLL_<br>CFG[0:4] <sup>10,13</sup> | PCI Clock<br>Input<br>(PCI_<br>SYNC_IN)<br>Range <sup>1</sup><br>(MHz) | Periph<br>Logic/Mem<br>Bus Clock<br>Range<br>(MHz) | CPU<br>Clock<br>Range<br>(MHz) | PCI Clock<br>Input<br>(PCI_<br>SYNC_IN)<br>Range <sup>1</sup><br>(MHz) | Periph<br>Logic/Mem<br>Bus Clock<br>Range<br>(MHz) | CPU<br>Clock<br>Range<br>(MHz) | PCI-to-<br>Mem<br>(Mem<br>VCO) | Mem-to-<br>CPU<br>(CPU<br>VCO) |

| 0   | 00000 <sup>12</sup>               | 25–44 <sup>16</sup>                                                    | 75–132                                             | 188–330                        | 25–44 <sup>16</sup>                                                    | 75–132                                             | 188–330                        | 3 (2)                          | 2.5 (2)                        |

| 1   | 00001 <sup>12</sup>               | 25–37 <sup>5,7</sup>                                                   | 75–111                                             | 225–333                        | 25–38 <sup>5</sup>                                                     | 75–114                                             | 225–342                        | 3 (2)                          | 3 (2)                          |

MPC8240 and MPC8245: Comparison and Compatibility, Rev. 5

Table 10. PLL Configurations (333- and 350-MHz Parts) (continued)

|            |                                   | 33                                                                     | 33 MHz Part <sup>9</sup>                           | )                              | 35                                                                     | 50 MHz Part <sup>9</sup>                           | )                              | Multipliers                    |                                |

|------------|-----------------------------------|------------------------------------------------------------------------|----------------------------------------------------|--------------------------------|------------------------------------------------------------------------|----------------------------------------------------|--------------------------------|--------------------------------|--------------------------------|

| Ref        | PLL_<br>CFG[0:4] <sup>10,13</sup> | PCI Clock<br>Input<br>(PCI_<br>SYNC_IN)<br>Range <sup>1</sup><br>(MHz) | Periph<br>Logic/Mem<br>Bus Clock<br>Range<br>(MHz) | CPU<br>Clock<br>Range<br>(MHz) | PCI Clock<br>Input<br>(PCI_<br>SYNC_IN)<br>Range <sup>1</sup><br>(MHz) | Periph<br>Logic/Mem<br>Bus Clock<br>Range<br>(MHz) | CPU<br>Clock<br>Range<br>(MHz) | PCI-to-<br>Mem<br>(Mem<br>VCO) | Mem-to-<br>CPU<br>(CPU<br>VCO) |

| 2          | 00010 <sup>11</sup>               | 50 <sup>18</sup> –66 <sup>1</sup>                                      | 50-66                                              | 225–297                        | 50 <sup>18</sup> –66 <sup>1</sup>                                      | 50–66                                              | 225–297                        | 1 (4)                          | 4.5 (2)                        |

| 3          | 00011 <sup>11,14</sup>            | 50 <sup>17</sup> –66 <sup>1</sup>                                      | 50-66                                              | 100–133                        | 50 <sup>17</sup> –66 <sup>1</sup>                                      | 50–66                                              | 100–133                        | 1 (Bypass)                     | 2 (4)                          |

| 4          | 00100 <sup>12</sup>               | 25-46 <sup>4</sup>                                                     | 50-92                                              | 100–184                        | 25–46 <sup>4</sup>                                                     | 50–92                                              | 100–184                        | 2 (4)                          | 2 (4)                          |

| 6          | 00110 <sup>15</sup>               |                                                                        | Bypass                                             |                                |                                                                        | Bypass                                             |                                | Вура                           | ass                            |

| 7<br>Rev B | 00111 <sup>14</sup>               | 60 <sup>6</sup> –66 <sup>1</sup>                                       | 60–66                                              | 180–198                        | 60 <sup>6</sup> –66 <sup>1</sup>                                       | 60–66                                              | 180–198                        | 1 (Bypass)                     | 3 (2)                          |

| 7<br>Rev D | 00111 <sup>14</sup>               | 1                                                                      | Not available                                      |                                | 25                                                                     | 100                                                | 350                            | 4(2)                           | 3.5(2)                         |

| 8          | 01000 <sup>12</sup>               | 60 <sup>6</sup> –66 <sup>1</sup>                                       | 60–66                                              | 180–198                        | 60 <sup>6</sup> –66 <sup>1</sup>                                       | 60–66                                              | 180–198                        | 1 (4)                          | 3 (2)                          |

| 9          | 01001 <sup>12</sup>               | 45 <sup>6</sup> –66 <sup>1</sup>                                       | 90–132                                             | 180–264                        | 45 <sup>6</sup> –66 <sup>1</sup>                                       | 90–132                                             | 180–264                        | 2 (2)                          | 2 (2)                          |

| Α          | 01010 <sup>12</sup>               | 25–37 <sup>5,7</sup>                                                   | 50–74                                              | 225–333                        | 25–38 <sup>5</sup>                                                     | 50–76                                              | 225–342                        | 2 (4)                          | 4.5 (2)                        |

| В          | 01011 <sup>12</sup>               | 45 <sup>3</sup> –66 <sup>1</sup>                                       | 68–99                                              | 204–297                        | 45 <sup>3</sup> –66 <sup>1</sup>                                       | 68–99                                              | 204–297                        | 1.5 (2)                        | 3 (2)                          |

| С          | 01100 <sup>12</sup>               | 36 <sup>6</sup> –46 <sup>4</sup>                                       | 72–92                                              | 180–230                        | 36 <sup>6</sup> –46 <sup>4</sup>                                       | 72–92                                              | 180–230                        | 2 (4)                          | 2.5 (2)                        |

| D          | 01101 <sup>12</sup>               | 45 <sup>3</sup> –63 <sup>5,7</sup>                                     | 68–95                                              | 238–333                        | 45 <sup>3</sup> –66 <sup>1</sup>                                       | 68–99                                              | 238–347                        | 1.5 (2)                        | 3.5 (2)                        |

| Е          | 01110 <sup>12</sup>               | 30 <sup>6</sup> –46 <sup>4</sup>                                       | 60–92                                              | 180–276                        | 30 <sup>6</sup> –46 <sup>4</sup>                                       | 60–92                                              | 180–276                        | 2 (4)                          | 3 (2)                          |

| F          | 01111 <sup>12</sup>               | 25–31 <sup>5</sup>                                                     | 75–93                                              | 263–326                        | 25–33 <sup>5</sup>                                                     | 75–99                                              | 263–347                        | 3 (2)                          | 3.5 (2)                        |

| 10         | 10000 <sup>12</sup>               | 30 <sup>6</sup> –44 <sup>2</sup>                                       | 90–132                                             | 180–264                        | 30 <sup>6</sup> –44 <sup>2</sup>                                       | 90–132                                             | 180–264                        | 3 (2)                          | 2 (2)                          |

| 11         | 10001 <sup>12</sup>               | 25–33 <sup>2,16</sup>                                                  | 100–132                                            | 250–330                        | 25-33 <sup>2,16</sup>                                                  | 100–132                                            | 250–330                        | 4 (2)                          | 2.5 (2)                        |

| 12         | 10010 <sup>12</sup>               | 60 <sup>6</sup> –66 <sup>1</sup>                                       | 90–99                                              | 180–198                        | 60 <sup>6</sup> –66 <sup>1</sup>                                       | 90–99                                              | 180–198                        | 1.5 (2)                        | 2 (2)                          |

| 13         | 10011 <sup>12</sup>               | 25–27 <sup>5</sup>                                                     | 100–108                                            | 300–324                        | 25–29 <sup>5</sup>                                                     | 100–116                                            | 300–348                        | 4 (2)                          | 3 (2)                          |

| 14         | 10100 <sup>12</sup>               | 26 <sup>6</sup> –47 <sup>4</sup>                                       | 52-94                                              | 182–329                        | 26 <sup>6</sup> –47 <sup>4</sup>                                       | 52–94                                              | 182–329                        | 2 (4)                          | 3.5 (2)                        |

| 15         | 10101 <sup>12</sup>               | 27 <sup>3</sup> –33 <sup>5</sup>                                       | 68–83                                              | 272–332                        | 27 <sup>3</sup> –34 <sup>5</sup>                                       | 68–85                                              | 272–340                        | 2.5 (2)                        | 4 (2)                          |

| 16         | 10110 <sup>12</sup>               | 25–41 <sup>5</sup>                                                     | 50-82                                              | 200–328                        | 25–43 <sup>5</sup>                                                     | 50–86                                              | 200–344                        | 2 (4)                          | 4 (2)                          |

| 17         | 10111 <sup>12</sup>               | 25–33 <sup>2</sup>                                                     | 100–132                                            | 200–264                        | 25–33 <sup>2</sup>                                                     | 100–132                                            | 200–264                        | 4 (2)                          | 2 (2)                          |

| 18         | 11000 <sup>12</sup>               | 27 <sup>3</sup> –44 <sup>5</sup>                                       | 68–110                                             | 204–330                        | 27 <sup>3</sup> –46 <sup>5</sup>                                       | 68–115                                             | 204–345                        | 2.5 (2)                        | 3 (2)                          |

| 19         | 11001 <sup>12</sup>               | 36 <sup>6</sup> –66 <sup>1</sup>                                       | 72–132                                             | 180–330                        | 36 <sup>6</sup> –66 <sup>1</sup>                                       | 72–132                                             | 180–330                        | 2 (2)                          | 2.5 (2)                        |

| 1A         | 11010 <sup>12</sup>               | 50 <sup>18</sup> –66 <sup>1</sup>                                      | 50–66                                              | 200–264                        | 50 <sup>18</sup> –66 <sup>1</sup>                                      | 50–66                                              | 200–264                        | 1 (4)                          | 4 (2)                          |

| 1B         | 11011 <sup>12</sup>               | 34 <sup>3</sup> –55 <sup>5</sup>                                       | 68–110                                             | 204–330                        | 34 <sup>3</sup> –58 <sup>5</sup>                                       | 68–116                                             | 204–348                        | 2 (2)                          | 3 (2)                          |