# **Freescale Semiconductor**

**Application Note**

AN1818 Rev. 1, 11/2004

# Software SCI Routines with the 16-Bit Timer Module

by: Brad Bierschenk MMD Applications Engineering Austin, Texas

# Introduction

Many applications that communicate to off-board devices require an asynchronous serial link. A Freescale microcontroller unit (MCU) with a serial communications interface (SCI) module can provide this communications functionality.

However, in many applications, an MCU that does not have an SCI module must be used. If asynchronous communications capability is needed, it must be provided through software control of existing modules. A bit-banged approach, as documented in HC05 MCU Software-Driven Asynchronous Serial Communication Techniques Using the MC68HC705J1A (Freescale document order number AN1240), is convenient, but requires dedicated software overhead while transmitting and receiving data.

Through the use of the 16-bit free-running counter, the HC05 and other MCU families can provide an interrupt-driven software SCI with minimal software overhead.

© Freescale Semiconductor, Inc., 2004. All rights reserved.

# **General Information**

The solution discussed here works in half-duplex mode. This means it can transmit or receive serial data, but cannot simultaneously transmit and receive. This is enough for most applications and is much easier to implement than a full-duplex solution.

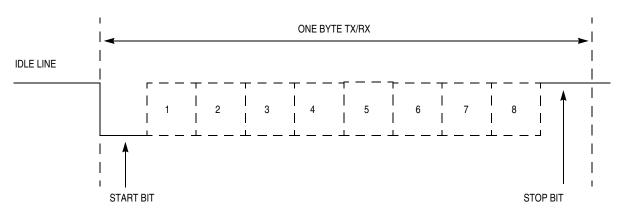

The timing in Figure 1 shows the standard non-return-to-zero (NRZ) asynchronous transmission protocol of an RS-232 serial transfer.

# Figure 1. Serial RS-232 Timing

A complete byte transfer takes 10 bit times due to the start and stop bits. The first falling edge indicates the beginning of the start bit, and thus the beginning of a byte transmission. After the start bit, data is sent in eight bits. The logic-high stop bit signals the end of the byte transmission.

A 16-bit free-running timer counter with one input capture (IC), one output compare (OC), and the associated interrupts, allows software emulation of an SCI module with only a small amount of processor overhead (see Figure 2). In addition to the timer module, one digital input pin that can be sampled using BRSET or BRCLR instructions is needed.

On some MCUs, including the MC68HC705P6A, the input capture pin can be read directly as a digital input. On other MCUs, the input capture pin also should be connected to a digital input pin to allow digital polling.

A byte variable in RAM can be used to simulate the flags of an SCI status and control register; likewise, a RAM variable can function as a data register where transmitted and received bytes are stored (see Figure 3).

#### **Receiving Serial Data**

| RX | TX | RDRF | TDRE | Х | Х | Х | Х |

|----|----|------|------|---|---|---|---|

| 7  | 6  | 5    | 4    | 3 | 2 | 1 | 0 |

## Figure 2. Simulated Status Register in RAM Variable

RX — Receive In-Progress Flag

A 1 here signifies that a receive is in progress.

TX — Transmit In-Progress Flag

A 0 here indicates a transmit is in progress.

#### RDRF — Receive Data Register Full

A 1 here indicates that a byte has been received.

# TDRE — Transmit Data Register Empty

A 1 here indicates that a byte has been transmitted.

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|----|----|----|----|----|----|----|----|

| 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

## Figure 3. Simulated Data Register in RAM Variable

## **Receiving Serial Data**

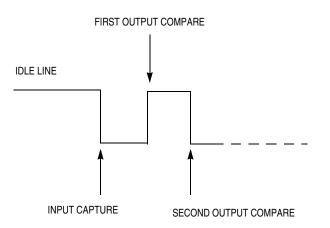

In this application, if data is not being transmitted, the input capture (IC) function of the timer is enabled. In this way, the user can wait for the start bit of an incoming transmission without any software overhead. When the start bit is received, the IC interrupt is triggered. This provides both a wakeup to start receiving and the start of a timing reference via the value in the IC registers (see Figure 4).

Figure 4. Receiving with the Timer Functions

#### Transmitting

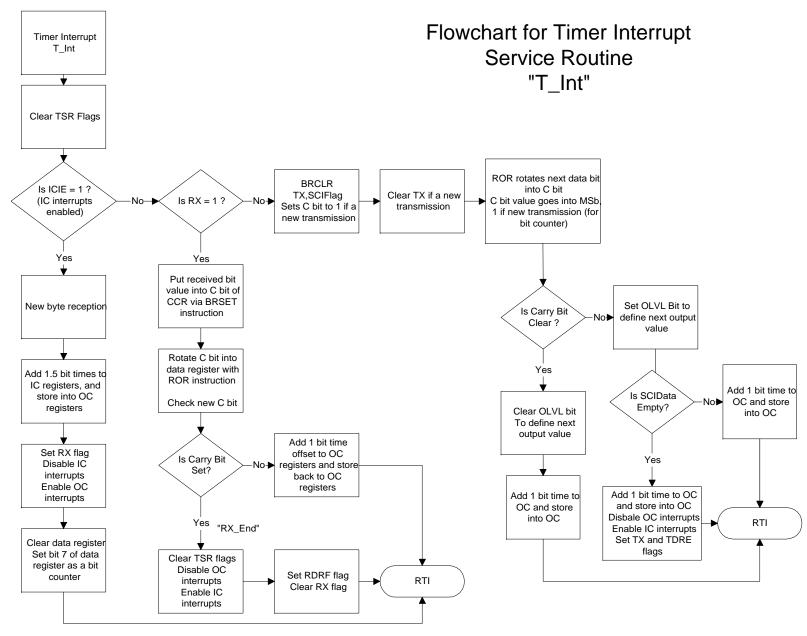

The contents of the IC registers show the time of the falling edge of the start bit. The resulting timer interrupt routine has to determine which event (IC or OC) triggered the interrupt. In the first entry, one and a half bit times are added to the content of the capture register. The result is stored in the OC registers and interrupts are switched from the IC to the OC. The delay of one and a half bit times will cause an output compare event approximately in the middle of the first data bits reception.

Next, the data register is cleared, and bit 7 of the data register is set. This most significant bit (MSB) of the data variable acts as a bit counter. In the next output compare, the data at the pin (either TCAP or port pin) is sampled using a BRSET instruction. This brings the value of the data received into the carry bit of the condition code register (CCR). The rotate right through carry (ROR) instruction rotates the new data bit into the data register. It is rotated into the data register and one bit time is added to the OC register.

Because the data register was cleared prior to reception, and bit 7 was set, a 0 is always rotated into the carry bit until the eighth data bit is received. The setting of the carry bit after a rotate indicates that the eighth bit has been received. When this happens, the receive data full flag is set and the interrupt capability is switched back to input capture.

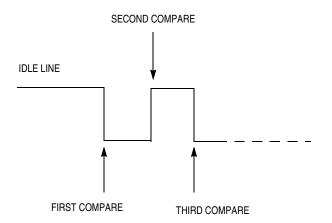

# Transmitting

To transmit a byte, a mechanism is needed that can trigger at a given rate and allow changing of the bit level of an output. The OC function of the 16-bit timer module allows this (see Figure 5).

The routine SCISend in the software listing provides the transmit function. Before calling SCISend, the user places the byte to be transmitted into the SCIData location. Transmission starts by setting the I bit in the condition code register (CCR) to ensure proper timing, and reading the contents of the free-running counter. An offset is then added to that value, and the result is stored into the output compare registers. This defines the time the transmission will begin. The OLVL bit is set to 0 to produce the required falling edge for the start bit at the time of the next compare. The OC interrupt is enabled, and the user can now wait for the predefined OC event to drive the TCMP pin low to start the transmission.

When running through the timer interrupt service routine, distinguishing between an IC or an OC event (they both use the same interrupt) is a must. In this way, the user can arbitrate between the beginning of a byte reception and a reception/transmission in progress.

Just as with the receiving code, the transmission of a byte uses the propagation of a logic 1 from the carry to provide a bit counter. When all bits have been transmitted, a logic 1 will be rotated into the carry bit, and OC can be set up to transmit the logic high stop bit.

# **Baud Rates**

To change the baud rate, adjust the values of BITHI and BITLO to represent one bit time at the frequency of the timer module. Likewise, BIT1HI and BIT1LO should be changed to represent one and a half bit times at the frequency of the timer module.

The internal frequency of operation and the latency of the timer interrupt define the maximum baud rate that can be achieved. The rate of the timer interrupts should not be programmed to be faster than the latency of the interrupt service routine. If this happens, one might miss OC or IC events (see Figure 6).

The frequency of the 16-bit timer counter is four times slower than the internal operating frequency. The formula to determine what number to add to the timer value to cause a specific delay is:

$f_{Bus} \div [(baud \ rate) \times 4]$

For example:

| Internal  | Timer     | 9600   | 4800   | 2400   | 1200 |

|-----------|-----------|--------|--------|--------|------|

| Frequency | Frequency | Baud   | Baud   | Baud   | Baud |

| 2 MHz     | 500 kHz   | \$0034 | \$0068 | \$00D0 |      |

ი

Figure 6. Flowchart for Timer Interrupt Service

The code listing that follows illustrates reading and writing serial data through the timer interface. This simple software loop waits for data to be received and echoes the value back to the sending device.

#### **Code Listing**

```

*

SWSCI.ASM

*

*

A software-driven SCI simulation for the 705P6A MCU,

*

using the timer's input capture and output compare

*

functions.

*

Brad Bierschenk, MMD Applications Engineering

*

Oak Hill, Austin, Texas

08/06/99

NOTES:

a) The "SCI" subroutine sets up the transmit routine

so to send a byte, you have to load it into SCI data

variable, and JSR to SCI

*

b) The "simulated" SCI status and data register are held

in RAM, and the "simulated" SCI interrupt is really the

timer interrupt.

*

c) Limitation is half-duplex only.

d) To transmit, use the SCI routine. But you will not

*

be able to receive until the transmission is complete.

*

e) This requires a part that can digitally read its

TCAP pin (P6A). Otherwise, a separate input pin should

*

be tied to the TCAP pin for polling.

4) The P6A REQUIRES a pullup on TCAP to \ensuremath{\text{V}_{\text{DD}}} for this

*

*

application.

*

_____

*

Needed P6A bits and bytes

------

_____

RAMSPACE

EQU

$0050

$0100

ROMSPACE

EQU

EQU

$01

PORTB

PORTC

EQU

$02

PORTD

EQU

$03

DDRB

EQU

$05

DDRC

EQU

$06

DDRD

EQU

$07

TCR

EQU

$12

TSR

EQU

$13

IC1HI

EQU

$14

IC1L0

EQU

$15

OC1HI

EQU

$16

OC1LO

EQU

$17

TCNTHI

EQU

$18

TCNTLO

EQU

$19

OLVL

EQU

0

```

| IEDG<br>OCF<br>ICF<br>OCIE<br>ICIE              | EQU<br>EQU<br>EQU<br>EQU<br>EQU            | 1<br>6<br>7<br>6<br>7                       |                                                                                             |  |  |

|-------------------------------------------------|--------------------------------------------|---------------------------------------------|---------------------------------------------------------------------------------------------|--|--|

| * Software<br>TDRE<br>RDRF<br>TX<br>RX          | e SCI e<br>EQU<br>EQU<br>EQU<br>EQU<br>EQU | quates for RAM va<br>4<br>5<br>6<br>7       | riable SCIFlag                                                                              |  |  |

| ;baud rate                                      | e.                                         |                                             | elay for 1.5 bit times at given                                                             |  |  |

| ;9600<br>BITHI<br>BITLO<br>BIT1HI<br>BIT1LO     | baud<br>EQU<br>EQU<br>EQU<br>EQU<br>EQU    | \$00<br>\$34                                |                                                                                             |  |  |

| ;4800<br>;BITHI<br>;BITLO<br>;BIT1HI<br>;BIT1LO | baud<br>EQU<br>EQU<br>EQU<br>EQU           | \$00<br>\$68<br>\$00<br>\$9C                |                                                                                             |  |  |

| ;2400<br>;BITHI<br>;BITLO<br>;BIT1HI<br>;BIT1LO | baud<br>EQU<br>EQU<br>EQU<br>EQU           | \$00<br>\$D0<br>\$01<br>\$38                |                                                                                             |  |  |

| ;1200<br>;BITHI<br>;BITLO<br>;BIT1HI<br>;BIT1LO | baud<br>EQU<br>EQU<br>EQU<br>EQU           | \$01<br>\$A0<br>\$02<br>\$70                |                                                                                             |  |  |

| *<br>* RAM Vari                                 |                                            |                                             |                                                                                             |  |  |

| SCIFlag<br>SCIData                              | ORG<br>RMB<br>RMB                          | RAMSPACE<br>1<br>1                          | ;Simulated Status register<br>;Simulated Data register                                      |  |  |

| * Start of program code<br>*                    |                                            |                                             |                                                                                             |  |  |

| Begin                                           | ORG<br>LDA<br>STA<br>LDA<br>STA            | ROMSPACE<br>#\$10<br>PORTB<br>#\$F7<br>DDRB | ;Set OC pin to high ==> idle line                                                           |  |  |

|                                                 | CLR<br>CLR<br>LDA<br>LDA<br>LDA            | SCIFlag<br>SCIData<br>TSR<br>IC1LO<br>OC1LO | ;Clear SCI status register<br>;Clear SCI data register<br>;Clear possibly set OC & IC flags |  |  |

;Initialize timer system to OCLevel High (idle) ;IC falling edge (detect start bit), disable OCI ;enable ICI (SCI ready to receive) #\$81 LDA TCR STA BSET TX, SCIFlag ;Clear first-entry-to-transmit ;flag CLI ;Globally enable interrupts Main BRCLR RDRF, SCIFlag, \* ;Wait for a byte to be received ;Allow ~2 bit times for rest of last bit and stop bit ;~210 µs ~= 55 cycles #\$09 ;2 LDA DelayLoop DECA ;3 ;3 BNE DelayLoop ;Echo back the received byte... BCLR RDRF, SCIFlag JSR SCISend ;Wait for next received byte BRA Main \_\_\_\_\_ \_\_\_\_\_ SCISend sets up the timer module to transmit a byte. Uses the OC function to transmit data. Can't receive while transmitting (limitation is half-duplex) \_\_\_\_\_ SCISend SEI ;Disable interrupts to ensure ;timing LDX TCNTHI ;Read current timer value LDA TCNTLO ADD #\$15 ;Add offset STA OC1LO ;Store new value TXA ADC #\$00 ;Accommodate carry if needed STA OC1HI LDA TSR LDA OC1LO STA OC1LO ;Generate start bit by setting OLVL LDA #%01000000 STA TCR ; bit to falling edge, disable ICI, ;enable OCI CLI ;Globally enable interrupts again RTS \_\_\_\_\_ \* T\_Int is the timer interrupt service routine. \* Must arbitrate whether an IC or OC caused the interrupt, to determine whether receiving or transmitting a byte. (Timer interrupt ~= SCI Interrupt) \* OC event is either 1) byte transmitting or 2) sampling byte being received. IC event is the start bit of a received byte \_\_\_\_\_ \_\_\_\_\_ LDA T\_Int TSR ;Clear any flags

; If IC interrupts are enabled, we are in receive mode ;and have received start bit on TCAP BRSET ICIE, TCR, Receive ; If OC interrupts are enabled, we are either ;transmitting a byte, or are sampling a byte coming in BRSET RX,SCIFlag,RX1 ;Is SCI receiving? ; Is this a byte transmitalready-in-progress? ;The BRCLR instruction sets the carry bit to the value ; of the bit being tested. TX,SCIFlag,TX1 BRCLR ;New transmission ;Carry bit gets set, clear the flag to indicate ;transmit-in-progress. ;C = 1 will be rotated into bit 7 of data register ; for use as a bit counter. TX,SCIFlag BCLR ;Transmitting TX1 ROR SCIData ;Shift next data bit into carry BCC TX2 ; If low, go to TX2 ; If high, next OC level to high BSET OLVL,TCR ; If Data register is zero, and Carry is set, we have ; just rotated out the last bit, and need to send the ;stop bit. BEQ TX\_End ; If stop bit, go to TX\_End ;Otherwise, add bit time to OC LDA OC1LO ADD #BITLO ; for the next bit TAX LDA OC1HI ADC #BITHI STA OC1HI STX OC1LO RTI TX2 BCLR OLVL, TCR ;Carry was low means next data bit ;low ;so next OC level to low ;Add bit time to OC LDA OC1LO ADD #BITLO TAX OC1HI LDA ADC #BITHI OC1HI STA STX OC1LO RTI ;Add last bit time to OC for the TX\_End LDA OC1LO ;stop bit #BITLO ADD TAX LDA OC1HI ADC **#BITHI** OC1HI STA STX OC1LO LDA TSR LDA IC1L0 LDA #\$81 ;Disable OCI, enable ICI STA TCR

|                    | ;and set ;<br>;the TDRE<br>;is not co                                             | bit is set, t                                                                                                                                                                                                        | NOTE that even though<br>he TX of the data byte<br>the rest of the last bit                                                                                                                                  |  |  |  |

|--------------------|-----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Receive            | LDA<br>ADD<br>TAX<br>LDA<br>ADC<br>STA<br>LDA<br>STX<br>BSET<br>LDA<br>STA<br>LDA | IC1LO<br>#BIT1LO<br>IC1HI<br>#BIT1HI<br>OC1HI<br>TSR<br>OC1LO<br>RX,SCIF1ag<br>#\$41<br>TCR<br>#\$80                                                                                                                 | <pre>;Start bit has been received<br/>;add 1+1/2 bit times<br/>;to OC for the first bit sampling<br/>;Set receive-in-progress flag<br/>;disable ICI, enable OCI<br/>;Clear data register, set bit 7 as</pre> |  |  |  |

|                    | STA<br>RTI                                                                        | SCIData                                                                                                                                                                                                              | ;a bit counter                                                                                                                                                                                               |  |  |  |

| RX1<br>RX2         | BRSET<br>ROR<br>BCS<br>LDA<br>ADD<br>TAX<br>LDA<br>ADC<br>STA<br>STX<br>RTI       | 7, PORTD, RX2<br>SCIData<br>RX_End<br>OC1LO<br>#BITLO<br>OC1HI<br>#BITHI<br>OC1HI<br>OC1HI<br>OC1LO                                                                                                                  | ;get bit level from TCAP pin and<br>;put it into data variable<br>;End if it is the last bit<br>;If not add bit time<br>;for next sample                                                                     |  |  |  |

| RX_End             | LDA                                                                               | TSR                                                                                                                                                                                                                  | ;Byte received, clear possibly set<br>;IC flag                                                                                                                                                               |  |  |  |

|                    | ;NOTE that<br>;the rest<br>;still on<br>BSET                                      | LDA #\$81 ;Disable OCI, enable ICI<br>STA TCR<br>;Set receive register full flag in RAM<br>;NOTE that even so, the RX byte is not complete<br>;the rest of the data bit and the stop bit are<br>;still on their way. |                                                                                                                                                                                                              |  |  |  |

|                    | BCLR<br>RTI                                                                       | RX,SCIFlag                                                                                                                                                                                                           | ;Clear receive-in-progress flag                                                                                                                                                                              |  |  |  |

| *<br>* P6A Ve<br>* | ctor defin:                                                                       | itions                                                                                                                                                                                                               |                                                                                                                                                                                                              |  |  |  |

|                    | ORG<br>FDB                                                                        | \$1FF8<br>T_Int                                                                                                                                                                                                      | ;Timer vector                                                                                                                                                                                                |  |  |  |

|                    | ORG<br>FDB                                                                        | \$1FFE<br>Begin                                                                                                                                                                                                      | ;Reset vector                                                                                                                                                                                                |  |  |  |

#### How to Reach Us:

Home Page: www.freescale.com

E-mail: support@freescale.com

#### **USA/Europe or Locations Not Listed:**

Freescale Semiconductor Technical Information Center, CH370 1300 N. Alma School Road Chandler, Arizona 85224 +1-800-521-6274 or +1-480-768-2130 support@freescale.com

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) support@freescale.com

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor Hong Kong Ltd. Technical Information Center 2 Dai King Street Tai Po Industrial Estate Tai Po, N.T., Hong Kong +800 2666 8080 support.asia@freescale.com

#### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center P.O. Box 5405 Denver, Colorado 80217 1-800-441-2447 or 303-675-2140 Fax: 303-675-2150 LDCForFreescaleSemiconductor@hibbertgroup.com Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © Freescale Semiconductor, Inc. 2004. All rights reserved.

AN1818 Rev. 1, 11/2004