Freescale Semiconductor

Semiconductor Products Sector Application Note **AN1739**

# A/D Conversion Software for the MC68HC05JJ/JP Series Microcontrollers

By Mark L. Shaw Member, Technical Staff Phoenix, Arizona

#### Introduction

The MC68HC05JJ/JP series of microcontrollers (MCUs) can be used to build simple single slope analog-to-digital (A/D) converters of up to 12-bits of measurement. The intent of this application note is to present a set of software examples for the MC68HC05JJ/JP using each of the four modes of operation. Additional information on the analog subsystem of these MCUs can be found in *Applications Using the Analog Subsystem on MC68HC05JJ/JP Series Microcontrollers*, Freescale

© Freescale Semiconductor, Inc., 2004. All rights reserved.

# **Analog-to-Digital Conversion**

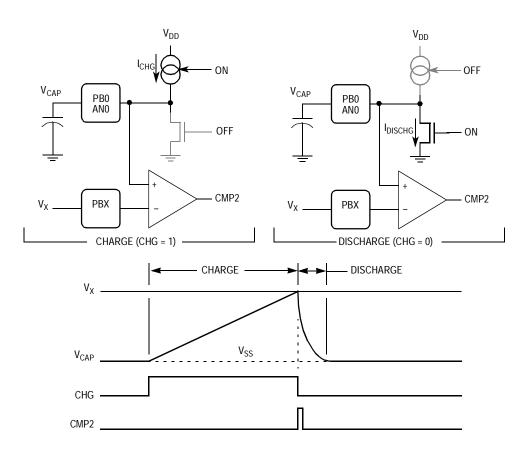

Analog-to-digital conversion can be accomplished using the JJ/JP-series by allowing the current source to charge up (ramp) an integration capacitor connected to PB0 and use comparator 2 to detect the time when the ramp voltage crosses the unknown voltage being measured as shown in **Figure 1**.

Figure 1. Single Slope A/D Convertor

Application Note Analog-to-Digital Conversion

# Performance Calculations

Fundamental to the single slope A/D conversion technique is the following equation relating time to voltage dependent on the external ramping capacitor and its charging current:

$$t_{CHG} = \frac{C_{EXT} \times V_{x}}{I_{CHG}}$$

where:

t<sub>CHG</sub> = Charge time (seconds)

$V_X$  = Voltage to reach (volts)

$C_{EXT}$  = External ramp capacitor ( $\mu F$ )

$I_{CHG}$  = Charge current ( $\mu$ A)

From this basic equation the time can be translated into a number of counts at a given frequency:

$$t_{FS} = \frac{P \times N_{FS}}{f_{OSC}} = \frac{C_{EXT} \times V_{FS}}{I_{CHG}}$$

where:

t<sub>FS</sub> = Full scale charge time (seconds)

$N_{FS}$  = Full scale counts (counts)

P = Prescaler (counts out/counts in)

$f_{OSC}$  = Oscillator frequency (Hz)

$C_{EXT}$  = External ramp capacitor ( $\mu$ F)

#### **Application Note**

# Step-By-Step A/D Conversion

After selecting the right components, the single slope A/D can be operated as a series of simple software controlled steps:

- 1. Initialize the analog subsystem to the desired configuration.

- Discharge the internal sample capacitor and channel select bus.

- 3. Select a signal source.

- 4. Start charging the ramp capacitor (set CHG bit in ACR)

- 5. Keep track of time while waiting for comparator 2 output to go high.

- 6. Capture time when comparator 2 output goes high.

- 7. Start discharging the ramp capacitor (clear CHG bit in ACR)

- 8. Calculate the charge time.

- 9. Compare the charge time to that for a reference signal.

- 10. When the ramp capacitor is fully discharged, go back to step 3.

#### **Analog Subsystem Registers**

The analog subsystem is structured around several basic components: a pair of voltage comparators and a constant current source which are controlled and monitored by the analog MUX register (AMUX) at \$0003, the analog control register (ACR) at \$001D, and the analog status register (ASR) at \$001E. All the registers relating to the analog subsystem are shown in Figure 2.

Application Note Analog Subsystem Registers

| Addr.  | Register                    | R/W             | Bit 7 | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |

|--------|-----------------------------|-----------------|-------|-------|-------|-------|-------|-------|-------|-------|

| \$0001 | Port B Data, PORTB          | Read:<br>Write: | PB7   | PB6   | PB5   | PB4   | PB3   | PB2   | PB1   | PB0   |

| \$0003 | Analog MUX Register, AMUX   | Read:<br>Write: | HOLD  | DHOLD | INV   | VREF  | MUX4  | MUX3  | MUX2  | MUX1  |

| \$0005 | Port B Data Direction, DDRB | Read:<br>Write: | DDRB7 | DDRB6 | DDRB5 | DDRB4 | DDRB3 | DDRB2 | DDRB1 | DDRB0 |

| 40044  | Port B Pulldown, PDRB       | Read:           |       |       |       |       |       |       |       |       |

| \$0011 |                             | Write:          | PDIB7 | PDIB6 | PDIB5 | PDIB4 | PDIB3 | PDIB2 | PDIB1 | PDIB0 |

| \$0012 | Timer Control, TCR          | Read:<br>Write: | ICIE  | OCIE  | TOIE  | 0     | 0     | 0     | IEDG  | OLVL  |

| \$0013 | Timer Status, TSR           | Read:<br>Write: | ICF   | OCF   | TOF   | 0     | 0     | 0     | 0     | 0     |

| \$0014 | Input Capture MSB, ICRH     | Read:<br>Write: | BIT15 | 14    | 13    | 12    | 11    | 10    | 9     | BIT8  |

| \$0015 | Input Capture LSB, ICRL     | Read:<br>Write: | BIT7  | 6     | 5     | 4     | 3     | 2     | 1     | BIT0  |

| \$0016 | Output Compare MSB, OCRH    | Read:<br>Write: | BIT15 | 14    | 13    | 12    | 11    | 10    | 9     | BIT8  |

# Pitfalls in Using Single Slope A/D

Single slope A/D conversion has six unwanted faults near the limits of its input voltage range, in the signal noise, and timing with respect to the software. The user should check their application to see if any of these faults are possible. These faults are described briefly here with further detail available from *Applications Using the Analog Subsystem on MC68HC05JJ/JP Series Microcontrollers*, Freescale document order number AN1740/D.

# Infinite Conversion Time

When the unknown input signal is above the common-mode range of comparator 2 the integration ramp on the PB0 pin can never reach the level to trip comparator 2 and set the CPF2 flag.

# Disabled Conversion A/D Fault

The CPF2 flag bit is set by a rising transition on the output of comparator 2. If the output of comparator 2 cannot return to the low state this flag bit cannot get set indefinitely. This occurs if the PB0 pin cannot be discharged below the level on the negative input to comparator 2.

# Extra Conversion A/D Fault

When the PB0 pin has been discharged and the input voltage is near  $V_{SS}$  the presence of noise on either the measured input voltage or the PB0 pin can cause comparator 2 to switch and the CPF2 flag bit will be set even though there is no conversion ramp in progress.

# Early Conversion A/D Fault

When the conversion time is long there exists the possibility for noise on either the input signal or the PB0 ramping voltage to cause comparator 2 to trip the CPF2 flag earlier than would normally have occurred.

# Conversion Overlap A/D Fault

When the conversion time becomes too long in mode 0 or 1 the software is still looping on the conversion and no subsequent events can occur. But in mode 2 or 3 a very long conversion could overlap the next TOF or OCF which is trying to start another conversion. The net result will be

AN1739

Application Note Manual A/D Conversions (Modes 0 and 1)

that an ICF for the first conversion may appear associated with the start of the second conversion. This fault is only associated with mode 2 or 3.

# Conversion Masking A/D Fault

In mode 0 or 1 the software handles all the events in an established subsequence such that simultaneous events do not happen. But in mode 2 or 3 an unwanted conversion fault may make an ICF occur near the same time as the TOF or OCF which is trying to start another conversion. Such an unwanted ICF just before the TOF cannot be discerned from a true ICF that would occur if the input voltage were near  $V_{SS}$ . This fault is only associated with mode 2 or 3.

### Manual A/D Conversions (Modes 0 and 1)

Mode 0 or 1 conversions are completely under the control of the software and therefore are slow compared to hardware timing. All events are therefore predictable and occur in a known sequence.

The main limitation of modes 0 and 1 is that the timing will be slower either due to software timing loops or slower accesses to the 16-bit timer or multifunction timer. Therefore, modes 0 or 1 are usually limited to 8-bit conversions unless extremely long conversion times can be tolerated in the application.

#### **Application Note**

# Timing via Timer Reads

Timing of the conversion can be done by reading the state of the 16-bit timer or the multifunction timer. The software must account for the delays in reading these registers and the asynchronous clocking of these timers with respect to the instruction cycles. These sources of timing "jitter" will degrade the accuracy of the readings.

# Analog Interrupt Timing

The conversion can be timed with a combination of software start of the charging ramp and an analog interrupt which reads the 16-bit timer or multifunction timer. This mode of operation will allow other tasks to be performed while the conversion is in progress, which is especially useful for very long conversions. However, the accuracy of the analog interrupt being able to capture the ending time means that all other interrupts may not be active until after the conversion is complete.

Also, once the analog interrupt is entered, the time that is read must be corrected for the minimum interrupt latency time to get into the analog interrupt service routine and read the timer state. This latency, and therefore the accuracy of the time, will be affected by the variation in cycle times of all instruction types used in the particular application software. Avoiding long cycle time instructions such as JSR, SWI, MUL, and some indexed addressing modes can reduce this variation from 9 to 3 bus cycles.

# **Automated A/D Conversions (Modes 2 and 3)**

Mode 2 and 3 conversions are mostly under the control of the 16-bit timer, but need occasional maintenance to keep flags cleared and transfer input capture times to RAM for use by other routines. Due to the more accurate start and stop timing and high possible bit counts, mode 2 or 3 conversions are best for conversions of more than 8 bits.

Mode 2 or 3 conversions use the timer overflow flag (TOF) or the output compare flag (OCF) and the input capture flag (ICF) of the 16-bit timer to control the charging of the integration capacitor connected to PB0.

AN1739

Application Note Automated A/D Conversions (Modes 2 and 3)

When using these timer flags the designer should be aware of the following behaviors:

- The TOF flag bit is set whenever the 16-bit timer counter overflows from \$FFFF to \$0000 regardless of whether or not the timer overflow interrupt is enabled (TOIE bit set in TCR).

- a. Once set, the TOF bit must be reset by the proper software sequence of reading the TSR, then the TMRL.

- b. Since the timer starts with \$FFFC after a reset of the MCU a TOF will occur almost immediately following a reset.

- The OCF flag bit is set whenever the 16-bit timer counter matches

the count stored into the output compare registers <u>regardless of</u>

whether or not the timer output compare interrupt is enabled

(OCIE bit set in TCR).

- a. Once set, the OCF bit must be reset by the proper software sequence of reading the TSR, then the OCRL.

- b. Once set, the OCF will lock out any future compares until the OCF flag bit is cleared.

- An OCF can occur at any time following a reset since the contents of the OCRL and OCRH are unaffected by a reset.

- 3. The ICF flag bit is set whenever an input capture is received by the 16-bit timer <u>regardless of whether or not the timer input capture interrupt is enabled</u> (ICIE bit set in TCR).

- a. Once set, the ICF bit must be reset by the proper software sequence of reading the TSR, then the ICRL.

- b. Once set, the ICF will lock out any future input captures until the ICF flag bit is cleared.

- c. In the control of the analog current source the ICF flag overrides the TOF or OCF flags. If an TOF or OCF is present when the ICF is cleared, the charging of the PB0 pin will begin immediately.

- d. The ICF can be triggered by a positive or negative going edge depending on the state of the IEDG bit in the TCR.

- e. The trigger source for the ICF can be either the signal on PB3 or the output of voltage comparator 2 dependent on the state of the ICEN bit in the ACR.

The most important considerations in using the automated modes 2 or 3 is that the TOF, OCF, and ICF flags can get set without any enabling control; and that following a reset they can get set <u>before</u> the software is ready to use them. This means that modes 2 or 3 can operate as either interrupt driven or free-running software. The following examples for mode 2 or 3 A/D conversions take into account these factors.

# Use of Conversion Flags

It is highly recommended that modes 2 and 3 use conversion status flags such as EOC (for end-of-conversion) and CIP (for conversion-Inprogress). These flags allow the timer interrupt service routine to determine if the conversions are executing properly or a fault has occurred. These flags should be contained in an assigned RAM location. Avoid using the CHG bit in the ACR or the CPF2 or CMP2 bits in the ASR for these purposes since they can be set automatically by hardware events that are not under the user's direct software control.

### Value of the Captured Times

The biggest advantage of modes 2 and 3 is that the start time of the conversion is clearly defined by the TOF of OCF timer state and the end of conversion is captured precisely by the ICF. Therefore, the software sequence and cycle times are not critical to the timing accuracy. The only concern should be that the ICF is combined with the correct TOF of OCF that started the conversion ramp. Also the software must access the proper values and clear the flags before the next conversion is to begin. This allows more latitude in defining error checks than is possible with modes 0 or 1 which are sensitive to software cycle timing.

# Correct Mode Initialization

The initialization of either mode 2 or 3 must be done at the proper time since the TOF or OCF flags may become set before the mode can be established. If the TOF is already set and mode 2 is initiated, then the charge ramp will begin immediately without regard for when the TOF actually occurred. Similarly, the OCF could be set before mode 3 is initialized. It is important that the TOF and ICF flags be clear before the mode 2 is established; or that the OCF and ICF flags be clear before the mode 3 is established. The best way to accomplish this is to wait for the first TOF in mode 2 or first OCF in mode 3, then clear all flags and finally set the ATD1 and ATD2 bits as required.

AN1739

Application Note A/D Examples

### A/D Examples

The following A/D conversion examples all use the include files from Appendix B — Software Include File for variables and the subroutines in Appendix C — General Subroutines Used in Examples.

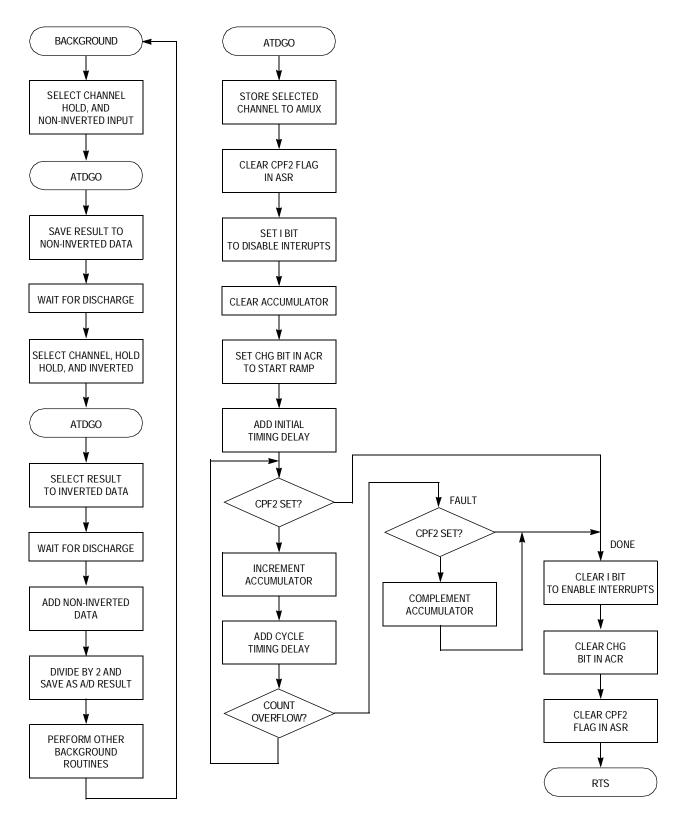

#### A/D #1 — Mode 0

In this A/D example the device is placed in mode 0 and the current source is controlled by software to charge the PB0 pin while keeping a count in software. Results are stored as an 8-bit result in RAM. Code is added to test for any excessively long conversion times in case the input is undefined, out of the common range of the comparator, or at or below the  $V_{SS}$  potential. This A/D conversion example will follow the basic flow chart given in **Figure 3** and the listing given in **Software Listing 1** — **Mode 0** A/D **Conversions**.

The A/D cycle time is about 4.4 ms between maximum length conversions for a 0.1- $\mu$ F capacitor and 2-MHz oscillator. Discharge time is about 0.8 ms. Full scale value of \$FF occurs with an input voltage of about 3.5 volts for a 5-volt supply to  $V_{DD}$ .

At first glance this may look like a lot of code to simply set the CHG bit and count time until the CMP2 bit goes high. But only 29 bytes do the actual A/D conversion subroutine. The conversion loop takes 14 CPU bus cycles which is equal to a prescaler of 28 with respect to the oscillator frequency, f<sub>OSC</sub>. The A/D conversion software also handles the possible faults described earlier. The software example provides for ideal sampling, where it is desirable to have the first test of the comparator output occur at 1/2 of the recurring cycle time or "bit time" of the conversion loop. Thus, the start of the charge ramp occurs on the 4th bus cycle of the BSET instruction and the first read of the comparator output occurs on the 3rd bus cycle of the BRSET instruction. The BRN instruction gives a three cycle delay for a total time from ramp start to first read of 7 bus cycles.

### **Application Note**

The A/D conversion is implemented as a subroutine which can be called as needed by the background routines. This allows the background routine to select the desired channel and use the conversion results as needed.

NOTE:

It should be noted that some assemblers do not support the BRN instruction. In this case, insert a FDB \$2100 which is the opcode for the BRN instruction (\$21) plus a dummy offset (\$00).

In mode 0 careful attention to the timing of read or write cycles should be done when controlling signals to the comparators or reading their output states. The information in *Instruction Cycle Timing of MC68HC05JJ/JP Series Microcontrollers*, Freescale document order number AN1738/D, indicates the time within the instruction where it actually reads or writes data.

Application Note

A/D #1 — Mode 0

Figure 3. A/D #1 Mode 0 Flow Chart

AN1739

# Software Listing 1 — Mode 0 A/D Conversions

|                              | includ                                                             | de jp7incl.asm                                                                                                                 |                                                                                                                                                                                                                                           |

|------------------------------|--------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                              | ALIZE DI                                                           |                                                                                                                                | ***********                                                                                                                                                                                                                               |

| BEGIN                        | org                                                                | \$0800                                                                                                                         | Redundant reset of                                                                                                                                                                                                                        |

|                              | sei                                                                |                                                                                                                                | <pre>; stack pointer. ;Redundant set of ; interrupt mask bit, I.</pre>                                                                                                                                                                    |

|                              | jsr                                                                | INITO                                                                                                                          | ;Initialize analog subsyste;Set up oscillator                                                                                                                                                                                             |

|                              | cli                                                                |                                                                                                                                | Enable interrupts, if used                                                                                                                                                                                                                |

| * MAKE<br>* Ready            | A/D COM                                                            | NVERSIONS BY MON                                                                                                               | **************************************                                                                                                                                                                                                    |

| * MAKE<br>* Ready            | A/D COM<br>y to mon<br>nel for<br>lda                              | NVERSIONS BY MON<br>nitor comparator<br>comparator 2.<br>#%10000001                                                            | outputs and selected input  ;Select HOLD and MUX1                                                                                                                                                                                         |

| * MAKE<br>* Ready<br>* chann | A/D COM<br>y to mornel for<br>lda<br>jsr<br>sta                    | NVERSIONS BY MON<br>nitor comparator<br>comparator 2.                                                                          | SITORING COMPARATOR 2 OUTPUT outputs and selected input  ;Select HOLD and MUX1 ;Go fetch A/D conversion ; count in accumulator  ;Wait 720 usec for discharg ; delay of 6 msec/uF. Dela                                                    |

| * MAKE<br>* Ready<br>* chann | A/D COM<br>y to mornel for<br>lda<br>jsr<br>sta                    | NVERSIONS BY MON<br>nitor comparator<br>comparator 2.<br>#%10000001<br>ATDGO<br>DATA<br>#\$76                                  | ITORING COMPARATOR 2 OUTPUT outputs and selected input  ;Select HOLD and MUX1 ;Go fetch A/D conversion ; count in accumulator ;Wait 720 usec for discharg                                                                                 |

| * MAKE<br>* Ready<br>* chann | A/D COM<br>y to mornel for<br>lda<br>jsr<br>sta<br>ldx<br>jsr      | WVERSIONS BY MON<br>nitor comparator<br>comparator 2.<br>#%10000001<br>ATDGO<br>DATA<br>#\$76<br>TDELAY                        | ;Select HOLD and MUX1 ;Go fetch A/D conversion ; count in accumulator ;Wait 720 usec for discharg ; delay of 6 msec/uF. Dela ; not required if backgroun ; software time long enough ;Select HOLD, INV, and MUX1                          |

| * MAKE<br>* Ready<br>* chann | A/D COM<br>y to mornel for<br>lda<br>jsr<br>sta<br>ldx<br>jsr      | WVERSIONS BY MON<br>nitor comparator<br>comparator 2.<br>#%10000001<br>ATDGO<br>DATA<br>#\$76<br>TDELAY                        | ;Select HOLD and MUX1 ;Go fetch A/D conversion ; count in accumulator ;Wait 720 usec for discharg ; delay of 6 msec/uF. Dela ; not required if backgroun ; software time long enough                                                      |

| * MAKE<br>* Ready<br>* chann | A/D COM<br>y to more<br>nel for<br>lda<br>jsr<br>sta<br>ldx<br>jsr | WVERSIONS BY MON<br>nitor comparator<br>comparator 2.<br>#%10000001<br>ATDGO<br>DATA<br>#\$76<br>TDELAY<br>#%10100001<br>ATDGO | ;Select HOLD and MUX1 ;Go fetch A/D conversion ; count in accumulator ;Wait 720 usec for discharg ; delay of 6 msec/uF. Dela ; not required if backgroun ; software time long enough ;Select HOLD, INV, and MUX1 ;Go fetch A/D conversion |

Application Note Software Listing 1 — Mode 0 A/D Conversions

| add<br>rora | DATA   | ;Add in non-inverted data<br>;Rotate ACCA right and pull<br>; in carry to divide by 2 |

|-------------|--------|---------------------------------------------------------------------------------------|

| sta         | RESULT | ;Store averaged result                                                                |

| nop<br>nop  |        | ;Insert other uses of the ; data or other background ; processes here                 |

| bra         | BLOOP  | Restart background loop                                                               |

\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*

| *     |            |               |                                                                                                                                                                                                            |

|-------|------------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ATDGO | sta        | AMUX          | Connect channel selections; to AMUX                                                                                                                                                                        |

|       | bset       | CPFR2,ASR     | ;Set CPFR2 to clear CPF2; flag, if set.                                                                                                                                                                    |

|       | sei        |               | <pre>;Temporarily hold off ; interrupts</pre>                                                                                                                                                              |

|       | clra       |               | <pre>;Clear accumulator count ; to reset conversion count</pre>                                                                                                                                            |

|       | bset       | CHG, ACR      | ;Fire off current source<br>; ramp. Actual write to CHG<br>; occurs one cycle before<br>; next opcode is fetched.                                                                                          |

|       | brn        | *             | ;Add 3 cycle delay, using ; BRN with dummy branch ; to same instruction.                                                                                                                                   |

| ATDLP | brset      | CPF2,ASR,DONE | <pre>;Test state of comp 2 flag ; at 1/2 of the software ; counter's bit time. ; Carry remains clear if ; CPF2 tests as being clear.</pre>                                                                 |

|       | add        | #\$01         | ;Increment ACCA. Carry is<br>; cleared unless there is<br>; a carry from the add<br>; operation itself                                                                                                     |

|       | nop<br>nop |               | ;Add 4 cycle delay, using ; (2) NOP instructions                                                                                                                                                           |

|       | bcc        | ATDLP         | ;If accum. count reaches; maximum, then carry will; be set. If carry is clear; then A/D loop count should; continue, else continue on; to process fault, with; carry bit set and ACCA; left equal to \$00. |

# **Application Note**

| * Enter<br>* high | r FAULT<br>; which | suggests that the | rge cycle. That Comp 2 output was still e input may be near AVss. The ACCA should remain at \$00.                                                               |

|-------------------|--------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FAULT             | brset              | CMP2,ASR,DONE     | <pre>;Test static output of ; comparator 2 for high. ; If CMP2 is high, then ; input stuck near Vss so ; exit without changing ACCA.</pre>                      |

| CMPLO             | coma               |                   | ;Comparator 2 output was<br>; actually low; which may<br>; be input above the common<br>; mode range. Convert ACCA<br>; count result to max<br>; value of \$FF. |

| * * Compa         |                    | ? flag set.       |                                                                                                                                                                 |

| DONE              |                    |                   | ;Restore interrupt control,<br>; if used                                                                                                                        |

|                   | bclr               | CHG, ACR          | ;Turn off charge current.                                                                                                                                       |

|                   | bset               | CPFR2,ASR         | ;Set CPFR2, clears CPF2 flag.                                                                                                                                   |

|                   | rts                |                   | <pre>;Exit A/D conversion ; subroutine with conversion ; count in ACCA.</pre>                                                                                   |

| *                 | includ             | le subroutin.asm  |                                                                                                                                                                 |

| ****              | * * * * * * *      | *****             | *******                                                                                                                                                         |

| * RESE            | r and in           | TERRUPT VECTORS   |                                                                                                                                                                 |

| *                 | org<br>fdb         | \$1FFE<br>BEGIN   | Reset vector                                                                                                                                                    |

|                   | end                |                   |                                                                                                                                                                 |

Application Note A/D #2 — Mode 1

#### A/D #2 — Mode 1

This A/D example is the same as A/D #1 except that in mode 1 the CHG bit is automatically reset when the comparator output sets the CPF2 flag as shown in the flow chart in **Figure 4** and the listing in **Software Listing 2** — **Mode 1** A/D **Conversions**.

Mode 1 looks identical to the mode 0 example except for the exit method from ATDGO subroutine. But mode 1 has one tricky aspect dealing with the CHG bit. These changes are so minor that the setup subroutine (INIT1) looks very similar to mode 0 (INIT0) with the ACR initialized to \$25 instead of \$05. This sets the ATD1 bit and switches the A/D mode from 0 to 1. The software timing loop is also unchanged. But, the end of the ATDGO subroutine differs from **Software Listing 1** — **Mode 0** A/D **Conversions** with several changes given in the partial listing in **Software Listing 2** — **Mode 1** A/D **Conversions**:

- 1. The clearing of the CHG bit is omitted from the exit of the A/D subroutine in mode 1, since the CHG bit is automatically reset by hardware when the CPF2 bit becomes set.

- However the clearing of the CHG bit should be added to the FAULT routine for mode 1, since the CHG bit will not be automatically reset if the CPF2 bit never gets set. The clearing of the CHG bit must occur before the test of the CMP2 bit using a BRSET.

Therefore, it appears that the mode 1 functionality does not add any significant value over mode 0. Historically mode 1 was the result of using all of the four states of the mode selection bits, ATD1 and ATD2.

Figure 4. A/D #2 Mode 1 Flow Chart

AN1739

Application Note Software Listing 2 — Mode 1 A/D Conversions

# Software Listing 2 — Mode 1 A/D Conversions

| * MODE:  * See t  * Mark  **** | l, A/D Cotext des<br>L. Shaw | onversion <b>Partia</b><br>cription in AN17;<br>, © 1996-2001,<br>******** | **************************************                                                                                                                                                                                                 |

|--------------------------------|------------------------------|----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                |                              | ONVERSION SUBROUT                                                          | FINE                                                                                                                                                                                                                                   |

| ATDGO                          | sta                          | AMUX                                                                       | ;Connect channel selections ; to AMUX                                                                                                                                                                                                  |

|                                | bset                         | CPFR2,ASR                                                                  | ;Set CPFR2 to clear CPF2 ; flag, if set.                                                                                                                                                                                               |

|                                | sei                          |                                                                            | Temporarily hold off; interrupts                                                                                                                                                                                                       |

|                                | clra                         |                                                                            | Clear accumulator count; to reset conversion count                                                                                                                                                                                     |

|                                | bset                         | CHG, ACR                                                                   | ;Fire off current source<br>; ramp. Actual write to CHG<br>; occurs one cycle before<br>; next opcode is fetched.                                                                                                                      |

|                                | brn                          | *                                                                          | ;Add 3 cycle delay, using ; BRN with dummy branch ; to same instruction.                                                                                                                                                               |

| ATDLP                          | brset                        | CPF2,ASR,DONE                                                              | <pre>;Test state of comp 2 flag ; at 1/2 of the software ; counter's bit time. ; Carry remains clear if ; CPF2 tests as being clear.</pre>                                                                                             |

|                                | add                          | #\$01                                                                      | ;Increment ACCA. Carry is<br>; cleared unless there is<br>; a carry from the add<br>; operation itself                                                                                                                                 |

|                                | nop<br>nop                   |                                                                            | ;Add 4 cycle delay, using ; (2) NOP instructions                                                                                                                                                                                       |

|                                | bcc                          | ATDLP                                                                      | ;If accum. count reaches<br>; maximum, then carry will<br>; be set. If carry is clear<br>; then A/D loop count should<br>; continue, else continue on<br>; to process fault, with<br>; carry bit set and ACCA<br>; left equal to \$00. |

### **Application Note**

```

* Reached maximum time for charge cycle.

^{\star} Enter FAULT with assumption that Comp 2 output was still

\mbox{\ensuremath{^{\star}}} high; which suggests that the input may be near AVss.

* In which case the result in the ACCA should remain at $00.

*-----

FAULT bclr CHG, ACR

; Force the discharge of the

; ramp cap since the output

; of the comparator cannot

; trigger an automatic

; discharge.

brset

CMP2,ASR,DONE

;Test static output of

; comparator 2 for high.

; If CMP2 is high, then

; input stuck near Vss so

; exit without changing ACCA.

CMPLO

;Comparator 2 output was

coma

; actually low; which may

; be input above the common

; mode range. Convert ACCA

; count result to max

; value of $FF.

* Comparator 2 flag set.

*_____

; Restore interrupt control,

; if used. Discharge turned

; on automatically in Mode 1

; when comparator 2 output

; went high.

bset

CPFR2,ASR

;Set CPFR2, clears CPF2 flag.

;Exit A/D conversion

rts

; subroutine with conversion

; count in ACCA.

```

Application Note A/D #3 — Interrupt Driven Mode 2

#### A/D #3 — Interrupt Driven Mode 2

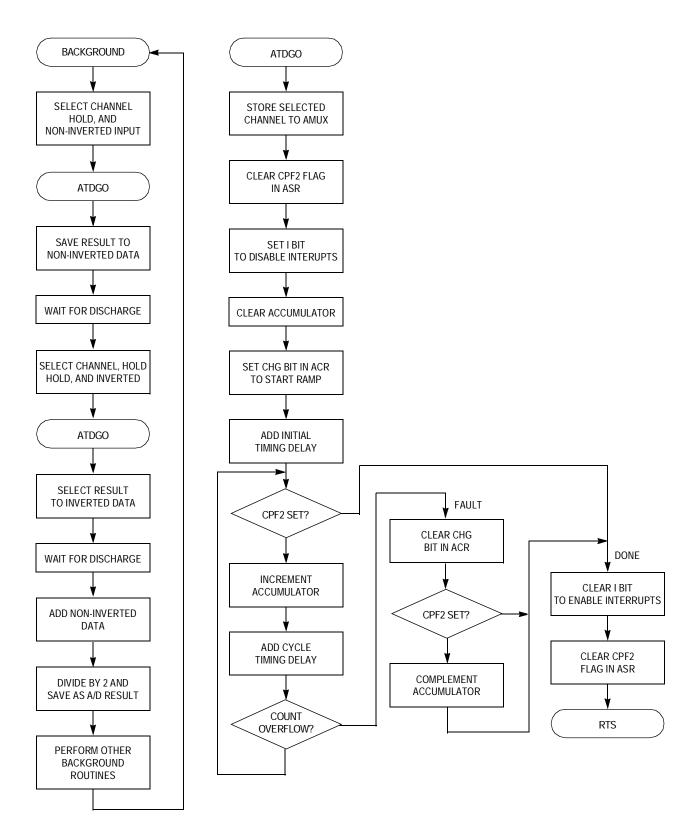

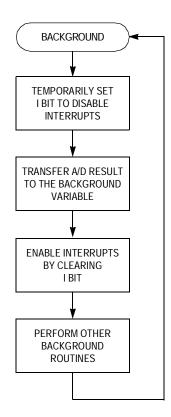

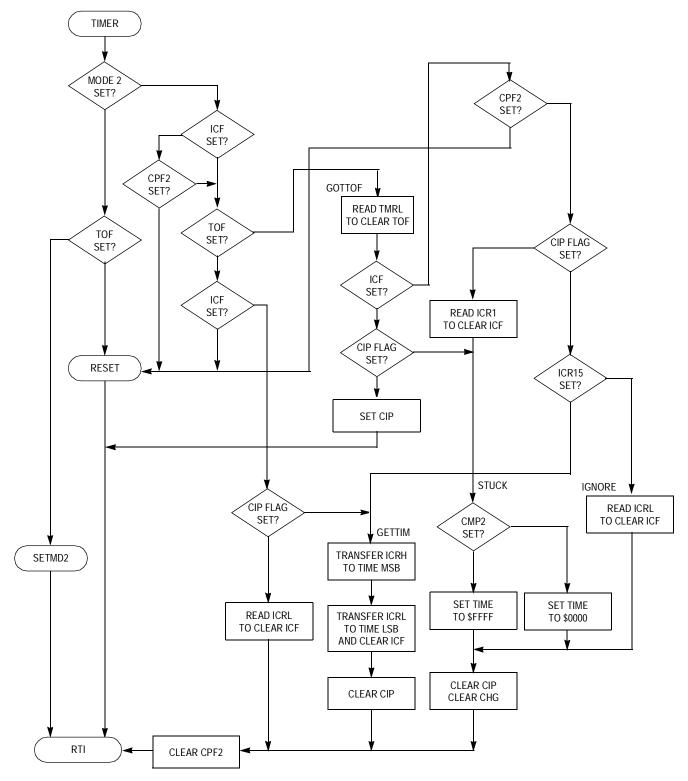

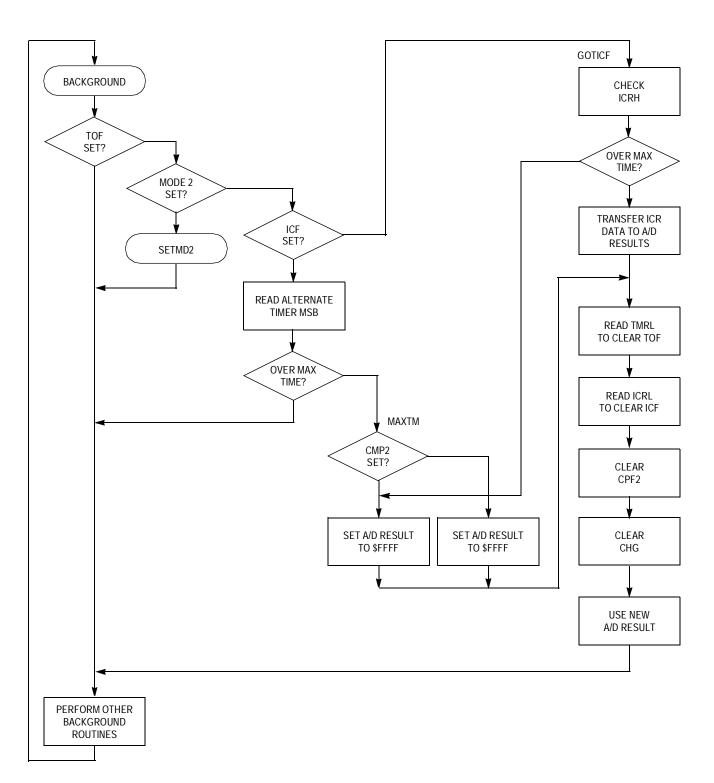

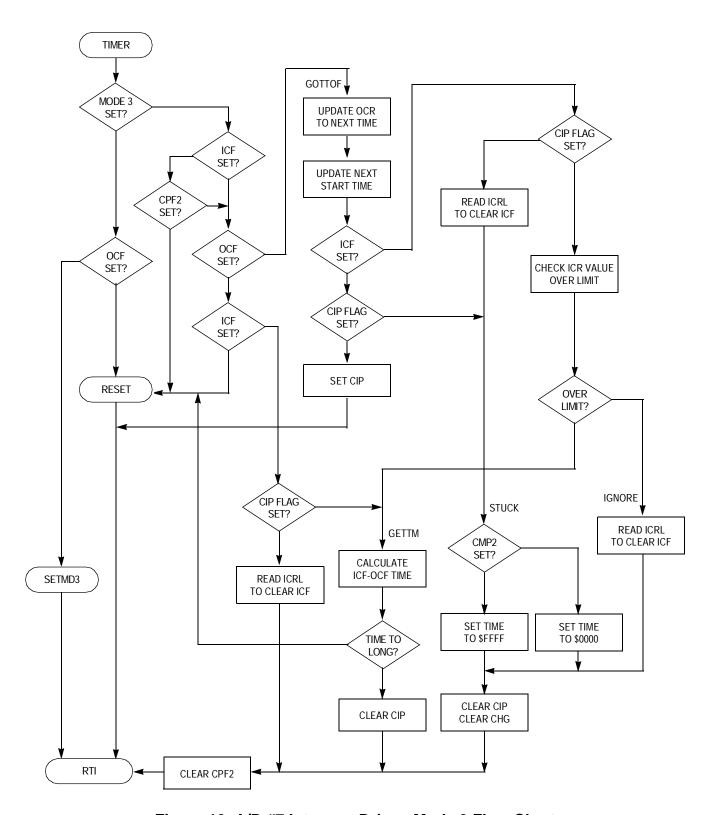

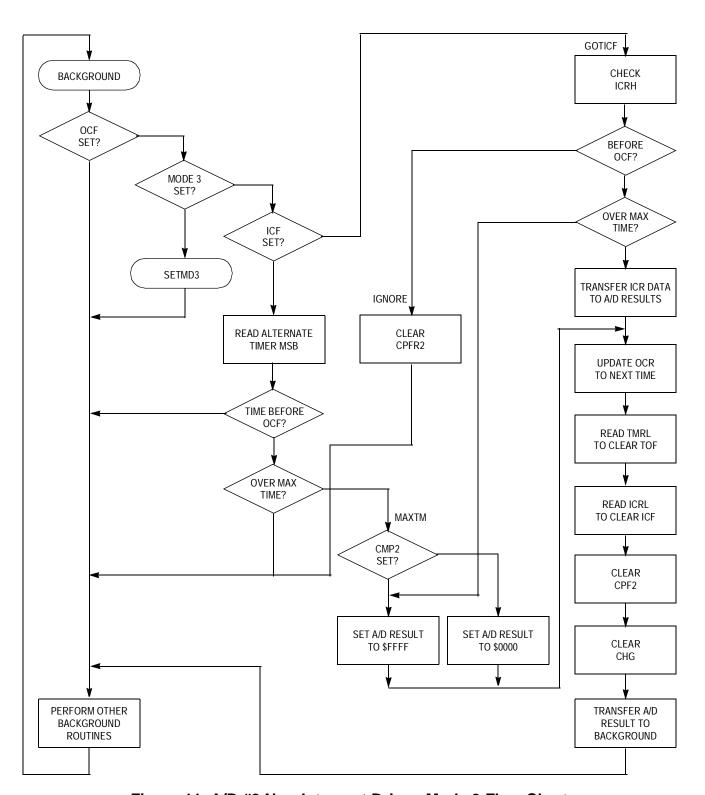

In this A/D example, the device is placed in mode 2 and the current source is controlled by the 16-bit timer to charge and discharge the PB0 pin. The TOF flag starts the charge cycle and the discharge is turned on after comparator 2 trips the input capture and causes an ICF flag. The resulting time count for the conversion is stored in the input capture register as an 16-bit number. If the next TOF occurs before the ICF, then the input to the comparator is either at or below  $V_{SS}$ . The software will follow the flow chart for the background routine given in Figure 5, the timer interrupt routine in Figure 6, and the listing in Software Listing 3 — Interrupt Driven Mode 2 A/D Conversions.

There are additional features to prevent low level inputs near  $V_{SS}$  from causing noisy readings. Also included is a maximum time check in case the input should get too close to  $V_{SS}$  or above the common mode range of the comparator.

The A/D cycle time is about 131 ms between TOF conversions for a 0.2  $\mu$ F capacitor and 4 MHz oscillator. Discharge time is about 0.8 ms. Full scale value of \$FFF occurs with an input voltage of about 4.0 volts for a 5 volt supply to  $V_{DD}$ .

The software example also makes use of the software flag bit, CIP, contained in a defined FLGS variable. The software example is commented to show the reader what is being performed in each step.

Figure 5. Background Flow Chart for A/D #3, #4, and #7

Application Note A/D #3 — Interrupt Driven Mode 2

Figure 6. A/D #3 Interrupt Driven Mode 2 Flow Chart

AN1739

# Software Listing 3 — Interrupt Driven Mode 2 A/D Conversions

\*\*\*\*\*\*\*\*\*\*\*\* \* MODE2, A/D Conversions Using Interrupts with TOF & ICF. \* See text description in AN1739 for more details. \* Mark L. Shaw, © 1996-2001, include jp7incl.asm \$0800 org \*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\* \* SETUP DEVICE BEGIN rsp ;Redundant reset of ; stack pointer ;Redundant set of sei ; interrupt mask bit, I jsr INIT0 ; Initialize analog subsystem ;Set up oscillator \*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\* \* SETUP ANALOG AND 16-BIT TIMER lda #\$10100010 ;Set ICIE, TOIE and IEDG sta TCR ;Enable both ICF and TOF ; interrupts; and set ; detection edge to rising. ; IMPORTANT - IEDG bit must be set if ICF is to be driven by comparator 2. RESET jsr Restore ramp capacitor to ; discharged state and reset ; A/D conversion process. clr TIMMSB ;Clear stored time reading ; to \$0000 clr TIMLSB #%10000001 ;Select HOLD and MUX1 lda ; to initially connect sta AMUX ; PB1 direct to input of ; comparator 2. cli ;Enable all interrupts

Application Note Software Listing 3 — Interrupt Driven Mode 2 A/D Conversions

\* BACKGROUND PROGRAM \* Loop through the background routine and use the Timer  $\mbox{\ensuremath{^{\star}}}$  interrupts to detect, calculate, and control any A/D \* conversions. BLOOP sei ;Temporarily disable ; interrupts so that ; reading of TIMMSB and ; TIMLSB registers will ; not be corrupted by an ; intervening interrupt. lda TIMMSB ;Transfer time data to ; another set of RAM sta ATDMSB lda TIMLSB ; registers. sta ATDLSB cli ;Restore interrupts ;Insert background code nop ; routines here; and then nop ; loop back to start of nop ; background loop. nop bra BLOOP \*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\* \* TIMER INTERRUPT ROUTINE \* When the I-bit is cleared, any interrupt can seize \* control. In this software example only the 16-bit Timer \* is defined as an interrupt. This interrupt routine \* captures the time data from the Input Capture Register \* and transfers it to RAM as TIMMSB, TIMLSB. The \* background routine will transfer this time data to \* another working variable in RAM as ATDMSB, ATDLSB. \* Signals near Vss which may cause extra ICFs later in \* the TOF cycle have been reduced by means of the CIP \* flag bit which helps to lock out further ICFs until \* the next TOF is detected. \* Additional feature added to check if TOF is received \* while the CIP flag is still set. This indicates that \* there was no intervening ICF and the comparator 2 inputs \* may be stuck near Vss or above the common mode range. \*\_\_\_\_\_ brset ATD2,ACR,CKICF ; If Mode 2 already established ; check for ICF present, else brset TOF, TSR, GOMD2 ; check for TOF present. RSTMD jsr RESET ;No TOF or Mode 2, therefore bra TEXIT ; ignore and reset analog ; and flags.

# **Application Note**

| GOMD2                                   | jsr<br>bra                      | SETMD2<br>TEXIT                                                                    | ;First TOF, so go set up ; Mode 2 for first time.                                                                          |

|-----------------------------------------|---------------------------------|------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| CKICF                                   | brset<br>bra                    |                                                                                    | ;If ICF present go check<br>; for valid CPF2 flag, else<br>; go check for TOF.                                             |

| CKCPF2                                  | brset<br>bra                    | CPF2,ASR,CKTOF<br>RSTMD                                                            | ;If valid CPF2 flag is<br>; present then go check<br>; for TOF, else reset A/D.                                            |

| CKTOF                                   | brset                           | TOF, TSR, GOTTOF                                                                   | ;Check if TOF present.                                                                                                     |

|                                         | brset<br>bra                    | ICF,TSR,ICF1<br>RSTMD                                                              | ;Check if ICF present. ;No ICF or TOF, therefore ; reset analog and flags.                                                 |

| ICF1                                    | brset                           | CIP, FLGS, GETTIM                                                                  | ;Test for CIP flag to see if ; a conversion was still in ; progress. If so, then the ; ICF is valid end of a ; conversion. |

|                                         |                                 | ICRL<br>CLCPF2                                                                     | ;Extra ICF found when no ; conversion in progress, so ; clear ICF and ignore.                                              |

| ; Alway<br>; TOF a<br>; will<br>; cycle | nd ICF a<br>cause an<br>without | ED<br>the TOF before c<br>re both set, clea<br>immediate start<br>regard for actua | al timing of the TOF.                                                                                                      |

| ;<br>GOTTOF                             |                                 | TMRL                                                                               | ;Clear TOF                                                                                                                 |

|                                         | brset                           | ICF, TSR, CKICF2                                                                   | ;Check if ICF present.                                                                                                     |

|                                         | brset                           | CIP, FLGS, STUCK                                                                   | ;Check for CIP flag; showing a conversion; was still in progress.                                                          |

| GOCONV                                  | bset<br>bra                     | CIP, FLGS<br>TEXIT                                                                 | ;Set CIP to indicate ; that a conversion has ; been started.                                                               |

| CKICF2                                  | brset<br>bra                    | CPF2,ASR,ICF2                                                                      | <pre>;Test for CPF2 flag with ; ICF for validity. ;No ICF with CPF2, therefore</pre>                                       |

Application Note Software Listing 3 — Interrupt Driven Mode 2 A/D Conversions

| ICF2            | brset                    | CIP, FLGS, CLRICF                | ;Check for CIP flag; showing that conversion; is in progress.                                                                                 |

|-----------------|--------------------------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

|                 | brset<br>bra             | 7,ICRH,IGNORE<br>GETTIM          | ;Check most significant; bit of ICR to see if; captured time was near; TOF time.                                                              |

| CLRICF          | lda                      | ICRL                             | ;ICF captured near next; TOF, so ignore ICF and; check CMP2.                                                                                  |

| STUCK           | brset                    | CMP2, ASR, STKLOW                | ;Check output of comparator; 2 to determine input; state.                                                                                     |

|                 | lda<br>sta<br>sta        | #\$FF<br>TIMMSB<br>TIMLSB        | ;Comparator 2 output was ; low, therefore input was ; greater than common-mode ; range.                                                       |

| CLRCHG          | bclr                     | CIP,FLGS                         | ;Clear CIP to indicate ; that conversion is over.                                                                                             |

|                 | bclr<br>bra              | CHG, ACR<br>CLCPF2               | <pre>;Clear CHG bit in ACR ; to discharge ramp ; capacitor due to ; infinite conversion. ; (TOF was already cleared ; above at GOTTOF.)</pre> |

| STKLOW          | clr<br>clr<br>bra        | TIMMSB<br>TIMLSB<br>CLRCHG       | ;Comparator 2 output was ; high, therefore input was ; near Vss or lower.                                                                     |

| IGNORE          | lda<br>bra               | ICRL<br>CLRCHG                   | ;Read ICRL to clear ICF. ;GO clear CHG bit in ACR.                                                                                            |

| GETTIM          | lda<br>sta<br>lda<br>sta | ICRH<br>TIMMSB<br>ICRL<br>TIMLSB | ;Transfer ICR time to<br>; measured reading and<br>; clear ICF when ICRL<br>; is read.                                                        |

|                 | bclr                     | CIP,FLGS                         | ;Clear CIP to indicate ; that conversion is over.                                                                                             |

| CLCPF2<br>TEXIT | bset<br>rti              | CPFR2,ASR                        | ;Clear CPF2 flag.                                                                                                                             |

include subroutin.asm

#### **Application Note**

| * : | * * * * * * | **** | *****     | **********    |

|-----|-------------|------|-----------|---------------|

| *   | RESET       | AND  | INTERRUPT | VECTORS       |

| *.  |             |      |           |               |

|     |             | org  | \$1FF6    |               |

|     |             | fdb  | TIMER     | ;Timer vector |

|     |             | org  | \$1FFE    |               |

|     |             | fdb  | BEGIN     | Reset vector  |

| *.  |             |      |           |               |

|     |             | end  |           |               |

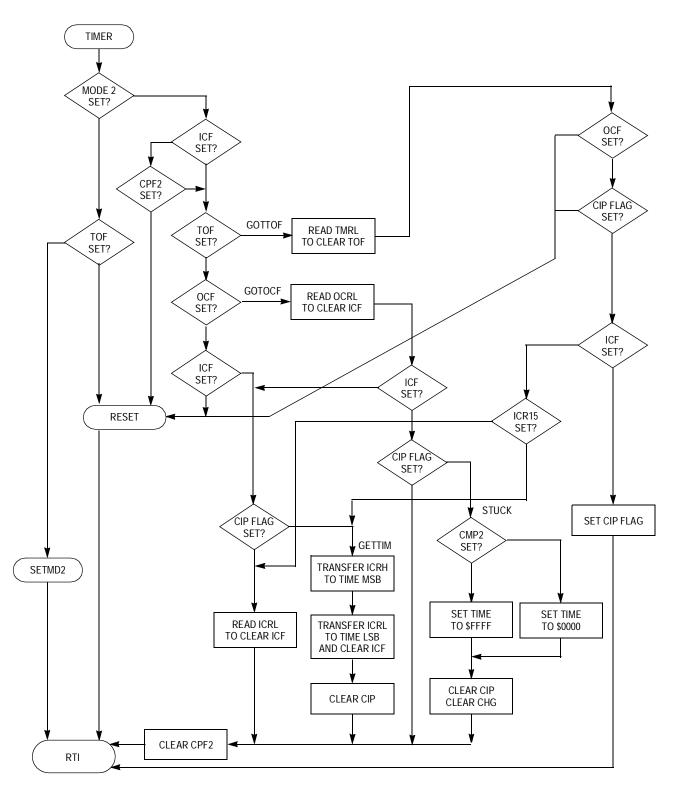

# A/D #4 — Interrupt Driven Mode 2 with OCF

Mode 2 conversions as in A/D #3 can be enhanced to give an earlier detection of a time-out if the OCF in the 16-bit timer is not being used for some other function. This example is the same as A/D #3 except that if an OCF occurs while a conversion is still in progress, then the input to the comparator is either near or below V<sub>SS</sub> or out of the common mode range. The software will follow the background flow chart given in Figure 5, the timer interrupt flow chart given in Figure 7; and the listing in Software Listing 4 — Interrupt Driven Mode 2 A/D Conversions with OCF.

The software example also makes use of the software flag bit, CIP, contained in a defined FLGS variable. The software example is commented to show the reader what is being performed in each step.

Application Note A/D #4 — Interrupt Driven Mode 2 with OCF

Figure 7. A/D #4 Interrupt Driven Mode 2 Flow Chart with OCF

AN1739

#### Software Listing 4 — Interrupt Driven Mode 2 A/D Conversions with OCF

```

************

* MODE2, A/D Conversions Using Interrupts with, TOF, OCF, & ICF.

* See text description in AN1739 for more details.

* Mark L. Shaw, © 1996-2001,

include jp7incl.asm

******************

* Program Specific Parameter Values

OVRFLW equ

$C0

;Count for MSB of OCR to

; check conversion overflow.

$0800

* SETUP DEVICE

BEGIN rsp

;Redundant reset of

; stack pointer

;Redundant set of

sei

; interrupt mask bit, I

jsr

INIT0

;Initialize analog subsystem

;Set up oscillator

*****************

* SETUP ANALOG AND 16-BIT TIMER

lda

#%11100010

;Set ICIE, OCIE, TOIE and IEDG

sta

TCR

;Enable both ICF and TOF

; interrupts; and set

; detection edge to rising.

;-----

; IMPORTANT - IEDG bit must be set if ICF is to be

driven by comparator 2.

;-----

lda

#OVRFLW

;Update TEMP value with

TEMP

; new value for OCR

sta

jsr

RESET

;Restore ramp capacitor to

; discharged state and reset

; A/D conversion process.

clr

;Clear stored time reading

TIMMSB

clr

TIMLSB

; to $0000

```

**Application Note**

Software Listing 4 — Interrupt Driven Mode 2 A/D Conversions with OCF

```

lda

#%10000001

;Select HOLD and MUX1

sta

; to initially connect

AMUX

; PB1 direct to input of

; comparator 2.

cli

; Enable all interrupts

***************

* BACKGROUND PROGRAM

* Loop through the background routine and use the Timer

* interrupts to detect, calculate, and control any A/D

* conversions.

BLOOP sei

;Temporarily disable

; interrupts so that

; reading of TIMMSB and

; TIMLSB registers will

; not be corrupted by an

; intervening interrupt.

lda

TIMMSB

;Transfer time data to

; another set of RAM

sta

ATDMSB

lda

TIMLSB

; registers.

ATDLSB

sta

cli

;Restore interrupts

; Insert background code

nop

; routines here; and then

nop

nop

; loop back to start of

nop

; background loop.

bra

BLOOP

*****************

* TIMER INTERRUPT ROUTINE

* When the I-bit is cleared, any interrupt can seize

* control. In this software example only the 16-bit Timer

* is defined as an interrupt. This interrupt routine

* captures the time data from the Input Capture Register

* and transfers it to RAM as TIMMSB, TIMLSB. The

* background routine will transfer this time data to

* another working variable in RAM as ATDMSB, ATDLSB.

^{\star} Signals near Vss which may cause extra ICFs later in

* the TOF cycle have been reduced by means of the CIP

* flag bit which helps to lock out further ICFs until

* the next TOF is detected.

* Additional feature added to check if OCF is received

* while the CIP flag is still set. This indicates that

* there was no intervening ICF and the comparator 2 inputs

* may be stuck near Vss or above the common mode range.

*_____

```

# **Application Note**

| TIMER                                   | brset                            | ATD2,ACR,CKICF                                                        | ;Check if Mode 2 has already ; been established.                                                                                       |

|-----------------------------------------|----------------------------------|-----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

|                                         | brset                            | TOF,TSR,GOMD2                                                         | ;Check if TOF present.                                                                                                                 |

| RSTMD                                   | lda<br>sta<br>jsr<br>bra         | #OVRFLW<br>TEMP<br>RESET<br>TEXIT                                     | ;Update TEMP value with<br>; new value for OCR<br>;No TOF or Mode 2, therefore<br>; ignore and reset analog<br>; and flags.            |

| GOMD2                                   | jsr<br>bra                       | SETMD2<br>TEXIT                                                       | ;First TOF, so go set up ; Mode 2 for first time.                                                                                      |

| CKICF                                   | brset<br>bra                     | ICF,TSR,CKCPF2<br>CKTOF                                               | ;If ICF present go check<br>; for valid CPF2 flag, else<br>; go check for TOF.                                                         |

| CKCPF2                                  | brset<br>bra                     |                                                                       | ;If valid CPF2 flag go check ; for TOF, else reset A/D.                                                                                |

| CKTOF                                   | brset                            | TOF,TSR,GOTTOF                                                        | ;Check if TOF present.                                                                                                                 |

|                                         | brset                            | OCF, TSR, GOTOCF                                                      | ;Check if OCF present.                                                                                                                 |

|                                         | brset<br>bra                     | ICF,TSR,ICF1<br>RSTMD                                                 | ;Check for ICF present.;No interrupt flags so; reset A/D.                                                                              |

| ICF1                                    | brset                            | CIP,FLGS,GETTIM                                                       | ;Test for CIP flag to see if<br>; a conversion was still in<br>; progress. If so, then the<br>; ICF is valid end of a<br>; conversion. |

| CLRICF                                  |                                  | ICRL<br>CLCPF2                                                        | ;Extra ICF found when no ; conversion in progress, so ; clear ICF and ignore.                                                          |

| ; Alway<br>; TOF a<br>; will<br>; cycle | and ICF a<br>cause an<br>without | the TOF before care both set, clear immediate start regard for actual | al timing of the TOF.                                                                                                                  |

| ;<br>GOTTOF                             |                                  |                                                                       | ;Clear TOF                                                                                                                             |

|                                         | brset                            | OCF,TSR,RSTMD                                                         | ;If OCF also present reset ; A/D, else go check for ; CIP flag.                                                                        |

|                                         | brset                            | CIP,FLGS,RSTMD                                                        | ;If CIP also present reset ; A/D, else go check for ; an ICF.                                                                          |

Application Note

Software Listing 4 — Interrupt Driven Mode 2 A/D Conversions with OCF

|        | brset                    | ICF,TSR,ICF2                     | ;Check if ICF present.                                                                                                                        |

|--------|--------------------------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

|        | bset<br>bra              | TEXIT                            | ;Set CIP flag to indicate ; conversion in progress.                                                                                           |

|        | NCOUNTER                 |                                  |                                                                                                                                               |

| •      | lda                      |                                  | ;Clear OCF                                                                                                                                    |

|        | brset                    | ICF,TSR,ICF1                     | ;If ICF present go check ; to see if conversion in ; progress.                                                                                |

|        | brset<br>bra             |                                  | ;Check for CIP flag<br>; showing a conversion<br>; was still in progress.                                                                     |

| ICF2   | brset<br>bra             | 7,ICRH,CLRICF<br>GETTIM          | ;Check most significant; bit of ICR to see if; captured time was near; TOF time.                                                              |

| STUCK  | brset                    | CMP2,ASR,STKLOW                  | ;Check output of comparator; 2 to determine input; state.                                                                                     |

|        | lda<br>sta<br>sta        | #\$FF<br>TIMMSB<br>TIMLSB        | ;Comparator 2 output was<br>; low, therefore input was<br>; greater than common-mode<br>; range.                                              |

| CLRCHG | bclr                     | CIP,FLGS                         | ;Clear CIP to indicate ; that conversion is over.                                                                                             |

|        | bclr<br>bra              | CHG,ACR<br>CLCPF2                | <pre>;Clear CHG bit in ACR ; to discharge ramp ; capacitor due to ; infinite conversion. ; (TOF was already cleared ; above at GOTTOF.)</pre> |

| STKLOW | clr<br>clr<br>bra        | TIMMSB<br>TIMLSB<br>CLRCHG       | ;Comparator 2 output was ; high, therefore input was ; near Vss or lower.                                                                     |

| GETTIM | lda<br>sta<br>lda<br>sta | ICRH<br>TIMMSB<br>ICRL<br>TIMLSB | ;Transfer ICR time to<br>; measured reading and<br>; clear ICF when ICRL<br>; is read.                                                        |

|        | bclr                     | CIP,FLGS                         | Clear CIP to indicate; that conversion is over.                                                                                               |

#### **Application Note**

| TEXIT   | rti             | CPFR2,ASR      | ;Clear CPF2 flag. |

|---------|-----------------|----------------|-------------------|

|         |                 | subroutin.asm  |                   |

| *****   | * * * * * * * * | ******         | ******            |

| * RESET | AND INT         | ERRUPT VECTORS |                   |

| *       |                 |                |                   |

|         | org             | \$1FF6         |                   |

|         | fdb             | TIMER          | ;Timer vector     |

|         | org             | \$1FFE         |                   |

|         | fdb             | BEGIN          | ;Reset vector     |

| *       |                 |                |                   |

|         | end             |                |                   |

# A/D #5 — Non-Interrupt Driven Mode 2

In this A/D example the device is placed in mode 2 with similar performance to A/D #3, except that this example does not rely on enabling the timer interrupts and requires additional checks to make sure that the TOF and ICF are in the proper sequence. The software will follow the flow chart given in Figure 8 and the listing in Software Listing 5 — Non-Interrupt Driven Mode 2 A/D Conversions.

The software example does not make use of the software flag bit, CIP. The software example is commented to show the reader what is being performed in each step.

Application Note A/D #5 — Non-Interrupt Driven Mode 2

Figure 8. A/D #5 Non-Interrupt Driven Mode 2 Flow Chart

# Software Listing 5 — Non-Interrupt Driven Mode 2 A/D Conversions

| ************************************** |            |                                   |                                                                                       |

|----------------------------------------|------------|-----------------------------------|---------------------------------------------------------------------------------------|

|                                        | equ        |                                   | ;Limit for time MSB                                                                   |

|                                        | _          |                                   | *********                                                                             |

| *BEGIN                                 |            |                                   | ;Redundant reset of<br>; stack pointer                                                |

|                                        | sei        |                                   | <pre>;Redundant set of ; interrupt mask bit, I</pre>                                  |

|                                        | jsr        | INITO                             | ;Initialize analog subsystem ;Set up oscillator                                       |

| * SETU                                 | P ANALOG   | G AND 16-BIT TIM                  |                                                                                       |

| *                                      | lda<br>sta |                                   | ;Set IEDG for detection ; of rising edge to ICF.                                      |

| ; IMPOI                                | RTANT -    | IEDG bit must be driven by compa: |                                                                                       |

| ,                                      |            | RESET                             | Restore ramp capacitor to discharged state and reset; A/D conversion process.         |

|                                        | clr<br>clr | ATDMSB<br>ATDLSB                  | Clear stored time reading; to \$0000                                                  |

|                                        | lda<br>sta | #%10000001<br>AMUX                | ;Select HOLD and MUX1 ; to initially connect ; PB1 direct to input of ; comparator 2. |

Application Note

Software Listing 5 — Non-Interrupt Driven Mode 2 A/D Conversions

| BLOOP              | brset<br>bra                                  | TOF,TSR,CHKMD<br>LOOP                        | ;If TOF found go check for ; Mode 2, else skip checks                                                                                         |

|--------------------|-----------------------------------------------|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| CHKMD              | brset<br>jsr<br>bra                           | ATD2,ACR,CKICF<br>SETMD2<br>LOOP             | ;If Mode 2 already established; check for ICF present, else; set up Mode 2.                                                                   |

| CKICF              | brset                                         | ICF,TSR,GOTICF                               | ;If ICF present go get<br>; conversion data, else<br>; go check for overrun.                                                                  |

| CHKTM              | lda<br>cmp<br>bhs<br>bra                      | ACRH<br>#LIMIT<br>MAXTM<br>LOOP              | ;Fetch MSB of timer count.<br>;Check against max limit.<br>;If over limit go check<br>; comparator state, else<br>; continue with background. |

| GOTICF             | lda<br>cmp<br>bhs<br>sta<br>lda<br>sta<br>bra | ICRH #LIMIT SETMAX ATDMSB ICRL ATDLSB RSTATD | ;Check MSB of ICF data; against limit.; If higher or same set the; A/D result to \$FFFF, else; transfer ICR contents to; to A/D result.       |

| MAXTM              | brset                                         | CMP2, ASR, SETLO                             | ;If CMP2 set then comparator ; input stuck low, else it ; is stuck high.                                                                      |

| SETMAX             | lda<br>sta<br>sta<br>bra                      | #\$FF<br>ATDMSB<br>ATDLSB<br>RSTATD          | ;Default A/D result to the ; maximum value of \$FFFF.                                                                                         |

| SETLO              | lda<br>sta<br>sta                             | #\$00<br>ATDMSB<br>ATDLSB                    | ;Default A/D result to the ; minimum value of \$0000.                                                                                         |

| RSTATD             | lda                                           | TSR                                          | Read the TSR to arm flags; for clearing.                                                                                                      |

| ;;<br>; IMPOR<br>: | TANT - 2                                      | =                                            | before clearing ICF.                                                                                                                          |

| ,                  | lda<br>lda<br>bset                            | TMRL<br>ICRL<br>CPFR2,ASR                    | Clear TOF flag, if any. Clear ICF flag, if any. Clear CPF2 flag, if any.                                                                      |

## **Application Note**

|         | bclr                            | CHG, ACR                                                      | Force discharge of PBO; for case where time; was over limit. |

|---------|---------------------------------|---------------------------------------------------------------|--------------------------------------------------------------|

| CALC    | lda<br>sta<br>lda<br>sta        | TIMMSB<br>ATDLSB                                              | ;Transfer A/D result to the ; other background routines.     |

| LOOP    | nop<br>nop<br>nop<br>nop<br>nop |                                                               |                                                              |

| *       |                                 |                                                               | ;Repeat background loop.                                     |

| *****   |                                 | <pre>subroutin.asm ************************************</pre> | *****                                                        |

| * RESET |                                 | ERRUPT VECTORS                                                |                                                              |

| *       | org<br>fdb                      |                                                               | Reset vector                                                 |

|         | end                             |                                                               |                                                              |

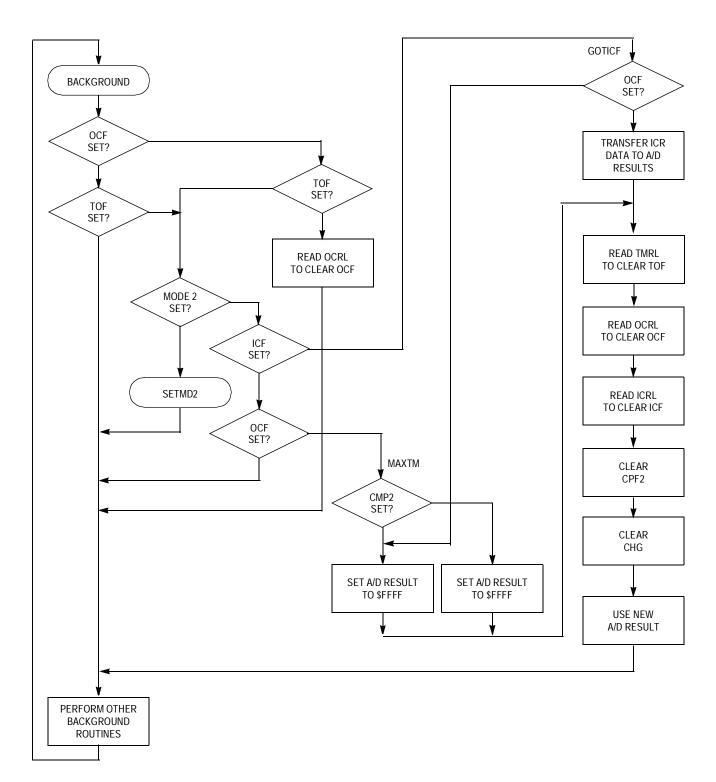

## A/D #6 — Non-Interrupt Driven Mode 2 with OCF

The mode 2 conversions in A/D #5 can be enhanced to give an earlier detection of a time-out if the OCF in the 16-bit timer is not being used for some other function. This A/D example is the same as A/D #5 except that this example does not rely on enabling the timer interrupts and requires additional checks to make sure that the TOF, OCF, and ICF are in the proper sequence. The software will follow the flow chart given in Figure 9 and the listing in Software Listing 6 — Non-Interrupt Driven Mode 2 A/D Conversions with OCF.

The software example does not make use of the software flag bit, CIP. The software example is commented to show the reader what is being performed in each step.

Application Note A/D #6 — Non-Interrupt Driven Mode 2 with OCF

Figure 9. A/D #6 Non-Interrupt Driven Mode 2 Flow Chart with OCF

# Software Listing 6 — Non-Interrupt Driven Mode 2 A/D Conversions with OCF

| *****  | *****      | ******             | *******                                      |

|--------|------------|--------------------|----------------------------------------------|

| * MODE | 2, A/D (   | Conversions Usin   | g TOF, OCF & ICF without Interrupts          |

| * See  | text des   | scription in AN1   | 739 for more details.                        |

| * Mark | L. Shav    | w, © 1996-2001,    |                                              |

| *****  | *****      | ******             | ********                                     |

|        | includ     | de jp7incl.asm     |                                              |

|        |            |                    |                                              |

| *****  | *****      | ******             | *******                                      |

| * Pro  | gram Spe   | ecific Parameter   | Values                                       |

|        |            |                    |                                              |

| LIMIT  | equ        | \$10               | ; Limit for time using OCF MSB               |

|        | ora        | \$0800             |                                              |

| *****  | _          | ·                  | *******                                      |

|        |            |                    |                                              |

|        | P DEVICE   | <u> </u>           |                                              |

|        |            |                    |                                              |

| BEGIN  | rsp        |                    | Redundant reset of                           |

|        |            |                    | ; stack pointer                              |

|        | sei        |                    | Redundant set of                             |

|        |            |                    | ; interrupt mask bit, I                      |

|        |            |                    |                                              |

|        | jsr        | INITO              | ;Initialize analog subsystem                 |

|        | -          |                    | ;Set up oscillator                           |

|        |            |                    | _                                            |

| *****  | *****      | ******             | *******                                      |

|        |            |                    |                                              |

| *      |            | G AND 16-BIT TIM   | er                                           |

|        |            | ще. оо оо оо оо    |                                              |

|        |            |                    | ;Set IEDG for detection                      |

|        | sta        | TCR                | ; of rising edge to ICF.                     |

|        |            |                    |                                              |

| •      |            |                    |                                              |

| ; IMPO | RTANT -    | IEDG bit must b    | e set if ICF is to be                        |

| ;      |            | driven by compa    | rator 2.                                     |

| ;      |            |                    |                                              |

|        | lda        | #LIMIT             | ;Update TEMP value with                      |

|        | sta        | TEMP               | ; new value for OCR                          |

|        | jsr        | RESET              | Restore ramp capacitor to                    |

|        | JOI        | KUDUI              | ; discharged state and reset                 |

|        |            |                    | _                                            |

|        |            |                    | ; A/D conversion process.                    |

|        |            |                    |                                              |

|        | clr        | ATDMSB             | ;Clear stored time reading                   |

|        | clr        | ATDLSB             | ; to \$0000                                  |

|        |            |                    |                                              |

|        |            |                    |                                              |

|        | lda        | #%10000001         | ;Select HOLD and MUX1                        |

|        | lda<br>sta | #%10000001<br>AMUX | ;Select HOLD and MUX1 ; to initially connect |

|        |            |                    | ; to initially connect                       |

|        |            |                    |                                              |

**Application Note**

Software Listing 6 — Non-Interrupt Driven Mode 2 A/D Conversions with OCF

- \* BACKGROUND PROGRAM

- \* Loop through the background routine and use the Timer

| * conve | rsions.                         |                                            | lculate, and control any A/D                                                      |

|---------|---------------------------------|--------------------------------------------|-----------------------------------------------------------------------------------|