## **AN14577** S32Z2E2 Built-In Self-Test Rev. 1.0 — 11 April 2025

**Application note**

#### **Document information**

| Information | Content                                                                                                                    |

|-------------|----------------------------------------------------------------------------------------------------------------------------|

| Keywords    | S32Z2E2                                                                                                                    |

| Abstract    | This document describes how to configure and execute Built-In Self Test (BIST) for the NXP S32Z2/E2 Automotive Processors. |

#### Self-test overview 1

The S32Z2/E2 microcontrollers include logic and memory Built-In Self-test (BIST) features. These features are designed to provide diagnostic coverage at device power up or shut-down/idle to ensure that logic and memory partitions do not contain permanent faults that might affect proper operation of the device.

The MCU implements BIST using a central self-test controller (CSTCU) and multiple local self-test controllers (LSTCUs) that cooperate to perform the full series of tests. These modules are highly programmable and customizable. As a result, and to ensure proper coverage and correct operation of the test procedure, only the test procedure and data provided with this application note might be used. Other configurations are not supported by NXP.

Start-up (also referred to as "power-up") self-test is executed by the device's boot ROM after the "Initialize 1" boot sequence. It is intended to be executed before the application is loaded and executed and it is run only after a Power-On Reset (POR) event.

Shut-down or Idle self-test (sometimes called "online" self-test in previous devices) might be initiated by application control, usually at an idle time or prior to shut-down. Running at this time might be advantageous if the amount of time required to run a self-test cannot be tolerated during start-up.

This application note describes both types of self-test initiation.

#### 1.1 Start-up self-test

#### 1.1.1 Configuration

AN14577

Start-up self-test is configured by including the Device Configuration Data (DCD) binary image for self-test attached to this application note in the Image Vector Table (IVT) boot image. The IVT has pointers to the selftest Image and (optionally) back-up self-test image. The back-up image is simply a redundant copy of the primary self-test image and is used if the primary image should fail to be read or authenticated by the boot process.

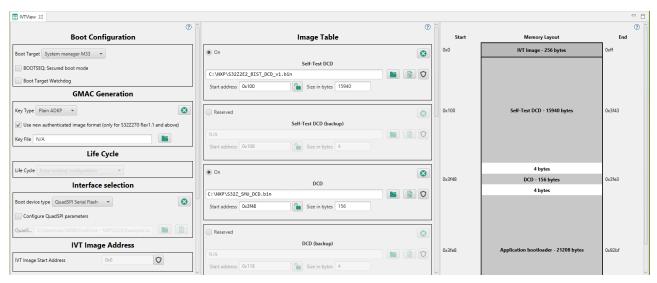

If using the S32 Design Studio IVT Tool for configuration, simply enable the self-test DCD section and specify the filename of the binary self-test DCD image. It may be necessary to press "auto align" after doing so to arrange the blocks in the IVT image. Include the back-up image in the same way, if desired.

Include the application binary and specify the Boot Target and Type, the Export BLOB Image to create a bootable flash image containing both the start-up self-test and user application.

#### **1.1.2 Start-up self-test execution**

If properly configured in the IVT, no additional steps are necessary to execute self-test. This will occur automatically during application boot after a POR event. BootROM configures the central and local self-test controllers and initiates the test. Upon completion, the device goes through a functional reset and application boot will continue in the "Initialize 2" phase, followed by loading and executing the Hardware Security Engine (HSE) firmware (secure boot) or the application boot-loader (non-secure boot).

Whether a secure or non-secure boot, it is the responsibility of the application to check the status of self-test execution.

#### 1.2 Shut-down self-test

Self-test may also be initiated by the software application at any time. Typically, this will be done during an idle time or prior to shut-down when there is sufficient time available to execute all tests. As with start-up self-test, a reset will occur when test execution is complete.

#### 1.2.1 Preparing for shut-down self-test

There are three basic requirements to run self-test at an idle / shut-down time.

- 1. Stop running processes and disable interrupts.

- 2. Ensure any previous self-test run has completed.

- 3. Disable all active Clock Monitoring Units (CMU\_FC)

#### **1.2.1.1 Stop running processes**

To ensure no interference from running processes or interrupts during the configuration or execution of shutdown self-test, begin by stopping application processes in RTU, FlexLLCE, and any process on the SMU core but the one conducting self-test.

Disable any peripheral interrupts that might occur during the configuration or executed phases of self-test.

#### 1.2.1.2 Ensure previous self-test procedures are completed

This should be the case if the self-test is being run at a shut-down / idle time, but as a precaution simply read the CSTCU module's Reset Domain Enable Status (RDENSTAT) fields. All bit fields should read as zero (disabled).

If these status bits do not all read back zero, then it is possible that a previous BIST run was aborted. Write 0 to all four bit fields of the Reset Domain self-test Enable (RDEN) register, and again poll RDENSTAT until it reads back zero.

#### 1.2.1.3 Disable all active clock monitoring units

To avoid false triggering of Clock Monitoring alarms during the execution of self-test procedures, clear the Frequency Check Enable (FCE) bit in each CMU\_FC instance's Global Configuration Register (GCR).

#### 1.2.2 Shut-down self-test configuration

Self-Test configuration consists of setting up MBIST, LBIST, and general CSTCU/LSTCU parameters for the full test run. Below is an outline of this procedure, however this contains many chip-specific details and register settings, not all of which are documented in the User Reference Manual. For full detail of the necessary procedure use as a reference the attached source code files: STCU.C, STCU.h, MMC\_GLS\_FULL.c, and MMC\_GLS\_FULL.h.

#### 1.2.2.1 MBIST

- 1. Set CSTCU.LSCHLVD[MBPLVLD] = 1 to enable MBIST.

- 2. Perform MTR MBIST configuration.

- 3. Configure CSTCU's LMBPTR0 through LMBPTR17 to schedule the MBIST sequences.

#### 1.2.2.2 LBIST

- 1. Set CSTCU.LSCHLVLD[LBPLVLD] = 1 to enable LBIST.

- 2. Perform LBIST MMC Setup

- 3. Configure CSTCU's LLBPTR0 through LLBPTR17 to schedule LBIST sequences.

#### 1.2.2.3 General CTSTCU/LSTCU

- 1. Write 1 to CSTCU.RDEN fields SERD0, SERD1, and SERD2 to enable SMU and both RTU domains.

- 2. Wait for CSTCU.RDENSTAT not equal to 7.

- 3. Clear to zero the recoverable and unrecoverable error status bits RFSF and UFSF in CSTCU.ERR\_STAT.

- 4. Set LB\_DELAY = 15 and MB\_DELAY = 15 in CSTCU.STAG and all LSTCU\_n.STAG registers to slightly stagger the starts of concurrent LBIST and MBIST partitions.

- 5. Set RTU0/1\_LSTCU0/1.MBPTR registers MBEOL field to 0 and MBPTR field to 1.

- 6. Set RTU0/1\_LSTCU0/1.PH1\_DUR[PH1DUR] = 0x3ff.

- 7. Set RTU0/1\_LSTCU0/1.MBPTR0[MBCSM] = 1 to enable concurrent MBIST.

#### 1.2.3 Shut-down self-test execution

Self-test execution is started simply by setting CSTCU.RUNSWREG[RUNSW] = 1. After this, the application may enter an idle loop. The device will automatically issue a functional reset when it completes the self-test procedure.

#### **1.3 Checking self-test results**

Regardless of the method chosen for self-test execution, as noted, a reset follows completion of the test procedure. Upon entry into the application code after self-test execution and reset, results can be checked by following these steps:

As a preliminary check, first look at the Reset Generation Module's Destructive and Functional Reset Status registers (MC\_RGM.DES and MC\_RGM.FES). If MC\_RGM.DES[3] or MC\_RGM.DES[4] is set, this indicates a BIST destructive reset occurred and the previous self-test run overall failed in an unrecoverable way (e.g. Watchdog reset). No results need be checked. The device should be placed in a safe-state.

If MC\_RGM.FES[4] is set, then the previous reset was due to a completed self-test run. If this is the case, the following procedure may be followed to check detailed results.

- Read CSTCU's ERR\_STAT[ABORTHW] field. If set to 1, a hardware abort was received during the self-test procedure. Results are invalid and should be ignored. It is recommended to re-run the test procedure by requesting a Power On Reset (POR).

- Read CSTCU's ERR\_STAT[UFSF] and ERR\_STAT[RFSF] fields to determine if any Unrecoverable or Recoverable error events were logged during the self-test run. If both fields are 0, the test ran successfully and the rest of this procedure may be skipped.

- In the case that there is any error indicated in ERR\_STAT, check to ensure the LSTCU pointers for both Logic (LBIST) and Memory (MBIST) are valid by reading the CSTCU's ERR\_STAT[INVP\_LB] and ERR\_STAT[INVP\_MB] fields. If either or both bits are set, this may indicate a configuration error. This is an unexpected result since the configuration provided in this application note is correctly structured, however

#### S32Z2E2 Built-In Self-Test

it might indicate that there was an error reading the configuration. If re-running self-test after another POR indicates the same error, then it may indicate a device failure or a corrupt non-volatile memory.

(Optional) If LBIST and MBIST pointers are valid, check which local self-test controllers (LSTCUs) reported errors by reading the CSTCU's LRFSTAT0 and LUFSTAT0 registers. For any bit which is set to 1 in either register, determine if this was an LBIST or MBIST failure by reading the corresponding LSTCU's MB\_RSTATn and LB\_RSTAT0 registers. This only provides some additional detail on the failure location. It is already known at this point that a failure has occurred. The application should at this point log the error and enter a fail-safe state.

#### 1.4 Using the attached self-test source code

The attached source code provides a main procedure for starting a shut-down self-test execution as detailed in this application note. Include the attached source code files in the application build and then invoke function SetupAndRunSTCU() to configure and execute BIST. This is intended to be executed from the System Manager Unit (SMU) CM33 core.

It is recommended to include the steps in "Checking Self-Test Results" above first. Check MC\_RGM FES and DES registers as described. If a self-test procedure is not indicates by the reset status registers then execute SetupAndRunSTCU(). If DES and FES indicate a completed BIST run, then check results as described.

Since the self-test involves a system reset after completion, demonstrating this procedure is best done using an external flash or SD-Card boot configuration for the MCU such that the application is able to execute again immediately after reset to check results.

## 2 References

#### 2.1 NXP references

| Document ID | Document Title          | Source           |

|-------------|-------------------------|------------------|

| RM638609    | S32Z27 Reference Manual | NXP Secure Files |

| RM716503    | S32E27 Reference Manual | NXP Secure Files |

| DS718401    | S32Z27 Data Sheet       | NXP Secure Files |

| DS718301    | S32E27 Data Sheet       | NXP Secure Files |

#### Table 1. NXP document references

#### 2.2 External references

This guide is supplementary to the S32ZSE Reference Manual and Data Sheet.

The following documentation provides useful information about the Arm processor architecture:

- For information about the Arm Cortex-R52 processor, see: <u>https://developer.arm.com/ip-products/processors/</u> <u>cortex-r/cortex-r52</u>

- For information about the Arm Cortex-M33 processor, see: <a href="https://developer.arm.com/ip-products/processors/cortex-m/cortex-m33">https://developer.arm.com/ip-products/processors/cortex-m/cortex-m33</a>

## 3 Acronyms and definition

#### Table 2. Acronyms and definition

| Acronym          | Definition                                                                 |                                      |  |

|------------------|----------------------------------------------------------------------------|--------------------------------------|--|

| ARM              | Advanced RISC Machines processor architecture                              |                                      |  |

| AN14577          | All information provided in this document is subject to legal disclaimers. | © 2025 NXP B.V. All rights reserved. |  |

| Application note | Rev. 1.0 — 11 April 2025                                                   | Document feedback                    |  |

S32Z2E2 Built-In Self-Test

| Acronym          | Definition                                          |

|------------------|-----------------------------------------------------|

| BGA              | Ball Grid Array package                             |

| BOM              | Bill of Materials                                   |

| BSDL             | Boundary Scan Description Language                  |

| CAN              | Controller Area Network                             |

| DDR              | Dual Data Rate DRAM                                 |

| EEPROM           | Electrically Erasable Programmable Read-Only Memory |

| ETM              | Embedded Trace Macrocell                            |

| GND              | Ground                                              |

| GPIO             | General Purpose Input/Output                        |

| I <sup>2</sup> C | Inter-integrated Circuit interface                  |

| IBIS             | Input output Buffer Information Specification       |

| IOMUX            | Input Output Multiplexing                           |

| JTAG             | Joint Test Action Group                             |

| LDO              | Low Drop-Out regulator                              |

| LPDDR4           | Low Power DDR4 DRAM                                 |

| LVDS             | Low-Voltage Differential Signaling                  |

| LIN              | Local Interconnect Network                          |

| MAC              | Media Access Control                                |

| MDIO             | Management Data Input/Output                        |

| MII              | Media Independent Interface                         |

| NC               | Not Connect                                         |

| NMI              | Non-Maskable Interrupt                              |

| ODT              | On-Die Termination                                  |

| РСВ              | Printed Circuit Board                               |

| PDN              | Power Delivery Network                              |

| РНҮ              | Physical Layer Interface                            |

| PMIC             | Power Management Integrated Circuit                 |

| POR              | Power-On Reset                                      |

| QSPI             | Quad serial peripheral interface.                   |

| RGM              | Reset Generation Module                             |

| RGMII            | Reduced Gigabit Media Independent Interface         |

| ROM              | Read-Only Memory                                    |

| SDHC             | Secure Digital High Capacity                        |

| SDR              | Single Data Rate                                    |

Table 2. Acronyms and definition...continued

## 4 Revision history

| Table 3. Revision history |               |                        |  |

|---------------------------|---------------|------------------------|--|

| Document ID               | Release date  | Description            |  |

| AN14577v.1.0              | 11 April 2025 | Initial public release |  |

# AN14577

#### S32Z2E2 Built-In Self-Test

## Legal information

### Definitions

**Draft** — A draft status on a document indicates that the content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included in a draft version of a document and shall have no liability for the consequences of use of such information.

### Disclaimers

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. NXP Semiconductors takes no responsibility for the content in this document if provided by an information source outside of NXP Semiconductors.

In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of NXP Semiconductors.

**Right to make changes** — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors and its suppliers accept no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this respect.

Terms and conditions of commercial sale — NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at https://www.nxp.com/profile/terms, unless otherwise agreed in a valid written individual agreement. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. NXP Semiconductors hereby expressly objects to applying the customer's general terms and conditions with regard to the purchase of NXP Semiconductors products by customer.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

Suitability for use in non-automotive qualified products — Unless this document expressly states that this specific NXP Semiconductors product is automotive qualified, the product is not suitable for automotive use. It is neither qualified nor tested in accordance with automotive testing or application requirements. NXP Semiconductors accepts no liability for inclusion and/or use of non-automotive qualified products in automotive equipment or applications.

In the event that customer uses the product for design-in and use in automotive applications to automotive specifications and standards, customer (a) shall use the product without NXP Semiconductors' warranty of the product for such automotive applications, use and specifications, and (b) whenever customer uses the product for automotive applications beyond NXP Semiconductors' specifications such use shall be solely at customer's own risk, and (c) customer fully indemnifies NXP Semiconductors for any liability, damages or failed product claims resulting from customer design and use of the product for automotive applications beyond NXP Semiconductors' standard warranty and NXP Semiconductors' product specifications.

**HTML publications** — An HTML version, if available, of this document is provided as a courtesy. Definitive information is contained in the applicable document in PDF format. If there is a discrepancy between the HTML document and the PDF document, the PDF document has priority.

**Translations** — A non-English (translated) version of a document, including the legal information in that document, is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.

Security — Customer understands that all NXP products may be subject to unidentified vulnerabilities or may support established security standards or specifications with known limitations. Customer is responsible for the design and operation of its applications and products throughout their lifecycles to reduce the effect of these vulnerabilities on customer's applications and products. Customer's responsibility also extends to other open and/or proprietary technologies supported by NXP products for use in customer's applications. NXP accepts no liability for any vulnerability. Customer should regularly check security updates from NXP and follow up appropriately. Customer shall select products with security features that best meet rules, regulations, and standards of the intended application and make the ultimate design decisions regarding its products and is solely responsible for compliance with all legal, regulatory, and security related requirements concerning its products, regardless of any information or support that may be provided by NXP.

NXP has a Product Security Incident Response Team (PSIRT) (reachable at <u>PSIRT@nxp.com</u>) that manages the investigation, reporting, and solution release to security vulnerabilities of NXP products.

$\ensuremath{\mathsf{NXP}}\xspace$  B.V. — NXP B.V. is not an operating company and it does not distribute or sell products.

## Trademarks

Notice: All referenced brands, product names, service names, and trademarks are the property of their respective owners. **NXP** — wordmark and logo are trademarks of NXP B.V.

## AN14577

S32Z2E2 Built-In Self-Test

## **Tables**

| Tab. 1. | NXP document references | . 5 |

|---------|-------------------------|-----|

| Tab. 2. | Acronyms and definition | .5  |

| Tab. 3. | Revision history | 7 |

|---------|------------------|---|

|         | •                |   |

## AN14577

#### S32Z2E2 Built-In Self-Test

### Contents

| 1       | Self-test overview                        | 2 |

|---------|-------------------------------------------|---|

| 1.1     | Start-up self-test                        | 2 |

| 1.1.1   | Configuration                             | 2 |

| 1.1.2   | Start-up self-test execution              | 3 |

| 1.2     | Shut-down self-test                       | 3 |

| 1.2.1   | Preparing for shut-down self-test         | 3 |

| 1.2.1.1 | Stop running processes                    | 3 |

| 1.2.1.2 | Ensure previous self-test procedures are  |   |

|         | completed                                 | 3 |

| 1.2.1.3 | Disable all active clock monitoring units | 3 |

| 1.2.2   | Shut-down self-test configuration         | 3 |

| 1.2.2.1 | MBIST                                     | 4 |

| 1.2.2.2 | LBIST                                     | 4 |

| 1.2.2.3 | General CTSTCU/LSTCU                      | 4 |

| 1.2.3   | Shut-down self-test execution             | 4 |

| 1.3     | Checking self-test results                | 4 |

| 1.4     | Using the attached self-test source code  | 5 |

| 2       | References                                | 5 |

| 2.1     | NXP references                            | 5 |

| 2.2     | External references                       | 5 |

| 3       | Acronyms and definition                   | 5 |

| 4       | Revision history                          |   |

|         | Legal information                         | 8 |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.

© 2025 NXP B.V.

All rights reserved.

For more information, please visit: https://www.nxp.com

Document feedback Date of release: 11 April 2025 Document identifier: AN14577