# AN14547

Four-channel universal input solution with NAFE13388 family of devicesRev. 1.0 — 28 March 2025Application note

#### **Document information**

| Information | Content                                                                                                                                                                                                                                                                                                                                |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Keywords    | NAFE13188, NAFE13388, NAFE73388 industrial, multichannel, AI-AFE                                                                                                                                                                                                                                                                       |

| Abstract    | This application note presents how to configure and design a four-channel, universal-input system using the NAFE13388 family of devices. The design supports $2/3/4$ -wire RTD, thermocouple, 0 V to 10 V voltage input, 4 ma to 20 mA current input, and load cell. The NAFE13188 variant of the family has been used in this design. |

# 1 Introduction

In this application note, a four-channel, universal-input system using the <u>NAFE13388/NAFE73388</u> (NAFEx3388) family of devices is presented.

The NAFE13388 products are highly configurable, industrial-grade, multichannel analog input analog front-ends (AI-AFE) that meet high-precision measurement requirements.

The system is able to measure the most common transducer inputs in the industrial environment: voltage, current, RTD, thermocouple and Wheatstone bridges. All four channels can be configured with software to measure any of the above transducers.

# 2 NAFE13388 family description

The NAFE13388 family of devices are highly configurable, industrial-grade multichannel universal input analog front-ends (NAFE) that meet high-precision measurement requirements. The NAFE13388 family of products is designed to measure any input voltage and current typically used in the industrial market, such as ±10 V, ±0 to 20 mA, RTDs, PTC, NTC, thermocouples, and Wheatstone bridges.

The device integrates low-leakage, high-voltage fast multiplexers (mux), low-offset and low-drift programmable gain amplifier (PGA), high data-rate 16- or 24-bit sigma-delta, analog-to-digital converter (ADC), precise voltage and current excitation source, and low-drift voltage reference. The digital data are read by the host MCU/MPU through the serial peripheral interface (SPI).

The family is composed of different parts, which differs for speed, factory calibration, ADC resolution, and number of channels.

The NAFE13188, which is the part used in this report, is a 288 kSPS, eight-input, 24-bit ADC version. Other version includes NAFE73388, which features a data rate up to 576 kSPS, or the NAFE13144, which is a four-input version.

# 3 NAFE13188 operation in universal input system

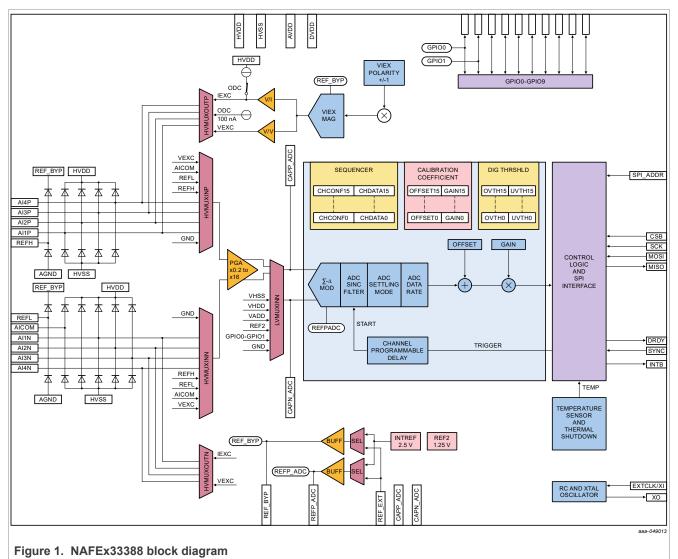

The NAFE13188 has eight analog inputs AI1P...AI4P, AI1N...AI4N and one common input AICOM (see <u>Figure 1</u>), which can measure low voltages, in the range of millivolts, to tens of volts. <u>Table 1</u> shows the different input voltage ranges according to the PGA gain.

Even if the AICOM is mostly used as a reference in pseudo-differential measurements, it can also be used as a standard analog input, such as AIxP or AIxN. This pin is used as part of the analog inputs for one of the four channels.

The analog input signals are routed to the PGA through two multiplexers.

The excitation (VIEX) is able to inject current or voltage to any of the inputs except AICOM.

In a four-channel universal input system, the input multiplexer performances play an important role. To obtain good performance, one input channel must not influence the other channels. The NAFE13388 has a low DC crosstalk of 1  $\mu$ V/V, which corresponds to 120 dB.

|                       | Nominal range values (V) |       |            |              |       |        |         |         |

|-----------------------|--------------------------|-------|------------|--------------|-------|--------|---------|---------|

| PGA gain              | 0.2                      | 0.4   | 0.8        | 1            | 2     | 4      | 8       | 16      |

| Bipolar differential  | ±20                      | ±10   | ±5         | ±4           | ±2    | ±1     | ±0.5    | ±0.25   |

| Bipolar single-ended  | ±10                      | ±5    | ±2.5       | ±2           | ±1    | ±0.5   | ±0.25   | ±0.125  |

| Unipolar differential | ±10                      | ±5    | ±2.5       | ±2           | ±1    | ±0.5   | ±0.25   | ±0.125  |

| Unipolar single-ended | ±10                      | ±5    | ±2.5       | ±2           | ±1    | ±0.5   | ±0.25   | ±0.125  |

|                       |                          | ·     | Min and ma | x values (V) |       |        |         |         |

| PGA gain              | 0.2                      | 0.4   | 0.8        | 1            | 2     | 4      | 8       | 16      |

| Bipolar differential  | ±25                      | ±12.5 | ±6.25      | ±5           | ±2.5  | ±1.25  | ±0.6.25 | ±0.3125 |

| Bipolar single-ended  | ±12.5                    | ±6.25 | ±3.125     | ±2.5         | ±1.25 | ±0.625 | ±0.3125 | ±0.1562 |

| Unipolar differential | ±12.5                    | ±6.25 | ±3.125     | ±2.5         | ±1.25 | ±0.625 | ±0.3125 | ±0.1562 |

| Unipolar single-ended | ±12.5                    | ±6.25 | ±3.125     | ±2.5         | ±1.25 | ±0.625 | ±0.3125 | ±0.1562 |

#### Table 1. Nominal and min/max input voltage ranges

The low-noise sigma-delta ADC samples the PGA output and filters the signal with configurable SINC filters. In the digital domain, the gain, and offset calibration coefficients are used to compensate the measurements.

The NAFE13388 can store 16 different measurement configurations. Each of them applies different settings to the input multiplexer, PGA gain, calibration coefficients, data rate, SINC filter, and IEXC. In this way, 16 logical channels (LCH0 to LCH15) are available to the user. With the channel-based configurations, the user is able to switch among the configured channels seamlessly, and without the need to perform multiple SPI transactions to set up various configurations before each ADC conversion. The sequencer steps through the activated channels to execute the conversion and transfers the results on the data register. The sequencer gives a high degree of flexibility to implement the universal input capability.

The NAFE13388 also integrates ten GPIOs that drive the switches used in the system. In galvanic isolated systems, using the integrated GPIOs allows the host to drive the switches on the isolated side through the SPI, thus saving additional digital isolators. GPIO0 and GPIO1 can also be used as auxiliary inputs of the ADC.

# 4 Application schematic description

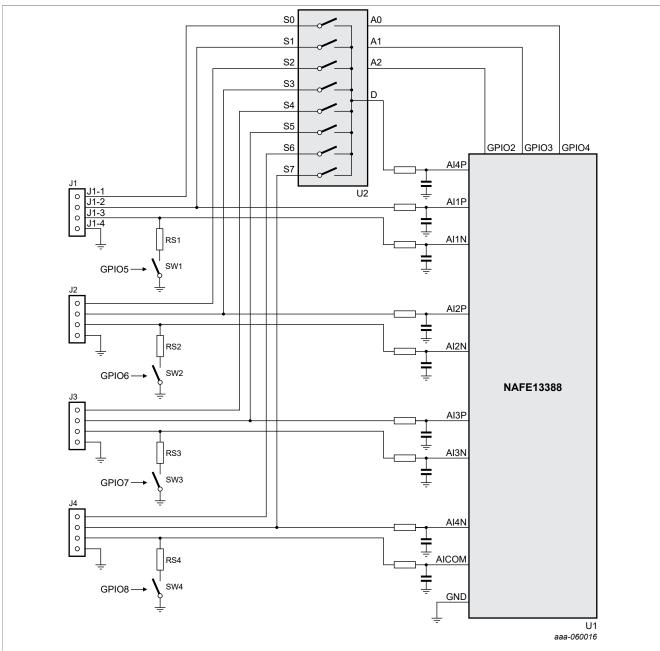

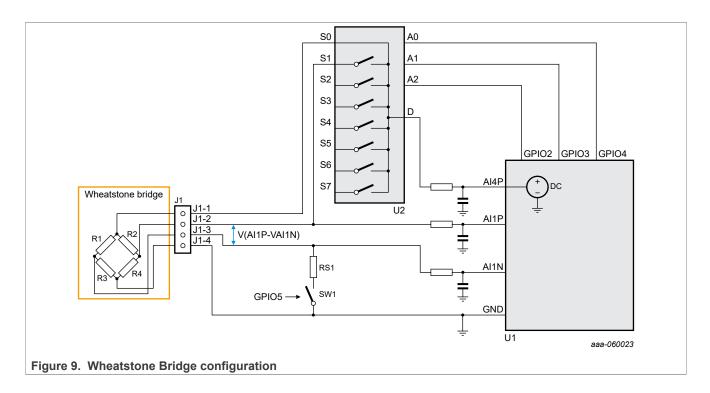

<u>Figure 2</u> shows the implementation of the four-channel, software-compatible, universal-input solution with the NAFE13388.

J1 to J4 are the connectors to the transducers. Each connector has four terminals, which are all used in the case of 4-wire RTDs. Other transducers require fewer terminals.

The AI4P pin of the NAFE13388 is used as current excitation to measure the RTD resistance. To support multiple channels, the current is routed to the Jx connectors through the multiplexer U2.

Referring to J1 connector, for example, the current is supplied to the J1-1 terminal for 4-wire RTDs, to J1-2 for 3-wire RTDs, and to J1-3 for 2-wire RTDs. The multiplexer is driven by three NAFE13388 GPIOs (GPIO2 to GPIO4). A detailed description of the system operation for RTD transducers is described in the dedicated sections.

To support 4-20 mA or 0-20 mA current input, each channel has a sense resistor RSx and a switch. The switch is needed to disconnect the sense resistor from AlxN when other types of transducer are measured. The switches are driven by the NAFE13388 GPIOs (GPIO5 to GPIO8).

For the ±0-10 V inputs, no additional components, such as a resistor divider, are needed because the NAFE13388 inputs can directly measure these voltage ranges.

Figure 2. Application schematic

|    | Voltage<br>input | Current<br>input | 4-wire RTD                        | 3-Wire RTD                        | 2-wire RTD                | Thermocouple              | Wheatstone                        |

|----|------------------|------------------|-----------------------------------|-----------------------------------|---------------------------|---------------------------|-----------------------------------|

| J1 | AIP-AIN          | AI1N-GND         | Force: S0-GND<br>Sense: AI1P-AI1N | Force: S1-GND<br>Sense: AI1P-AI1N | Force/Sense:<br>AI1P-AI1N | AIP-AIN<br>CJC: GPIO0-1   | Force: S0-GND<br>Sense: Al1P-Al1N |

| J2 | AI2P-AI2N        | AI2N-GND         | Force: S2-GND<br>Sense: AI2P-AI2N | Force: S3-GND<br>Sense: Al2P-Al2N | AI2P-AI2N                 | AI2P-AI2N<br>CJC: GPIO0-1 | Force: S2-GND<br>Sense: Al2P-Al2N |

| J3 | AI3P-AI3N        | AI3N-GND         | Force: S4-GND<br>Sense: AI3P-AI3N | Force: S5-GND<br>Sense: Al3P-Al3N | AI3P-AI3N                 | AI3P-AI3N<br>CJC: GPIO0-1 | Force: S4-GND<br>Sense: Al3P-Al3N |

## **NXP Semiconductors**

## Four-channel universal input solution with NAFE13388 family of devices

#### Table 2. Transducers configuration summary...continued

|    | Voltage<br>input | Current<br>input | 4-wire RTD                         | 3-Wire RTD                         | 2-wire RTD | Thermocouple               | Wheatstone                         |

|----|------------------|------------------|------------------------------------|------------------------------------|------------|----------------------------|------------------------------------|

| J4 | AI4N-AICOM       | AICOM-GND        | Force: S6-GND<br>Sense: Al4N-AICOM | Force: S7-GND<br>Sense: Al4N-AICOM | AI4N-AICOM | AI4N-AICOM<br>CJC: GPIO0-1 | Force: S6-GND<br>Sense: Al4N-AICOM |

Note: CJC: cold junction compensation

# 5 Detailed operation

In this section the operation for the supported transducers is described:

- Voltage Input

- Current Input

- 4-wire RTD

- 3-wire RTD

- 2-wire RTD/PTC/NTC

- Thermocouple with cold junction compensations

- Wheatstone bridge

<u>Table 3</u> summarizes the supported sensors. The min/max values refer to the nominal signal range inside which the NAFE13388 accuracy specifications are guaranteed. An extended range is also supported.

### Table 3. Supported transducer nominal signal range

| Sensor                        | Linea  | r range | Extended range                                                   |

|-------------------------------|--------|---------|------------------------------------------------------------------|

|                               | Min    | Max     | _                                                                |

| Voltage input                 | -10 V  | 0 V     | ±12.5 V                                                          |

| Current input [Rs = 250 Ω]    | -40 mA | 40 mA   | ±50 mA                                                           |

| 4/3/2-wire RTD                | All t  | ypes    | For example, Pt100, Pt1000                                       |

| NTC, PTC                      | 1 mΩ   | 1 MΩ    |                                                                  |

| Thermocouple                  | All t  | ypes    |                                                                  |

| Wheatstone Bridge (impedance) | 2.5 kΩ |         | Lower impedance values supported with additional current buffer. |

In the following sections, the examples are all referred to J1 connector. All the cases can be applied, as well, to the other connectors according to  $\underline{\text{Table 3}}$

## 5.1 Voltage input

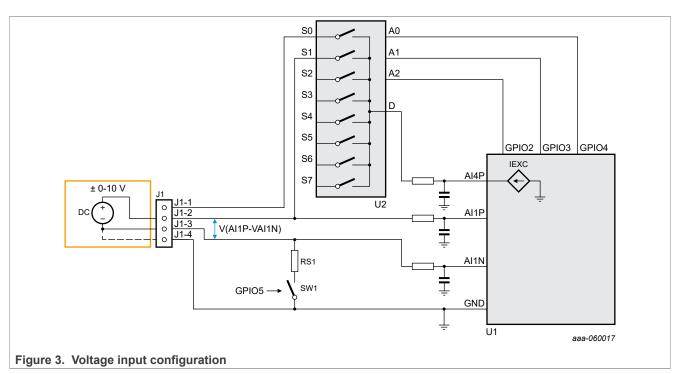

The NAFE13388 measures the most common industrial voltage sensors without any need of external components. The linearity range is guaranteed between -10 V and 10 V. However, the NAFE13388 is able to measure the voltage up to ±12.5 V. The S0 and S1 switches of U2 are open.

The voltage is measured between J1-2 and J1-3 in differential mode, a single-ended configuration is also possible by connecting the transducer between J1-2 and J1-4.

## 5.2 Current input

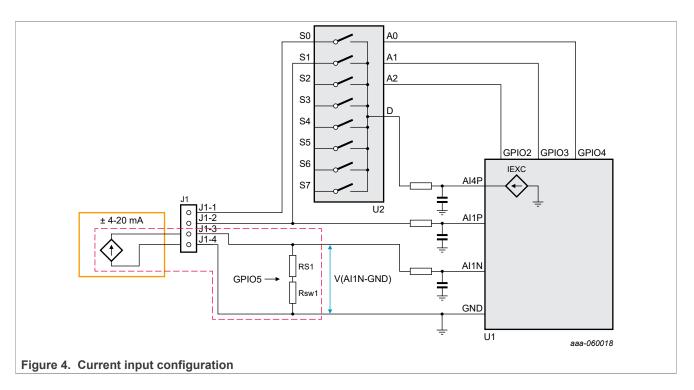

The NAFE13388 measures the typical 4-20 mA or 0-20mA current loop transducers by sensing the voltage across the sense resistor RS1.

To close the current path, the SW1 switch is closed. In <u>Figure 4</u>, the equivalent series resistor of SW1 is also shown. The sum of RS1 and RSW1 translates the current into voltage, which is measured between Al1N and GND pins.

The S0 and S1 switches of U2 are open.

## 5.3 4-wire RTD

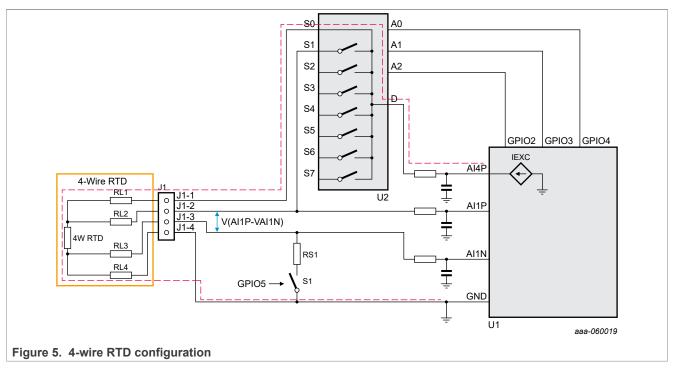

The 4-wire RTD measurement is implemented by injecting the current using the integrated current source in the NAFE13388. The current is routed to J1-1 by closing the S0 switch of U2. It goes through the RTD and returns to ground. Figure 5 shows the resulting current flow. The equivalent series resistances, RL1 to RL4, of the RTD wires are also shown. As the current does not flow through the sensing wires, the resulting voltage of VAI1P-VA1N provides the measurement with good accuracy.

## **NXP Semiconductors**

### Four-channel universal input solution with NAFE13388 family of devices

## 5.4 3-wire RTD

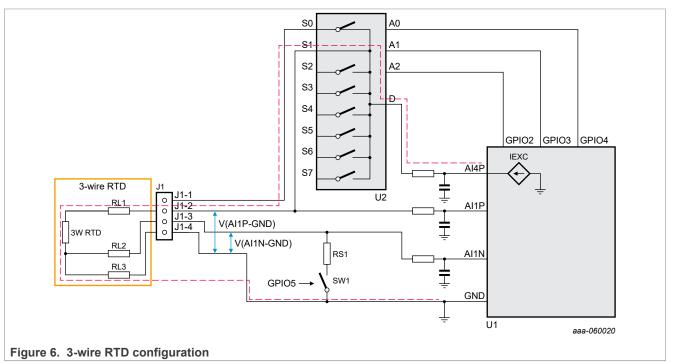

For the 3-wire RTD measurement, the current is injected by the integrated current source of the NAFE13388. The current is routed to J1-2 by closing the S1 switch of U2. It goes through the RTD and returns to ground. <u>Figure 6</u> shows the resulting current flow. The equivalent series resistances, RL1 to RL3, of the RTD wires are also shown. The resulting voltage (V1) is measured between J1-2 and GND. As the wire resistances RL1 and RL3 are also part of the current flow, the measured voltage also includes the wire resistances contribution. The NAFE13388 reduces the error caused by this wire resistance by also measuring the voltage (V2) between J1-3 and GND, which measures the voltage drop caused by RL3 only.

The RTD resistance is calculated as:

$$R_{RTD} = (V1 - 2 \times V2) / IEXC$$

A detailed description and test results of a 3-wire RTD system with NAFE13388 can be found in Reference [3].

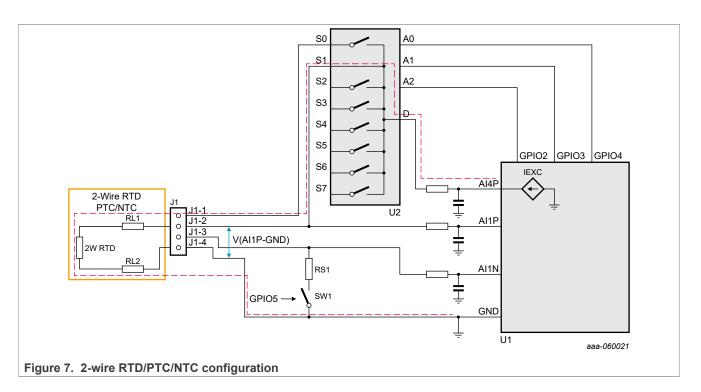

## 5.5 2-wire RTD/PTC/NTC

The 2-wire RTD measurement is the simplest one, but also the least accurate. As seen in the 3-wire RTD configuration, the current is injected through S1, goes to the J1-2 pin, and returns to ground. This time there is no way to estimate or measure the wire resistance RL1 or RL2. The resulting voltage measurement contains the error given by those resistances. To minimize the impact of these resistances, it is recommended to have  $R_{RTD} >> RL1$  and RL2. A Pt1000 RTD with short-wire connection is a configuration where the error can be acceptable.

The same configuration can measure NTC and PTC. These transducers typically have a high value of resistance so the 2-wire configuration achieves good accuracy.

## 5.6 Thermocouple with cold junction compensation

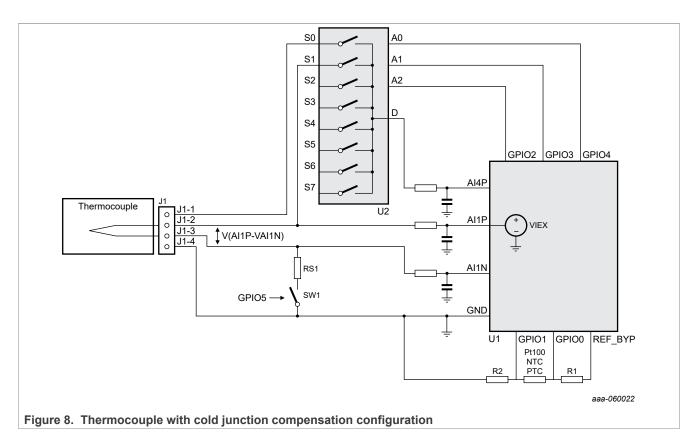

Thanks to the bipolar input range, the NAFE13388 measures thermocouple voltages without the need of bias resistors. This allows implementing the universal input capability without additional switches that typically disconnect the bias resistors in case of other transducers (RTD for example).

In the typical case when a Common mode voltage has to be fixed for the thermocouple, the excitation (VIEXC) can be configured as voltage output on either the AI1P or the AI1N pin. A VIEXC value of some millivolts (DAC code 1-3) allows to fix the Common mode voltage without exceeding the full-scale input.

In addition, the NAFE13388 supports cold junction compensation measurement by using the low-voltage auxiliary inputs of the ADC available at the GPIO0 and GPIO1 pins.

<u>Figure 8</u> shows the implemented configuration. The thermocouple voltage is measured differentially between J1-2 and J1-3. An onboard Pt100 is used to measure the cold junction temperature. The Pt100 current is set by using the precise voltage reference output REF\_BYP and the two low-temperature coefficient resistors R1 and R2. The Pt100 voltage is measured by the auxiliary inputs GPIO0/GPIO1.

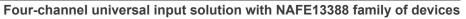

## 5.7 Wheatstone bridge

The NAFE13388 excitation source can also be configured as voltage output. In this way, it is possible to support a Wheatstone bridge measurement without additional components.

When configured as voltage output, the excitation source has an output impedance of 500  $\Omega$ . The applied voltage at J1-1 is the result of the excitation impedance and bridge impedance that work as a resistor divider. In case the measured Wheatstone bridge has low impedance, a voltage buffer might be needed.

The bridge output is measured differentially between AI1P and AI1N.

# 6 Universal input solution test results

The performance tests for a specific transducer input can be found in dedicated documents (References [1], [4].

In this document, the scenario in which different types of transducers are connected to the inputs has been considered. This determines a challenge on the AI-AFE signal chain, which must avoid interactions among the various transducers.

<u>Table 4</u> shows the configuration used in the test. Each connector has a different type of sensor. Six logical channels LCH0 to LCH5 are used and activated to store the various settings and to allow the sequencer to perform the conversions.

|    | Input type               | Logical<br>channel | IN+   | IN-   | Excitation | PGA  | Data rate | Digital filter |

|----|--------------------------|--------------------|-------|-------|------------|------|-----------|----------------|

| J1 | Voltage input            | LCH0               | Al1P  | AI1N  | OFF        | 0.2x | 1 kSPS    | SINC4+2        |

| J2 | Current input            | LCH1               | GND   | AI2N  | OFF        | 0.4x | 1 kSPS    | SINC4+2        |

| J3 | RTD: 3-                  | LCH2               | AI3P  | AI3N  | S5         | 16x  | 50 SPS    | SINC4+3        |

| 33 | wire Pt100               | LCH3               | GND   | AI3N  | S5         | 102  |           |                |

| J4 | Thermocouple<br>with CJC | LCH4               | AICOM | Al4N  | OFF        | 16x  | 50SPS     | SINC4+3        |

|    | Pt100 fo CJC             | LCH5               | GPIO0 | GPIO1 | OFF        | -    | 50 SPS    | SINC4+3        |

Table 4. Transducers input connections and AFE settings

# AN14547

## Four-channel universal input solution with NAFE13388 family of devices

For the voltage input on J1, a gain of 0.2x has been used. This gain setting allows measuring voltages up to  $\pm 10$  V in Unipolar mode and  $\pm 20$  V differentially. See <u>Table 1</u> for detailed values of nominal and min/max ranges according to different PGA gains.

For the current input (J2), a 250  $\Omega$  sense resistor has been used in all channels. A normally open MOSFET relay SPST activates the current input path. The SPST has a series resistance of around 7  $\Omega$ . This additional resistance is also part of the voltage-to-current conversion during the onboard calibration. The resulting voltage is around 5 V, so a gain of 0.4x has been used for the PGA.

The Pt100 RTD is emulated with a 100  $\Omega$  resistor connected as a 3-wire RTD. The wires are 10-meter AWG25 cables. The resistance of each wire is around 1  $\Omega$ .

The thermocouple signal is emulated with a voltage source of around 5 mV, and the CJC is implemented with a Pt100 RTD as described in <u>Section 5.6</u>.

<u>Table 5</u> summarizes the test results. All the channels have been calibrated with the two-points calibration method described in Reference [1]. All the measurements have been verified using a digital multimeter (DMM), and calculating the errors as percentage.

Table 5. Measurement results

| Function      | Logical channel | IN+                | IN-                    | PGA   | Data rate | SINC filter | VIEXC | DMM           | MEAS       | Error [%] |

|---------------|-----------------|--------------------|------------------------|-------|-----------|-------------|-------|---------------|------------|-----------|

| Voltage input | 0               | AI1P               | AI1N                   | 0.2   | 1k        | SINC4+2     | OFF   | 6.995 V       | 6.996 V    | 0.017 %   |

| Current input | 1               | Al2P               | GND                    | 0.4   | 1k        | SINC4+2     | OFF   | 14.211 mA     | 14.216 mA  | 0.036 %   |

| 3-wire RTD    | 2               | AI3P               | GND                    | 16    | 50        | SINC4+3     | S5    | _             | 0.050836 V | —         |

|               | 3               | AI3N               | GND                    | 16    | 50        | SINC4+3     | S5    | _             | 0.000504 V | —         |

|               | _               | (V <sub>LCH2</sub> | -2*V <sub>LCH3</sub> ) | /IEXC | _         | —           | _     | 99.690 Ω      | 99.656 Ω   | -0.034 %  |

| Thermocouple  | 4               | AI4N               | AICOM                  | 16    | 50        | SINC4+3     | OFF   | 0.005160<br>V | 0.005156 V | -0.078 %  |

| CJC           | 5               | GPIO0              | GPIO1                  | х     | 50        | SINC4+3     | OFF   | 0.04541 V     | 0.04540 V  | -0.010 %  |

The 3-wire RTD measurement needs a detailed explanation to describe the implemented wire cancelation technique, see Reference [3].

Logical channel 2 (LCH2) and logical channel 3 (LCH3) has been configured to measure AI3P vs GND and AI3N vs GND.

The system has been previously calibrated by measuring two precise test resistors on LCH2 to perform the two points calibration. After the onboard calibration, the emulated Pt100 resistor with 10-meter cable is tested.

As anticipated in <u>Section 5.4</u>, in LCH2 measurement, the result is the composition of the voltage drop in RL1, RTD and RL3, while in LCH3 only the RL3 contribution creates the voltage drop. As usual, in 3-wire RTD systems, assuming RL1 = RL2 = RL3, the measurement of RTD is obtained as:

$$R_{RTD} = (V_{LCH2} - 2 \times V_{LCH3}) / \text{IEXC} = (0.050836 - 0.001008) / 500^{-6} = 99.656\Omega$$

The test resistor was measured with DMM to be 99.960  $\Omega$  , so the error corresponds to 0.09 °C.

For CJC, the following formula provides the relationship between the voltage measured  $V_{MEAS}$  on GPIO0-1 and the resistance value:

$$R(Pt100) = \frac{V_{MEAS}(R1+R2)}{VREF-V_{MEAS}} = 109.215 \ \Omega$$

Where:

$$R1 = R2 = 2.94 \ k\Omega$$

$VREF = 2.49 \ V$

$V_{MEAS} = 0.0450 \ V$

The measured resistance corresponds to a cold junction temperature of 23.93 °C.

# 7 Summary

The proposed solution implements a four-channel, fully configurable universal-input system. All the channels are exchangeable and each channel supports all the most common transducers used in industrial applications.

The logical channels feature of the NAFE13388 allows implementation of the universal input thanks to the possibility to configure different settings for analog inputs, gain, data rate, and excitation source on each logical channel.

The test results show good performance, even when high-amplitude signals and small signals are applied on different channels at the same time.

# 8 References

- [1] AN14102 Industrial application measurements using NXP AFE

- [2] NAFE13388 NAFE13388/NAFE73388 data sheets

- [3] AN14127 RTD measurement system with NAFE13388/73388 family of devices

- [4] AN14539 3-wire RTD with NAFE13388

# 9 Revision history

#### Table 6. Revision history

| Document ID   | Release date  | Description     |

|---------------|---------------|-----------------|

| AN14547 v.1.0 | 28 March 2025 | Initial version |

# Legal information

## Definitions

**Draft** — A draft status on a document indicates that the content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included in a draft version of a document and shall have no liability for the consequences of use of such information.

## Disclaimers

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. NXP Semiconductors takes no responsibility for the content in this document if provided by an information source outside of NXP Semiconductors.

In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of NXP Semiconductors.

**Right to make changes** — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this respect.

Terms and conditions of commercial sale — NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at https://www.nxp.com/profile/terms, unless otherwise agreed in a valid written individual agreement. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. NXP Semiconductors hereby expressly objects to applying the customer's general terms and conditions with regard to the purchase of NXP Semiconductors products by customer.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

**HTML publications** — An HTML version, if available, of this document is provided as a courtesy. Definitive information is contained in the applicable document in PDF format. If there is a discrepancy between the HTML document and the PDF document, the PDF document has priority.

**Translations** — A non-English (translated) version of a document, including the legal information in that document, is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.

Security — Customer understands that all NXP products may be subject to unidentified vulnerabilities or may support established security standards or specifications with known limitations. Customer is responsible for the design and operation of its applications and products throughout their lifecycles to reduce the effect of these vulnerabilities on customer's applications and products. Customer's responsibility also extends to other open and/or proprietary technologies supported by NXP products for use in customer's applications. NXP accepts no liability for any vulnerability. Customer should regularly check security updates from NXP and follow up appropriately. Customer shall select products with security features that best meet rules, regulations, and standards of the intended application and make the ultimate design decisions regarding its products and is solely responsible for compliance with all legal, regulatory, and security related requirements concerning its products, regardless of any information or support that may be provided by NXP.

NXP has a Product Security Incident Response Team (PSIRT) (reachable at <u>PSIRT@nxp.com</u>) that manages the investigation, reporting, and solution release to security vulnerabilities of NXP products.

Suitability for use in industrial applications (functional safety) - This NXP product has been qualified for use in industrial applications. It has been developed in accordance with IEC 61508, and has been SIL-classified accordingly. If this product is used by customer in the development of, or for incorporation into, products or services (a) used in safety critical applications or (b) in which failure could lead to death, personal injury, or severe physical or environmental damage (such products and services hereinafter referred to as "Critical Applications"), then customer makes the ultimate design decisions regarding its products and is solely responsible for compliance with all legal, regulatory, safety, and security related requirements concerning its products, regardless of any information or support that may be provided by NXP. As such, customer assumes all risk related to use of any products in Critical Applications and NXP and its suppliers shall not be liable for any such use by customer. Accordingly, customer will indemnify and hold NXP harmless from any claims, liabilities, damages and associated costs and expenses (including attorneys' fees) that NXP may incur related to customer's incorporation of any product in a Critical Application.

$\ensuremath{\mathsf{NXP}}\xspace \mathsf{B.V.}$  — NXP B.V. is not an operating company and it does not distribute or sell products.

## Trademarks

Notice: All referenced brands, product names, service names, and trademarks are the property of their respective owners. **NXP** — wordmark and logo are trademarks of NXP B.V.

# Tables

- Tab. 1. Nominal and min/max input voltage ranges ..... 5

- Tab. 2.

Transducers configuration summary ......7

- Tab. 3.Supported transducer nominal signal range ......9

# **Figures**

| Fig. 1. | NAFEx33388 block diagram    | 4  |

|---------|-----------------------------|----|

| Fig. 2. | Application schematic       | 7  |

| Fig. 3. | Voltage input configuration |    |

| Fig. 4. | Current input configuration | 11 |

| Fig. 5. | 4-wire RTD configuration    | 11 |

| Fig. 6. | 3-wire RTD configuration    |    |

| Fig. 7.  | 2-wire RTD/PTC/NTC configuration          | 13 |

|----------|-------------------------------------------|----|

| Fig. 8.  | Thermocouple with cold junction           |    |

|          | compensation configuration                | 14 |

| Fig. 9.  | Wheatstone Bridge configuration           | 15 |

| Fig. 10. | Schematic of the configuration under test | 17 |

## Contents

| 1   | Introduction                           | 2  |

|-----|----------------------------------------|----|

| 2   | NAFE13388 family description           | 3  |

| 3   | NAFE13188 operation in universal input |    |

|     | system                                 | 4  |

| 4   | Application schematic description      | 6  |

| 5   | Detailed operation                     | 9  |

| 5.1 | Voltage input                          |    |

| 5.2 | Current input                          |    |

| 5.3 | 4-wire RTD                             |    |

| 5.4 | 3-wire RTD                             | 12 |

| 5.5 | 2-wire RTD/PTC/NTC                     | 12 |

| 5.6 | Thermocouple with cold junction        |    |

|     | compensation                           | 13 |

| 5.7 | Wheatstone bridge                      |    |

| 6   | Universal input solution test results  |    |

| 7   | Summary                                |    |

| 8   | References                             |    |

| 9   | Revision history                       |    |

| -   | Legal information                      |    |

|     | -                                      |    |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.

© 2025 NXP B.V.

All rights reserved.

For more information, please visit: https://www.nxp.com

Document feedback Date of release: 28 March 2025 Document identifier: AN14547