# AN14417 Using the SEMC SRAM WAIT feature on i.MX RT1180 Rev. 2.0 — 10 March 2025

**Application note**

#### **Document information**

| Information | Content                                                                                                                                                    |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Keywords    | AN14417, SEMC SRAM wait feature, RT1180, i.MX RT1180, smart external memory controller, SEMC, SRAM, WAIT                                                   |

| Abstract    | This application note introduces the i.MX RT1180 SEMC SRAM WAIT feature, the background for necessity of the WAIT feature and how it works on i.MX RT1180. |

## 1 Overview

This application note describes the i.MX RT1180 smart external memory controller (SEMC) static randomaccess memory (SRAM) WAIT feature. The document also provides the background for the necessity of the WAIT feature and how it works on i.MX RT1180. An i.MX RT1170 EVK board helps simulate a device and generate the WAIT signal for evaluation.

# 2 Importance of the WAIT signal

For some device, each access cycle is not constant and you must not access it by a fixed configuration. In such case, use the WAIT/BUSY/RDY signal to get the maximum bandwidth. For example, a device sometimes needs 80 ns to end the access cycle. Whereas sometimes a device needs 200 ns to end the access cycle. By fixed configuration, one must set the wait time as the maximum access time, which is 200 ns access cycle. In such a case, 120 ns gets wasted for a short period access cycle of 80 ns.

### Note: In different scenario, WAIT is referred to as BUSY or READY/RDY.

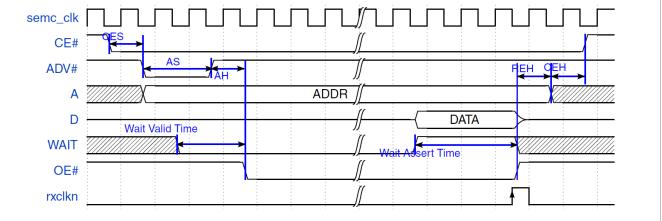

The picture below is an example that the negating WAIT pin terminates the access cycle.

Figure 1. Example of the WAIT pin use case

# 3 Design of the WAIT feature on i.MX RT1180

This section describes the WAIT feature-related bit and the configuration of the modes.

## 3.1 WAIT feature-related register bit

The WAIT feature-related register bit includes:

- WAITEN: Bit 2 in SRAMC0/4

- WAITSP: Bit 3 in SRAMC0/4

- WAIT\_TIME: Bit 16 in SRAMC0/4

#### Note:

- Device 0/CSX 0 uses SRAMC0

- Device 1-3/CSX 1-3 uses SRAMC4

### 3.2 Configuration for two different modes

The following table lists the two modes used in the application.

| Table 1. Configuration of mode | s |

|--------------------------------|---|

|--------------------------------|---|

|        | WAITEN | WAITSP | WAIT_TIME | Comment                                                                                                |

|--------|--------|--------|-----------|--------------------------------------------------------------------------------------------------------|

| Mode 1 | 1      | 1      | 0         | If there is WAIT asserted in every access cycle, use this configuration mode.                          |

| Mode 2 | 1      | 1      | 1         | If the device sometimes asserts WAIT, and sometimes does not assert WAIT, use this configuration mode. |

- For Mode 1: SEMC checks the WAIT rising edge. When WAIT rising edge appears, SEMC immediately terminates the current access cycle.

- For Mode 2: SEMC at first counts the REL/WEL down. When a REL/WEL timeout happens, SEMC checks the WAIT line status. If WAIT asserts at this moment, SEMC waits until WAIT negates. If WAIT does not assert at the moment, SEMC terminates the current access cycle.

## 4 Evaluate SEMC WAIT feature on i.MX RT1180 EVK

This section describes the steps to <u>route signals out from i.MX RT1180</u> and <u>simulate device behavior</u>. The section also describes the <u>test cases and result for mode 1 and mode 2</u>.

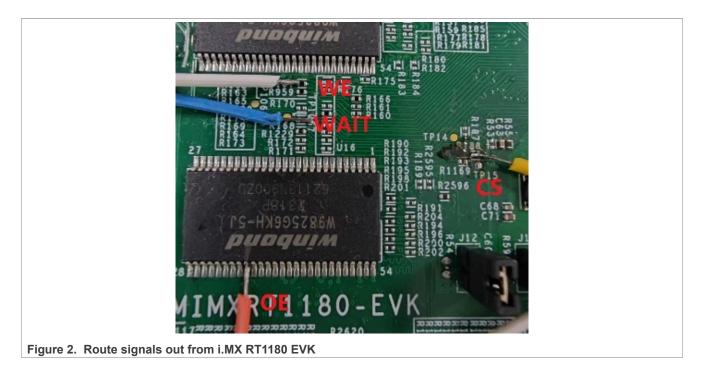

### 4.1 How to route signals out from i.MX RT1180 EVK

Due to hardware limitation, this application note shows only the basic WAIT feature behavior, instead of a fully and whole SRAM access with WAIT feature. At least four signals route out to evaluate the SEMC WAIT feature. The signals are CS, WAIT, OE, and WE.

The table below guides how to route the signals out from i.MX RT1180 EVK.

| Table Il Reate eignale eat |                 |                               |

|----------------------------|-----------------|-------------------------------|

| Signal                     | Mapping to SEMC | Watchpoint on i.MX RT1180 EVK |

| CS                         | SEMC_CSX0       | R188                          |

| WAIT                       | SEMC_BA0        | R168                          |

| OE                         | SEMC_A12        | Pin36 of U16                  |

| WE                         | SEMC_A11        | R167                          |

Table 2. Route signals out from i.MX RT1180 EVK

Using the SEMC SRAM WAIT feature on i.MX RT1180

## 4.2 How to simulate device behavior

To evaluate the wait feature in different conditions, we need a device for checking CS. Once CS is low, after Delay\_1 it asserts WAIT. After Delay 2, it negates WAIT.

The command in the console enables the programming and specification of Delay 1 and Delay 2.

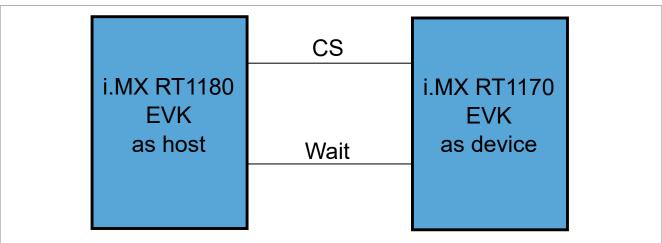

An i.MX RT1170 EVK board was used for the device test. The figure below shows the connection between the i.MX RT1180 EVK and i.MX RT1170 EVK boards.

Figure 4. Connection between i.MX RT1180 EVK and i.MX RT1170 EVK

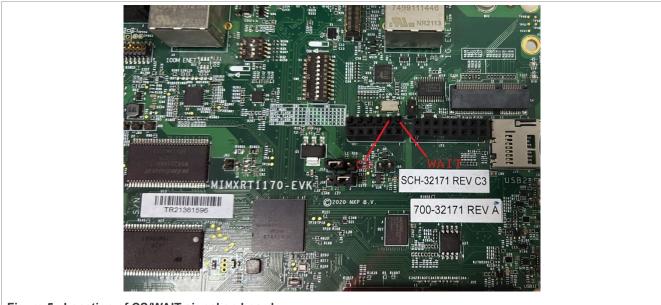

For i.MX RT1170 pin assignment, see the table below.

| Table 3. I.MX R11170 pin a | assignment     |                   |

|----------------------------|----------------|-------------------|

| Signal                     | Pin assignment | Location on board |

| CS                         | GPIO_AD_11     | J26 pin 4         |

| WAIT                       | GPIO_AD_10     | J26 pin 2         |

| GND                        |                | J26 pin 1         |

For the location of the signals on the board, see the image below.

Figure 5. Location of CS/WAIT signal on board

## 4.3 Test cases and result

This section introduces some test cases to check the WAIT feature on the i.MX RT1180 EVK board.

The delay and wait\_low value mentioned below is the parameter for void wait\_simulate(int delay, int wait\_low) and it is used to generate Delay\_1 and Delay\_2 mentioned in Section 4.2. For more information on code, see Section 5.2.

### 4.3.1 Test cases for Mode 1

Test case 1: Read, WAIT for 16 ns (delay=0, wait low=0).

#### **Result:**

Figure 6. Mode 1, Read, WAIT for 16 ns

**Test case 2**: Read, WAIT for 104 ns (delay=0, wait\_low=10). The following image illustrates that the WAIT signal extends the access cycle.

#### Result:

Figure 7. Mode 1, Read, WAIT for 104 ns

Test case 3: Write, WAIT for 16 ns (delay=0, wait\_low=0).

Result:

Figure 8. Mode 1, Write, WAIT for 16 ns

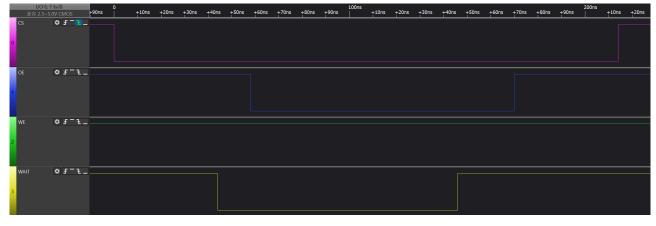

**Test case 4**: Write, WAIT for 104 ns (delay=0, wait\_low=10). The following image illustrates that the WAIT signal extends the access cycle.

#### Result:

|         | 电平标准<br>~5.0V CMOS | 0<br>-90ns | +10ns  | +20ns | +30ns | +40ns | +50ns | +60ns | +70ns | +80ns | +90ns | 100ns | +10ns | +20ns | +30ns | +40ns | +50ns | +60ns | +70ns | +80ns | +90ns | 200ns | +10ns | +20ns | +30ns |

|---------|--------------------|------------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| cs<br>0 | \$ <b></b> _       |            |        |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |

| OE<br>1 | ¢∮-1_              |            |        |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |

| 2 WE    | ¢∮-1_              |            |        |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |

| WAIT    | \$F-f_             |            |        |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |

| Figure  | 9 Mod              | a 1 Wi     | rito \ | רו אי | for   | 104   | ne    |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |

Figure 9. Mode 1, Write, WAIT for 104 ns

### 4.3.2 Test cases for Mode 2

**Test case 1**: Read, no WAIT (delay=20, wait\_low=0). When REL timeout, WAIT is not asserted, then the SEMC begins to terminate the current access cycle.

Result:

Figure 10. Read, no WAIT

**Test case 2**: Read, with WAIT (delay=0, wait\_low=10). When REL timeout, WAIT is asserted, then the SEMC terminates the current access cycle after WAIT negates.

Result:

Figure 11. Read, with WAIT

**Test case 3**: Write, no WAIT (delay=20, wait\_low=0). When WEL timeout, WAIT is not asserted, then the SEMC begins to terminate the current access cycle.

Result:

## **NXP Semiconductors**

# AN14417

Using the SEMC SRAM WAIT feature on i.MX RT1180

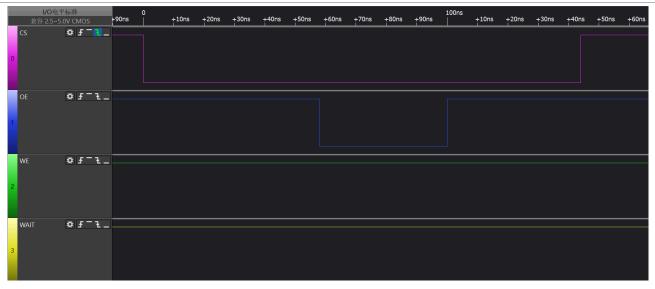

**Test case 4**: Write, with WAIT (delay=0, wait\_low=10). When WEL timeout, WAIT is asserted, then the SEMC terminates the current access cycle after WAIT negates.

Result:

|   |           | 1                    | -90ns  | +10ns | +20ns | +30ns | +40ns | +50ns | +60ns | +70ns | +80ns | +90ns | 100ns | +10ns | +20ns | +30ns | +40ns | +50ns | +60ns | +70ns | +80ns | +90ns | 200ns | +10ns | +20ns | +30ns |

|---|-----------|----------------------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

|   | cs        | ¤ <b>₹</b> ¯∎_)      |        |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |

|   | OE<br>1   | ¢ ƒ <sup>−</sup> ₹_) |        |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |

|   | WE<br>2   | ¢ ƒ <sup>−</sup> ₹_  |        |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |

|   | WAIT<br>3 | ¢ f <sup>−</sup> t_  |        |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |

| F | igure     | 13. Wri              | te, wi | th WA | IT    |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |

# 5 Key code

This section lists the key codes on the i.MX RT1180 EVK and i.MX RT1170 EVK boards.

## 5.1 Key code on i.MX RT1180

The test code is based on the SEMC driver example in the SDK.

Make sure to configure GPIO\_EMC\_B1\_41 for SEMC\_CSX00.

Also, BOARD\_InitPins() must have the following code added to it.

```

IOMUXC_SetPinMux(IOMUXC_GPIO_EMC_B1_41_SEMC_CSX00, 0U);

IOMUXC_SetPinConfig(IOMUXC_GPIO_EMC_B1_41_SEMC_CSX00, 0x08U);

```

```

Semc sdram.c must have the following code applied to it.

```

```

/*

* Copyright 2017-2020 NXP

* All rights reserved.

* SPDX-License-Identifier: BSD-3-Clause

*/

#include "fsl_debug_console.h"

#include "fsl_device_registers.h"

#include "pin_mux.h"

#include "clock config.h"

#include "board.h"

#include "fsl semc.h"

#include "fsl cache.h"

* Definitions

#define EXAMPLE SEMC

SEMC

#define EXAMPLE SEMC START ADDRESS (0x800000000)

#define EXAMPLE SEMC CLK FREQ CLOCK GetRootClockFreq(kCLOCK Root Semc)

* Code

void APP ConfigMPU(void)

{

/* Disable code & system cache */

XCACHE DisableCache (XCACHE PC);

XCACHE DisableCache (XCACHE PS);

/* Disable MPU */

ARM MPU Disable();

/* Region 9 setting: Memory with Normal type, not shareable, outer/inner

write through */

ARM MPU SetRegion (2U, ARM MPU RBAR (EXAMPLE SEMC START ADDRESS,

ARM MPU SH OUTER, OU, 1U, OU), ARM MPU RLAR(0xDFFFFFFF, 1U));

/* Enable MPU */

ARM MPU Enable (MPU CTRL PRIVDEFENA Msk);

/* Enable code & system cache */

XCACHE EnableCache (XCACHE_PS);

XCACHE EnableCache (XCACHE PC);

}

status t BOARD InitSEMC SRAM(void)

{

status t status;

semc_config_t config;

semc_sram_config_t sram_config;

uint32_t clockFrq = EXAMPLE SEMC CLK FREQ;

memset(&config, 0, sizeof(semc config t));

memset(&sram config, 0, sizeof(sram config));

/* Initialize SEMC. */

SEMC GetDefaultConfig(&config);

AN14417

```

#### Using the SEMC SRAM WAIT feature on i.MX RT1180

```

config.dqsMode = kSEMC Loopbackdqspad; /* For more accurate timing. */

SEMC Init(SEMC, &config);

//SRAM config.

sram config.cePinMux = kSEMC MUXCSX0;

sram config.addr27 = kSEMC MORA27 NONE;

sram config.address = EXAMPLE SEMC START ADDRESS;

sram config.memsize kbytes = 1\overline{6};

sram config.addrPortWidth = 8;

sram config.addrMode = kSEMC AddrDataNonMux;

sram_config.burstLen = kSEMC_Nor_BurstLen1;

sram_config.portSize = kSEMC_PortSize8Bit;

sram config.syncMode = kSEMC AsyncMode;

sram config.waitEnable = true;

sram config.waitSample = true;

sram config.advLevelCtrl = kSEMC AdvHigh;

#define NS SET 20

#define NS_SET 20

sram_config.tCeSetup_Ns = NS_SET;

sram_config.tCeHold_Ns = NS_SET;

sram_config.tAddrSetup_Ns = NS_SET;

sram_config.tAddrHold_Ns = NS_SET;

sram_config.tWeLow_Ns = NS_SET;

sram_config.tReLow_Ns = NS_SET;

sram_config.tReHigh_Ns = NS_SET;

sram_config.tCeInterval_Ns = NS_SET;

// For async mode

sram config.tTurnAround Ns = NS SET;

sram config.tAddr2WriteHold Ns = NS SET;

PRINTF("semc clock = %d\r\n", clockFrq);

status = SEMC ConfigureSRAM(SEMC, &sram config, clockFrq);

// Enable Mode 2, mask this line to get Mode 1.

SEMC->SRAMCR0 |= 0x10000;

PRINTF("SEMC->SRAMCR0 = %x\r\n", SEMC->SRAMCR0);

PRINTF("SEMC->SRAMCR1 = %x\r\n", SEMC->SRAMCR1);

PRINTF("SEMC->SRAMCR2 = %x\r\n", SEMC->SRAMCR2);

PRINTF("SEMC->SRAMCR3 = %x\r\n", SEMC->SRAMCR3);

if (SEMC->SRAMCR0 & 0x10000)

{

PRINTF("wait mode: mode 2.\r\n");

}

else

{

PRINTF("wait mode: mode 1.\r\n");

}

return status;

```

Using the SEMC SRAM WAIT feature on i.MX RT1180

```

}

void test semc sram(void)

{

char c;

volatile uint8_t * p_8 = (volatile uint8_t *) EXAMPLE_SEMC_START_ADDRESS;

volatile uint8 t r 8;

while (1)

{

PRINTF("Press r for read and w for write. \r\n");

c = GETCHAR();

if(c == 'r')

{

PRINTF("read. \r\n");

r 8 = *p 8;

}

if(c == 'w')

{

PRINTF("write. \r\n");

*p 8 = r 8;

}

}

}

int main(void)

{

BOARD ConfigMPU();

BOARD InitPins();

BOARD BootClockRUN();

BOARD InitDebugConsole();

APP ConfigMPU();

PRINTF("\r\n SEMC SDRAM Example Start!\r\n");

if (BOARD InitSEMC SRAM() != kStatus Success)

{

PRINTF("\r\n SEMC SDRAM Init Failed\r\n");

}

while (1)

{

test semc sram();

}

}

```

## 5.2 Key code on i.MX RT1170

Apply the following code in the hello\_world.c file of the hello world example in the SDK.

```

/*

* * Copyright 2016-2017 NXP

* All rights reserved.

*

* SPDX-License-Identifier: BSD-3-Clause

*/

```

Using the SEMC SRAM WAIT feature on i.MX RT1180

```

#include "fsl_device_registers.h"

#include "fsl_debug_console.h"

#include "pin_mux.h"

#include "clock config.h"

#include "board.h"

#include "fsl iomuxc.h"

#include <cr section macros.h>

* Code

#define WAIT HIGH CM7 GPIO3->DR SET = 0x200

#define WAIT_LOW CM7_GPI03->DR_CLEAR = 0x200

/*

delay: Control the time delay to assert WAIT after CS falling edge.

low: Control the WAIT low period length.

Typically used value:

Short wait period:

delay = 0, wait low = 0, 16ns, 16ns

delay = 0; wait low = 10; Ons, 104 ns

Long wait period :

No wait period during access cycle: delay = 10, wait low = 0; 104ns, 0ns,

*/

RAMFUNC(SRAM ITC cm7) void wait simulate(int delay, int wait low)

{

while(CM7 GPIO3->DR & 0x400)

;

while(delay)

delay--;

WAIT LOW;

while (wait low)

wait low--;

WAIT HIGH;

}

void set gpio3 fast(int pin index)

{

if(pin index <= 16)

{

IOMUXC GPR->GPR42 |= (1UL << pin index);</pre>

}

else

{

IOMUXC GPR->GPR43 |= (1UL << (pin index-16));</pre>

}

}

void rgpio init(void)

{

gpio pin config t gpio config output = {kGPIO DigitalOutput, 0,

kGPIO NoIntmode};

gpio pin config t gpio config input = {kGPIO DigitalInput, 0,

kGPIO NoIntmode};

CLOCK EnableClock(kCLOCK Iomuxc);

// WAIT, GPIO AD 10 --> RGPIO 3, 9, RGPIO OUTPUT --> J26 pin 2

```

}

{

}

# AN14417

### Using the SEMC SRAM WAIT feature on i.MX RT1180

```

IOMUXC SetPinMux(IOMUXC GPIO AD 10 GPIO MUX3 IO09,

OU);

IOMUXC SetPinConfig(IOMUXC GPIO AD 10 GPIO MUX3 IO09, 0U);

// CS, GPIO AD 11 --> GPIO 9, 10, RGPIO INPUT --> J26 pin 4

IOMUXC SetPinMux(IOMUXC GPIO AD 11 GPIO MUX3 IO10,

OU);

IOMUXC SetPinConfig(IOMUXC GPIO AD 11 GPIO MUX3 IO10, 0U);

GPIO_PinInit(CM7_GPIO3, 9, &gpio_config_output);

GPIO_PinInit(CM7_GPIO3, 10, &gpio_config_input);

set gpio3 fast(9);

set gpio3 fast(10);

// Set wait high.

WAIT HIGH;

int main (void)

int delay;

int low;

/* Init board hardware. */

BOARD ConfigMPU();

BOARD_InitPins();

BOARD_BootClockRUN();

BOARD InitDebugConsole();

PRINTF("hello world.\r\n");

rgpio init();

while (1)

{

PRINTF("input delay and low: \r\n");

SCANF("%d %d", &delay, &low);

PRINTF("delay = %d, low = %d\r\n", delay, low);

wait_simulate(delay, low);

}

```

#### Note about the source code in the document 6

Example code shown in this document has the following copyright and BSD-3-Clause license:

Copyright 2025 NXP Redistribution and use in source and binary forms, with or without modification, are permitted provided that the following conditions are met:

- 1. Redistributions of source code must retain the above copyright notice, this list of conditions and the following disclaimer.

- 2. Redistributions in binary form must reproduce the above copyright notice, this list of conditions and the following disclaimer in the documentation and/or other materials must be provided with the distribution.

- Neither the name of the copyright holder nor the names of its contributors may be used to endorse or promote products derived from this software without specific prior written permission.

THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS "AS IS" AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE ARE DISCLAIMED. IN NO EVENT SHALL THE COPYRIGHT HOLDER OR CONTRIBUTORS BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL, SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE, DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE OF THIS SOFTWARE, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

## 7 Revision history

Table 4 summarizes revisions to this document.

Table 4. Revision history

| Document ID   | Release date     | Description                 |

|---------------|------------------|-----------------------------|

| AN14417 v.2.0 | 10 March 2025    | Replaced "SMEC" with "SEMC" |

| AN14417 v.1.0 | 18 February 2025 | Initial public revision     |

### Using the SEMC SRAM WAIT feature on i.MX RT1180

# Legal information

## Definitions

**Draft** — A draft status on a document indicates that the content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included in a draft version of a document and shall have no liability for the consequences of use of such information.

## Disclaimers

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. NXP Semiconductors takes no responsibility for the content in this document if provided by an information source outside of NXP Semiconductors.

In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of NXP Semiconductors.

**Right to make changes** — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors and its suppliers accept no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this respect.

Terms and conditions of commercial sale — NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at https://www.nxp.com/profile/terms, unless otherwise agreed in a valid written individual agreement. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. NXP Semiconductors hereby expressly objects to applying the customer's general terms and conditions with regard to the purchase of NXP Semiconductors products by customer.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

Suitability for use in non-automotive qualified products — Unless this document expressly states that this specific NXP Semiconductors product is automotive qualified, the product is not suitable for automotive use. It is neither qualified nor tested in accordance with automotive testing or application requirements. NXP Semiconductors accepts no liability for inclusion and/or use of non-automotive qualified products in automotive equipment or applications.

In the event that customer uses the product for design-in and use in automotive applications to automotive specifications and standards, customer (a) shall use the product without NXP Semiconductors' warranty of the product for such automotive applications, use and specifications, and (b) whenever customer uses the product for automotive applications beyond NXP Semiconductors' specifications such use shall be solely at customer's own risk, and (c) customer fully indemnifies NXP Semiconductors for any liability, damages or failed product claims resulting from customer design and use of the product for automotive applications beyond NXP Semiconductors' standard warranty and NXP Semiconductors' product specifications.

**HTML publications** — An HTML version, if available, of this document is provided as a courtesy. Definitive information is contained in the applicable document in PDF format. If there is a discrepancy between the HTML document and the PDF document, the PDF document has priority.

**Translations** — A non-English (translated) version of a document, including the legal information in that document, is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.

Security — Customer understands that all NXP products may be subject to unidentified vulnerabilities or may support established security standards or specifications with known limitations. Customer is responsible for the design and operation of its applications and products throughout their lifecycles to reduce the effect of these vulnerabilities on customer's applications and products. Customer's responsibility also extends to other open and/or proprietary technologies supported by NXP products for use in customer's applications. NXP accepts no liability for any vulnerability. Customer should regularly check security updates from NXP and follow up appropriately. Customer shall select products with security features that best meet rules, regulations, and standards of the intended application and make the ultimate design decisions regarding its products and is solely responsible for compliance with all legal, regulatory, and security related requirements concerning its products, regardless of any information or support that may be provided by NXP.

NXP has a Product Security Incident Response Team (PSIRT) (reachable at <u>PSIRT@nxp.com</u>) that manages the investigation, reporting, and solution release to security vulnerabilities of NXP products.

$\ensuremath{\mathsf{NXP}}\xspace$  B.V. — NXP B.V. is not an operating company and it does not distribute or sell products.

# Trademarks

Notice: All referenced brands, product names, service names, and trademarks are the property of their respective owners. **NXP** — wordmark and logo are trademarks of NXP B.V.

### Using the SEMC SRAM WAIT feature on i.MX RT1180

## Contents

| 1     | Overview                                  | 2  |

|-------|-------------------------------------------|----|

| 2     | Importance of the WAIT signal             | 2  |

| 3     | Design of the WAIT feature on i.MX        |    |

| -     | RT1180                                    | 2  |

| 3.1   | WAIT feature-related register bit         | 2  |

| 3.2   | Configuration for two different modes     |    |

| 4     | Evaluate SEMC WAIT feature on i.MX        |    |

|       | RT1180 EVK                                | 3  |

| 4.1   | How to route signals out from i.MX RT1180 |    |

|       | EVK                                       | 3  |

| 4.2   | How to simulate device behavior           | 4  |

| 4.3   | Test cases and result                     | 5  |

| 4.3.1 | Test cases for Mode 1                     | 6  |

| 4.3.2 | Test cases for Mode 2                     | 7  |

| 5     | Key code                                  | 9  |

| 5.1   | Key code on i.MX RT1180                   |    |

| 5.2   | Key code on i.MX RT1170                   | 12 |

| 6     | Note about the source code in the         |    |

|       | document                                  | 14 |

| 7     | Revision history                          | 15 |

|       | Legal information                         |    |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.

© 2025 NXP B.V.

All rights reserved.

For more information, please visit: https://www.nxp.com

Document feedback Date of release: 10 March 2025 Document identifier: AN14417